## **Ordering Information**

|        | Package                                                                        | e Options                                                               |                | en Initia             |

|--------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------|-----------------------|

| Device | <b>48-Lead LQFP</b><br>7.00x7.00mm body<br>1.60mm height (max)<br>0.50mm pitch | 28-Lead PLCC<br>.453x.453in body<br>.180in height (max)<br>.050in pitch | $(\mathbb{N})$ | Supertex<br>Compliant |

| HV219  | HV219FG-G                                                                      | HV219PJ-G                                                               | $\sim$         | (Pb)                  |

-G indicates the part is RoHS compliant (Green)

### Absolute Maximum Ratings

| Parameter                                          | Value                            |

|----------------------------------------------------|----------------------------------|

| $V_{_{DD}}$ logic power supply voltage             | -0.5V to +15V                    |

| $V_{PP}$ - $V_{NN}$ supply voltage                 | 220V                             |

| $V_{_{\rm PP}}$ positive high voltage supply       | -0.5V to V <sub>NN</sub> +200V   |

| $V_{_{\rm NN}}$ negative high voltage supply       | +0.5V to -200V                   |

| Logic input voltages                               | -0.5V to V <sub>DD</sub> +0.3V   |

| Analog signal range                                | $V_{_{ m NN}}$ to $V_{_{ m PP}}$ |

| Peak analog signal current/channel                 | 3.0A                             |

| Storage temperature                                | -65°C to +150°C                  |

| Power dissipation:<br>28-Lead PLCC<br>48-Lead LQFP | 1.2W<br>1.0W                     |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Continuous operation of the device at the absolute rating level may affect device reliability. All voltages are referenced to device ground.

## **Operating Conditions**

| Sym              | Parameter                             | Value                                        |

|------------------|---------------------------------------|----------------------------------------------|

| V <sub>DD</sub>  | Logic power supply voltage            | 4.5V to 13.2V                                |

| V <sub>PP</sub>  | Positive high voltage supply          | 40V to V <sub>NN</sub> +200V                 |

| V <sub>NN</sub>  | Negative high voltage supply          | -40V to -160V                                |

| V <sub>IH</sub>  | High level input logic voltage        | $V_{dd}$ -1.5V to $V_{dd}$                   |

| V <sub>IL</sub>  | Low-level input logic voltage         | 0V to 1.5V                                   |

| V <sub>SIG</sub> | Analog signal voltage<br>peak-to-peak | $V_{_{\rm NN}}$ +10V to $V_{_{\rm PP}}$ -10V |

| T <sub>A</sub>   | Operating free air temperature        | 0°C to 70°C                                  |

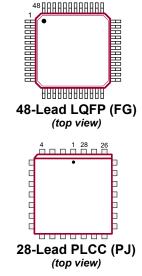

## **Pin Configurations**

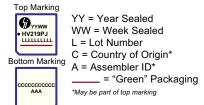

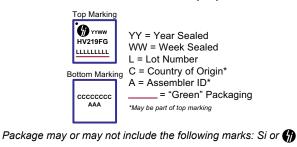

#### **Product Marking**

Package may or may not include the following marks: Si or 28-Lead PLCC (PJ)

48-Lead LQFP (FG)

#### Power Up/Down Sequence

- 1. Power up/down sequence is arbitrary except GND must be powered up first and powered down last. This applies for applications powering GND of the IC with different voltages.

- $V_{_{SIG}}$  must always be at or in between  $V_{_{PP}}$  and  $V_{_{NN}}$  or floating during power up/down transition. Rise and fall times of the power supplies  $V_{_{DD}}$ ,  $V_{_{PP}}$  and  $V_{_{NN}}$  should not be less than 1.0ms. 2.

- 3.

## HV219

## DC Electrical Characteristics (over recommended operating conditions unless otherwise noted)

|                   |                                               | ,    | °C  |      | +25°C |     |      | 0°C |       |                                                                           |

|-------------------|-----------------------------------------------|------|-----|------|-------|-----|------|-----|-------|---------------------------------------------------------------------------|

| Sym               | Parameter                                     | Min  | Max | Min  | Тур   | Max | Min  | Max | Units | Conditions                                                                |

|                   |                                               | -    | 15  | -    | 13    | 19  | -    | 24  |       | I <sub>SIG</sub> = 5.0mA V <sub>PP</sub> = +40V                           |

|                   |                                               | -    | 13  | -    | 11    | 14  | -    | 16  |       | $I_{SIG} = 200 \text{mA}$ $V_{NN}^{PP} = -160 \text{V}$                   |

|                   | Small signal switch                           | -    | 13  | -    | 11    | 14  | -    | 15  |       | I <sub>SIG</sub> = 5.0mA V <sub>PP</sub> = +100V                          |

| R <sub>ons</sub>  | on-resistance                                 | -    | 9.0 | -    | 9.0   | 12  | -    | 14  | Ω     | I <sub>SIG</sub> = 200mA V <sub>NN</sub> <sup>FF</sup> = -100V            |

|                   |                                               | -    | 12  | -    | 10    | 13  | -    | 15  |       | I <sub>SIG</sub> = 5.0mA V <sub>PP</sub> = +160V                          |

|                   |                                               | -    | 11  | -    | 8     | 13  | -    | 14  |       | I <sub>SIG</sub> = 200mA V <sub>NN</sub> <sup></sup> = -40V               |

| $\Delta R_{ons}$  | Small signal switch<br>on-resistance matching | -    | 20  | -    | 5.0   | 20  | -    | 20  | %     | $I_{SIG} = 5.0 \text{mA}, V_{PP} = +100 \text{V}, V_{NN} = -100 \text{V}$ |

| R <sub>ONL</sub>  | Large signal switch<br>on-resistance          | -    | -   | -    | 8.0   | -   | -    | -   | Ω     | $V_{SIG} = V_{PP}$ -10V, $I_{SIG} = 1.0A$                                 |

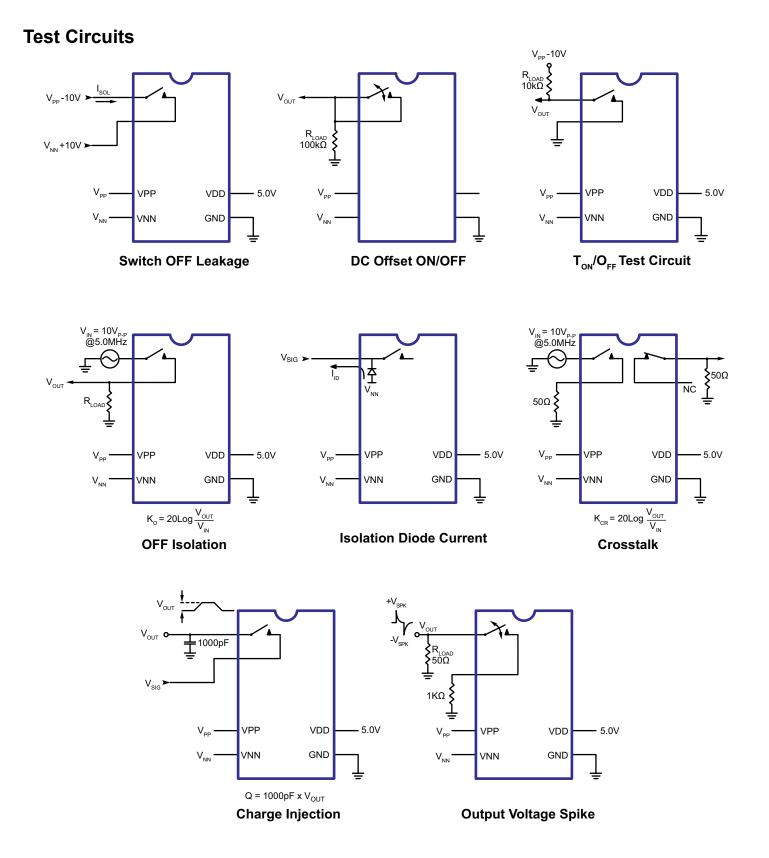

| I <sub>SOL</sub>  | Switch off leakage per switch                 | -    | 5.0 | -    | 1.0   | 10  | -    | 15  | μA    | $V_{SIG} = V_{PP} - 10V \& V_{NN} + 10V$                                  |

| V                 | DC offset switch off                          | -    | 300 | -    | 100   | 300 | -    | 300 | mV    | R <sub>LOAD</sub> = 100kΩ                                                 |

| V <sub>os</sub>   | DC offset switch on                           | -    | 500 | -    | 100   | 500 | -    | 500 | mV    | R <sub>LOAD</sub> = 100kΩ                                                 |

| I <sub>PPQ</sub>  | Quiescent V <sub>PP</sub> supply current      | -    | -   | -    | 10    | 50  | -    | -   | μA    | All switches off                                                          |

| I <sub>NNQ</sub>  | Quiescent $V_{_{NN}}$ supply current          | -    | -   | -    | -10   | -50 | -    | -   | μA    | All switches off                                                          |

| I <sub>PPQ</sub>  | Quiescent V <sub>PP</sub> supply current      | -    | -   | -    | 10    | 50  | -    | -   | μA    | All switches on,<br>I <sub>sw</sub> = 5.0mA                               |

| I <sub>nnq</sub>  | Quiescent $V_{_{NN}}$ supply current          | -    | -   | -    | -10   | -50 | -    | -   | μA    | All switches on,<br>I <sub>sw</sub> = 5.0mA                               |

| I <sub>sw</sub>   | Switch output peak current                    | -    | 3.0 | -    | 3.0   | 2.0 | -    | 2.0 | Α     | V <sub>SIG</sub> duty cycle < 0.1%                                        |

| f <sub>sw</sub>   | Output switch frequency                       | -    | -   | -    | -     | 50  | -    | -   | kHz   | Duty cycle = 50%                                                          |

|                   |                                               | -    | 6.5 | -    | -     | 7.0 | -    | 8.0 |       | $V_{PP} = +40V$ All output<br>$V_{NN} = -160V$ switches                   |

| I <sub>PP</sub>   | Average $V_{_{PP}}$ supply current            | -    | 4.0 | -    | -     | 5.0 | -    | 5.5 | mA    | $V_{PP}$ = +100V are turning<br>$V_{NN}$ = -100V on and off               |

|                   |                                               | -    | 4.0 | -    | -     | 5.0 | -    | 5.5 |       | $V_{PP} = +160V$ at 50kHz<br>$V_{NN} = -40V$ with no load                 |

|                   |                                               | -    | 6.5 | -    | -     | 7.0 | -    | 8.0 |       | $V_{PP} = +40V$ All output<br>$V_{NN} = -160V$ switches                   |

| I <sub>NN</sub>   | Average $V_{_{NN}}$ supply current            | -    | 4.0 | -    | -     | 5.0 | -    | 5.5 | mA    | $V_{PP} = +100V$ are turning<br>$V_{NN} = -100V$ on and off               |

|                   |                                               |      | 4.0 | -    | -     | 5.0 | -    | 5.5 |       | $V_{PP} = +160V$ at 50kHz<br>$V_{NN} = -40V$ with no load                 |

| I <sub>DD</sub>   | Average V <sub>DD</sub> supply current        | -    | 4.0 | -    | -     | 4.0 | -    | 4.0 | mA    | f <sub>CLK</sub> = 5.0MHz, V <sub>DD</sub> = 5.0V                         |

| I <sub>DDQ</sub>  | Quiescent V <sub>DD</sub> supply current      | -    | 10  | -    | -     | 10  | -    | 10  | μA    | All logic inputs are static                                               |

|                   | Data out source current                       |      | -   | 0.45 | 0.70  | -   | 0.40 | -   | mA    | $V_{OUT} = V_{DD} - 0.7V$                                                 |

| I <sub>SINK</sub> | Data out sink current                         | 0.45 | -   | 0.45 | 0.70  | -   | 0.40 | -   | mA    | V <sub>OUT</sub> = 0.7V                                                   |

| C <sub>IN</sub>   | Large input capacitance                       | -    | 10  | -    | -     | 10  | -    | 10  | pF    |                                                                           |

## HV219

|                                        |                                       | <b>0</b> ¢ | <b>D</b> C |     | +25°C |            | +7  | 0°C |       |                                                                              |

|----------------------------------------|---------------------------------------|------------|------------|-----|-------|------------|-----|-----|-------|------------------------------------------------------------------------------|

| Sym                                    | Parameter                             | Min        | Max        | Min | Тур   | Max        | Min | Max | Units | Conditions                                                                   |

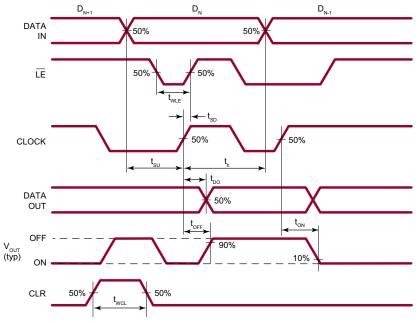

| t <sub>sD</sub>                        | Set-up time before LE rises           | 150        | -          | 150 | -     | -          | 150 | -   | ns    |                                                                              |

| t <sub>WLE</sub>                       | Time width of LE                      | 150        | -          | 150 | -     | -          | 150 | -   | ns    |                                                                              |

| t <sub>DO</sub>                        | Clock delay time to data out          | -          | 150        | -   | -     | 150        | -   | 150 | ns    |                                                                              |

| t <sub>wcL</sub>                       | Time width of CL                      | 150        | -          | 150 | -     | -          | 150 | -   | ns    |                                                                              |

| t <sub>su</sub>                        | Set-up time data to clock             | 15         | -          | 15  | 8.0   | -          | 20  | -   | ns    |                                                                              |

| t <sub>H</sub>                         | Hold time data from clock             | 35         | -          | 35  | -     | -          | 35  | -   | ns    |                                                                              |

| f <sub>CLK</sub>                       | Clock frequency                       | -          | 5.0        | -   | -     | 5.0        | -   | 5.0 | MHz   | 50% duty cycle,<br>$f_{DATA} = f_{CLK}/2$                                    |

| tr, tf                                 | Clock rise and fall times             | -          | 50         | -   | -     | 50         | -   | 50  | ns    |                                                                              |

| T <sub>ON</sub>                        | Turn-on time                          | -          | 5.0        | -   | -     | 5.0        | -   | 5.0 | μs    | $V_{SIG} = V_{PP} - 10V,$                                                    |

| T <sub>OFF</sub>                       | Turn-off time                         | -          | 5.0        | -   | -     | 5.0        | -   | 5.0 | μs    | $R_{LOAD} = 10k\Omega$                                                       |

|                                        |                                       | -          | 20         | -   | -     | 20         | -   | 20  |       | V <sub>PP</sub> = +40V, V <sub>NN</sub> = -160V                              |

| dv/dt                                  | Maximum $V_{SIG}$ slew rate           | -          | 20         | -   | -     | 20         | -   | 20  | V/ns  | V <sub>PP</sub> = +100V, V <sub>NN</sub> = -100V                             |

|                                        |                                       | -          | 20         | -   | -     | 20         | -   | 20  |       | V <sub>PP</sub> = +160V, V <sub>NN</sub> = -40V                              |

| Ko                                     | Off isolation                         | -30        | -          | -30 | -33   | -          | -   | -   | dB    | f = 5.0MHz,<br>1.0KΩ//15pF load                                              |

|                                        |                                       | -58        | -          | -58 | -     | -          | -   | -   |       | f = 5.0MHz, 50Ω load                                                         |

| K <sub>CR</sub>                        | Switch crosstalk                      | -          | -          | -60 | -     | -          | -   | -   | dB    | f = 5.0MHz, 50Ω load                                                         |

| I <sub>ID</sub>                        | Output switch isolation diode current | -          | 300        | -   | -     | 300        | -   | 300 | mA    | 300ns pulse width,<br>2% duty cycle                                          |

| C <sub>SG(OFF)</sub>                   | Off capacitance SW to GND             | 14         | 25         | 14  | 20    | 25         | 14  | 25  | pF    | 0V, f = 1.0MHz                                                               |

| C <sub>SG(ON)</sub>                    | On capacitance SW to GND              | 40         | 60         | 40  | 50    | 60         | 40  | 60  | pF    | 0V, f = 1.0MHz                                                               |

| +V <sub>SPK</sub>                      | -                                     | -          | -          | -   | -     | 150        | -   | -   |       | V <sub>PP</sub> = +40V,                                                      |

| -V <sub>SPK</sub>                      | -                                     | -          | -          | -   | -     | 200        | -   | -   |       | $V_{\rm NN} = -160 V, R_{\rm LOAD} = 50 \Omega$                              |

| +V <sub>SPK</sub>                      | Output voltage spike                  | -          | -          | -   | -     | 150        | -   | -   | mV    | V <sub>PP</sub> = +100V,<br>V <sub>NN</sub> = -100V, R <sub>LOAD</sub> = 50Ω |

| -V <sub>SPK</sub>                      | -                                     | -          | -          | -   | -     | 200<br>150 | -   | -   |       |                                                                              |

| +V <sub>SPK</sub><br>-V <sub>SPK</sub> | -                                     |            | _          | _   | _     | 200        | _   | _   |       | $V_{PP} = +160V,$<br>$V_{NN} = -40V, R_{LOAD} = 50\Omega$                    |

| SPK                                    |                                       | -          | -          | -   | 1450  | -          | -   | -   |       | $V_{PP} = +40V,$<br>$V_{NN} = -160V, V_{SIG} = 0V$                           |

| QC                                     | Charge injection                      | -          | -          | -   | 1050  | -          | -   | -   | рС    | V <sub>PP</sub> = +100V,<br>V <sub>NN</sub> = -100V, V <sub>SIG</sub> = 0V   |

|                                        |                                       | -          | -          | -   | 550   | -          | -   | -   |       | V <sub>PP</sub> = +160V,<br>V <sub>NN</sub> = -40V, V <sub>SIG</sub> = 0V    |

# AC Electrical Characteristics (over recommended operating conditions, V<sub>DD</sub> = 5.0V, unless otherwise noted)

#### **Truth Table**

|    | Da | ata in | 8-Bit | Shift I | Regis | ter |    |    |    |     |     | Ou  | tput Sv  | vitch St | ate |     |     |

|----|----|--------|-------|---------|-------|-----|----|----|----|-----|-----|-----|----------|----------|-----|-----|-----|

| D0 | D1 | D2     | D3    | D4      | D5    | D6  | D7 | LE | CL | SW0 | SW1 | SW2 | SW3      | SW4      | SW5 | SW6 | SW7 |

| L  |    |        |       |         |       |     |    | L  | L  | OFF |     |     |          |          |     |     |     |

| Н  |    |        |       |         |       |     |    | L  | L  | ON  |     |     |          |          |     |     |     |

|    | L  |        |       |         |       |     |    | L  | L  |     | OFF |     |          |          |     |     |     |

|    | Н  |        |       |         |       |     |    | L  | L  |     | ON  |     |          |          |     |     |     |

|    |    | L      |       |         |       |     |    | L  | L  |     |     | OFF |          |          |     |     |     |

|    |    | Н      |       |         |       |     |    | L  | L  |     |     | ON  |          |          |     |     |     |

|    |    |        | L     |         |       |     |    | L  | L  |     |     |     | OFF      |          |     |     |     |

|    |    |        | Н     |         |       |     |    | L  | L  |     |     |     | ON       |          |     |     |     |

|    |    |        |       | L       |       |     |    | L  | L  |     |     |     |          | OFF      |     |     |     |

|    |    |        |       | Н       |       |     |    | L  | L  |     |     |     |          | ON       |     |     |     |

|    |    |        |       |         | L     |     |    | L  | L  |     |     |     |          |          | OFF |     |     |

|    |    |        |       |         | Н     |     |    | L  | L  |     |     |     |          |          | ON  |     |     |

|    |    |        |       |         |       | L   |    | L  | L  |     |     |     |          |          |     | OFF |     |

|    |    |        |       |         |       | Н   |    | L  | L  |     |     |     |          |          |     | ON  |     |

|    |    |        |       |         |       |     | L  | L  | L  |     |     |     |          |          |     |     | OFF |

|    |    |        |       |         |       |     | Н  | L  | L  |     |     |     |          |          |     |     | ON  |

| Х  | Х  | Х      | Х     | Х       | Х     | Х   | Х  | Н  | L  |     |     | Ho  | old Prev | ious Sta | ate |     |     |

| Х  | Х  | Х      | Х     | Х       | Х     | Х   | Х  | Х  | Н  | OFF | OFF | OFF | OFF      | OFF      | OFF | OFF | OFF |

#### Notes:

1. The eight switches operate independently.

2. Serial data is clocked in on the L to H transition clock.

3. The switches go to a state retaining their present condition at the rising edge of the  $\overline{LE}$ .

4. When LE is low, the shift register data flows through the latch.

5. Shift register clocking has no effect on the switch states if  $\overline{LE}$  is high.

6. The clear input overrides all other inputs.

#### **Logic Timing Waveforms**

## HV219

## Pin Description 48-Lead LQFP (FG)

| Pin | Name | Pin | Name | Pin | Name | Pin | Name |

|-----|------|-----|------|-----|------|-----|------|

| 1   | SW5  | 13  | NC   | 25  | VNN  | 37  | DOUT |

| 2   | NC   | 14  | SW2  | 26  | NC   | 38  | NC   |

| 3   | SW4  | 15  | NC   | 27  | NC   | 39  | SW7  |

| 4   | NC   | 16  | SW1  | 28  | GND  | 40  | NC   |

| 5   | SW4  | 17  | NC   | 29  | VDD  | 41  | SW7  |

| 6   | NC   | 18  | SW1  | 30  | NC   | 42  | NC   |

| 7   | NC   | 19  | NC   | 31  | NC   | 43  | SW6  |

| 8   | SW3  | 20  | SW0  | 32  | NC   | 44  | NC   |

| 9   | NC   | 21  | NC   | 33  | DIN  | 45  | SW6  |

| 10  | SW3  | 22  | SW0  | 34  | CLK  | 46  | NC   |

| 11  | NC   | 23  | NC   | 35  | LE   | 47  | SW5  |

| 12  | SW2  | 24  | VPP  | 36  | CLR  | 48  | NC   |

#### Pin Description 28-Lead PLCC (PJ)

| Pin | Name | Pin | Name | Pin | Name | Pin | Name |

|-----|------|-----|------|-----|------|-----|------|

| 1   | SW3  | 8   | SW0  | 15  | NC   | 22  | SW7  |

| 2   | SW3  | 9   | NC   | 16  | DIN  | 23  | SW6  |

| 3   | SW2  | 10  | VPP  | 17  | CLK  | 24  | SW6  |

| 4   | SW2  | 11  | NC   | 18  | LE   | 25  | SW5  |

| 5   | SW1  | 12  | VNN  | 19  | CL   | 26  | SW5  |

| 6   | SW1  | 13  | GND  | 20  | DOUT | 27  | SW4  |

| 7   | SW0  | 14  | VDD  | 21  | SW7  | 28  | SW4  |

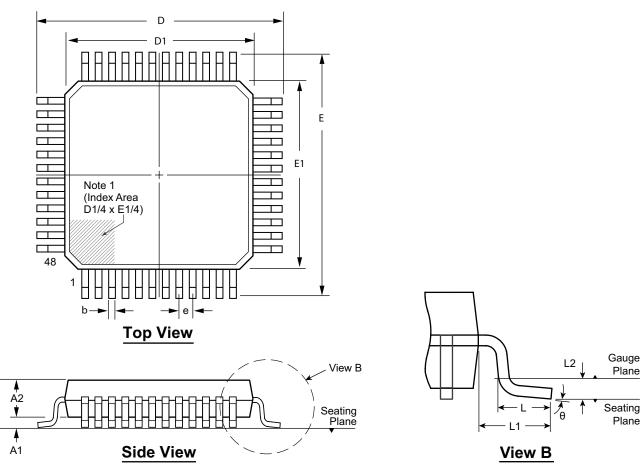

## 48-Lead LQFP Package Outline (FG) 7.00x7.00mm body, 1.60mm height (max), 0.50mm pitch

#### Note:

1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

| Symbo             | ol  | Α     | A1   | A2   | b    | D     | D1    | E     | E1    | е           | L    | L1          | L2          | θ                |

|-------------------|-----|-------|------|------|------|-------|-------|-------|-------|-------------|------|-------------|-------------|------------------|

|                   | MIN | 1.40* | 0.05 | 1.35 | 0.17 | 8.80* | 6.80* | 8.80* | 6.80* |             | 0.45 |             |             | <b>0</b> 0       |

| Dimension<br>(mm) | NOM | -     | -    | 1.40 | 0.22 | 9.00  | 7.00  | 9.00  | 7.00  | 0.50<br>BSC | 0.60 | 1.00<br>REF | 0.25<br>BSC | 3.5 <sup>0</sup> |

| ()                | MAX | 1.60  | 0.15 | 1.45 | 0.27 | 9.20* | 7.20* | 9.20* | 7.20* |             | 0.75 |             |             | <b>7</b> °       |

JEDEC Registration MS-026, Variation BBC, Issue D, Jan. 2001. \* This dimension is not specified in the JEDEC drawing.

Drawings are not to scale.

Supertex Doc. #: DSPD-48LQFPFG Version, D041309.

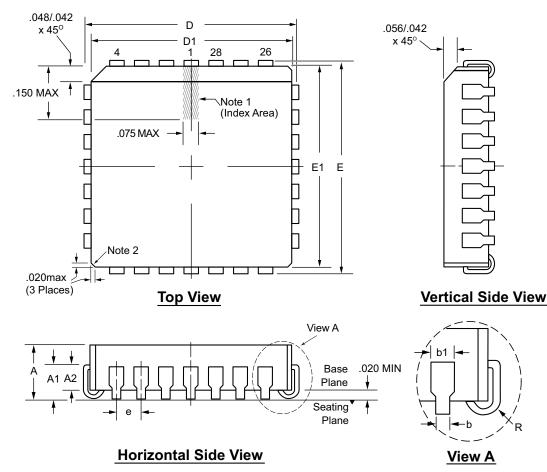

## 28-Lead PLCC Package Outline (PJ) .453x.453in. body, .180in. height (max), .050in. pitch

#### Notes:

- 1. A Pin 1 identifier must be located in the index area indicated. The Pin 1 identifier can be: a molded mark/identifier; an embedded metal marker; or a printed indicator.

- 2. Actual shape of this feature may vary.

| Symbo                 |     | Α    | A1   | A2   | b    | b1   | D    | D1   | E    | E1   | е           | R    |

|-----------------------|-----|------|------|------|------|------|------|------|------|------|-------------|------|

|                       | MIN | .165 | .090 | .062 | .013 | .026 | .485 | .450 | .485 | .450 |             | .025 |

| Dimension<br>(inches) | NOM | .172 | .105 | -    | -    | -    | .490 | .453 | .490 | .453 | .050<br>BSC | .035 |

| (                     | MAX | .180 | .120 | .083 | .021 | .032 | .495 | .456 | .495 | .456 | 200         | .045 |

JEDEC Registration MS-018, Variation AB, Issue A, June, 1993.

Drawings not to scale.

Supertex Doc. #: DSPD-28PLCCPJ, Version B031111.

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>http://www.supertex.com/packaging.html</u>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

9

©2011 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.

Downloaded from Arrow.com.