### Static @ T<sub>J</sub> = 25°C (unless otherwise specified)

|                                   | Parameter                                                        | Min. | Тур. | Max. | Units | Conditions                                                                                                      |

|-----------------------------------|------------------------------------------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------------------------------------|

| V <sub>(BR)DSS</sub>              | Drain-to-Source Breakdown Voltage                                | 60   |      |      | V     | V <sub>GS</sub> = 0V, I <sub>D</sub> = 250µA                                                                    |

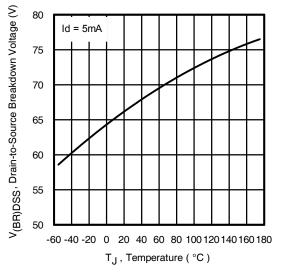

| $\Delta V_{(BR)DSS} / \Delta T_J$ | Breakdown Voltage Temp. Coefficient                              |      | 0.07 |      | V/°C  | Reference to 25°C, $I_D$ = 5mA $@$                                                                              |

| R <sub>DS(on)</sub>               | Static Drain-to-Source On-Resistance                             |      | 5.4  | 6.8  |       | V <sub>GS</sub> = 10V, I <sub>D</sub> = 50A                                                                     |

|                                   |                                                                  |      | 6.6  | 8.3  |       | V <sub>GS</sub> = 4.5V, I <sub>D</sub> = 50A ⑤                                                                  |

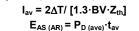

| V <sub>GS(th)</sub>               | Gate Threshold Voltage                                           | 1.0  |      | 2.5  | V     | $V_{DS} = V_{GS}, I_{D} = 100 \mu A$                                                                            |

| gfs                               | Forward Trans conductance                                        | 31   |      |      | S     | V <sub>DS</sub> = 25V, I <sub>D</sub> = 50A                                                                     |

| R <sub>G(Int)</sub>               | Internal Gate Resistance                                         |      | 0.6  |      | Ω     |                                                                                                                 |

| I <sub>DSS</sub>                  | Drain-to-Source Leakage Current                                  |      |      | 20   | μA    | V <sub>DS</sub> = 60V, V <sub>GS</sub> = 0V<br>V <sub>DS</sub> = 60V,V <sub>GS</sub> = 0V,T <sub>J</sub> =125°C |

|                                   |                                                                  |      |      | 250  |       | V <sub>DS</sub> = 60V,V <sub>GS</sub> = 0V,T <sub>J</sub> =125°C                                                |

| I <sub>GSS</sub>                  | Gate-to-Source Forward Leakage<br>Gate-to-Source Reverse Leakage |      |      | 100  |       | V <sub>GS</sub> = 16V                                                                                           |

|                                   |                                                                  |      |      | -100 |       | V <sub>GS</sub> = -16V                                                                                          |

### Dynamic Electrical Characteristics @ T<sub>J</sub> = 25°C (unless otherwise specified)

| Q <sub>g</sub>             | Total Gate Charge                                           |   | 33   | 49 |    | I <sub>D</sub> = 50A                                |

|----------------------------|-------------------------------------------------------------|---|------|----|----|-----------------------------------------------------|

| Q <sub>gs</sub>            | Gate-to-Source Charge                                       |   | 11   |    | nC | V <sub>DS</sub> = 30V                               |

| Q <sub>gd</sub>            | Gate-to-Drain Charge                                        |   | 15   |    |    | V <sub>GS</sub> = 4.5V⑤                             |

| Q <sub>sync</sub>          | Total Gate Charge Sync. (Q <sub>g</sub> - Q <sub>gd</sub> ) |   | 18   |    |    |                                                     |

| t <sub>d(on)</sub>         | Turn-On Delay Time                                          |   | 45   |    |    | V <sub>DD</sub> = 39V                               |

| t <sub>r</sub>             | Rise Time                                                   |   | 216  |    |    | I <sub>D</sub> = 50A                                |

| t <sub>d(off)</sub>        | Turn-Off Delay Time                                         |   | 43   |    | ns | R <sub>G</sub> = 7.5Ω                               |

| t <sub>f</sub>             | Fall Time                                                   |   | 69   |    |    | V <sub>GS</sub> = 4.5V⑤                             |

| C <sub>iss</sub>           | Input Capacitance                                           |   | 3779 |    |    | V <sub>GS</sub> = 0V                                |

| C <sub>oss</sub>           | Output Capacitance                                          |   | 332  |    |    | V <sub>DS</sub> = 50V                               |

| C <sub>rss</sub>           | Reverse Transfer Capacitance                                |   | 163  |    | pF | f = 1.0MHz                                          |

| C <sub>oss eff.</sub> (ER) | Effective Output Capacitance (Energy Related)               |   | 437  |    |    | $V_{GS} = 0V, V_{DS} = 0V \text{ to } 48V \bigcirc$ |

| C <sub>oss eff.</sub> (TR) | Effective Output Capacitance (Time Related)                 |   | 636  |    |    | $V_{GS}$ = 0V, $V_{DS}$ = 0V to 48V (6)             |

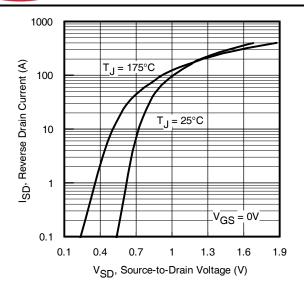

| Diode Characteristics      |                                                             |   |      |    |    |                                                     |

|                            |                                                             | 1 |      |    | 1  |                                                     |

|                 | Parameter                                 | Min.      | Тур.     | Max.        | Units    | Conditions                                                                             |

|-----------------|-------------------------------------------|-----------|----------|-------------|----------|----------------------------------------------------------------------------------------|

| I <sub>S</sub>  | Continuous Source Current<br>(Body Diode) |           |          | <b>99</b> ① |          | MOSFET symbol showing the                                                              |

| I <sub>SM</sub> | Pulsed Source Current<br>(Body Diode) ①   |           |          | 396         |          | integral reverse                                                                       |

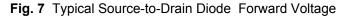

| $V_{SD}$        | Diode Forward Voltage                     |           |          | 1.3         | V        | T <sub>J</sub> = 25°C,I <sub>S</sub> = 50A,V <sub>GS</sub> = 0V ⑤                      |

| t <sub>rr</sub> | Reverse Recovery Time                     |           | 27<br>32 |             | ns       | $T_{J} = 25^{\circ}C$<br>$T_{J} = 125^{\circ}C$ $V_{R} = 51V$ ,                        |

| Q <sub>rr</sub> | Reverse Recovery Charge                   |           | 31<br>43 |             | nC       | $T_J = 25^{\circ}C$<br>$T_J = 125^{\circ}C$<br>$I_F = 50A$<br>$di/dt = 100A/\mu s$ (5) |

|                 |                                           |           | 2.1      |             | Α        | T <sub>J</sub> = 25°C                                                                  |

| t <sub>on</sub> | Forward Turn-On Time                      | Intrinsic | turn-or  | n time is   | negligil | ble (turn-on is dominated by $L_{S}+L_{D}$ )                                           |

Notes:

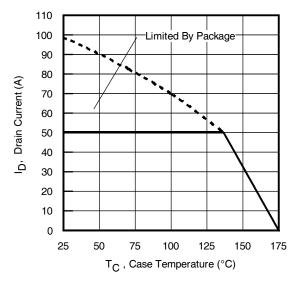

- ① Calculated continuous current based on maximum allowable junction temperature. Bond wire current limit is 50A. Note that current limitations arising from heating of the device leads may occur with some lead mounting arrangements.

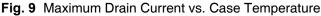

- ② Repetitive rating; pulse width limited by max. junction temperature. (See fig. 11)

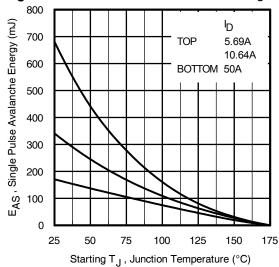

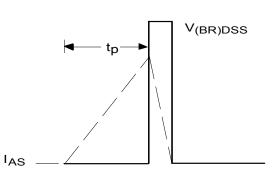

- $\$  Limited by T<sub>Jmax</sub>, starting T<sub>J</sub> = 25°C, L = 0.136mH, R<sub>G</sub> = 25 $\Omega$ , I<sub>AS</sub> = 50A, V<sub>GS</sub> =10V. Part not recommended for use above this value.

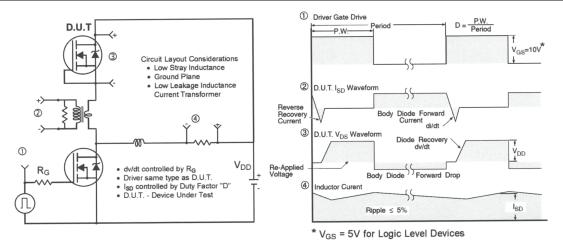

- $\label{eq:ISD} \textcircled{0.5mu}{0.5mu} I_{SD} \leq 50A, \, di/dt \leq 1109A/\mu s, \, V_{DD} \leq V_{(BR)DSS}, \, T_J \leq 175^{\circ}C.$

- S Pulse width  $\leq 400 \mu s$ ; duty cycle  $\leq 2\%$ .

- 6 C<sub>oss eff.</sub> (TR) is a fixed capacitance that gives the same charging time as C<sub>oss</sub> while V<sub>DS</sub> is rising from 0 to 80% V<sub>DSS</sub>.

- $\odot$  C<sub>oss eff.</sub> (ER) is a fixed capacitance that gives the same energy as C<sub>oss</sub> while V<sub>DS</sub> is rising from 0 to 80% V<sub>DSS</sub>.

- When mounted on 1" square PCB (FR-4 or G-10 Material). For recommended footprint and soldering techniques refer to application note #AN-994

- $\begin{tabular}{ll} \end{tabular} \end{tabular} & $R_{\theta}$ is measured at $T_J$ approximately $90^{\circ}C$. \end{tabular} \end{tabular}$

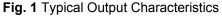

Fig. 3 Typical Transfer Characteristics

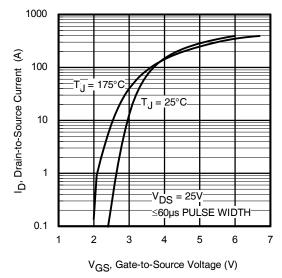

Fig 5. Typical Capacitance vs. Drain-to-Source Voltage

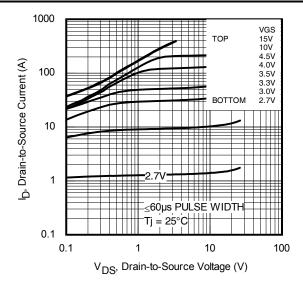

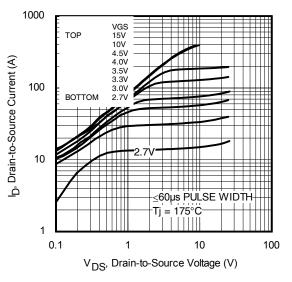

Fig. 2 Typical Output Characteristics

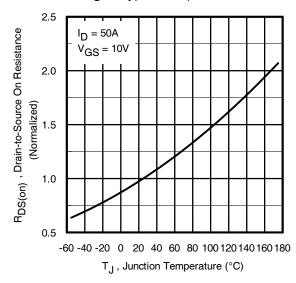

Fig. 4 Normalized On-Resistance vs. Temperature

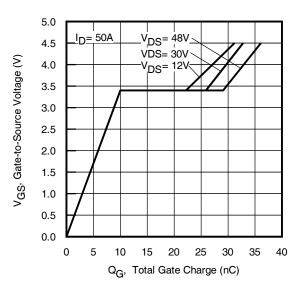

Fig 6. Typical Gate Charge vs. Gate-to-Source Voltage

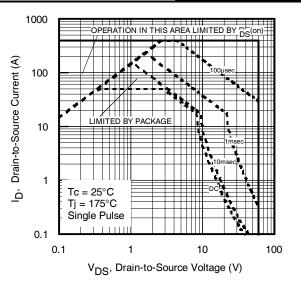

Fig 8. Maximum Safe Operating Area

Fig 10. Drain-to-Source Breakdown Voltage

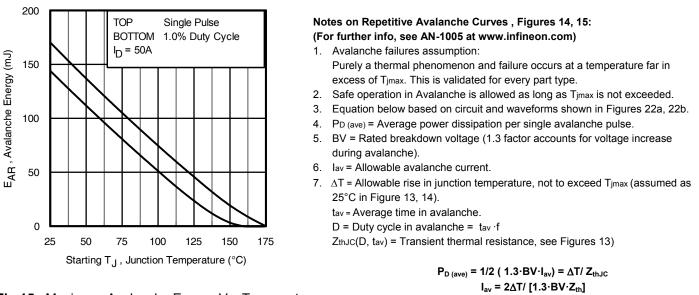

Fig 12. Maximum Avalanche Energy vs. Drain Current

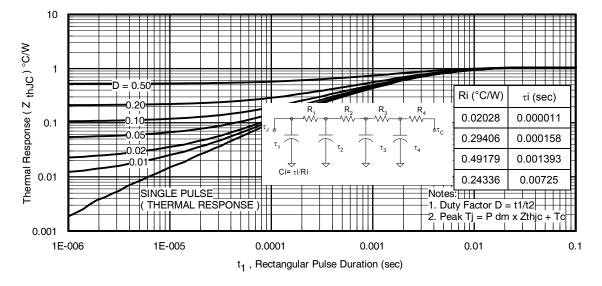

Fig 13. Maximum Effective Transient Thermal Impedance, Junction-to-Case

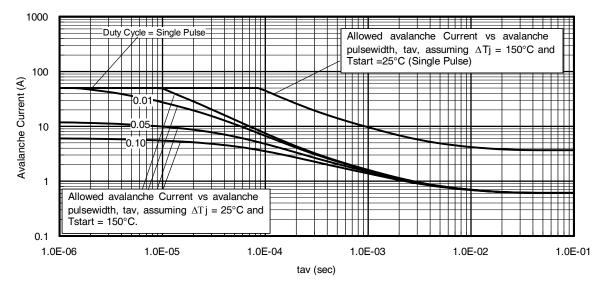

Fig 14. Typical Avalanche Current Vs. Pulse width

Fig 15. Maximum Avalanche Energy Vs. Temperature

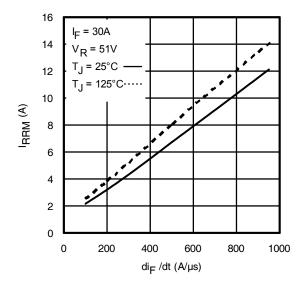

Fig. 18 - Typical Recovery Current vs. dif/dt

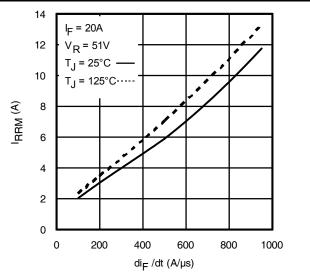

Fig. 17 - Typical Recovery Current vs. dif/dt

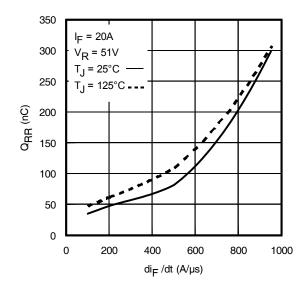

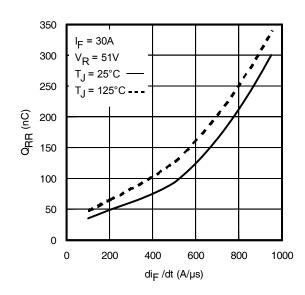

Fig. 19 - Typical Stored Charge vs. dif/dt

Fig. 20 - Typical Stored Charge vs. dif/dt

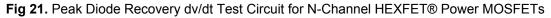

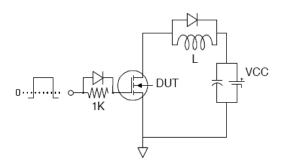

Fig 22a. Unclamped Inductive Test Circuit

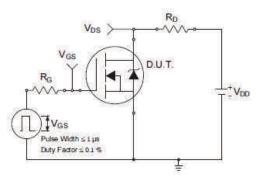

Fig 23a. Switching Time Test Circuit

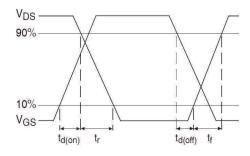

## Fig 22b. Unclamped Inductive Waveforms

Fig 23b. Switching Time Waveforms

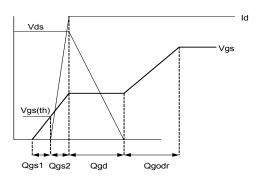

Fig 24b. Gate Charge Waveform

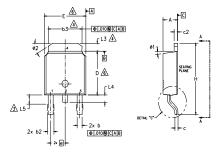

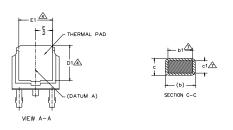

## D-Pak (TO-252AA) Package Outline (Dimensions are shown in millimeters (inches))

| NOTES: |

|--------|

|--------|

- 1.- DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994

- 2.- DIMENSION ARE SHOWN IN INCHES [MILLIMETERS].

- A- LEAD DIMENSION UNCONTROLLED IN L5.

- A- DIMENSION D1, E1, L3 & 63 ESTABLISH A MINIMUM MOUNTING SURFACE FOR THERMAL PAD.

- 5.- SECTION C-C DIMENSIONS APPLY TO THE FLAT SECTION OF THE LEAD BETWEEN .005 AND 0.10 [0.13 AND 0.25] FROM THE LEAD TIP.

- ▲ DIMENSION D & E DO NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED .005 [0.13] PER SIDE. THESE DIMENSIONS ARE MEASURED AT THE OUTMOST EXTREMES OF THE PLASTIC BODY.

- A- DIMENSION 61 & c1 APPLIED TO BASE METAL ONLY.

- $\underline{\&}$  DATUM A & B TO BE DETERMINED AT DATUM PLANE H. 9.- OUTLINE CONFORMS TO JEDEC OUTLINE TO-252AA.

| S<br>Y<br>M |        | N<br>O<br>T |          |        |   |  |  |

|-------------|--------|-------------|----------|--------|---|--|--|

| В           | MILLIM | ETERS       | INC      | INCHES |   |  |  |

| 0<br>L      | MIN.   | MAX.        | MIN.     | MAX.   | Ê |  |  |

| A           | 2.18   | 2.39        | .086     | .094   |   |  |  |

| A1          | -      | 0.13        | -        | .005   |   |  |  |

| b           | 0.64   | 0.89        | .025     | .035   |   |  |  |

| ь1          | 0.65   | 0.79        | .025     | .031   | 7 |  |  |

| b2          | 0.76   | 1.14        | .030     | .045   |   |  |  |

| b3          | 4.95   | 5.46        | .195     | .215   | 4 |  |  |

| с           | 0.46   | 0.61        | .018     | .024   |   |  |  |

| c1          | 0.41   | 0.56        | .016     | .022   | 7 |  |  |

| c2          | 0.46   | 0.89        | .018     | .035   |   |  |  |

| D           | 5.97   | 6.22        | .235     | .245   | 6 |  |  |

| D1          | 5.21   | -           | .205     | -      | 4 |  |  |

| Е           | 6.35   | 6.73        | .250     | .265   | 6 |  |  |

| E1          | 4.32   | -           | .170     | -      | 4 |  |  |

| е           | 2.29   | BSC         | .090     | BSC    |   |  |  |

| Н           | 9.40   | 10.41       | .370     | .410   |   |  |  |

| L           | 1.40   | 1.78        | .055     | .070   |   |  |  |

| L1          | 2.74   | BSC         | .108     | REF.   |   |  |  |

| L2          | 0.51   | BSC         | .020 BSC |        |   |  |  |

| L3          | 0.89   | 1.27        | .035     | .050   | 4 |  |  |

| L4          | -      | 1.02        | -        | .040   |   |  |  |

| L5          | 1.14   | 1.52        | .045     | .060   | 3 |  |  |

| ø           | 0.     | 10*         | 0.       | 10*    |   |  |  |

| ø1          | 0*     | 15 <b>°</b> | 0.       | 15°    |   |  |  |

| ø2          | 25'    | 35°         | 25*      | 35*    |   |  |  |

#### LEAD ASSIGNMENTS

<u>HEXFET</u>

1.- GATE 2.- DRAIN 3.- SOURCE 4.- DRAIN

#### IGBT & CoPAK

1.- GATE

2.- COLLECTOR 3.- EMITTER

4.- COLLECTOR

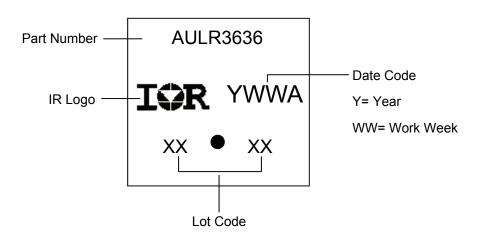

## D-Pak (TO-252AA) Part Marking Information

Note: For the most current drawing please refer to IR website at http://www.irf.com/package/

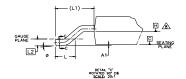

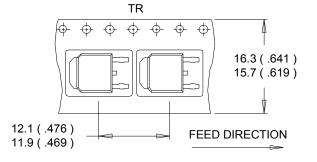

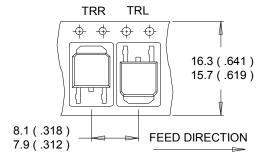

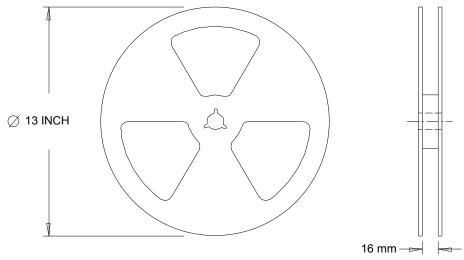

## D-Pak (TO-252AA) Tape & Reel Information (Dimensions are shown in millimeters (inches))

### NOTES :

- 1. CONTROLLING DIMENSION : MILLIMETER.

- 2. ALL DIMENSIONS ARE SHOWN IN MILLIMETERS ( INCHES ).

- 3. OUTLINE CONFORMS TO EIA-481 & EIA-541.

#### NOTES : 1. OUTLINE CONFORMS TO EIA-481.

Note: For the most current drawing please refer to IR website at http://www.irf.com/package/

### **Qualification Information**

|                            |                      | Automotive                                                                                                                                                                    |                |  |  |  |  |

|----------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|

|                            |                      |                                                                                                                                                                               | (per AEC-Q101) |  |  |  |  |

|                            |                      | Comments: This part number(s) passed Automotive qualification. Infineon's Industrial and Consumer qualification level is granted by extension of the higher Automotive level. |                |  |  |  |  |

| Moisture Sensitivity Level |                      | D-Pak                                                                                                                                                                         | MSL1           |  |  |  |  |

|                            | Machine Model        | Class M4 (+/- 600V) <sup>†</sup>                                                                                                                                              |                |  |  |  |  |

|                            |                      | AEC-Q101-002                                                                                                                                                                  |                |  |  |  |  |

|                            | Liuman Dady Madal    | Class H1C (+/- 2000V) <sup>†</sup>                                                                                                                                            |                |  |  |  |  |

| ESD                        | Human Body Model     | AEC-Q101-001                                                                                                                                                                  |                |  |  |  |  |

|                            | Charged Device Model | Class C5 (+/- 2000V) <sup>†</sup>                                                                                                                                             |                |  |  |  |  |

|                            |                      | AEC-Q101-005                                                                                                                                                                  |                |  |  |  |  |

| RoHS Compliant             |                      |                                                                                                                                                                               | Yes            |  |  |  |  |

† Highest passing voltage.

### **Revision History**

| Date      | Comments                                                                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3/18/2014 | <ul> <li>Added "Logic Level Gate Drive" bullet in the features section on page 1</li> <li>Updated data sheet with new IR corporate template</li> </ul> |

| 4/9/2014  | <ul> <li>Updated package outline on page 8.</li> <li>Updated typo on the fig.19 and fig.20, unit of y-axis from "A" to "nC" on page 6.</li> </ul>      |

| 11/4/2015 | <ul> <li>Updated datasheet with corporate template</li> <li>Corrected ordering table on page 1.</li> </ul>                                             |

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2015 All Rights Reserved.

### **IMPORTANT NOTICE**

The information given in this document shall in <u>no event</u> be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<u>www.infineon.com</u>).

## WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may <u>not</u> be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.