| Pin #         | Name                 | Туре   | Description                                                                                                                     |

|---------------|----------------------|--------|---------------------------------------------------------------------------------------------------------------------------------|

| 1             | V <sub>DD</sub>      | Power  | Core Power Supply                                                                                                               |

| 2             | CLK_SEL              | Input  | Clock select input. When high, selects CLK1 input. When low, selects CLK0 input. LVCMOS/LVTTL level with $50k\Omega$ pull down. |

| 3             | CLK0                 | Input  | Differential clock input with pull-down                                                                                         |

| 4             | /CLK0                | Input  | Inverting differential clock input. Defaults to V <sub>DD</sub> /2 if left floating.                                            |

| 5             | V <sub>BB</sub> (NC) | Power  | Internal Common Mode Voltage, can be left as not connected if unused.                                                           |

| 6             | CLK1                 | Input  | Differential clock input with pull-down                                                                                         |

| 7             | /CLK1                | Input  | Inverting differential clock input. Defaults to VDD/2 if left floating.                                                         |

| 8             | V <sub>EE</sub>      | Power  | Connect to negative power supply                                                                                                |

| 9, 16, 25, 32 | V <sub>DDO</sub>     | Power  | Output Power pin                                                                                                                |

| 11, 10        | Q9, /Q9              | Output | Differential output pair, LVPECL interface level.                                                                               |

| 13,12         | Q8, /Q8              | Output | Differential output pair, LVPECL interface level.                                                                               |

| 15,14         | Q7, /Q7              | Output | Differential output pair, LVPECL interface level.                                                                               |

| 18,17         | Q6, /Q6              | Output | Differential output pair, LVPECL interface level.                                                                               |

| 20,19         | Q5, /Q5              | Output | Differential output pair, LVPECL interface level.                                                                               |

| 22,21         | Q4, /Q4              | Output | Differential output pair, LVPECL interface level.                                                                               |

| 24, 23        | Q3, /Q3              | Output | Differential output pair, LVPECL interface level.                                                                               |

| 27,26         | Q2, /Q2              | Output | Differential output pair, LVPECL interface level.                                                                               |

| 29,28         | Q1, /Q1              | Output | Differential output pair, LVPECL interface level.                                                                               |

| 31,30         | Q0, /Q0              | Output | Differential output pair, LVPECL interface level.                                                                               |

# Pin Description<sup>(1)</sup>

#### Note:

1. I = Input, O = Output, P = Power supply connection.

## **Control Input Function Table**

| CLK_SEL | Outputs |

|---------|---------|

| 0       | CLK0    |

| 1       | CLK1    |

2

| Absolute | Maximum | Ratings <sup>(1)</sup> |

|----------|---------|------------------------|

|----------|---------|------------------------|

| Symbol           | Parameter                            | Conditions        | Min  | Тур | Max            | Units |

|------------------|--------------------------------------|-------------------|------|-----|----------------|-------|

| V <sub>DD</sub>  | Supply voltage                       | Referenced to GND |      |     | 4.6            | V     |

| V <sub>IN</sub>  | Input voltage                        | Referenced to GND | -0.5 |     | $V_{DD}$ +0.5V | V     |

| IOUT             | Surge Current                        |                   |      |     | 100            | mA    |

| T <sub>STG</sub> | Storage temperature                  |                   | -55  |     | 150            | °C    |

| V <sub>BB</sub>  | Sink/source Current, I <sub>BB</sub> |                   | -0.5 |     | +0.5           | mA    |

| Тј               | Junction Temperature                 |                   |      |     | 125            | °C    |

Note:

1. Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These ratings are stress specifications only and correct functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

# **Operating Conditions**

| Symbol           | Parameter                   | Conditions                  | Min   | Тур | Max | Units |

|------------------|-----------------------------|-----------------------------|-------|-----|-----|-------|

| V <sub>DD</sub>  | Core Power Supply Voltage   |                             | 2.375 |     | 3.6 | V     |

| V <sub>DDO</sub> | Output Power Supply Voltage |                             | 2.375 |     | 3.6 | V     |

| T <sub>A</sub>   | Ambient Temperature         |                             | -40   |     | 85  | °C    |

| I <sub>DD</sub>  | Core Power Supply Current   |                             |       | 70  | 95  |       |

| I <sub>DDO</sub> | Output Power Supply Current | All LVPECL outputs unloaded |       | 110 | 200 | mA    |

## **LVCMOS/LVTTL DC Characteristics** (TA = -40°C to +85°C, VDD = $3.3V \pm 10\%$ , VDDO = $2.5V \pm 5\%$ to 3.3V

±10%)

| Symbol          | Parameter                |          | Conditions                   | Min  | Тур | Max                  | Units |

|-----------------|--------------------------|----------|------------------------------|------|-----|----------------------|-------|

| V <sub>IH</sub> | Input High Voltage       | CLK_SEL  |                              | 1.7  |     | V <sub>DD</sub> +0.3 | V     |

| V <sub>IL</sub> | Input Low Voltage        | CLK_SEL  |                              | -0.3 |     |                      | v     |

| I <sub>IH</sub> | Input High Current       | CLK_SEL  | $V_{IN} = V_{DD} = 3.6V$     |      |     | 150                  | μΑ    |

| I <sub>IL</sub> | Input Low Current        | CLK_SEL  | $V_{IN} = 0V, V_{DD} = 3.6V$ | -150 |     |                      | μΑ    |

| R               | Input Pullup/Pulldown Re | sistance |                              |      | 50  |                      | kΩ    |

| Symbol           | Parameter                                |                 | Conditions                              | Min                       | Тур                   | Max                   | Units |

|------------------|------------------------------------------|-----------------|-----------------------------------------|---------------------------|-----------------------|-----------------------|-------|

| т                | Input High                               | CLK0, CLK1      | $V_{IN} = V_{DD} = 3.6V$                |                           |                       | 150                   | μA    |

| I <sub>IH</sub>  | Current                                  | /CLK0, /CLK1    | $V_{IN} = V_{DD} = 3.6V$                |                           |                       | 150                   | μΑ    |

| I                | Input Low Cur-                           | CLK0, CLK1      | $V_{DD} = 3.6V, V_{IN} = 0V$            | -150                      |                       |                       | μΑ    |

| I <sub>IL</sub>  | rent                                     | /CLK0, /CLK1    | $V_{DD} = 3.6V, V_{IN} = 0V$            | -150                      |                       |                       | μΑ    |

| V <sub>CMR</sub> | Common Mode Input Voltage <sup>(1)</sup> |                 |                                         | V <sub>EE</sub> +0.5      |                       | V <sub>DD</sub>       | V     |

| V <sub>OH</sub>  | Output High Voltage <sup>(2)</sup>       |                 | $V_{DDO} = 2.5 V \text{ or } 3.3 V$     | V <sub>DDO</sub> -<br>1.5 | V <sub>DDO</sub> -1.4 | V <sub>DDO</sub> -0.9 | V     |

| V <sub>OL</sub>  | Output Low Voltage <sup>(2)</sup>        |                 | $V_{\rm DDO} = 2.5 V \text{ or } 3.3 V$ | V <sub>DDO</sub> -<br>2.2 | V <sub>DDO</sub> -2.0 | V <sub>DDO</sub> -1.7 | V     |

| R                | Input Pullup/Pull                        | down Resistance |                                         |                           | 50                    |                       | kΩ    |

### **LVPECL DC Characteristics** (T<sub>A</sub> = -40°C to +85°C, $V_{DD}$ = 3.3V ±10%, $V_{DDO}$ = 2.5V ±5% to 3.3V ±10%)

#### Notes:

1. For single-ended applications, the maximum input voltage for CLK and /CLK is  $\mathrm{V_{DD}+0.3V}$

2. Outputs terminated with 50  $\Omega$  to  $V_{DD}\mbox{-}2.0V$

### **AC Characteristics** ( $T_A = -40^{\circ}C$ to $+85^{\circ}C$ , $V_{DD} = 3.3V \pm 10\%$ , $V_{DDO} = 2.5V \pm 5\%$ to $3.3V \pm 10\%$ )

| Symbol                         | Parameter                            | Conditions                                                                                                            | Min | Тур  | Max  | Units |

|--------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|------|------|-------|

| f <sub>max</sub>               | Output Frequency                     |                                                                                                                       |     |      | 1500 | MHz   |

| t <sub>pd</sub>                | Propagation Delay <sup>(1)</sup>     |                                                                                                                       |     | 1200 |      | ps    |

| Tsk                            | Output-to-output Skew <sup>(2)</sup> |                                                                                                                       |     | 40   |      | ps    |

| t <sub>r</sub> /t <sub>f</sub> | Output Rise/Fall time                | 20% - 80%                                                                                                             |     | 150  |      | ps    |

| t <sub>odc</sub>               | Output duty cycle                    | f ≤ 650 MHz                                                                                                           | 48  |      | 52   | %     |

| V <sub>PP</sub>                | Output Swing                         | LVPECL outputs                                                                                                        | 0.6 | 1.0  |      | V     |

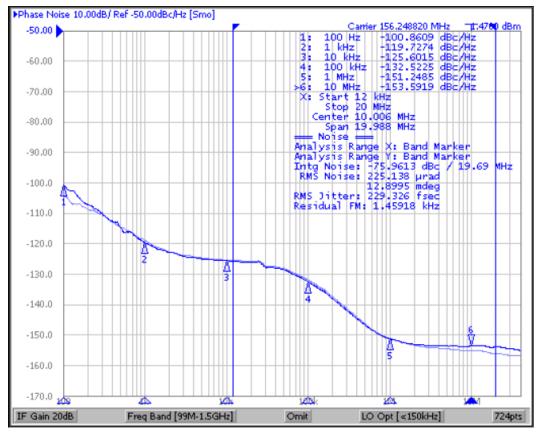

| tj                             | Buffer additive jitter RMS           | 156.25MHz (12KHz-<br>20MHz integration range)<br>Input condition per Phase<br>Noise and Additive Jitter<br>Plot below |     | 0.03 | 0.05 | ps    |

#### Notes:

1. Measured from the differential input to the differential output crossing point

2. Defined as skew between outputs at the same supply voltage and with equal loads. Measured at the output differential crossing point

# **Phase Noise and Additive Jitter**

Output phase noise (Dark Blue) vs Input Phase noise (light blue) Additive jitter is calculated at ~27fs RMS (12kHz to 20MHz). Additive jitter =  $\sqrt{(Output jitter^2 - Input jitter^2)}$

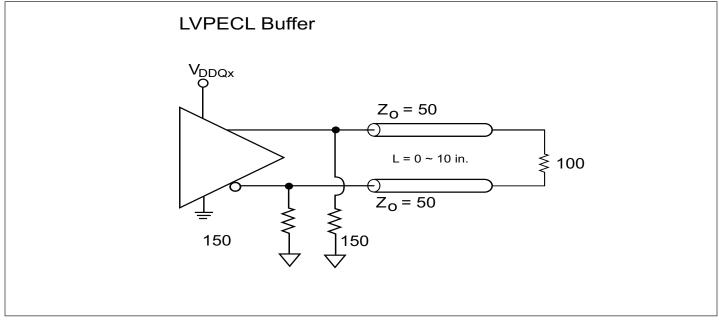

## **Configuration Test Load Board Termination for LVPECL Outputs**

# **Application Information**

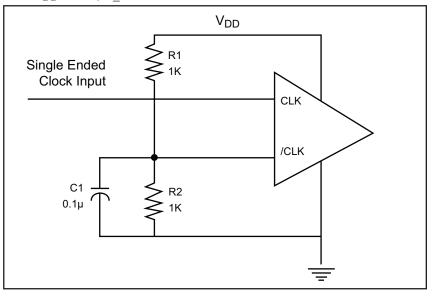

#### Wiring the differential input to accept single ended levels

Figure 1 shows how the differential input can be wired to accept single ended levels. The reference voltage  $V_REF = V_{DD}/2$  is generated by the bias resistors R1, R2 and C1. This bias circuit should be located as close as possible to the input pin. The ratio of R1 and R2 might need to be adjusted to postion the V\_REF in the center of the input voltage swing. For example, if the input clock swing is only 2.5V and  $V_{DD} = 3.3V$ , V\_REF should be 1.25V and R1/R2 = 0.609.

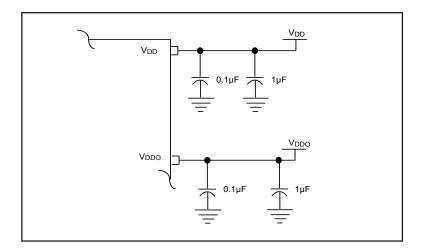

## **Power Supply Filtering Techniques**

As in any high speed analog circuitry, the power supply pins are vulnerable to random noise. To achieve optimum jitter performance, power supply isolation is required. All power pins should be individually connected to the power supply plane through vias, and 0.1µF an 1µF bypass capacitors should be used for each pin.

## **PI6C4911510** 2.5V/3.3V 1.5GHz Low Skew 1-to-10 Differential to LVPECL Fanout Buffer w/ 2 to 1 Differential Clock Input Mux

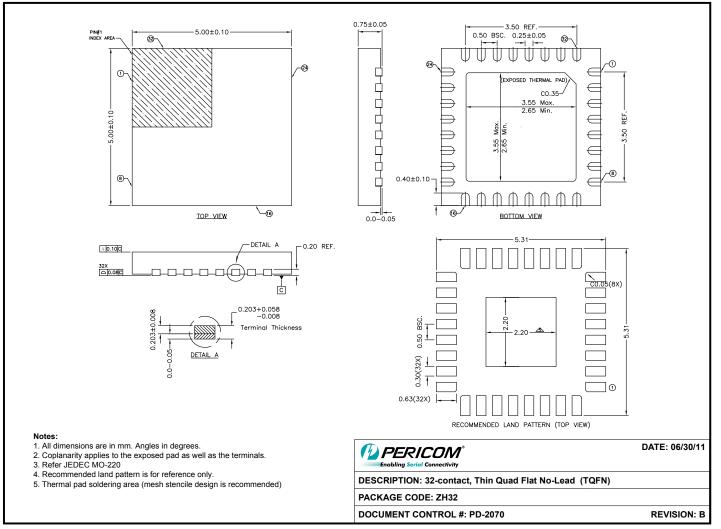

# Packaging Mechanical: 32-pin QFN (ZH)

11-0147

#### **Thermal Information**

| Symbol                 | Description                            | Condition |            |

|------------------------|----------------------------------------|-----------|------------|

| $\Theta_{\mathrm{JA}}$ | Junction-to-ambient thermal resistance | Still air | 44.70 °C/W |

| Θ <sub>JC</sub>        | Junction-to-case thermal resistance    |           | 21.70 °C/W |

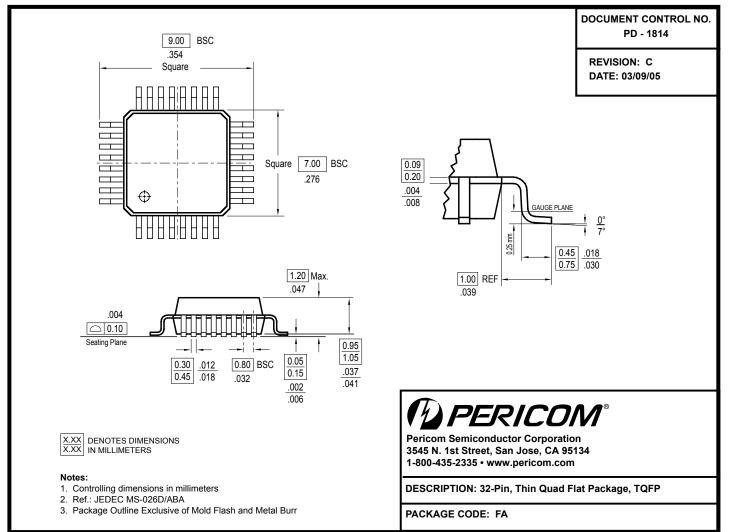

### **PI6C4911510** 2.5V/3.3V 1.5GHz Low Skew 1-to-10 Differential to LVPECL Fanout Buffer w/ 2 to 1 Differential Clock Input Mux

## Packaging Mechanical: 32-pin TQFP (FA)

#### **Thermal Information**

| Symbol          | Description                            | Condition |           |

|-----------------|----------------------------------------|-----------|-----------|

| Θ <sub>JA</sub> | Junction-to-ambient thermal resistance | Still air | 86 °C/W   |

| Θ <sub>JC</sub> | Junction-to-case thermal resistance    |           | 12.7 °C/W |

Downloaded from Arrow.com.

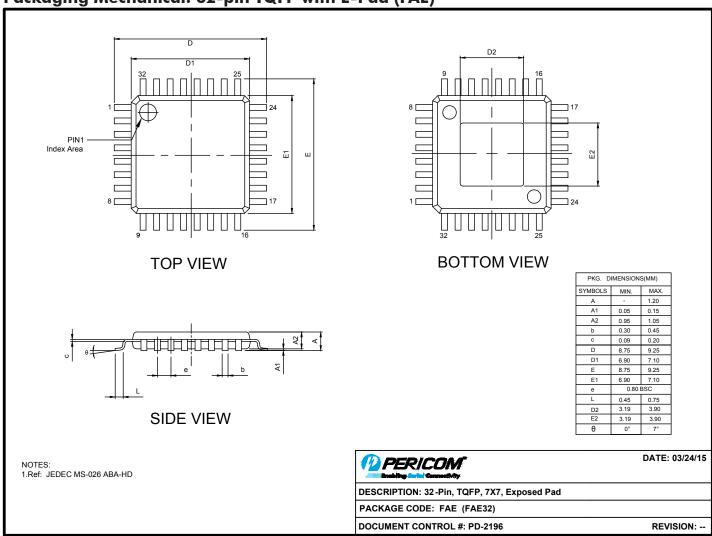

## Packaging Mechanical: 32-pin TQFP with E-Pad (FAE)

### **Thermal Information**

| Symbol          | Description                            | Condition |         |

|-----------------|----------------------------------------|-----------|---------|

| Θ <sub>JA</sub> | Junction-to-ambient thermal resistance | Still air | 45 °C/W |

| Θ <sub>JC</sub> | Junction-to-case thermal resistance    |           | 15 °C/W |

# Ordering Information<sup>(1,2,3)</sup>

| Ordering Code     | Package Code | Package Description                             |

|-------------------|--------------|-------------------------------------------------|

| PI6C4911510ZHIE   | ZH           | Pb-free & Green, 32-pin QFN                     |

| PI6C4911510ZHIEX  | ZH           | Pb-free & Green, 32-pin QFN, Tape & Reel        |

| PI6C4911510FAIE   | FA           | Pb-free & Green, 32-pin TQFP                    |

| PI6C4911510FAIEX  | FA           | Pb-free & Green, 32-pin TQFP, Tape & Reel       |

| PI6C4911510FAEIE  | FAE          | Pb-free & Green, 32-pin TQFP E-Pad              |

| PI6C4911510FAEIEX | FAE          | Pb-free & Green, 32-pin TQFP E-Pad, Tape & Reel |

#### Notes:

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

2. E = Pb-free & Green

3. X suffix = Tape/Reel

Pericom Semiconductor Corporation • 1-800-435-2336 • www.pericom.com