#### ■ Ports

• I/O ports

• Reset pin

Ports whose input/output can be specified in 1-bit units: 34 (P00 to P07, P10 to P17, P20 to P25, P30 to P34,

P70 to P73, PWM0, PWM1, XT2)

• USB ports 4 (UHAD+, UHAD-, UHBD+, UHBD-)

Dedicated oscillator ports

Input-only port (also used for the oscillator)

2 (CF1, CF2)

1 (XT1)

• Power supply pins 6 (VSS1 to 3, VDD1 to 3)

#### ■Timers

• Timer 0: 16-bit timer/counter with 2 capture registers

Mode 0: 8-bit timer with an 8-bit programmable prescaler

(with two 8-bit capture registers)  $\times$  2 channels

Mode 1: 8-bit timer with an 8-bit programmable prescaler

(with two 8-bit capture registers) + 8-bit counter (with two 8-bit capture registers)

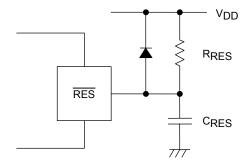

$1 (\overline{RES})$

Mode 2: 16-bit timer with an 8-bit programmable prescaler (with two 16-bit capture registers)

Mode 3: 16-bit counter (with two 16-bit capture registers)

• Timer 1: 16-bit timer/counter that supports PWM/toggle output

Mode 0: 8-bit timer with an 8-bit prescaler (with toggle output)

+ 8-bit timer/counter with an 8-bit prescaler (with toggle output)

Mode 1: 8-bit PWM with an 8-bit prescaler × 2 channels

Mode 2: 16-bit timer/counter with an 8-bit prescaler (with toggle output)

(Toggle output also possible from low-order 8 bits.)

Mode 3: 16-bit timer with an 8-bit prescaler (with toggle output)

(Low-order 8 bits can be used as a PWM output.)

- Timer 4: 8-bit timer with a 6-bit prescaler

- Timer 5: 8-bit timer with a 6-bit prescaler

- Timer 6: 8-bit timer with a 6-bit prescaler (with toggle output)

- Timer 7: 8-bit timer with a 6-bit prescaler (with toggle output)

- Base timer

- 1) The clock can be selected from among a subclock (32.768kHz crystal oscillator), low-speed RC oscillator clock, system clock, and timer 0 prescaler output.

- 2) Interrupts programmable in 5 different time schemes.

#### ■ Serial Interfaces

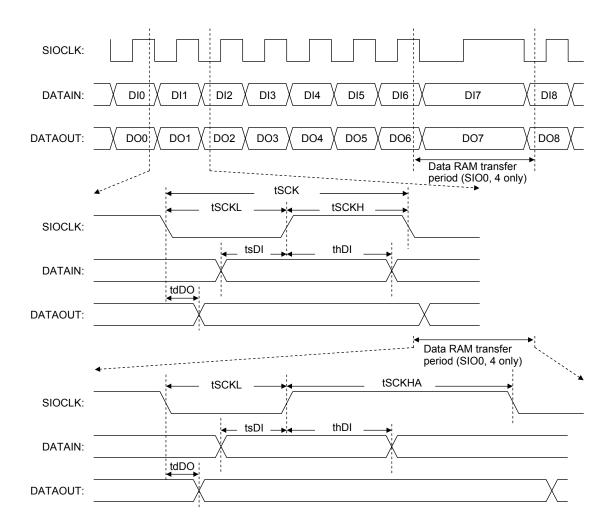

- SIO0: Synchronous serial interface

- 1) LSB first/MSB first selectable

- 2) Transfer clock cycle: 4/3 to 512/3 tCYC

- 3) Continuous automatic data transmission (1 to 256 bits can be specified in 1-bit units) (Suspension and resumption of data transfer possible in 1-byte units)

- SIO1: 8-bit asynchronous/synchronous serial interface

- Mode 0: Synchronous 8-bit serial I/O (2- or 3-wire configuration, 2 to 512 tCYC transfer clock)

- Mode 1: Asynchronous serial I/O (half-duplex, 8 data bits, 1 stop bit, 8 to 2048 tCYC baudrate)

- Mode 2: Bus mode 1 (start bit, 8 data bits, 2 to 512 tCYC transfer clock)

- Mode 3: Bus mode 2 (start detection, 8 data bits, stop detection)

- SIO4: Synchronous serial interface

- 1) LSB first/MSB first selectable

- 2) Transfer clock cycle: 4/3 to 1020/3 tCYC

- 3) Continuous automatic data transmission (1 to 8192 bytes can be specified in 1-byte units) (Suspension and resumption of data transmission possible in 1-byte units or in word units)

- 4) Clock polarity can be selected.

- 5) CRC16 calculator circuit built- in

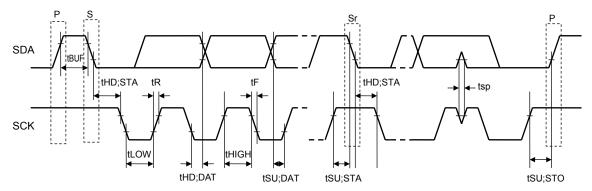

- SMIIC0: Single-master I<sup>2</sup>C/8-bit synchronous SIO

- Mode 0: Communication in single-master mode.

- Mode 1: 8-bit synchronous serial I/O (data MSB first)

#### ■Full Duplex UART

1) Data length: 7/8/9 bits selectable

2) Stop bits: 1 bit (2 bits in continuous transmission mode)

3) Parity bits: None/even/odd selectable (for 8-bit data only)

4) Baudrate: 16/3 to 8192/3 tCYC

$\blacksquare$ AD Converter: 12 bits  $\times$  12 channels

$\blacksquare$ PWM: Variable frequency 12-bit PWM × 2 channels

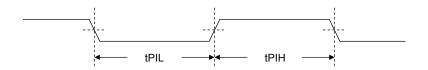

#### ■Infrared Remote Control Receiver Circuit

- 1) Noise rejection function (noise filter time constant: Approx. 120µs when the 32.768kHz crystal oscillator is selected as the reference clock)

- 2) Supports data encoding systems such as PPM (Pulse Position Modulation) and Manchester encoding.

- 3) X'tal HOLD mode release function

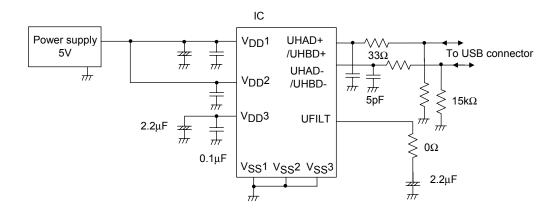

### ■USB Interface (host control function) × 2 ports

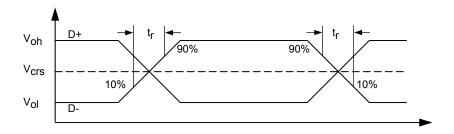

- 1) Supports full-speed (12Mbps) and low-speed (1.5Mbps) specifications.

- 2) Supports four transfer types (control transfer, bulk transfer, interrupt transfer, and isochronous transfer).

#### ■Audio Interface

1) Sampling frequencies (fs): 8kHz/11.025kHz/12kHz/16kHz/22.05kHz/24kHz/32kHz/44.1kHz/48kHz

2) Master clock: 256fs/384fs3) Bit clock: 48fs/64fs

4) Data bit length: 16bits/18bits/20bits/24bits

5) LSB first/MSB first selectable.

6) Left justified/right justified/I2S format selectable

#### ■Watchdog Timer

- External RC time constant type

- 1) Interrupt generation/reset generation selectable

- 2) Operation in HALT/HOLD mode can be selected from "continue operation" and "suspend operation."

- Internal timer type

- 1) Capable of generating a internal reset signal on an overflow of the timer running on the low-speed RC oscillator clock, or subclock.

- 2) Operation in HALT/HOLD mode can be selected from among "continue count operation," "suspend operation," and "retain the count value."

### ■Clock Output Function

- 1) Can output a clock with a clock rate of 1/1, 1/2, 1/4, 1/8, 1/16, 1/32, or 1/64 of the source oscillator clock selected as the system clock.

- 2) Can output the source oscillator clock for the subclock.

#### **■**Interrupts

- 44 sources, 10 vectors

- 1) Provides three levels (low (L), high (H), and highest (X)) of multiplex interrupt control. Any interrupt request of the level equal to or lower than the current interrupt level is not accepted.

- 2) When interrupt requests to two or more vector addresses occur at the same time, the interrupt of the highest level takes precedence over the other interrupts. For interrupts of the same level, the interrupt into the lowest vector address is given priority.

| No. | Vector | Level  | Interrupt Source                                                            |

|-----|--------|--------|-----------------------------------------------------------------------------|

| 1   | 00003H | X or L | INTO                                                                        |

| 2   | 0000BH | X or L | INT1                                                                        |

| 3   | 00013H | H or L | INT2/T0L/INT4/UHC-A bus active/UHC-B bus active/remote control receive      |

| 4   | 0001BH | H or L | INT3/INT5/base timer                                                        |

| 5   | 00023H | H or L | T0H/INT6/UHC-A device connected, disconnected, resumed                      |

| 6   | 0002BH | H or L | T1L/T1H/INT7/AIF start/SMIIC0/UHC-B device connected, disconnected, resumed |

| 7   | 00033H | H or L | SIO0/UART1 reception completed                                              |

| 8   | 0003BH | H or L | SIO1/SIO4/UART1 buffer empty/UART1 transmission completed/AIF end           |

| 9   | 00043H | H or L | ADC/T6/T7/UHC-ACK/UHC-NAK/UHC error/UHC-STALL                               |

| 10  | 0004BH | H or L | Port 0/PWM0/PWM1/T4/T5/UHC-SOF                                              |

- Priority levels X > H > L

- When interrupts of the same level occur at the same time, the interrupt with the lowest vector address is given priority.

- Subroutine Stack Levels: Up to 4096 levels (The stack is allocated in RAM.)

- High-speed Multiplication/Division Instructions

16 bits × 8 bits

24 bits × 16 bits

16 bits ÷ 8 bits

24 bits ÷ 16 bits

(12 tCYC execution time)

(8 tCYC execution time)

24 bits ÷ 16 bits

(12 tCYC execution time)

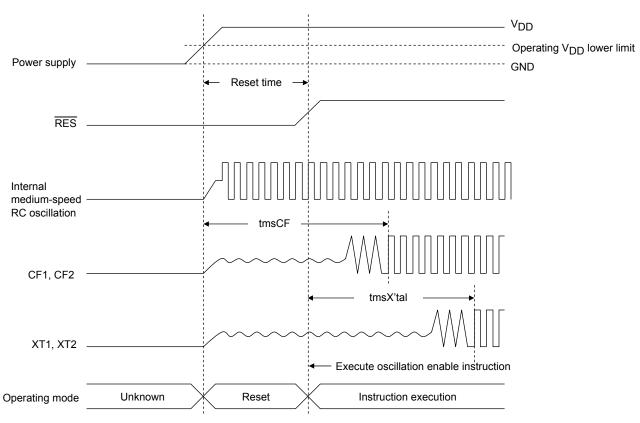

#### ■Oscillator Circuit and PLL

• Medium-speed RC oscillator circuit (internal): For system clock (approx. 1MHz)

• Low-speed RC oscillator circuit (internal): For system clock, timer, and watchdog timer (approx. 30kHz)

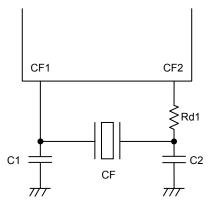

• CF oscillator circuit: For system clock

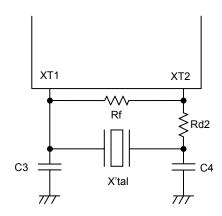

• Crystal oscillator circuit: For system clock and time-of-day clock

• PLL circuit (internal): For USB interface (see Fig. 5) and audio interface (see Fig. 6)

#### ■Internal Reset Functions

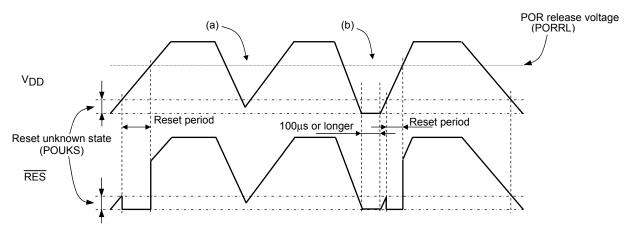

- Power-on reset (POR) function

- 1) POR is activated at power-on.

- 2) POR release voltage can be selected from 8 levels (1.67V, 1.97V, 2.07V, 2.37V, 2.57V, 2.87V, 3.86V, and 4.35V) by setting options.

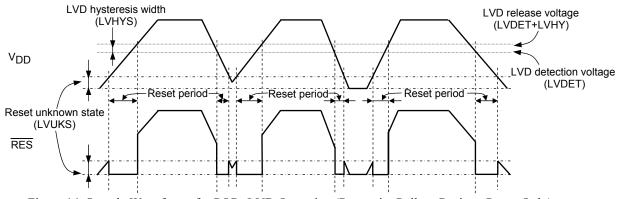

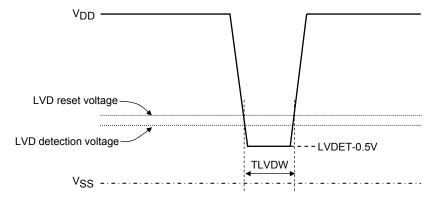

- Low voltage detection reset (LVD) function

- 1) LVD and POR functions are combined to generate resets when power is turned on and when power voltage falls below a threshold level.

- 2) The use/disuse of the LVD function and the low voltage threshold level (7 levels: 1.91V, 2.01V, 2.31V, 2.51V, 2.81V, 3.79V, and 4.28V) can be selected by setting options.

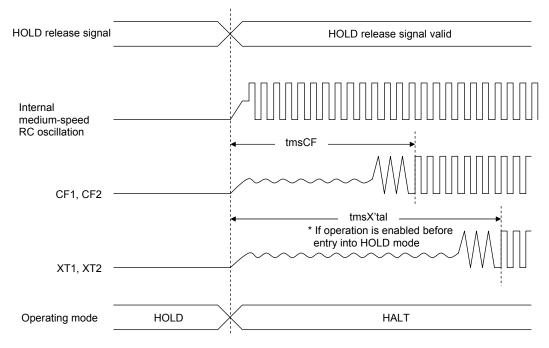

#### ■Standby Function

- HALT mode: Halts instruction execution while allowing the peripheral circuits to continue operation.

- 1) Oscillators do not stop automatically.

- 2) There are three ways of releasing HOLD mode.

- (1) Setting the reset pin to a low level.

- (2) Generating a reset signal by watchdog timer or low-voltage detection

- (3) Occurrence of an interrupt

- HOLD mode: Suspends instruction execution and operation of the peripheral circuits.

- 1) The PLL, CF, RC and crystal oscillators automatically stop operation.

Note: Low-speed RC oscillator is controlled directly by the watchdog timer and its oscillation in standby mode is also controlled.

- 2) There are five ways of releasing HOLD mode.

- (1) Setting the reset pin to a low level

- (2) Generating a reset signal by the watchdog timer or low-voltage detection

- (3) Establishing an interrupt source at one of INT0, INT1, INT2, INT4, and INT5 pins

- \* INTO and INT1 HOLD mode release is available only when level detection is configured.

- (4) Establishing an interrupt source at port 0

- (5) Establishing an bus active interrupt source in the USB host control circuit

- X'tal HOLD mode: Suspends instruction execution and the operation of the peripheral circuits except the base timer and infrared remote control receiver circuit.

- 1) The PLL, CF and RC oscillators automatically stop operation.

Note: Low-speed RC oscillator is controlled directly by the watchdog timer and its oscillation in standby mode is also controlled.

Note: The low-speed RC oscillator retains the state that is established on entry into X'tal HOLD mode if the base timer is running with the low-speed RC oscillator selected as the base timer input clock source.

- 2) The state of crystal oscillator established when the X'tal HOLD mode is entered is retained.

- 3) There are seven ways of releasing X'tal HOLD mode.

- (1) Setting the reset pin to a low level

- (2) Generating a reset signal by the watchdog timer or low-voltage detection

- (3) Establishing an interrupt source at one of INT0, INT1, INT2, INT4, and INT5 pins

- \* INT0 and INT1 X'tal HOLD mode release is available only when level detection is configured.

- (4) Establishing an interrupt source at port 0

- (5) Establishing an interrupt source in the base timer circuit

- (6) Establishing an interrupt source in the infrared remote control receiver circuit

- (7) Establishing an bus active interrupt source in the USB host control circuit

#### ■ Development Tools

• On-chip debugger: TCB87–Type B + LC87F1K64A or

TCB87-Type C (3-wire communication cable) + LC87F1K64A

### ■Flash ROM Programming Board

| Package      | Programming Board |

|--------------|-------------------|

| SQFP48 (7×7) | W87F55256SQ       |

■Flash ROM Programmer

| Maker                                |               | Model                           | Supported Version   | Device     |  |

|--------------------------------------|---------------|---------------------------------|---------------------|------------|--|

| Flash Support Group<br>Company (FSG) | Single        | AF9709C                         | Rev.03.32 and later | 87F064JU   |  |

| Flash Support Group                  |               | AF9101/AF9103 (main unit)       |                     |            |  |

| Company (FSG)                        | Onboard       | (FSG model)                     | (Nata 0)            | LC87F1K64A |  |

| +                                    | single/ganged | SIB87 Type C (interface driver) | (Note 2)            | LC87F1K64A |  |

| Our company (Note 1)                 |               | (Our company model)             |                     |            |  |

|                                      | Cingle/genged | SKK/SKK Type C                  |                     |            |  |

| Company (FSG)                        | Single/ganged | (SANYO FWS)                     | 1.07 and later      | LC87F1K64  |  |

|                                      | Onboard       | SKK-DBG Type C                  | Chip data version   | LCO/FIN04  |  |

|                                      | single/ganged | (SANYO FWS)                     | 2.39 and later      |            |  |

(Further information on the AF series)

Flash Support Group Company (TOA ELECTRONICS, Inc.)

Phone: 053-459-1050 E-mail: sales@j- fsg.co.jp

Note 1: PC-less standalone onboard programming is possible using the FSG onboard programmer (AF9101/AF9103) and the serial interface driver (SIB87 Type C) provided by Our company in pair.

Note 2: Dedicated programming device and program are required depending on the programming conditions. Contact Our company or FSG if you have any questions or difficulties regarding this matter.

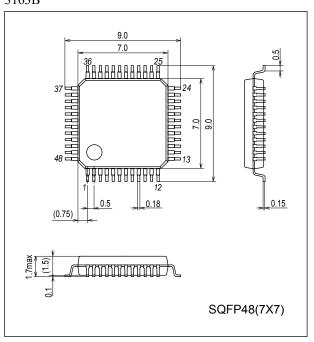

# **Package Dimensions**

unit : mm (typ) 3163B

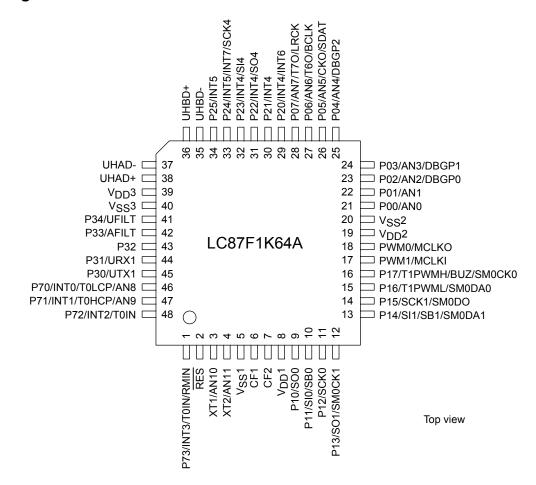

# **Pin Assignment**

SQFP48 (7×7) (Lead-/halogen-free product)

| SQFP48 | NAME                  |

|--------|-----------------------|

| 1      | P73/INT3/T0IN/RMIN    |

| 2      | RES                   |

| 3      | XT1/AN10              |

| 4      | XT2/AN11              |

| 5      | V <sub>SS</sub> 1     |

| 6      | CF1                   |

| 7      | CF2                   |

| 8      | V <sub>DD</sub> 1     |

| 9      | P10/SO0               |

| 10     | P11/SI0/SB0           |

| 11     | P12/SCK0              |

| 12     | P13/SO1/SM0CK1        |

| 13     | P14/SI1/SB1/SM0DA1    |

| 14     | P15/SCK1/SM0DO        |

| 15     | P16/T1PWML/SM0DA0     |

| 16     | P17/T1PWMH/BUZ/SM0CK0 |

| 17     | PWM1/MCLKI            |

| 18     | PWM0/MCLKO            |

| 19     | V <sub>DD</sub> 2     |

| 20     | V <sub>SS</sub> 2     |

| 21     | P00/AN0               |

| 22     | P01/AN1               |

| 23     | P02/AN2/DBGP0         |

| 24     | P03/AN3/DBGP1         |

| SQFP48 | NAME               |

|--------|--------------------|

| 25     | P04/AN4/DBGP2      |

| 26     | P05/AN5/CKO/SDAT   |

| 27     | P06/AN6/T6O/BCLK   |

| 28     | P07/AN7/T7O/LRCK   |

| 29     | P20/INT4/INT6      |

| 30     | P21/INT4           |

| 31     | P22/INT4/SO4       |

| 32     | P23/INT4/SI4       |

| 33     | P24/INT5/INT7/SCK4 |

| 34     | P25/INT5           |

| 35     | UHBD-              |

| 36     | UHBD+              |

| 37     | UHAD-              |

| 38     | UHAD+              |

| 39     | V <sub>DD</sub> 3  |

| 40     | V <sub>SS</sub> 3  |

| 41     | P34/UFILT          |

| 42     | P33/AFILT          |

| 43     | P32                |

| 44     | P31/URX1           |

| 45     | P30/UTX1           |

| 46     | P70/INT0/T0LCP/AN8 |

| 47     | P71/INT1/T0HCP/AN9 |

| 48     | P72/INT2/T0IN      |

|        |                    |

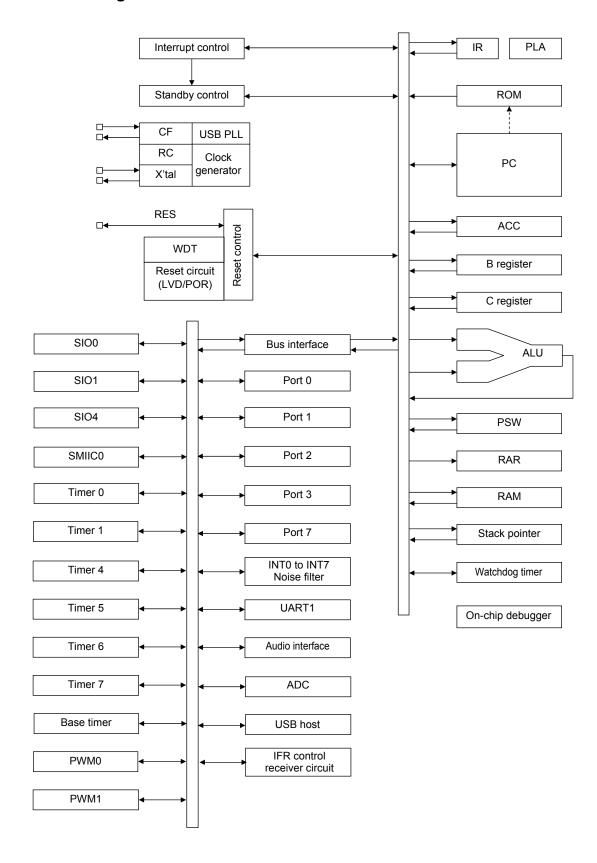

# **System Block Diagram**

Pin Description

| Pin Name                              | I/O |                                                                                                                                                                                                                |                    | D                   | escription            |         |         | Option |

|---------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|---------------------|-----------------------|---------|---------|--------|

| V <sub>SS</sub> 1, V <sub>SS</sub> 2, | -   | -power suppl                                                                                                                                                                                                   | y                  |                     |                       |         |         | No     |

| V <sub>SS</sub> 3                     |     |                                                                                                                                                                                                                |                    |                     |                       |         |         |        |

| V <sub>DD</sub> 1, V <sub>DD</sub> 2  | -   | +power supp                                                                                                                                                                                                    | ly                 |                     |                       |         |         | No     |

| V <sub>DD</sub> 3                     | -   | USB reference                                                                                                                                                                                                  | ce voltage         |                     |                       |         |         | Yes    |

| Port 0                                | I/O | • 8-bit I/O po                                                                                                                                                                                                 | rt                 |                     |                       |         |         | Yes    |

| P00 to P07                            |     |                                                                                                                                                                                                                | specified in 1-bit |                     |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                |                    | ned on and off in   | 1-bit units.          |         |         |        |

|                                       |     | HOLD release                                                                                                                                                                                                   | •                  |                     |                       |         |         |        |

|                                       |     | Port 0 interi     Pin function                                                                                                                                                                                 |                    |                     |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                |                    | 10 to AN7 (P00 to   | P07)                  |         |         |        |

|                                       |     |                                                                                                                                                                                                                |                    | GP0 to DBGP2 (      | •                     |         |         |        |

|                                       |     |                                                                                                                                                                                                                |                    | audio interface S   | •                     |         |         |        |

|                                       |     |                                                                                                                                                                                                                |                    | / audio interface l |                       |         |         |        |

|                                       |     | P07: Timer                                                                                                                                                                                                     | 7 toggle output    | / audio interface   | LRCK I/O              |         |         |        |

| Port 1                                | I/O | • 8-bit I/O po                                                                                                                                                                                                 | rt                 |                     |                       |         |         | Yes    |

| P10 to P17                            |     | • I/O can be                                                                                                                                                                                                   | specified in 1-bit | units               |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                |                    | ned on and off in   | 1-bit units.          |         |         |        |

|                                       |     | • Pin function                                                                                                                                                                                                 |                    |                     |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                | data output        | 1/0                 |                       |         |         |        |

|                                       |     | P11: SIO0                                                                                                                                                                                                      | data input / bus   | 1/0                 |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                | data output / SN   | IIIC0 clock I/O     |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                | *                  | I/O / SMIIC0 bus    | I/O / data input      |         |         |        |

|                                       |     |                                                                                                                                                                                                                | •                  |                     | sed in 3-wire SIO     | mode)   |         |        |

|                                       |     | P16: Timer                                                                                                                                                                                                     | 1 PWML output      | t / SMIIC0 bus I/C  | / data input          |         |         |        |

|                                       |     | P17: Timer                                                                                                                                                                                                     | 1 PWMH outpu       | t / buzzer output / | SMIIC0 clock I/O      |         |         |        |

| Port 2                                | I/O | • 6-bit I/O po                                                                                                                                                                                                 | rt                 |                     |                       |         |         | Yes    |

| P20 to P25                            |     |                                                                                                                                                                                                                | specified in 1-bit |                     |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                |                    | ned on and off in   | 1-bit units.          |         |         |        |

|                                       |     | • Pin function                                                                                                                                                                                                 |                    | OLD roleges innut   | t / timer 1 event in  | must /  |         |        |

|                                       |     | F20 t0 F23                                                                                                                                                                                                     | · ·                | · ·                 | t / timer 1 event in  | put /   |         |        |

|                                       |     | timer 0L capture input / timer 0H capture input P24 to P25: INT5 input / HOLD release input / timer 1 event input / timer 0L capture input / timer 0H capture input P20: INT6 input / timer 0L capture 1 input |                    |                     |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                |                    |                     |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                |                    |                     |                       |         |         |        |

|                                       |     | P22: SIO4                                                                                                                                                                                                      |                    |                     |                       |         |         |        |

|                                       |     | P23: SIO4 data I/O                                                                                                                                                                                             |                    |                     |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                | •                  | capture 1 input / S | SIO4 clock I/O        |         |         |        |

|                                       |     | Interrupt aci                                                                                                                                                                                                  | knowledge types    | S                   | Diaina 0              | 1       |         |        |

|                                       |     |                                                                                                                                                                                                                | Rising             | Falling             | Rising &<br>Falling   | H Level | L Level |        |

|                                       |     | INT4                                                                                                                                                                                                           | Enable             | Enable              | Enable                | Disable | Disable |        |

|                                       |     | INT5                                                                                                                                                                                                           | Enable             | Enable              | Enable                | Disable | Disable |        |

|                                       |     | INT6                                                                                                                                                                                                           | Enable             | Enable              | Enable                | Disable | Disable |        |

|                                       |     |                                                                                                                                                                                                                |                    |                     |                       |         |         |        |

|                                       |     | INT7                                                                                                                                                                                                           | Enable             | Enable              | Enable                | Disable | Disable |        |

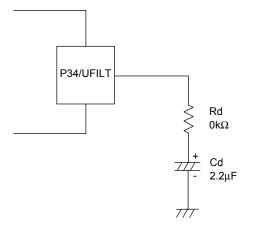

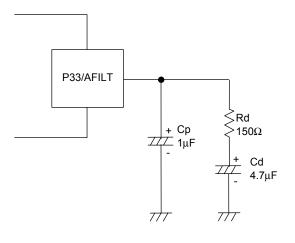

| Port 3                                | I/O | • 5-bit I/O po                                                                                                                                                                                                 | rt                 |                     |                       |         |         | Yes    |

|                                       | 1/0 | •                                                                                                                                                                                                              | specified in 1-bit | units               |                       |         |         | 163    |

| P30 to P34                            |     |                                                                                                                                                                                                                | •                  | ned on and off in   | 1-bit units.          |         |         |        |

|                                       |     | • Pin function                                                                                                                                                                                                 |                    |                     |                       |         |         |        |

|                                       |     | P30: UART                                                                                                                                                                                                      | 1 transmit         |                     |                       |         |         |        |

|                                       |     | P31: UART                                                                                                                                                                                                      | 1 receive          |                     |                       |         |         |        |

|                                       |     |                                                                                                                                                                                                                |                    |                     | circuit (see Fig. 6)  |         |         |        |

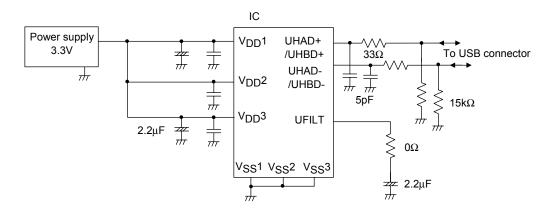

|                                       |     | P34: Conn                                                                                                                                                                                                      | ected to USB int   | erface PLL filter o | circuit (see Fig. 5). |         |         |        |

Continued on next page.

Continued from preceding page.

| Pin Name                      | I/O                                                        |                                                                                      |                     | D                    | escription            |         |         | Option |

|-------------------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------|----------------------|-----------------------|---------|---------|--------|

| Port 7                        | I/O                                                        | • 4-bit I/O po                                                                       | rt                  |                      | No                    |         |         |        |

| P70 to P73                    | Ī                                                          | • I/O can be                                                                         | specified in 1-bit  | units                |                       |         |         |        |

|                               | Pull-up resistors can be turned on and off in 1-bit units. |                                                                                      |                     |                      |                       |         |         |        |

|                               | • Pin functions                                            |                                                                                      |                     |                      |                       |         |         |        |

|                               |                                                            | P70: INT0                                                                            | input / HOLD rele   | ease input / timer   | OL capture input /    |         |         |        |

|                               |                                                            | watch                                                                                | ndog timer output   |                      |                       |         |         |        |

|                               |                                                            | P71: INT1                                                                            | input / HOLD rele   | ease input / timer   | 0H capture input      |         |         |        |

|                               |                                                            | P72: INT2                                                                            | input / HOLD rele   | ease input / timer   | 0 event input /       |         |         |        |

|                               |                                                            | timer                                                                                | 0L capture input    | / high-speed cloc    | ck counter input      |         |         |        |

|                               |                                                            |                                                                                      |                     | noise filter) / time | •                     |         |         |        |

|                               |                                                            |                                                                                      |                     |                      | e control receiver in | nput    |         |        |

|                               |                                                            |                                                                                      |                     | l8 (P70), AN9 (P7    | 71)                   |         |         |        |

|                               |                                                            | Interrupt acknowledge types                                                          |                     |                      |                       |         |         |        |

|                               |                                                            |                                                                                      | Rising              | Falling              | Rising &<br>Falling   | H Level | L Level |        |

|                               |                                                            | INT0                                                                                 | Enable              | Enable               | Disable               | Enable  | Enable  |        |

|                               |                                                            | INT1                                                                                 | Enable              | Enable               | Disable               | Enable  | Enable  |        |

|                               |                                                            | INT2                                                                                 | Enable              | Enable               | Enable                | Disable | Disable |        |

|                               |                                                            | INT3                                                                                 | Enable              | Enable               | Enable                | Disable | Disable |        |

| PWM0                          | I/O                                                        | PWM0 and F                                                                           | PWM1 output por     |                      |                       |         |         | No     |

| PWM1                          |                                                            | General-purpose input port  Pin functions  PWM0: Audio interface master clock output |                     |                      |                       |         |         |        |

|                               |                                                            |                                                                                      |                     |                      |                       |         |         |        |

|                               |                                                            |                                                                                      |                     |                      |                       |         |         |        |

|                               |                                                            | PWM1: Audio interface master clock input                                             |                     |                      |                       |         |         |        |

| UHAD-                         | I/O                                                        | USB-A port                                                                           | data I/O pin / gen  | eral-purpose I/O     | port                  |         |         | No     |

| JHAD+                         |                                                            |                                                                                      |                     |                      |                       |         |         |        |

| UHBD-                         | I/O                                                        | USB-B port of                                                                        | data I/O pin / gen  | eral-purpose I/O     | port                  |         |         | No     |

| JHBD+                         |                                                            |                                                                                      |                     |                      |                       |         |         |        |

| RES                           | I/O                                                        | External rese                                                                        | et input / internal | reset output         |                       |         |         | No     |

| XT1                           | 1                                                          | • 32.768kHz                                                                          | crystal resonator   | rinput               |                       |         |         | No     |

|                               |                                                            | • Pin functions                                                                      |                     |                      |                       |         |         |        |

|                               |                                                            | General-pu                                                                           | irpose input port   |                      |                       |         |         |        |

| AD converter input port: AN10 |                                                            |                                                                                      |                     |                      |                       |         |         |        |

| KT2                           | I/O                                                        | • 32.768kHz                                                                          | crystal resonator   | output               |                       |         |         | No     |

|                               | • Pin functions                                            |                                                                                      |                     |                      |                       |         |         |        |

|                               |                                                            | General-purpose I/O port                                                             |                     |                      |                       |         |         |        |

|                               |                                                            | AD conver                                                                            | ter input port: AN  | 111                  |                       |         |         |        |

| CF1                           | I                                                          | -                                                                                    | stal resonator inp  |                      |                       |         |         | No     |

| CF2                           | 0                                                          | Ceramic/crys                                                                         | stal resonator out  | tput                 |                       |         |         | No     |

# **On-chip Debugger Pin Treatment**

For the treatment of the on-chip debugger pins, refer to the separately available documents entitled "RD87 On-chip Debugger Installation Manual."

### **Recommended Unused Pin Treatment**

| Pin Name  P00 to P03, P05 to P07  P04  P10 to P17  P20 to P25  P30 to P34  P70 to P73  PWM0, PWM1  UHAD+, UHAD-  UHBD+, UHBD-  XT1 | Recommend                                    | ded Unused Pin Treatment |

|------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------|

| Pin Name                                                                                                                           | Board                                        | Software                 |

| P00 to P03, P05 to P07                                                                                                             | Open                                         | Set output low.          |

| P04                                                                                                                                | Pull-down with a $100k\Omega$ resistor.      | -                        |

| P10 to P17                                                                                                                         | Open                                         | Set output low.          |

| P20 to P25                                                                                                                         | Open                                         | Set output low.          |

| P30 to P34                                                                                                                         | Open                                         | Set output low.          |

| P70 to P73                                                                                                                         | Open                                         | Set output low.          |

| PWM0, PWM1                                                                                                                         | Open                                         | Set output low.          |

| UHAD+, UHAD-                                                                                                                       | Open                                         | Set output low.          |

| UHBD+, UHBD-                                                                                                                       | Open                                         | Set output low.          |

| XT1                                                                                                                                | Pull-down with a resistor of 100kΩ or lower. | -                        |

| XT2                                                                                                                                | Open                                         | Set output low.          |

Note: Since P34 is multiplexed with UFILT, it must be configured for input when the USB function is to be used.

Since P33 is multiplexed with AFILT, it must be configured for input when the audio interface PLL circuit is to be used.

# **Port Output Types**

The table below lists the type of port output and the presence/absence of a pull-up resistor.

Data can be read into any input port even if it is in output mode.

| Port Name    | Option Selected in Units of | Option Type | Output Type                        | Pull-up Resistor |

|--------------|-----------------------------|-------------|------------------------------------|------------------|

| P00 to P07   | 1 bit                       | 1           | CMOS                               | Programmable     |

| P10 to P17   |                             | 2           | N-channel open drain               | Programmable     |

| P20 to P25   |                             |             |                                    |                  |

| P30 to P34   |                             |             |                                    |                  |

| P70          | -                           | No          | N-channel open drain               | Programmable     |

| P71 to P73   | -                           | No          | CMOS                               | Programmable     |

| PWM0, PWM1   | -                           | No          | CMOS                               | No               |

| UHAD+, UHAD- | -                           | No          | CMOS                               | No               |

| UHBD+, UHBD- |                             |             |                                    |                  |

| XT1          | -                           | No          | Input only                         | No               |

| XT2          | -                           | No          | 32.768kHz crystal resonator output | No               |

|              |                             |             | (N-channel open drain when in      |                  |

|              |                             |             | general-purpose output mode)       |                  |

**User Option Table**

| Option Name             | Option to be<br>Applied on | Flash-ROM Version | Option Selected in Units of | Option Selection     |

|-------------------------|----------------------------|-------------------|-----------------------------|----------------------|

| Port output type        | D00 / D07                  | 0                 | 4.17                        | CMOS                 |

|                         | P00 to P07                 | O                 | 1 bit                       | N-channel open drain |

|                         | D404 D47                   | 0                 | 4.17                        | CMOS                 |

|                         | P10 to P17                 | O                 | 1 bit                       | N-channel open drain |

|                         | Doo's Doo                  | 0                 | 4.19                        | CMOS                 |

|                         | P20 to P25                 | 0                 | 1 bit                       | N-channel open drain |

|                         | Doo's Doo's                | 0                 | 4.17                        | CMOS                 |

|                         | P30 to P34                 | O                 | 1 bit                       | N-channel open drain |

| Program start           |                            | 0                 |                             | 00000h               |

| address                 | -                          | 0                 | -                           | 0FE00h               |

| USB regulator           | 1100                       | 0                 |                             | Use                  |

| JSB regulator           | USB regulator              | 0                 | -                           | Non-use              |

|                         | USB regulator              | 0                 |                             | Use                  |

|                         | (HOLD mode)                | O                 | -                           | Non-use              |

|                         | USB regulator              | 0                 |                             | Use                  |

|                         | (HALT mode)                | O                 | -                           | Non-use              |

| Main clock 8MHz         |                            | 0                 |                             | Enable               |

| selection               | -                          | O                 | -                           | Disable              |

| Low-voltage             | 5                          | 0                 |                             | Enable: Use          |

| detection reset         | Detection function         | 0                 | -                           | Disable: Non-use     |

| function                | Detection level            | 0                 | -                           | 7 levels             |

| Power-on reset function | Power-on reset level       | 0                 | -                           | 8 levels             |

## **USB Reference Power Option**

When a voltage 4.5 to 5.5V is supplied to V<sub>DD</sub>1 and the internal USB reference voltage circuit is activated, the reference voltage for USB port output is generated. The active/inactive state of the reference voltage circuit can be switched by selecting an option. The procedure for making the option selection is described below.

|                                 |                            | (1)    | (2)      | (3)      | (4)      |

|---------------------------------|----------------------------|--------|----------|----------|----------|

| Online collines                 | USB regulator              | Use    | Use      | Use      | Non-use  |

| Option settings                 | USB regulator at HOLD mode | Use    | Non-use  | Non-use  | Non-use  |

|                                 | USB regulator at HALT mode | Use    | Non-use  | Use      | Non-use  |

|                                 | Normal mode                | Active | Active   | Active   | Inactive |

| Reference voltage circuit state | HOLD mode                  | Active | Inactive | Inactive | Inactive |

|                                 | HALT mode                  | Active | Inactive | Active   | Inactive |

- When the USB reference voltage circuit is made inactive, the level of the reference voltage for the USB port output is equal to VDD1.

- Selection (2) or (3) can be used to set the reference voltage circuit inactive in HOLD or HALT mode.

- When the reference voltage circuit is activated, the current drain increases by approximately 100µA compared with when the reference voltage circuit is inactive.

Example 1: V<sub>DD</sub>1=V<sub>DD</sub>2=3.3V

- Inactivating the reference voltage circuit (selection (4)).

- Connecting V<sub>DD</sub>3 to V<sub>DD</sub>1 and V<sub>DD</sub>2.

Example 2: V<sub>DD</sub>1=V<sub>DD</sub>2=5.0V

- Activating the reference voltage circuit (selection (1)).

- $\bullet$  Isolating VDD3 from VDD1 and VDD2, and connecting capacitor between VDD3 and VSS.

(Note: Do not apply the voltage of more than 3.6V to UHAD+, UHAD-, UHBD+ and UHBD- when the reference voltage circuit is active.

Absolute Maximum Ratings at Ta = 25°C,  $V_{SS}1 = V_{SS}2 = V_{SS}3 = 0V$

|                           | Parameter                         | Symbol              | Pin/Remarks                                             | Conditions                                                    |                     |      | Specific | cation               |      |

|---------------------------|-----------------------------------|---------------------|---------------------------------------------------------|---------------------------------------------------------------|---------------------|------|----------|----------------------|------|

|                           |                                   |                     |                                                         |                                                               | V <sub>DD</sub> [V] | min  | typ      | max                  | unit |

|                           | kimum supply<br>age               | V <sub>DD</sub> max | V <sub>DD</sub> 1, V <sub>DD</sub> 2, V <sub>DD</sub> 3 | V <sub>DD</sub> 1=V <sub>DD</sub> 2=V <sub>DD</sub> 3         |                     | -0.3 |          | +6.5                 |      |

| Inpi                      | ut voltage                        | V <sub>I</sub> (1)  | XT1, CF1, RES                                           |                                                               |                     | -0.3 |          | V <sub>DD</sub> +0.3 | V    |

| -                         | ut/output<br>age                  | V <sub>IO</sub> (1) | Ports 0, 1, 2, 3, 7<br>PWM0, PWM1<br>XT2                |                                                               |                     | -0.3 |          | V <sub>DD</sub> +0.3 | V    |

|                           | Peak output current               | IOPH(1)             | Ports 0, 1, 2                                           | When CMOS output<br>type is selected     Per 1 applicable pin |                     | -10  |          |                      |      |

|                           |                                   | IOPH(2)             | PWM0, PWM1                                              | Per 1 applicable pin                                          | 1                   | -20  |          |                      |      |

|                           |                                   | IOPH(3)             | Port 3<br>P71 to P73                                    | When CMOS output<br>type is selected     Per 1 applicable pin |                     | -5   |          |                      |      |

|                           | Average output current (Note 1-1) | IOMH(1)             | Ports 0, 1, 2                                           | When CMOS output<br>type is selected     Per 1 applicable pin |                     | -7.5 |          |                      |      |

| nz cn                     |                                   | IOMH(2)             | PWM0, PWM1                                              | Per 1 applicable pin                                          |                     | -15  |          |                      |      |

| High level output current |                                   | IOMH(3)             | Port 3<br>P71 to P73                                    | When CMOS output<br>type is selected     Per 1 applicable pin |                     | -3   |          |                      |      |

|                           | Total output<br>current           | ΣΙΟΑΗ(1)            | Ports 0, 2                                              | Total current of all applicable pins                          |                     | -25  |          |                      |      |

|                           |                                   | ΣΙΟΑΗ(2)            | Port 1<br>PWM0, PWM1                                    | Total current of all applicable pins                          |                     | -25  |          |                      |      |

|                           |                                   | ΣΙΟΑΗ(3)            | Ports 0, 1, 2<br>PWM0, PWM1                             | Total current of all applicable pins                          |                     | -45  |          |                      |      |

|                           |                                   | ΣΙΟΑΗ(4)            | Port 3<br>P71 to P73                                    | Total current of all applicable pins                          |                     | -10  |          |                      |      |

|                           |                                   | ΣΙΟΑΗ(5)            | UHAD+, UHAD-<br>UHBD+, UHBD-                            | Total current of all applicable pins                          |                     | -50  |          |                      | m/   |

|                           | Peak output current               | IOPL(1)             | P02 to P07<br>Ports 1, 2<br>PWM0, PWM1                  | Per 1 applicable pin                                          |                     |      |          | 20                   |      |

|                           |                                   | IOPL(2)             | P00, P01                                                | Per 1 applicable pin                                          |                     |      |          | 30                   |      |

|                           |                                   | IOPL(3)             | Ports 3, 7<br>XT2                                       | Per 1 applicable pin                                          |                     |      |          | 10                   |      |

| rent                      | Average output current (Note 1-1) | IOML(1)             | P02 to P07<br>Ports 1, 2<br>PWM0, PWM1                  | Per 1 applicable pin                                          |                     |      |          | 15                   |      |

| t cur                     | ,                                 | IOML(2)             | P00, P01                                                | Per 1 applicable pin                                          |                     |      |          | 20                   |      |

| ei outpu                  |                                   | IOML(3)             | Ports 3, 7<br>XT2                                       | Per 1 applicable pin                                          |                     |      |          | 7.5                  |      |

| Low level output current  | Total output current              | ΣIOAL(1)            | Ports 0, 2                                              | Total current of all applicable pins                          |                     |      |          | 45                   |      |

| _                         |                                   | ΣIOAL(2)            | Port 1<br>PWM0, PWM1                                    | Total current of all applicable pins                          |                     |      |          | 45                   |      |

|                           |                                   | ΣIOAL(3)            | Ports 0, 1, 2<br>PWM0, PWM1                             | Total current of all applicable pins                          |                     |      |          | 80                   |      |

|                           |                                   | ΣIOAL(4)            | Ports 3, 7<br>XT2                                       | Total current of all applicable pins                          |                     |      |          | 15                   |      |

|                           |                                   | ΣIOAL(5)            | UHAD+, UHAD-<br>UHBD+, UHBD-                            | Total current of all applicable pins                          |                     |      |          | 50                   |      |

|                           | wable power<br>sipation           | Pd max              | SQFP48(7×7)                                             | Ta=-40 to +85°C                                               |                     |      |          | 140                  | m۷   |

|                           | erating ambient<br>nperature      | Topr                |                                                         |                                                               |                     | -40  |          | +85                  | °C   |

| Sto                       | rage ambient                      | Tstg                |                                                         |                                                               |                     | -55  |          | +125                 |      |

Note 1-1: The average output current is an average of current values measured over 100ms intervals.

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Allowable Operating Conditions at Ta = -40 °C to +85 °C,  $V_{SS}1 = V_{SS}2 = V_{SS}3 = 0V$

| Parameter                                    | Symbol              | Pin/Remarks                                           | Conditions                                                                                        |                     |                            | Specific | ation                       |        |

|----------------------------------------------|---------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------|----------------------------|----------|-----------------------------|--------|

| i didilietei                                 | Gymbol              | 1 III/I CITIAINS                                      | Conditions                                                                                        | V <sub>DD</sub> [V] | min                        | typ      | max                         | unit   |

| Operating                                    | V <sub>DD</sub> (1) | $V_{DD}1=V_{DD}2=V_{DD}3$                             | 0.245μs ≤ tCYC ≤ 200μs                                                                            |                     | 3.0                        |          | 5.5                         |        |

| supply voltage<br>(Note 2-1)                 |                     |                                                       | 0.245μs ≤ tCYC ≤ 0.383μs<br>USB circuit active.                                                   |                     | 3.0                        |          | 5.5                         |        |

|                                              |                     |                                                       | 0.490μs ≤ tCYC ≤ 200μs<br>Except for onboard<br>programming mode                                  |                     | 2.7                        |          | 5.5                         |        |

| Memory<br>retention supply<br>voltage        | VHD                 | V <sub>DD</sub> 1=V <sub>DD</sub> 2=V <sub>DD</sub> 3 | RAM and register contents are retained in HOLD mode                                               |                     | 2.0                        |          | 5.5                         |        |

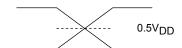

| High level input voltage                     | V <sub>IH</sub> (1) | Ports 0, 1, 2, 3, 7<br>PWM0, PWM1                     |                                                                                                   | 2.7 to 5.5          | 0.3V <sub>DD</sub><br>+0.7 |          | V <sub>DD</sub>             | V      |

|                                              | V <sub>IH</sub> (2) | XT1, XT2, CF1, RES                                    |                                                                                                   | 2.7 to 5.5          | 0.75V <sub>DD</sub>        |          | $V_{DD}$                    |        |

| Low level input voltage                      | V <sub>IL</sub> (1) | Ports 1, 2, 3, 7                                      |                                                                                                   | 4.0 to 5.5          | $V_{SS}$                   |          | 0.1V <sub>DD</sub><br>+0.4  |        |

|                                              | V <sub>IL</sub> (2) |                                                       |                                                                                                   | 2.7 to 4.0          | $V_{SS}$                   |          | 0.2V <sub>DD</sub>          |        |

|                                              | V <sub>IL</sub> (3) | Port 0<br>PWM0, PWM1                                  |                                                                                                   | 4.0 to 5.5          | V <sub>SS</sub>            |          | 0.15V <sub>DD</sub><br>+0.4 |        |

|                                              | V <sub>IL</sub> (4) |                                                       |                                                                                                   | 2.7 to 4.0          | V <sub>SS</sub>            |          | 0.2V <sub>DD</sub>          |        |

|                                              | V <sub>IL</sub> (5) | XT1, XT2, CF1, RES                                    |                                                                                                   | 2.7 to 5.5          | V <sub>SS</sub>            |          | 0.25V <sub>DD</sub>         |        |

| Instruction                                  | tCYC                |                                                       |                                                                                                   | 3.0 to 5.5          | 0.245                      |          | 200                         |        |

| cycle time                                   |                     |                                                       | USB circuit active.                                                                               | 3.0 to 5.5          | 0.245                      |          | 0.383                       |        |

| (Note 2-2)                                   |                     |                                                       | Except for onboard programming mode                                                               | 2.7 to 5.5          | 0.490                      |          | 200                         | μs     |

| External<br>system clock<br>frequency        | FEXCF(1)            | CF1                                                   | CF2 pin open System clock frequency division ratio =1/1 External system clock duty =50±5%         | 3.0 to 5.5          | 0.1                        |          | 12                          | NAL I- |

|                                              |                     |                                                       | CF2 pin open     System clock frequency division ratio =1/1     External system clock duty =50±5% | 2.7 to 5.5          | 0.1                        |          | 6                           | MHz    |

| Oscillation<br>frequency range<br>(Note 2-3) | FmCF                | CF1, CF2                                              | 12MHz ceramic oscillation<br>mode<br>See Fig. 1.                                                  | 3.0 to 5.5          |                            | 12       |                             | MHz    |

|                                              | FmRC                |                                                       | Internal medium-speed RC oscillation                                                              | 2.7 to 5.5          | 0.5                        | 1.0      | 2.0                         |        |

|                                              | FmSRC               |                                                       | Internal low-speed RC oscillation                                                                 | 2.7 to 5.5          | 15                         | 30       | 60                          |        |

|                                              | FsX'tal             | XT1, XT2                                              | 32.768kHz crystal oscillation<br>mode<br>See Fig. 2.                                              | 2.7 to 5.5          |                            | 32.768   |                             | kHz    |

Note 2-1: V<sub>DD</sub> must be held greater than or equal to 3.0V in the flash ROM onboard programming mode.

Note 2-3: See Tables 1 and 2 for the oscillation constants.

Note 2-2: Relationship between tCYC and oscillation frequency is 3/FmCF at a division ratio of 1/1 and 6/FmCF at a division ratio of 1/2.

Electrical Characteristics at  $Ta = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_SS1 = V_{SS}2 = V_{SS}3 = 0V$

| Parameter                | Symbol              | Pin/Remarks                              | Conditions                                                                               |                     |                      | Specifica          | ition |      |

|--------------------------|---------------------|------------------------------------------|------------------------------------------------------------------------------------------|---------------------|----------------------|--------------------|-------|------|

| Parameter                | Symbol              | Pili/Remarks                             | Conditions                                                                               | V <sub>DD</sub> [V] | min                  | typ                | max   | unit |

| High level input current | I <sub>IH</sub> (1) | Ports 0, 1, 2, 3, 7<br>RES<br>PWM0, PWM1 | Output disabled Pull-up resistor off VIN=VDD (Including output Tr's off leakage current) | 2.7 to 5.5          |                      |                    | 1     |      |

|                          | I <sub>IH</sub> (2) | XT1, XT2                                 | Input port configuration V <sub>IN</sub> =V <sub>DD</sub>                                | 2.7 to 5.5          |                      |                    | 1     |      |

|                          | I <sub>IH</sub> (3) | CF1                                      | V <sub>IN</sub> =V <sub>DD</sub>                                                         | 2.7 to 5.5          |                      |                    | 15    |      |

| Low level input current  | I <sub>IL</sub> (1) | Ports 0, 1, 2, 3, 7<br>RES<br>PWM0, PWM1 | Output disabled Pull-up resistor off VIN=VSS (Including output Tr's off leakage current) | 2.7 to 5.5          | -1                   |                    |       | μΑ   |

|                          | I <sub>IL</sub> (2) | XT1, XT2                                 | Input port configuration VIN=VSS                                                         | 2.7 to 5.5          | -1                   |                    |       |      |

|                          | I <sub>IL</sub> (3) | CF1                                      | V <sub>IN</sub> =V <sub>SS</sub>                                                         | 2.7 to 5.5          | -15                  |                    |       |      |

| High level output        | V <sub>OH</sub> (1) | Ports 0, 1, 2, 3                         | I <sub>OH</sub> =-1mA                                                                    | 4.5 to 5.5          | V <sub>DD</sub> -1   |                    |       |      |

| voltage                  | V <sub>OH</sub> (2) | P71 to P73                               | I <sub>OH</sub> =-0.4mA                                                                  | 3.0 to 5.5          | V <sub>DD</sub> -0.4 |                    |       |      |

|                          | V <sub>OH</sub> (3) |                                          | I <sub>OH</sub> =-0.2mA                                                                  | 2.7 to 5.5          | V <sub>DD</sub> -0.4 |                    |       |      |

|                          | V <sub>OH</sub> (4) | PWM0, PWM1                               | I <sub>OH</sub> =-10mA                                                                   | 4.5 to 5.5          | V <sub>DD</sub> -1.5 |                    |       |      |

|                          | V <sub>OH</sub> (5) | P05 to P07                               | I <sub>OH</sub> =-1.6mA                                                                  | 3.0 to 5.5          | V <sub>DD</sub> -0.4 |                    |       |      |

|                          | V <sub>OH</sub> (6) | (Note 3-1)                               | I <sub>OH</sub> =-1mA                                                                    | 2.7 to 5.5          | V <sub>DD</sub> -0.4 |                    |       |      |

| Low level output         | V <sub>OL</sub> (1) | P00, P01                                 | I <sub>OL</sub> =30mA                                                                    | 4.5 to 5.5          |                      |                    | 1.5   | .,   |

| voltage                  | V <sub>OL</sub> (2) |                                          | I <sub>OL</sub> =5mA                                                                     | 3.0 to 5.5          |                      |                    | 0.4   | V    |