## **Operating Conditions** at $Ta = 25^{\circ}C$ ,

| Parameter                       | Symbol             | Conditions                                              | Ratings | Unit |

|---------------------------------|--------------------|---------------------------------------------------------|---------|------|

| Recommended supply voltage      | V <sub>CC</sub>    |                                                         | 13.2    | V    |

| Recommended load resistance     | RL                 |                                                         | 4       | Ω    |

| Operating voltage range         | V <sub>CC</sub> op |                                                         | 5 to 16 | V    |

| Operating load resistance range | R <sub>L</sub> op  | Under conditions where maximum ratings are not exceeded | 2 to 8  | Ω    |

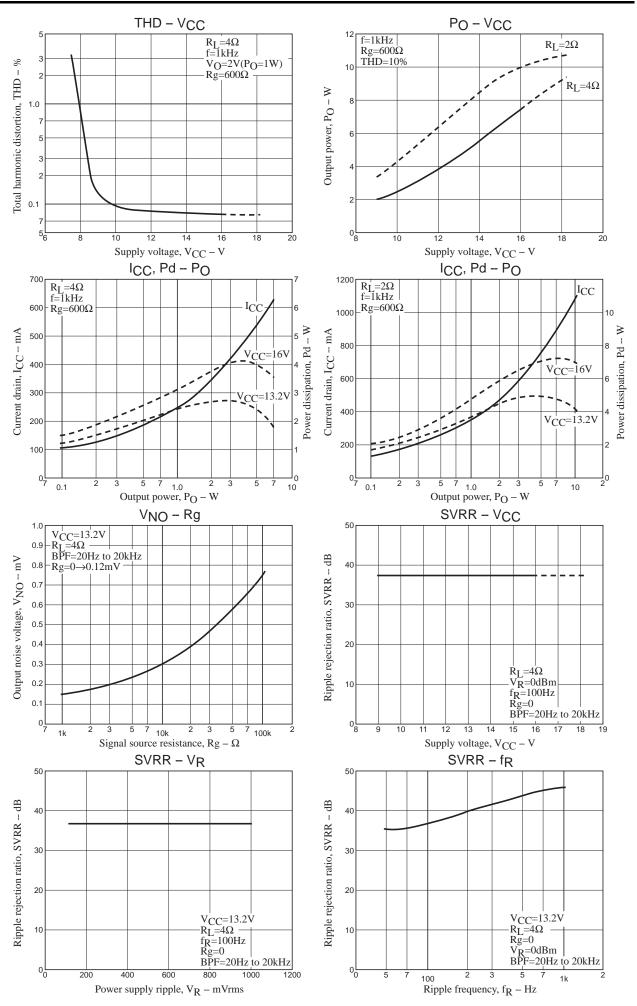

#### **Electrical Characteristics** at Ta = 25°C, $V_{CC} = 13.2V$ , $R_L = 4\Omega$ , f = 1 kHz, $Rg = 600\Omega$ , specified board/specified circuit $30 \times 30 \times 15$ mm<sup>3</sup> thick aluminum used

|                               |                   | specified board/specified circu        | II, 30×30×. | I.JIIIII ull | ck alumin | im used |

|-------------------------------|-------------------|----------------------------------------|-------------|--------------|-----------|---------|

| Parameter                     | Symbol            | Conditions                             | Ratings     |              |           | Unit    |

|                               |                   |                                        | min         | typ          | max       | Unit    |

| Quiescent current             | Icco              |                                        |             | 65           | 130       | mA      |

| Voltage gain                  | VG                | V <sub>O</sub> = 0dBm                  | 43          | 45           | 47        | dB      |

| Output power                  | P <sub>O</sub> 1  | 13.2 V / 4Ω, THD = 10%                 | 4           | 5            |           | W       |

|                               | P <sub>O</sub> 2  | 14.4 V / 4Ω, THD = 10%                 | 5           | 6            |           | W       |

| Total harmonic distortion     | THD               | $V_{O} = 2V$                           |             | 0.1          | 1.0       | %       |

| Output noise voltage          | V <sub>NO</sub>   | Rg = 0, BPF = 20 Hz to 20 kHz          | 30          | 40           |           | dB      |

| Ripple rejection ratio        | SVRR1             | Rg = 0, BPF = 20 Hz to 20 kHz          | 30          | 40           |           | dB      |

|                               |                   | $V_R = 0$ dBm, f <sub>R</sub> = 100Hz  |             |              |           |         |

|                               | SVRR2             | Rg = 0, BPF = 20 Hz to 20 kHz          |             | 47           |           | dB      |

|                               |                   | $V_R = 0$ dBm, f <sub>R</sub> = 100 Hz |             |              |           |         |

| Over-voltage attack           | V <sub>CC</sub> X | Rg = 0                                 |             | 21.5         |           | V       |

| Starting time                 | t <sub>S</sub>    |                                        |             | 0.35         |           | s       |

| Input resistance              | R <sub>IN</sub>   |                                        |             | 50           |           | kΩ      |

| Roll-off frequency            | fL                |                                        |             | 40           |           | Hz      |

|                               | fH                |                                        |             | 90           |           | kHz     |

| Thermal operating temperature | Тс                |                                        |             | 125          |           | °C      |

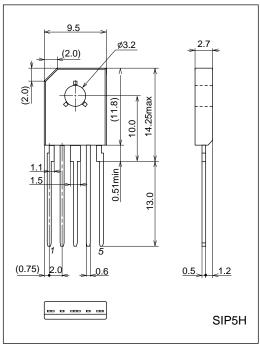

# **Package Dimensions**

unit : mm (typ) 3031C

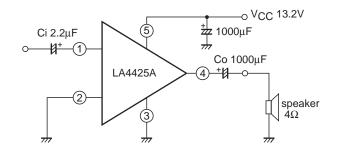

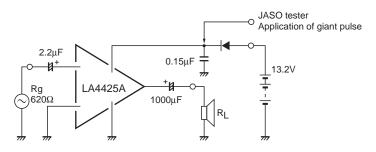

# **Sample Application Circuit**

- On-chip overvoltage protection

- On-chip thermal protection

- On-chip pop noise reducing circuit

- On-chip output D.C. short protection

# **Pin Voltage** at $V_{CC} = 13.2V$

| Characteristics                  | Input                         | Small signal<br>GND | Large signal<br>GND | Output                          | V <sub>CC</sub>             |

|----------------------------------|-------------------------------|---------------------|---------------------|---------------------------------|-----------------------------|

| Pin No.                          | 1                             | 2                   | 3                   | 4                               | 5                           |

| Pin voltage<br>(reference value) | (≈ 2V <sub>BE</sub> )<br>1.4V | 0V                  | 0V                  | (≈ 1/2V <sub>CC</sub> )<br>6.5V | (V <sub>CC</sub> )<br>13.2V |

## **IC Usage Notes**

### Maximum ratings

If the IC is used in the vicinity of the maximum ratings, even a slight variation in conditions may cause the maximum ratings to be exceeded, thereby leading to a breakdown.

#### Printed circuit board

When drawing the printed circuit pattern, refer to the sample printed circuit pattern. Be careful not to form a feedback loop between input and output.

## **Comparison of External Components**

| External Parts                                  | Our ICs now in use | LA4425A |  |

|-------------------------------------------------|--------------------|---------|--|

| Output coupling capacitor                       | 0                  | 0       |  |

| Input coupling capacitor                        | 0                  | 0       |  |

| Bootstrap capacitor                             | 0                  | -       |  |

| Feedback capacitor                              | 0                  | -       |  |

| Filter capacitor                                | 0                  | -       |  |

| Phase compensation capacitor                    | 0                  | -       |  |

| Oscillation correction polyester film capacitor | 0                  | -       |  |

| Oscillation correction resistor                 | 0                  | -       |  |

| Total                                           | 8 pcs.             | 2 pcs.  |  |

Note: The power supply capacitor is not counted as a power IC part.

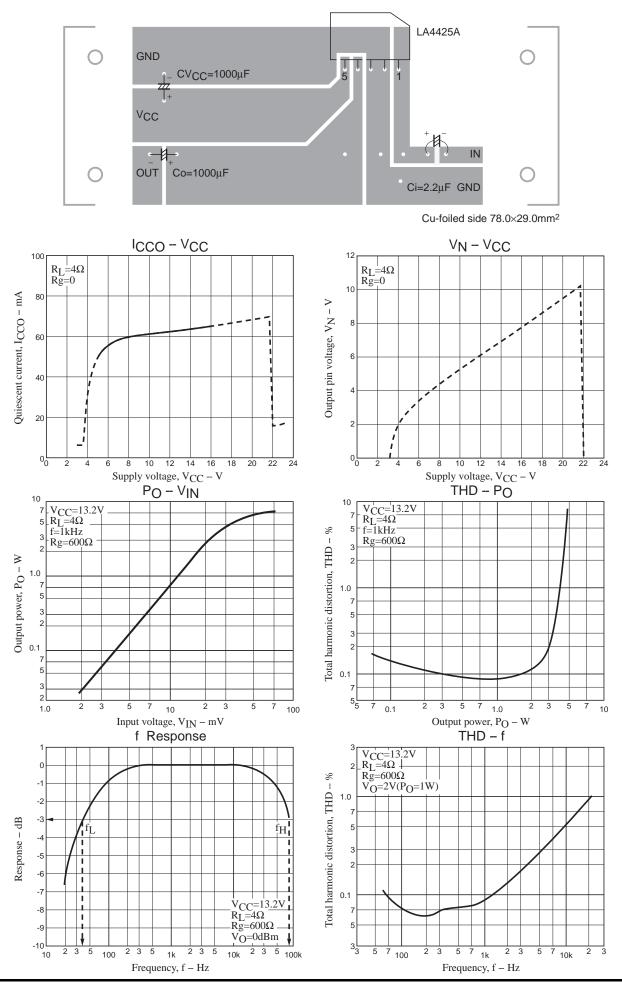

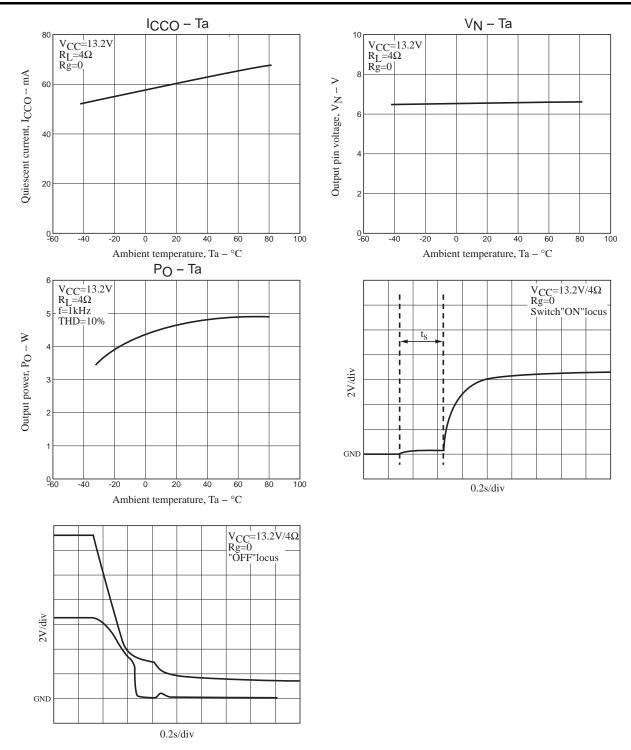

# **Sample Printed Circuit Pattern**

## **Instructions and Precautions**

- Connect a capacitor of 1000pF across pins ① and ② for external disturbance path.

- Be careful of the ground line artwork when laying out the printed circuit pattern. Arrange so that the Sg route and load current flow-in route do not overlap. Refer to the recommended printed circuit pattern or make slits, etc. at pins <sup>(2)</sup> and <sup>(3)</sup>.

# **DUAL Printed Circuit Pattern Example**

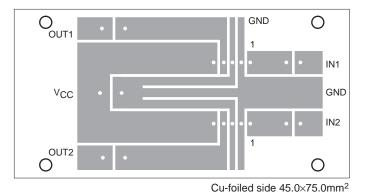

• Short Circuit Tests

Our company's recommended printed circuit board: Apply  $V_{CC}=13.2V$  using a  $30\times30\times1.5$  mm<sup>3</sup> thick aluminum board. The IC will be protected from the DC/AC shorting of switches 1 to 4 above. However, be careful not to damage the IC by turning  $V_{CC}$  "ON" when DC short (SW 1 or SW 2) is on.

• Power Supply Positive Surge

The over-voltage protector (V<sub>CC</sub>X  $\approx$  21.5V) inside the IC is used to cut all bias routes and reverse bias between B-E of output stage elements, in order to increase the power line's capability of handling positive surge. This means, of course, that a V<sub>CES</sub> (V<sub>CBO</sub>) type output stage element is used instead of the V<sub>CEO</sub> (V<sub>CER</sub>) type.

## • Load Resistance and Misoperation It should be noted that when $R_L < 2\Omega$ and $V_{CC}$ is high, and the switch is turned "ON" when setting is for a signal (THD = 10%), the ground detector (current × voltage Schmitt circuit) operates momentarily.

• Precautions on TaB

If power voltage is applied to the IC substrate (the heat sink on a set), the IC structure is such that the PN junctions may be burned, causing deterioration or destruction. Consult Our company's Quality Assurance Department with regard to the energy handling capability (voltage peak value, pulse width). Also, the IC TaB (substrate) is connected to pin 3, large signal GND.

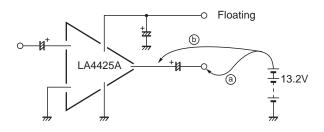

• Test of +V<sub>CC</sub> to Output Pin

The power pin is in a floating state when a power capacitor is connected, so if  $+V_{CC}$  touches output lines (a) and (b), the upper power transistor inside the IC will be damaged.

The LA4425A has a protective bypass route inside the IC.

• Starting Time (t<sub>s</sub>)

This is set at 0.35sec/typ, but it can be made shorter by making input capacitor Ci smaller, or longer by making it larger.

• Pop noise

The pop noise prevention circuit operates to reduce pop until Rg reaches  $50k\Omega$ . However, if Rg is left open, the charging route of input capacitor Ci is lost, so the pop noise reduction circuit stops operating and click noises become louder.

• VG/OSC

The voltage gain is fixed at 45dB inside the IC. It is impossible to change it externally. Phase compensation capacitors (350pF/total) are connected between individual stages inside the IC, and the open loop gain is low. In addition, the upper and lower drives are made equivalent so that final stage current gain is adjusted, providing a measure against unwanted high-frequency parasitic oscillation peculiar to power IC's.

BTL Connection

Connection is impossible with IC alone.

Reverse Mounting of IC

The pin assignment is such that there is no danger of damage.

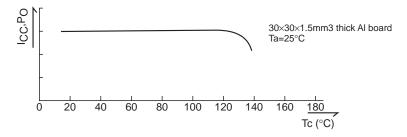

• T.S.D (Thermal Shutdown) Operating Temperature

T.S.D is capable of starting operation at Tc 120 to 130 $^{\circ}$ C. When this is converted to junction temperature (Tj) according to the formula below.

Tj ≈ 165C,

$T_i = Q_i c \cdot P d + T c$

As T.S.D operation progresses, the output pin bias voltage drops, and it becomes harder to drive the upper waveform. Therefore, the current ( $I_{CC}$ ) and power ( $P_O$ ) show a tendency to decrease.

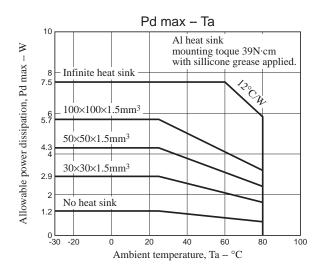

# **Proper Cares in Mounting Radiator Fin**

- 1. The mounting torque is in the range of 1. The mounting torque is in the range of 39 to 59 N·cm.

- 2. The distance between screw holes of the radiator fin must coincide with the distance between screw holes of the IC.

- 3. The screw to be used must have a head equivalent to the one of truss machine screw or binder machine screw defined by JIS. Washers must be also used to protect the IC case.

- 4. No foreign matter such as cutting particles shall exist between heat sink and radiator fin. When applying grease on the junction surface, it must be applied uniformly on the whole surface.

- 5. Because the heat sink mounting tab and the heat sink are at the same electric potential as the chip's GND, care must be taken when mounting the heat sink on more than one device.

- 6. IC lead pins are soldered to the printed circuit board after the radiator fin is mounted on the IC.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright have and is not for resale in any manner.