# Silicon Image, Inc.

SiI-DS-0021-E June 2005

#### **Application Information**

To obtain the most updated Application Notes and other useful information for your design, please visit the Silicon Image web site at www.siliconimage.com or contact your local Silicon Image sales office.

#### **Copyright Notice**

This manual is copyrighted by Silicon Image, Inc. Do not reproduce, transform to any other format, or send/transmit any part of this documentation without the expressed written permission of Silicon Image, Inc.

#### Trademark Acknowledgment

Silicon Image, the Silicon Image logo, PanelLink<sup>®</sup> and the PanelLink<sup>®</sup> Digital logo are registered trademarks of Silicon Image, Inc. TMDS<sup>TM</sup> is a trademark of Silicon Image, Inc. VESA<sup>®</sup>, FPD<sup>TM</sup> are trademarks of the Video Electronics Standards Association. I<sup>2</sup>C is a trademark of Philips Semiconductor. All other trademarks are the property of their respective holders.

#### **Disclaimer**

This document provides technical information for the user. Silicon Image, Inc. reserves the right to modify the information in this document as necessary. The customer should make sure that they have the most recent data sheet version. Silicon Image, Inc. holds no responsibility for any errors that may appear in this document. Customers should take appropriate action to ensure their use of the products does not infringe upon any patents. Silicon Image, Inc. respects valid patent rights of third parties and does not infringe upon or assist others to infringe upon such rights.

All information contained herein is subject to change without notice.

#### **Revision History**

| Revision      | Date  | Comment                                                                                                                                                                |

|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sil-DS-0021-A | 01/99 | Full Release                                                                                                                                                           |

| Sil-DS-0021-B | 03/99 | Internal Revision B release                                                                                                                                            |

| Sil-DS-0021-C | 04/02 | New format. I <sup>2</sup> C programming and strapping mode description,TFT mapping and Design Recommendations, pin names ISEL/RST changed to ISEL/RST# and PD to PD#. |

| Sil-DS-0021-D | 09/02 | Included Pb-free package. Added De-skew range. Corrected PD# pin number.                                                                                               |

| SiI-DS-0021-E | 06/05 | Corrected D1 dimension. Corrected JEDEC code. Included VCC details for power measurement. Added Register Reset values and additional sample programming code.          |

© 2005 Silicon Image, Inc.

## **TABLE OF CONTENTS**

| General Description                                                     |      |

|-------------------------------------------------------------------------|------|

| Features                                                                | 1    |

| SiI 164 Pin Diagram                                                     | 1    |

| Functional Description                                                  | 2    |

| PanelLink TMDS Digital Core                                             |      |

| I <sup>2</sup> C Interface and Registers                                | 2    |

| Data Capture Logic                                                      |      |

| Electrical Specifications                                               |      |

| Absolute Maximum Conditions                                             |      |

| Normal Operating Conditions                                             |      |

| Digital I/O Specifications                                              |      |

| DC Specifications                                                       |      |

| AC Specifications                                                       | 6    |

| Input Timing Diagrams                                                   |      |

| Pin Descriptions                                                        |      |

| Input Pins                                                              |      |

| Configuration Pins                                                      |      |

| Input Voltage Reference Pin                                             |      |

| Power Management Pins                                                   | . 11 |

| Differential Signal Data Pins                                           |      |

| Reserved Pins                                                           |      |

| Power and Ground Pins                                                   |      |

| l <sup>2</sup> C Registers                                              | . 12 |

| I <sup>2</sup> C Register Mapping                                       |      |

| I <sup>2</sup> C Register Definitions                                   |      |

| I <sup>2</sup> C Slave Interface and Address                            |      |

| Data De-skew Feature                                                    |      |

| Data Latching Modes                                                     |      |

| I <sup>2</sup> C Programming Sequence                                   |      |

| Enabling Hot Plug Detection Mode                                        |      |

| Non-I <sup>2</sup> C/Strap Mode Configuration                           | . 19 |

| TFT Panel Data Mapping                                                  | . 21 |

| Design Recommendations                                                  |      |

| 1.5V to 3.3V I <sup>2</sup> C Bus Level-Shifting                        |      |

| Voltage Ripple Regulation                                               |      |

| Decoupling Capacitors Series Damping Resistors on Outputs               | . ∠0 |

|                                                                         |      |

| Differential Trace Routing Package Dimensions and Marking Specification | . 27 |

|                                                                         |      |

| Ordering Information                                                    | . 29 |

# **LIST OF TABLES**

| Table 1. Data De-Skew Estimated Values                                             | 16 |

|------------------------------------------------------------------------------------|----|

| Table 2. Sample Programming Sequence for SiI 164 in 12-bit Mode                    | 18 |

| Table 3. Non-I <sup>2</sup> C/Strap Mode Options                                   | 20 |

| Table 4. One Pixel/Clock Input/Output TFT Mode - VESA P&D and FPDI-2 Compliant     | 21 |

| Table 5. 24-bit One Pixel/Clock Input with 24-bit Two Pixels/Clock Output TFT Mode | 22 |

| Table 6. 18-bit One Pixel/Clock Input with 18-bit Two Pixels/Clock Output TFT Mode |    |

| Table 7. Recommended Components for Bypass and Decoupling Circuits                 |    |

|                                                                                    |    |

| LIST OF FIGURES                                                                    |    |

| Figure 1. Pin Diagram for SiI 164                                                  | 1  |

| Figure 2. Functional Block Diagram                                                 |    |

| Figure 3. Clock Cycle High/Low Times                                               |    |

| Figure 4. Low Swing Differential Times                                             |    |

| Figure 5. ISEL/RST# Minimum Timing                                                 |    |

| Figure 6. Input Data Setup/Hold Time to IDCK                                       |    |

| Figure 7. VSYNC, HSYNC and CTL[3:1] Delay Time from DE                             | 8  |

| Figure 8. DE High and Low Times                                                    | 8  |

| Figure 9. I <sup>2</sup> C Data Valid Delay (driving Read Cycle data)              | 8  |

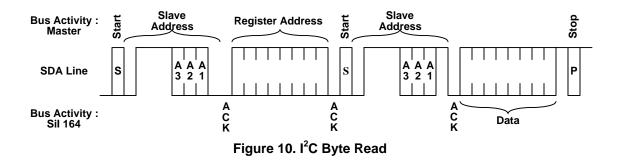

| Figure 10. I <sup>2</sup> C Byte Read                                              | 15 |

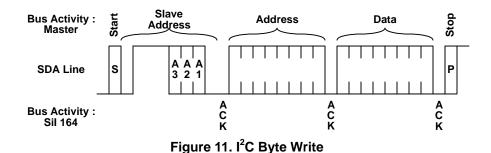

| Figure 11. I <sup>2</sup> C Byte Write                                             |    |

| Figure 12. Sil 164 Data De-skew Feature Timing                                     |    |

| Figure 13. 12-bit Input Data Latching                                              |    |

| Figure 14. 24-bit Input Data Latching                                              |    |

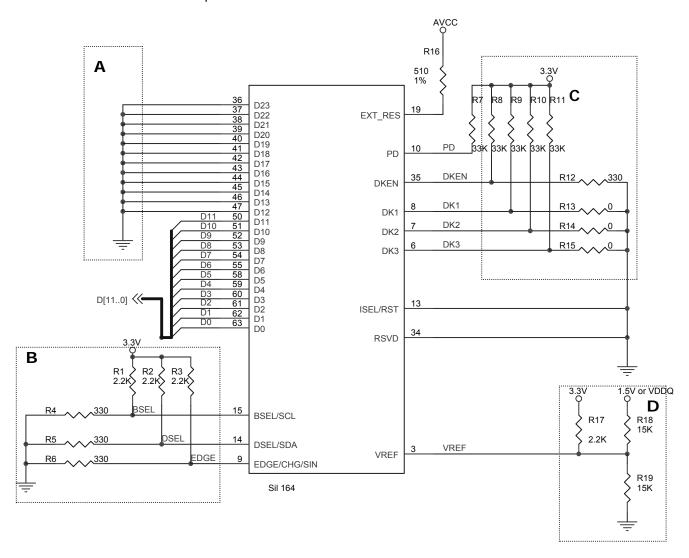

| Figure 15. Non- I <sup>2</sup> C/Strap Mode Schematic Example                      |    |

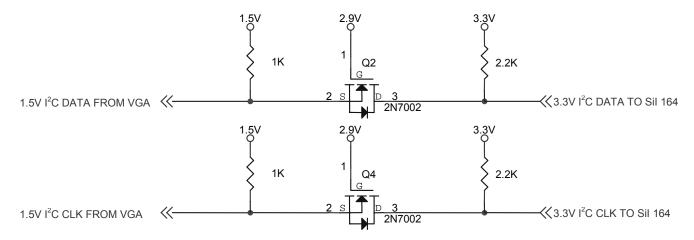

| Figure 16. I <sup>2</sup> C Bus Voltage Level-Shifting using Fairchild NDC7002N    |    |

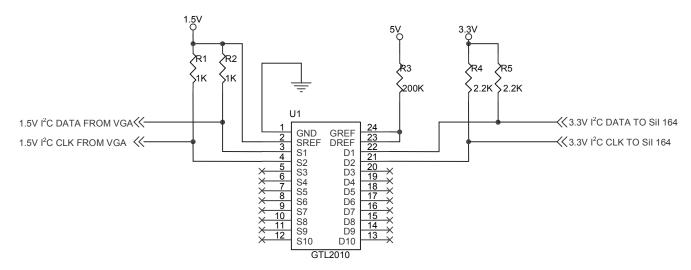

| Figure 17. I <sup>2</sup> C Bus Voltage Level Shifting using Philips GTL 2010      | 24 |

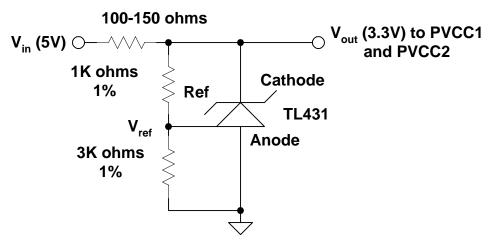

| Figure 18. Voltage Regulation using TL431                                          |    |

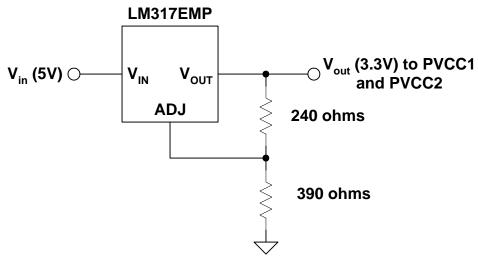

| Figure 19. Voltage Regulation using LM317                                          |    |

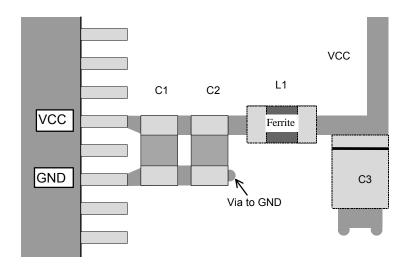

| Figure 20. Decoupling and Bypass Capacitor Placement                               |    |

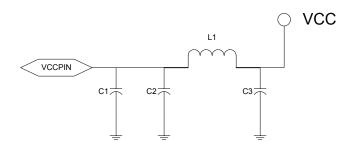

| Figure 21. Decoupling and Bypass Schematic                                         |    |

| Figure 22. Series Input Damping Resistors for Driving Source                       |    |

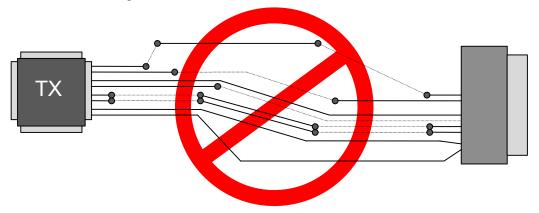

| Figure 23. Example of Incorrect Differential Signal Routing                        |    |

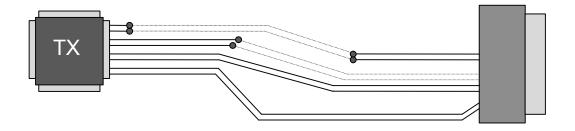

| Figure 24. Example of Correct Differential Signal Routing                          |    |

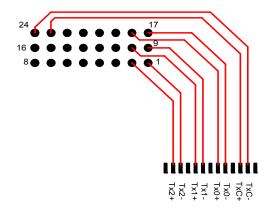

| Figure 25. Differential Trace Routing to DVI Connector(Top Side View)              |    |

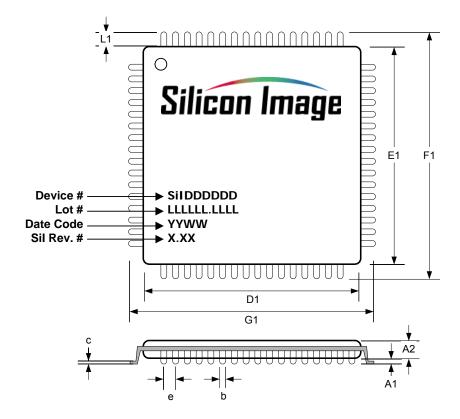

| Figure 26. 64-pin TQFP Package Dimensions (JEDEC code MS-026ACD)                   | 29 |

|                                                                                    |    |

#### **General Description**

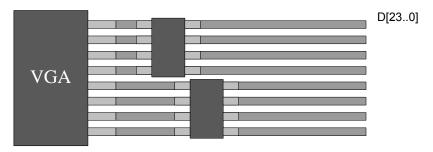

The SiI 164 transmitter uses PanelLink® Digital technology to support displays ranging from VGA to UXGA resolutions (25 - 165Mpps) in a single link interface.

The SiI 164 transmitter has a highly flexible interface with either a 12-bit mode ( $\frac{1}{2}$  pixel per clock edge) or 24-bit mode 1 pixel per clock edge input for true color (16.7 million) support. In 24-bit mode, the SiI 164 supports single or dual edge clocking. In 12-bit mode, the SiI164 supports dual edge single clocking or single edge dual clocking. The SiI 164 can be programmed though an I<sup>2</sup>C interface. In addition the SiI 164 also supports Receiver and Hot Plug Detection.

PanelLink Digital technology simplifies PC design by resolving many of the system level issues associated with high-speed mixed signal design, providing the system designer with a digital interface solution that is quicker to market and lower in cost.

#### **Features**

- Scaleable Bandwidth: 25 165MHz Flexible

- Graphics Controller Interface: 12-bit or 24-bit mode 1 pixel/clock inputs

- Flexible Input Clocking: Single clock single edge (24-bit), Single clock dual edge (12-/24bit), Dual clock single edge (12-bit)

- I<sup>2</sup>C Slave Programming Interface up to 100kHz

- Low Voltage Interface: 3.3V with option for 1.0 to 3.0V Low Voltage Signal Mode

- Monitor Detection supported through hot plug and receiver detection

- De-skewing Option varies input clock to input data timing

- Low Power: 3.3V operation (120mA max.) and Power Down mode (1mA max.)

- Cable Distance Support: over 5m with twisted pair and fiber-optics ready

- Compliant with DVI 1.0 (DVI is backwards compliant with VESA® P&D™ and DFP)

- Standard and Pb-free packages (see pg 29)

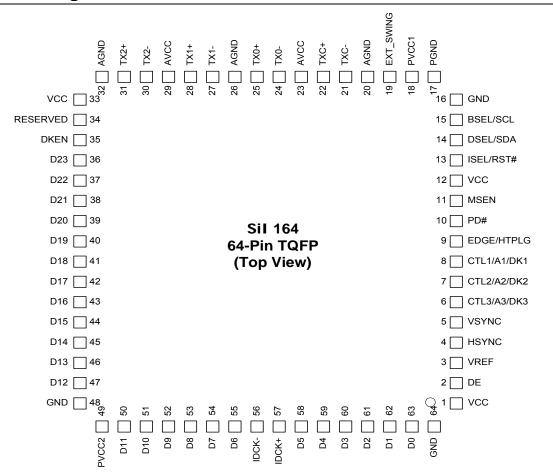

### Sil 164 Pin Diagram

Figure 1. Pin Diagram for SiI 164

## **Functional Description**

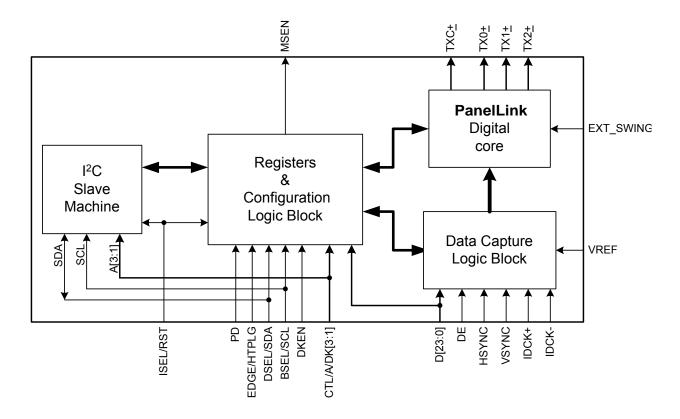

The SiI 164 is a DVI 1.0 compliant PanelLink transmitter in a compact package. It provides 24-bit data Input to allow for panel support up to UXGA resolution. Figure 2 shows the functional blocks of the chip.

Figure 2. Functional Block Diagram

### **PanelLink TMDS Digital Core**

The PanelLink TMDS core encodes video information onto three TMDS differential data lines and the differential clock. The video data is input by the Data Capture Logic Block, as a 12- or 24-bit bus, using one or two clocks with one or two edges per clock. An attached monitor may be sensed using the HTPLG pin or internally with Receiver Sense. This detected state may be output onto the MSEN pin. The device may be powered down using the PD# pin or with an internal register. The SiI 164 is reset using the ISEL/RST# pin. A resistor tied to the EXT\_SWING pin is used to control the TMDS swing amplitude.

# I<sup>2</sup>C Interface and Registers

The SiI 164 uses a slave I<sup>2</sup>C interface, capable of running at 100kHz. The slave I<sup>2</sup>C interface is not 5V tolerant. If the switching levels from the host are not 3.3V, then a voltage level shifter must be used. See Figure 16 and Figure 17 on page 24 for a system diagram.

A connected display may be detected using the DVI Hot Plug signal, attached to the HTPLG pin; or with the Receiver Sense logic internal to the SiI 164. The state of the detection, or an interrupt signal indicating a change of state, may be sent to the MSEN pin. This is useful to the host controller monitoring the SiI 164.

#### **Data Capture Logic**

Video data is input to the SiI 164 by way of a 12-bit or 24-bit interface. The functionality of this interface is affected by several of the configuration register settings, as follows.

- BSEL selects between 12-bit and 24-bit input bus widths.

- DSEL selects between single-edge and dual-edge modes for the input clocks.

- EDGE selects between rising and falling edge on the input clocks.

- CLK+ and CLK- provide the one or two clocks required for latching the input data bus.

- The PD# input selects the chip power down mode and allows for disabling of the TMDS outputs.

The ISEL/RST# input resets the HDCP engine and internal registers and is asserted after power up and receipt of a stable input pixel clock.

3

## **Electrical Specifications**

#### **Absolute Maximum Conditions**

Absolute Maximum Conditions are defined as the worst-case conditions the part will tolerate without sustaining damage. Permanent device damage may occur if absolute maximum conditions are exceeded. Proper operation under these conditions is not guaranteed. Functional operation should be restricted to the conditions described under Normal Operating Conditions.

| Symbol           | Parameter                                 | Min  | Тур | Max                   | Units |

|------------------|-------------------------------------------|------|-----|-----------------------|-------|

| $V_{CC}$         | Supply Voltage 3.3V                       | -0.3 |     | 4.0                   | V     |

| $V_{l}$          | Input Voltage                             | -0.3 |     | V <sub>CC</sub> + 0.3 | V     |

| Vo               | Output Voltage                            | -0.3 |     | V <sub>CC</sub> + 0.3 | V     |

| $T_J$            | Junction Temperature (with power applied) |      |     | 125                   | °C    |

| T <sub>STG</sub> | Storage Temperature                       | -65  |     | 150                   | °C    |

#### **Normal Operating Conditions**

| Symbol            | Parameter                                             | Min | Тур | Max | Units      |

|-------------------|-------------------------------------------------------|-----|-----|-----|------------|

| $V_{CC}$          | Supply Voltage                                        | 3.0 | 3.3 | 3.6 | V          |

| V <sub>CCN</sub>  | Supply Voltage Noise                                  |     |     | 100 | $mV_{P-P}$ |

| T <sub>A</sub>    | Ambient Temperature (with power applied)              | 0   | 25  | 70  | °C         |

| $\theta_{JA}$     | Thermal Resistance (Junction to Ambient) <sup>1</sup> |     |     | 64  | °C/W       |

| $\theta_{\sf JC}$ | Thermal Resistance (Junction to Case) <sup>1</sup>    |     |     | 20  | °C/W       |

#### Note

#### **Digital I/O Specifications**

Under normal operating conditions unless otherwise specified.

| Symbol            | Parameter                             | Conditions                         | Min                         | Тур | Max                            | Units |

|-------------------|---------------------------------------|------------------------------------|-----------------------------|-----|--------------------------------|-------|

| V <sub>IH</sub>   | High Swing High-level Input Voltage   | V <sub>REF</sub> = V <sub>CC</sub> | 2.0                         |     |                                | V     |

| V <sub>IL</sub>   | High Swing Low-level Input Voltage    | V <sub>REF</sub> = V <sub>CC</sub> |                             |     | 0.8                            | ٧     |

| $V_{\rm DDQ}^{2}$ | Low Swing Voltage                     |                                    | 1                           |     | 3.0                            | V     |

| $V_{SH}$          | Low Swing High-level Input<br>Voltage | $V_{REF} = V_{DDQ}/2$              | V <sub>DDQ</sub> /2 + 300mV |     |                                | V     |

| $V_{SL}$          | Low Swing Low-level Input<br>Voltage  | $V_{REF} = V_{DDQ}/2$              |                             |     | V <sub>DDQ</sub> /2 –<br>100mV | V     |

| $V_{CINL}$        | Input Clamp Voltage <sup>1</sup>      | I <sub>CL</sub> = -18mA            |                             |     | GND -0.8                       | V     |

| $V_{CIPL}$        | Input Clamp Voltage <sup>1</sup>      | I <sub>CL</sub> = 18mA             |                             |     | VCC + 0.8                      | ٧     |

| I <sub>IL</sub>   | Input Leakage Current                 |                                    | -10                         |     | 10                             | μА    |

| V <sub>IH</sub>   | High Swing High-level Input Voltage   | V <sub>REF</sub> = V <sub>CC</sub> | 2.0                         |     |                                | V     |

#### Notes

1. Guaranteed by design. Voltage undershoot or overshoot cannot exceed absolute maximum conditions

VDDQ defines the maximum voltage level of Low Swing input. It is not an actual input voltage. Chip characterization for Low Swing operation is performed at 1.5V only. Voltage level of Low Swing input should never exceed absolute maximum rating.

PanelLink®

<sup>1.</sup> Airflow at 0m/s.

### **DC Specifications**

Under normal operating conditions unless otherwise specified.

| Symbol           | Parameter                                                | Conditions                                                                                                 | Min | Тур             | Max              | Units |

|------------------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|-----------------|------------------|-------|

| V <sub>OD</sub>  | Differential Voltage Single ended peak to peak amplitude | $R_{LOAD} = 50\Omega$ , $R_{EXT\_SWING} = 510\Omega$                                                       | 510 | 550             | 590              | mV    |

| $V_{DOH}$        | Differential High-level Output Voltage <sup>1</sup>      |                                                                                                            |     | AVCC            |                  | V     |

| I <sub>DOS</sub> | Differential Output Short Circuit Current <sup>1</sup>   | V <sub>OUT</sub> = 0 V                                                                                     |     |                 | 5                | μА    |

| I <sub>PD#</sub> | Power-down Current <sup>2</sup>                          |                                                                                                            |     | 0.2             | 1.0              | mA    |

| I <sub>CCT</sub> | Transmitter Supply Current                               | IDCK= 165 MHz, 1-pixel/clock<br>mode, $R_{EXT\_SWING}$ = 510 $\Omega$ ,<br>Worst Case Pattern <sup>3</sup> |     | 85 <sup>4</sup> | 120 <sup>5</sup> | mA    |

5

#### Notes

- 1. Guaranteed by design.

- 2. Assumes all inputs to the transmitter are not toggling.

- 3. Black and white checkerboard pattern, each checker is one pixel wide.

- 4. Measurement taken at VCC = 3.30V.

- 5. Measurement taken at VCC = 3.60V.

### **AC Specifications**

Under normal operating conditions unless otherwise specified.

| Symbol              | Parameter                                                                                             | Conditions                                                  | Min                 | Тур | Max                  | Units    | Figure   |

|---------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|---------------------|-----|----------------------|----------|----------|

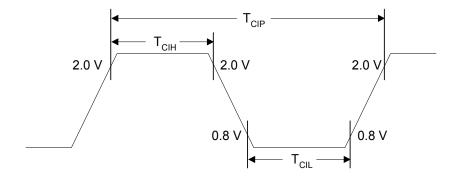

| T <sub>CIP</sub>    | IDCK Period, 1-pixel/clock                                                                            |                                                             | 6                   |     | 40                   | ns       | Figure 3 |

| F <sub>CIP</sub>    | IDCK Frequency, 1-pixel/clock                                                                         |                                                             | 25                  |     | 165                  | MHz      |          |

| T <sub>CIH</sub>    | IDCK High Time at 165MHz                                                                              |                                                             | 2.0                 |     |                      | ns       | Figure 3 |

| T <sub>CIL</sub>    | IDCK Low Time at 165MHz                                                                               |                                                             | 2.0                 |     |                      | ns       | Figure 3 |

| T <sub>IJIT</sub>   | Worst Case IDCK Clock Jitter <sup>2,3</sup>                                                           |                                                             |                     |     | 2                    | ns       |          |

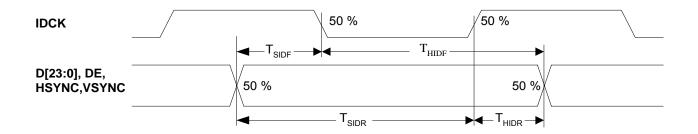

| T <sub>SIDF</sub>   | Data, DE, VSYNC, HSYNC Setup Time to IDCK falling edge (Default De-skew Setting)                      | Single Edge<br>(DSEL = 0,<br>EDGE = 0)                      | 1.0                 |     |                      | ns       | Figure 6 |

| T <sub>HIDF</sub>   | Data, DE, VSYNC, HSYNC Hold Time from IDCK falling edge (Default De-skew Setting)                     | Single Edge<br>(DSEL = 0,<br>EDGE = 0)                      | 0.9                 |     |                      | ns       | Figure 6 |

| T <sub>SIDR</sub>   | Data, DE, VSYNC, HSYNC Setup Time to IDCK rising edge <sup>1</sup> (Default De-skew Setting)          | Single Edge<br>(DSEL = 0,<br>EDGE = 1)                      | 1.0                 |     |                      | ns       | Figure 6 |

| T <sub>HIDR</sub>   | Data, DE, VSYNC, HSYNC Hold Time from IDCK rising edge <sup>1</sup> (Default De-skew Setting)         | Single Edge<br>(DSEL = 0,<br>EDGE = 1)                      | 0.9                 |     |                      | ns       | Figure 6 |

| T <sub>SID</sub>    | Data, DE, VSYNC, HSYNC Setup Time to IDCK falling/rising edge <sup>1</sup> (Default De-skew Setting)  | Dual Edge<br>(DSEL = 1,<br>BSEL = 0)                        | 0.6                 |     |                      | ns       |          |

| T <sub>HID</sub>    | Data, DE, VSYNC, HSYNC Hold Time from IDCK falling/rising edge <sup>1</sup> (Default De-skew Setting) | Dual Edge<br>(DSEL = 1,<br>BSEL = 0)                        | 1.3                 |     |                      | ns       |          |

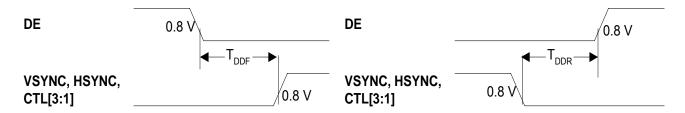

| $T_{DDF}$           | VSYNC, HSYNC Delay from DE falling edge <sup>1</sup>                                                  |                                                             | 1T <sub>CIP</sub>   |     |                      | ns       | Figure 7 |

| $T_DDR$             | VSYNC, HSYNC Delay to DE rising edge <sup>1</sup>                                                     |                                                             | 1T <sub>CIP</sub>   |     |                      | ns       | Figure 7 |

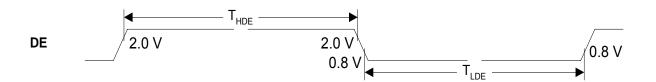

| T <sub>HDE</sub>    | DE high time <sup>1</sup>                                                                             |                                                             |                     |     | 8191T <sub>CIP</sub> | ns       | Figure 8 |

| T <sub>LDE</sub>    | DE low time <sup>1</sup>                                                                              |                                                             | 128T <sub>CIP</sub> |     |                      | ns       | Figure 8 |

| T <sub>STEP</sub>   | De-skew step size increment                                                                           | DKEN = 0b1                                                  |                     | 260 |                      | ps       |          |

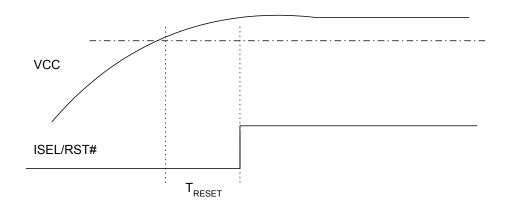

| T <sub>RESET</sub>  | Duration of RESET signal Low required for valid Reset                                                 |                                                             | 10                  |     |                      | μs       | Figure 5 |

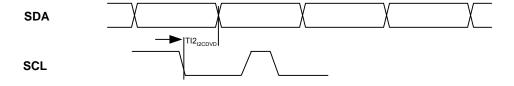

| T <sub>I2CDVD</sub> | SDA Data Valid Delay from SCL high to low transition <sup>3</sup>                                     | $C_L = 10pf$<br>$C_L = 400pf$                               |                     |     | 700<br>2000          | ns<br>ns | Figure 9 |

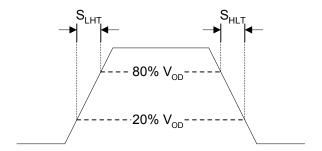

| S <sub>HLT</sub>    | Differential Swing High-to-Low Transition Time                                                        | $R_{LOAD} = 50\Omega$ ,<br>$R_{EXT\_SWING} = 510\Omega$     | 170                 | 200 | 230                  | ps       | Figure 4 |

| S <sub>LHT</sub>    | Differential Swing Low-to-High Transition Time                                                        | $R_{LOAD} = 50\Omega,$<br>$R_{EXT\_SWING} =$<br>$510\Omega$ | 170                 | 200 | 230                  | ps       | Figure 4 |

#### Notes

- 1. Guaranteed by design.

- 2. Actual jitter tolerance may be higher depending on the frequency of the jitter.

- 3. All Standard mode I<sup>2</sup>C (100kHz) timing requirements are guaranteed by design. Fast mode I<sup>2</sup>C (400kHz) timing requirements are guaranteed at 10pf loading.

### **Input Timing Diagrams**

Figure 3. Clock Cycle High/Low Times

**Figure 4. Low Swing Differential Times**

Figure 5. ISEL/RST# Minimum Timing

Figure 6. Input Data Setup/Hold Time to IDCK

Figure 7. VSYNC, HSYNC and CTL[3:1] Delay Time from DE

Figure 8. DE High and Low Times

Figure 9. I<sup>2</sup>C Data Valid Delay (driving Read Cycle data)

8

# **Pin Descriptions**

# **Input Pins**

| Din Name    | D: "  | T    | Presiden                                                                                                                                                                                                 |

|-------------|-------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name    | Pin#  | Type | Description                                                                                                                                                                                              |

| D[23:12]    | 36-47 | In   | Top half of 24-bit pixel bus.                                                                                                                                                                            |

|             |       |      | When BSEL = HIGH,                                                                                                                                                                                        |

|             |       |      | this bus inputs the top half of the 24-bit pixel bus.                                                                                                                                                    |

|             |       |      | When BSEL = LOW,                                                                                                                                                                                         |

|             |       |      | these bits are not used to input pixel data. In this mode, the state of D[23:16] is input to the I <sup>2</sup> C register CFG. This allows 8-bits of user configuration data to be read by the graphics |

|             |       |      | controller through the 1 <sup>2</sup> C interface (see 1 <sup>2</sup> C register definition). When not used D[23:16]                                                                                     |

|             |       |      | should be tied to ground. D[15:12] are reserved for SiI use only and should be tied to GND.                                                                                                              |

| D(44.01     |       |      | Bottom half of 24-bit pixel bus / 12-bit pixel bus input.                                                                                                                                                |

| D[11:0]     | 50-   | In   | When <b>BSEL = HIGH</b> .                                                                                                                                                                                |

|             | 55,   |      | this bus inputs the bottom half of the 24-bit pixel bus.                                                                                                                                                 |

|             | 58-63 |      | When BSEL = LOW,                                                                                                                                                                                         |

|             |       |      | this bus inputs ½ a pixel (12-bits) at every latch edge (both falling and/or rising) of the clock.                                                                                                       |

| IDCK+       | 57    | In   | Input Data Clock +. This clock is used for all input modes.                                                                                                                                              |

|             |       |      | 1                                                                                                                                                                                                        |

| IDCK-       | 56    | In   | Input Data Clock –. This clock is only used in 12-bit mode when dual edge clocking is turned off (DSEL = LOW). It is used to provide the ODD latching edges for dual clock single edge.                  |

|             |       |      | If BSEL = HIGH or DSEL = HIGH.                                                                                                                                                                           |

|             |       |      | this pin is unused and should be tied to GND.                                                                                                                                                            |

| DE          | 2     | In   | Input Data Enable. This signal qualifies the active data area. DE is always required by the                                                                                                              |

| DE          | _     | 111  | transmitter and must be high during active display time and low during blanking time.                                                                                                                    |

| HSYNC       | 4     | In   | Horizontal Sync input control Signal                                                                                                                                                                     |

| VSYNC       | 5     | In   | Vertical Sync input control signal.                                                                                                                                                                      |

|             | -     |      | , ,                                                                                                                                                                                                      |

| CTL1/A1/DK1 | 8     | In   | The use of these multi-function inputs depends on the settings of ISEL/RST# and DKEN.                                                                                                                    |

| CTL2/A2/DK2 | 7     |      | These inputs are regular high-swing 3.3V CMOS level inputs. These pins contain weak pull-down resistors so that if left unconnected, they will be LOW.                                                   |

| CTL3/A3/DK3 | 6     |      | When ISEL/RST# = LOW, DKEN = LOW                                                                                                                                                                         |

|             |       |      | General Purpose Input CTL[3:1] pins are active, for backward compatibility. These pins must                                                                                                              |

|             |       |      | be used to send DC signals only during the blanking time.                                                                                                                                                |

|             |       |      | When ISEL/RST# = LOW, DKEN = HIGH                                                                                                                                                                        |

|             |       |      | DK[3:1] are active, these inputs are used to select the De-skewing setting for the input bus.                                                                                                            |

|             |       |      | When ISEL/RST# = HIGH, DKEN = HIGH                                                                                                                                                                       |

|             |       |      | A[3:1] are active, these bits are used to set the lower 3 bits of the I <sup>2</sup> C device address.                                                                                                   |

# Pin Descriptions (cont'd)

# **Configuration Pins**

| Pin Name  | Pin# | Туре   | Description                                                                                                                                                                                                                    |

|-----------|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MSEN      | 11   | Out    | Monitor Sense. This pin is an open collector output. The behavior of this output depends on                                                                                                                                    |

|           |      |        | whether I <sup>2</sup> C interface active:                                                                                                                                                                                     |

|           |      |        | I <sup>2</sup> C bus inactive (ISEL/RST# = LOW)                                                                                                                                                                                |

|           |      |        | HIGH level indicates a powered on receiver is detected at the differential outputs.                                                                                                                                            |

|           |      |        | A LOW level indicates a powered on receiver is not detected.                                                                                                                                                                   |

|           |      |        | I <sup>2</sup> C bus is enabled (ISEL/RST# = HIGH)                                                                                                                                                                             |

|           |      |        | The output is programmable through the I <sup>2</sup> C interface (see I <sup>2</sup> C Register Definitions).                                                                                                                 |

|           |      |        | An external 5K pull-up resistor to VDDQ is required on this pin.                                                                                                                                                               |

| ISEL/RST# | 13   | In     | I <sup>2</sup> C Interface Select.                                                                                                                                                                                             |

|           |      |        | ISEL/RST#=HIGH,                                                                                                                                                                                                                |

|           |      |        | I <sup>2</sup> C interface is active.                                                                                                                                                                                          |

|           |      |        | ISEL/RST#=LOW,                                                                                                                                                                                                                 |

|           |      |        | I <sup>2</sup> C is inactive and the chip configuration is read from the configuration strapping pins. This pin also acts as an asynchronous reset to the I <sup>2</sup> C interface controller. The reset is active when this |

|           |      |        | input is held LOW.                                                                                                                                                                                                             |

|           |      |        | <b>Note</b> : When the I <sup>2</sup> C interface is active, DKEN must be set HIGH.                                                                                                                                            |

| BSEL/SCL  | 15   | In     | Input bus select / I <sup>2</sup> C clock. This pin is an open collector input. If I <sup>2</sup> C bus is enabled                                                                                                             |

| BSEL/SCL  | 15   | III    | (ISEL/RST# = HIGH), then this pin is the $I^2$ C clock input. If the $I^2$ C is disabled (ISEL/RST# =                                                                                                                          |

|           |      |        | LOW), then this pin selects the input bus width.                                                                                                                                                                               |

|           |      |        | Input Bus Select:                                                                                                                                                                                                              |

|           |      |        | HIGH selects 24-bit input mode                                                                                                                                                                                                 |

|           |      |        | LOW selects 12-bit input mode                                                                                                                                                                                                  |

| DSEL/SDA  | 14   | In/Out | Dual edge clock select / I <sup>2</sup> C Data. This pin is an open collector input/output. If I <sup>2</sup> C bus is                                                                                                         |

|           |      |        | enabled (ISEL/RST# = HIGH), then this pin is the $I^2$ C data line. If the $I^2$ C bus is disabled                                                                                                                             |

|           |      |        | (ISEL/RST# = LOW), then this pin selects whether single clock dual edge is used.                                                                                                                                               |

|           |      |        | Dual Edge clock select:                                                                                                                                                                                                        |

|           |      |        | When HIGH, IDCK+ latches input data on both falling and rising clock edges.                                                                                                                                                    |

|           |      |        | When LOW, IDCK+/IDCK- latches input data on only falling or rising clock edges.                                                                                                                                                |

|           |      |        | In 24-/12-bit mode:                                                                                                                                                                                                            |

|           |      |        | If HIGH (dual edge), IDCK+ is used to latch data on both falling and rising edges.                                                                                                                                             |

|           |      |        | If LOW (single edge), IDCK+ latches 1 <sup>st</sup> half data and IDCK- latches 2 <sup>nd</sup> half data.  Edge select / Hot Plug input. If the I <sup>2</sup> C bus is enabled (ISEL/RST# = HIGH), then this pin is          |

| EDGE/     | 9    | In     | used to monitor the "Hot Plug" detect signal (Please refer to the DVI <sup>TM</sup> or VESA <sup>®</sup> P&D <sup>TM</sup> and                                                                                                 |

| HTPLG     |      |        | DFP standards). This Input is ONLY 3.3V tolerant and has no internal de-bouncer circuit.                                                                                                                                       |

|           |      |        | If I <sup>2</sup> C bus is disabled (ISEL/RST# = LOW), then this pin selects the clock edge that will latch                                                                                                                    |

|           |      |        | the data. How the EDGE setting works depends on whether dual or single edge latching is                                                                                                                                        |

|           |      |        | selected:                                                                                                                                                                                                                      |

|           |      |        | Dual Edge Mode (DSEL = HIGH)                                                                                                                                                                                                   |

|           |      |        | EDGE = LOW, the primary edge (first latch edge after DE is asserted) is the falling edge.                                                                                                                                      |

|           |      |        | EDGE = HIGH, the primary edge (first latch edge after DE is asserted) is the rising edge.                                                                                                                                      |

|           |      |        | Note: In 24-bit Single Clock Dual Edge mode, EDGE is ignored.                                                                                                                                                                  |

|           |      |        | Single Edge Mode (DSEL = LOW)                                                                                                                                                                                                  |

|           |      |        | EDGE = LOW, the falling edge of the clock is used to latch data.                                                                                                                                                               |

|           |      |        | EDGE = HIGH, the rising edge of the clock is used to latch data.                                                                                                                                                               |

| DKEN      | 35   | In     | De-skewing enable.                                                                                                                                                                                                             |

|           |      |        | I <sup>2</sup> C mode (ISEL/RST# = HIGH)                                                                                                                                                                                       |

|           |      |        | DKEN pin must be set to HIGH. DK[3:1] pins are ignored and the De-skewing increments are                                                                                                                                       |

|           |      |        | selected through the I <sup>2</sup> C interface (see the I <sup>2</sup> C register definitions).                                                                                                                               |

|           |      |        | Non I <sup>2</sup> C mode (ISEL/RST# = LOW)  DKEN = LOW, then default De-skewing setting is used.                                                                                                                              |

|           |      |        | DKEN = LOW, then default De-skewing setting is used.<br>  DKEN = HIGH, then DK[3:1] is used as the De-skewing setting. The De-skewing increments                                                                               |

|           |      |        | are T <sub>STEP</sub> . Please see Data De-skew Feature for an illustration.                                                                                                                                                   |

|           |      |        | are istep. I lease see Data De-skew i catale for all illustration.                                                                                                                                                             |

# Pin Descriptions (cont'd)

## **Input Voltage Reference Pin**

| Pin Name | Pin# | Туре      | Description                                                                                                                                                                                                                                                          |

|----------|------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VREF     | 3    | Analog In | Input Reference Voltage. Selects the Swing range of the digital inputs, which include only D[23:0], IDCK+, IDCK-, DE, VSYNC, and HSYNC. Input pins SCL and SDA, RST, BSEL, DSEL, EDGE and PD# require 3.3V high swing signals and are not changed by the VREF input. |

|          |      |           | To set the digital inputs to 3.3V High Voltage Swing, VREF must be set to 3.3V.                                                                                                                                                                                      |

|          |      |           | To set the digital inputs to Low Voltage Swing, VREF must be set to ½ of VDDQ where VDDQ is swing level of input signal. Thus for DVO mode (1.5V Low Voltage Swing) VREF should be set to 0.75V and BSEL=LOW.                                                        |

## **Power Management Pins**

| Pin Name | Pin# | Type | Description                                                                                                    |

|----------|------|------|----------------------------------------------------------------------------------------------------------------|

| PD#      | 10   | In   | Power Down (active LOW). A HIGH level indicates normal operation. A LOW level indicates                        |

|          |      |      | Power Down mode. In Power Down mode the Analog core is disabled and Output                                     |

|          |      |      | buffers/pins are tri-stated however the Input buffer/pins and I <sup>2</sup> C Block for read and write are    |

|          |      |      | active. PD# pin is disabled during I <sup>2</sup> C mode. PD# should be tied low during I <sup>2</sup> C mode. |

## **Differential Signal Data Pins**

| Pin Name  | Pin# | Type   | Description                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TX0+      | 25   | Analog | TMDS Low Voltage Differential Signal input data pairs.                                                                                                                                                                                                                                                                                                                                                                        |

| TX0-      | 24   | Analog |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX1+      | 28   | Analog | These pins are tri-stated when PD# is pulled low.                                                                                                                                                                                                                                                                                                                                                                             |

| TX1-      | 27   | Analog |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX2+      | 31   | Analog |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TX2-      | 30   | Analog |                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TXC+      | 22   | Analog | TMDS Low Voltage Differential Signal input clock pair.                                                                                                                                                                                                                                                                                                                                                                        |

| TXC-      | 21   | Analog | These pins are tri-stated when PD# is pulled low.                                                                                                                                                                                                                                                                                                                                                                             |

| EXT_SWING | 19   | Analog | Voltage Swing Adjust. A resistor should tie this pin to AVCC. This resistor sets the amplitude of the voltage swing. A smaller resistor value sets a larger voltage swing and vice versa. For remote display applications a $510\Omega$ with $\pm$ 5% (max) tolerance resistor is recommended. While for notebook computers $680\Omega$ is recommended to ensure voltage swing is not overdriven over a short cable distance. |

### **Reserved Pins**

| Pin Name | Pin# | Type | Description                                   |

|----------|------|------|-----------------------------------------------|

| RESERVED | 34   | In   | Must be tied <b>LOW</b> for normal operation. |

### **Power and Ground Pins**

| Pin Name | Pin #    | Type   | Description                                          |

|----------|----------|--------|------------------------------------------------------|

| VCC      | 1,12,33  | Power  | Digital VCC, must be set to 3.3V nominal.            |

| GND      | 16,48,64 | Ground | Digital GND.                                         |

| AVCC     | 23,29    | Power  | Analog VCC, must be set to 3.3V nominal.             |

| AGND     | 20,26,32 | Ground | Analog GND.                                          |

| PVCC1    | 18       | Power  | Primary PLL Analog VCC, must be set to 3.3V nominal. |

| PVCC2    | 49       | Power  | Filter PLL Analog VCC, must be set to 3.3V nominal.  |

| PGND     | 17       | Ground | PLL Analog GND.                                      |

# I<sup>2</sup>C Registers

## I<sup>2</sup>C Register Mapping

| Addr | Reset<br>Value | Bit 7 | Bit 6          | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1 | Bit 0 |  |

|------|----------------|-------|----------------|-------|-------|--------|----------|-------|-------|--|

| 0x00 | 0x01           |       | VND_IDL        |       |       |        |          |       |       |  |

| 0x01 | 0x00           |       |                |       | VN    | ID_IDH |          |       |       |  |

| 0x02 | 0x06           |       |                |       | DE    | EV_IDL |          |       |       |  |

| 0x03 | 0x00           |       |                |       | DE    | V_IDH  |          |       |       |  |

| 0x04 | 0x00           |       |                |       | DE    | V_REV  |          |       |       |  |

| 0x05 | 0x00           |       |                |       | F     | RSVD   |          |       |       |  |

| 0x06 | 0x19           |       | FRQ_LOW        |       |       |        |          |       |       |  |

| 0x07 | 0x64           |       | FRQ_HIGH       |       |       |        |          |       |       |  |

| 0x08 | 00•••0         | RS    | VD             | VEN   | HEN   | DSEL   | BSEL     | EDGE  | PD#   |  |

| 0x09 | •000<br>0••0   | RSVD  |                | MSEL  |       | TSEL   | RSEN     | HTPLG | MDI   |  |

| 0x0A | 0x90           |       | DK[3:1]        |       | DKEN  |        | CTL[3:1] |       | RSVD  |  |

| 0x0B | ••••           |       | CFG[7:0]       |       |       |        |          |       |       |  |

| 0x0C | •••0           | SCNT  | RSVD PLLF[3:0] |       |       |        |          | PFEN  |       |  |

| 0x0D | 0x80           |       |                |       | F     | RSVD   |          |       |       |  |

| 0x0E | 0x00           |       |                |       | F     | RSVD   |          |       | _     |  |

| 0x0F | 0x00           |       |                |       | F     | RSVD   |          |       |       |  |

#### Notes

- 1. All values are Bit 7 [MSB] and Bit 0 [LSB].

- 2. Bits and registers **bold like this** are read only. All others are Read/Write.

- 3. Bits and registers in italics and bold like this are undefined after RESET, although they are accessible by read or write.

- 4. RSVD is a reserved register or bit field. It is available for future use by Silicon Image. All RSVD fields are read-only and are not affected by data written to them.

- 5. 0x0C is also called the **VDJK** Register. Default setting for the VDJK register 0x0C is 0x89, which is optimum for most applications.

I<sup>2</sup>C Reset values are shown in the column at the left of the table. Bits or registers which have no default value after power-on, or which have no defined value after RESET, are shown with the symbol ● in the table. All registers Hexadecimal values use a prefix of '0x'. Binary values use a prefix of '0b'. To enable the device, registers 0x08, 0x09, 0x0A and 0x0C must be programmed. A sample programming sequence is listed on page 18 for 12-bit mode.

# I<sup>2</sup>C Register Definitions

| i C Register  |        |                                                                                  |  |  |  |  |  |

|---------------|--------|----------------------------------------------------------------------------------|--|--|--|--|--|

| Register Name | Access | Description                                                                      |  |  |  |  |  |

| VND_IDL       | RO     | Vendor ID Low byte (01h)                                                         |  |  |  |  |  |

| VND_IDH       | RO     | Vendor ID High byte (00h)                                                        |  |  |  |  |  |

| DEV_IDL       | RO     | Device ID Low byte (06h)                                                         |  |  |  |  |  |

| DEV_IDH       | RO     | Device ID High byte (00h)                                                        |  |  |  |  |  |

| DEV_REV       | RO     | Device Revision (00h)                                                            |  |  |  |  |  |

| FRQ LOW       | RO     | ow frequency limit at 1-pixel/clock mode (MHz) (19h)                             |  |  |  |  |  |

| FRQ_HIGH      | RO     | High frequency limit at 1-pixel/clock mode Max frequency minus 65MHz (MHz) (64h) |  |  |  |  |  |

| PD            | RW     | Power Down mode (same function as PD# pin)                                       |  |  |  |  |  |

|               |        | 0 – Power Down (Default after RESET)                                             |  |  |  |  |  |

|               |        | 1 – Normal operation                                                             |  |  |  |  |  |

| EDGE          | RW     | Edge Select (same function as EDGE pin)                                          |  |  |  |  |  |

|               |        | 0 – Input data is falling edge latched (falling edge latched first in dual edge  |  |  |  |  |  |

|               |        | mode)                                                                            |  |  |  |  |  |

|               |        | 1 – Input data is rising edge latched (rising edge latched first in dual edge    |  |  |  |  |  |

|               |        | mode)                                                                            |  |  |  |  |  |

| BSEL          | RW     | Input Bus Select (same function as BSEL pin)                                     |  |  |  |  |  |

| 2022          |        | 0 – Input data bus is 12-bits wide                                               |  |  |  |  |  |

|               |        | 1 – Input data bus is 24-bits wide                                               |  |  |  |  |  |

| DSEL          | RW     | Dual Edge Clock Select (same function as DSEL pin)                               |  |  |  |  |  |

|               |        | 0 – Input data is single edge latched                                            |  |  |  |  |  |

|               |        | 1 – Input data is dual edge latched                                              |  |  |  |  |  |

| HEN           | RW     | Horizontal Sync Enable:                                                          |  |  |  |  |  |

|               |        | 0 – HSYNC input is transmitted as fixed LOW                                      |  |  |  |  |  |

|               |        | 1 – HSYNC input is transmitted as is                                             |  |  |  |  |  |

| VEN           | RW     | Vertical Sync Enable:                                                            |  |  |  |  |  |

|               |        | 0 – VSYNC input is transmitted as fixed LOW                                      |  |  |  |  |  |

|               |        | 1 – VSYNC input is transmitted as is                                             |  |  |  |  |  |

| MDI           | RW     | Monitor Detect Interrupt                                                         |  |  |  |  |  |

|               |        | 0 – Detection signal has changed logic level (write one to this bit to clear)    |  |  |  |  |  |

|               |        | 1 – Detection signal has not changed state                                       |  |  |  |  |  |

| HTPLG         | RO     | Hot Plug Detect input, the state of HTPLG pin can be read from this bit          |  |  |  |  |  |

| RSEN          | RO     | Receiver Sense (only available for use in DC coupled systems)                    |  |  |  |  |  |

|               |        | 0 – Active/Powered Receiver not detected                                         |  |  |  |  |  |

|               |        | 1 – Active/Powered Receiver detected                                             |  |  |  |  |  |

| TSEL          | RW     | Interrupt Generation Method                                                      |  |  |  |  |  |

|               |        | 0 – Interrupt bit (MDI) is generated by monitoring RSEN                          |  |  |  |  |  |

|               |        | 1 – Interrupt bit (MDI) is generated by monitoring HTPLG                         |  |  |  |  |  |

| MSEL[2:0]     | RW     | Select source of the MSEN output pin                                             |  |  |  |  |  |

|               |        | 000 – Force MSEN outputs high (disabled – default after RESET)                   |  |  |  |  |  |

|               |        | 001 – Outputs the MDI bit (interrupt)                                            |  |  |  |  |  |

|               |        | 010 – Output the RSEN bit (receiver sense detect)                                |  |  |  |  |  |

|               |        | 011 – Outputs the HTPLG bit (hotplug detect)                                     |  |  |  |  |  |

|               |        | 1xx – RESERVED                                                                   |  |  |  |  |  |

| VLOW          | RO     | VREF setting                                                                     |  |  |  |  |  |

|               |        | 1 – Indicates High Swing Input Mode                                              |  |  |  |  |  |

|               |        | 0 – Indicates Low Swing Input Mode                                               |  |  |  |  |  |

| CTL[3:1]      | RW     | General purpose inputs (same as CTL[3:1] pins). These bits are only transmitted  |  |  |  |  |  |

|               |        | during blanking period.                                                          |  |  |  |  |  |

13

# I<sup>2</sup>C Register Definitions (cont'd)

| Register Name | Access | Description                                                                                                                                                                                                   |  |  |  |

|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CFG[7:0]      | RO     | Contains state of inputs D[23:16]. These pins can be used to provide user selectable configuration data through the I <sup>2</sup> C bus. Only available in 12-bit mode                                       |  |  |  |

| PFEN          | RW     | PLL Filter Enable in the VDJK Register 0x0C.                                                                                                                                                                  |  |  |  |

|               |        | 1 – To enable PLL Filter (recommended setting)                                                                                                                                                                |  |  |  |

|               |        | 0 – To disable PLL Filter                                                                                                                                                                                     |  |  |  |

| PLLF[3:1]     | RW     | Set characteristics of PLL filter in VDJK Register 0x0C.                                                                                                                                                      |  |  |  |

|               |        | 100 – Recommended value                                                                                                                                                                                       |  |  |  |

|               |        | All other values are not recommended.                                                                                                                                                                         |  |  |  |

| SCNT          | RW     | SYNC Continuous                                                                                                                                                                                               |  |  |  |

|               |        | 1 – To enable (recommended setting)                                                                                                                                                                           |  |  |  |

|               |        | 0 – To disable                                                                                                                                                                                                |  |  |  |

| DK[3:1]       | RW     | De-skewing Setting. Increment 260psec.                                                                                                                                                                        |  |  |  |

|               |        | 000 – 1 step -> minimum setup / maximum hold                                                                                                                                                                  |  |  |  |

|               |        | 001 – 2 step                                                                                                                                                                                                  |  |  |  |

|               |        | 010 – 3 step                                                                                                                                                                                                  |  |  |  |

|               |        | 011 – 4 step                                                                                                                                                                                                  |  |  |  |

|               |        | 100 – 5 step -> default (recommended setting)                                                                                                                                                                 |  |  |  |

|               |        | 101 – 6 step                                                                                                                                                                                                  |  |  |  |

|               |        | 110 – 7 step                                                                                                                                                                                                  |  |  |  |

|               |        | 111 – 8 step -> maximum setup / minimum hold                                                                                                                                                                  |  |  |  |

|               |        | Please see Data De-Skew Feature for an illustration                                                                                                                                                           |  |  |  |

| DKEN          | RW     | De-skewing Enable through DK[3:1] bits. When DKEN pin is HIGH via pin or set to 1, then De-skew is enabled. When set to 0 De-skew is disabled. Please see Data Deskew Feature on page 16 for an illustration. |  |  |  |

#### I<sup>2</sup>C Slave Interface and Address

The Sil 164 slave state machine does not require an internal clock and support only byte read and write. Page mode is not supported. The 7-bit binary address of the  $I^2C$  machine is "0111  $A_3A_2A_1R$ " where R=1 sets a read operation while R=0 sets a write operation. Please see Figure 10 for a Byte Read operation and Figure 11 for a byte write operation. For more detailed information on  $I^2C$  protocols please refer to  $I^2C$  Bus Specification version 2.1 available from Philips Semiconductors Inc.

When ISEL/RST# = HIGH and DKEN = HIGH, pins 6,7,8 functions as A[3:1]. Each pin can be set to HIGH or LOW to select a desired  $I^2C$  address for the SiI 164. To set the SiI 164 to 0x72, tie pin 7 and 6 to ground and pull pin 8 to VCC via 2.2K resistor. The recommended setting is to tie pins 6,7 and 8 to ground to set "000" or address 0x70 in  $I^2C$  mode.

#### **Data De-skew Feature**

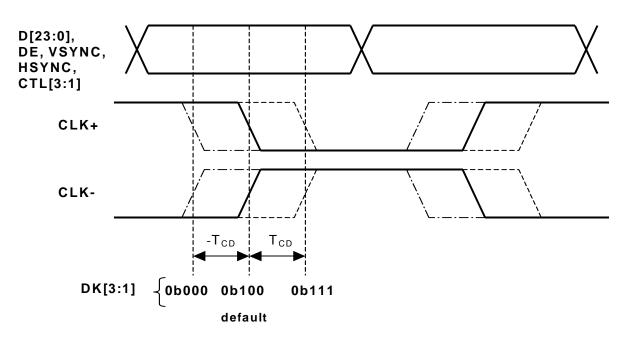

The de-skew feature allows adjustment of the clock-to-data delay on the input of the SiI 164. When driven by a chip with clock and data timings which do not meet the setup and hold time requirements of an SiI 164, the deskew register value can be modified to position the clock in the middle of the valid data time and meet the input setup and hold times. As shown in Figure 12, changing the DK[3:1] value from 0b100 to 0b111 delays the internal clock by approximately 750ps to 900ps, increasing setup time and reducing hold time. This is useful when the input clock, IDCK, arrives too early.

The default values for DK[3:1] are shown in Table 1, along with approximate times per setting. Note that the default is different when enabling  $I^2C$  mode (ISEL/RST#=HIGH) versus non- $I^2C$  mode (ISEL/RST#=LOW). Positive values of  $T_{CD}$  move the clock later, increasing setup time. Negative values of  $T_{CD}$  move the clock earlier, increasing hold time.

#### Where:

T<sub>CD</sub> is the amount of setup/hold timing variation DK[3:1] is the setting of the de-skew configuration pins or I<sup>2</sup>C registers

De-Skew Time DK[3:1]  $T_{CD}$ +0.75ns to +0.90ns 0b111 +0.50ns to +0.70ns 0b110 +0.20ns to +0.35ns 0b101 Default De-Skew 0b100 -0.20ns to -0.35ns 0b011 -0.50ns to -0.70ns 0b010 -0.75ns to -0.90ns 0b001 -1.0ns to -1.2ns 0b000

Table 1. Data De-Skew Estimated Values

Figure 12. Sil 164 Data De-skew Feature Timing

#### **Data Latching Modes**

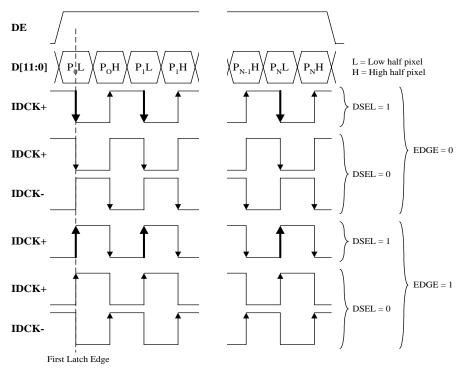

SiI 164 can be set to different to operate in either 12-bit or 24-bit input mode. In either mode the SiI 164 can be set to latch data at either rising or falling edge of the clock or support dual edge clocking mode. Figure 13 illustrates the latching edge for a 12-bit data input (**BSEL = 0**) by changing DSEL and EDGE option. Clock edges represented by arrows signify the latching edge. For Dual Edge mode, the dark arrows indicate the primary latch edge.

Figure 13. 12-bit Input Data Latching

Figure 14 illustrates the latching edge for a 24-bit data input (**BSEL=1**) with DSEL and EDGE option. EDGE pin has no affect in 24-bit Single Clock Dual Edge Mode.

Figure 14. 24-bit Input Data Latching

## I<sup>2</sup>C Programming Sequence

To program the SiI 164 in data latched on 12-bit mode Dual Edge Clock with Primary Edge as the rising edge or falling edge, De-skew enabled with Hotplug based monitor detection use the following sample programming sequence listed in Table 2. It is important to note that the suggested I<sup>2</sup>C address for SiI 164 be set to 0x70 by tying pins A1, A2 and A3 to ground.

Table 2. Sample Programming Sequence for SiI 164 in 12-bit Mode

| Register(Hex) | Value(Hex)                      | Description                                                                                                                                                                                                                                       |

|---------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x08          | Setting 1: 0x30 Setting 2: 0x32 | Setting 1: Enable HEN, VEN, 1 <sup>st</sup> data latched on falling edge with PD low until all registers are programmed.  Setting 2: Enable HEN, VEN, 1 <sup>st</sup> data latched on rising edge with PD low until all registers are programmed. |

| 0x09          | 0x30                            | Monitor detection mode via Hotplug input.                                                                                                                                                                                                         |

| 0x0A          | 0x90                            | De-skew enabled with default 100 value. CTL is not used.                                                                                                                                                                                          |