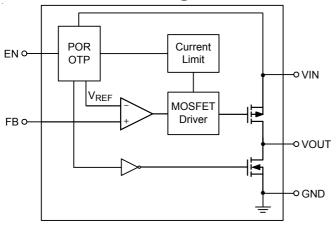

# **Function Block Diagram**

# **Functional Pin Description**

|                  |      | -                          |  |

|------------------|------|----------------------------|--|

| Pin No. Pin Name |      | Pin Function               |  |

| 1                | VIN  | Voltage Input.             |  |

| 2                | GND  | Ground.                    |  |

| 3                | EN   | Chip Enable (Active High). |  |

| 4                | FB   | Output Voltage Feedback.   |  |

| 5                | VOUT | Voltage Output.            |  |

# Absolute Maximum Ratings (Note 1)

| Supply Input Voltage, V <sub>IN</sub>                                       | 6V             |

|-----------------------------------------------------------------------------|----------------|

| • EN Input Voltage                                                          | 6V             |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| SOT-23-5                                                                    | 0.4W           |

| Package Thermal Resistance (Note 2)                                         |                |

| SOT-23-5, $\theta_{JA}$                                                     | 250°C/W        |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C          |

| • Junction Temperature                                                      | 150°C          |

| Storage Temperature Range                                                   | –65°C to 150°C |

| ESD Susceptibility (Note 3)                                                 |                |

| HBM                                                                         | 2kV            |

| MM                                                                          | 200V           |

# **Recommended Operating Conditions** (Note 4)

| • | Junction Temperature Range     | –40°C to | 125°C |

|---|--------------------------------|----------|-------|

|   | And blank Towns and the Dennis | 40004-   | 0500  |

3

## **Electrical Characteristics**

(V<sub>IN</sub> = 3.7V,  $C_{IN}$  =  $C_{OUT}$  = 1 $\mu$ F,  $I_{OUT}$  = 20mA,  $T_A$  = 25°C, unless otherwise specified)

| F                                     | Parameter          | Symbol            | Test Conditions                                                 | Min   | Тур   | Max   | Unit              |

|---------------------------------------|--------------------|-------------------|-----------------------------------------------------------------|-------|-------|-------|-------------------|

| Input Voltage Range                   |                    | V <sub>IN</sub>   |                                                                 | 2.2   | _     | 5.5   | V                 |

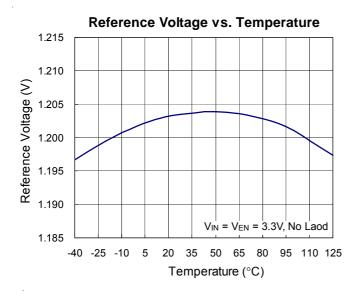

| Reference Voltage                     |                    | $V_{REF}$         |                                                                 | 1.188 | 1.200 | 1.212 | V                 |

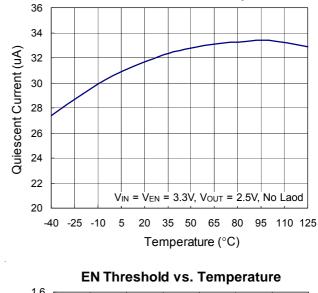

| Quiescent (                           | Current            | lQ                | I <sub>OUT</sub> = 0mA                                          |       | 35    | 50    | μΑ                |

| Shutdown C                            | Current            | I <sub>SHDN</sub> | V <sub>EN</sub> = 0V                                            |       | 0.7   | 1.5   | μA                |

| Current Lim                           | it                 | I <sub>LIM</sub>  | $R_{LOAD} = 0\Omega, 2.2V \le V_{IN} < 5.5V$                    | 400   | 650   |       | mA                |

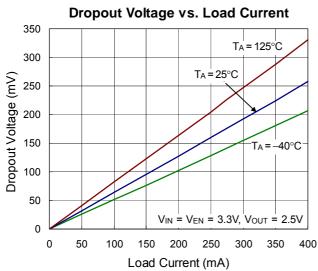

| Dropout Vo                            | ltage              | $V_{DROP}$        | I <sub>OUT</sub> = 400mA                                        |       | 230   | 350   | mV                |

| Load Regulation                       |                    | $\Delta V_{LOAD}$ | 1mA < I <sub>OUT</sub> < 400mA<br>2.2V ≤ V <sub>IN</sub> < 5.5V |       | _     | 1     | %                 |

| Line Regula                           | Line Regulation    |                   | $V_{IN} = (V_{OUT} + 0.5V)$ to 5.5V,<br>$I_{OUT} = 1mA$         |       | 0. 01 | 0.2   | %/V               |

| EN                                    | Logic-Low Voltage  | V <sub>IL</sub>   |                                                                 | 0     | -     | 0.6   | V                 |

| Threshold                             | Logic-High Voltage | V <sub>IH</sub>   |                                                                 | 1.6   | -     | 5.5   | V                 |

| EN Pin Cur                            | rent               | I <sub>EN</sub>   |                                                                 |       | 0.1   | 1     | μA                |

| FB Pin Current                        |                    | I <sub>FB</sub>   |                                                                 |       | 0.1   | 1     | μA                |

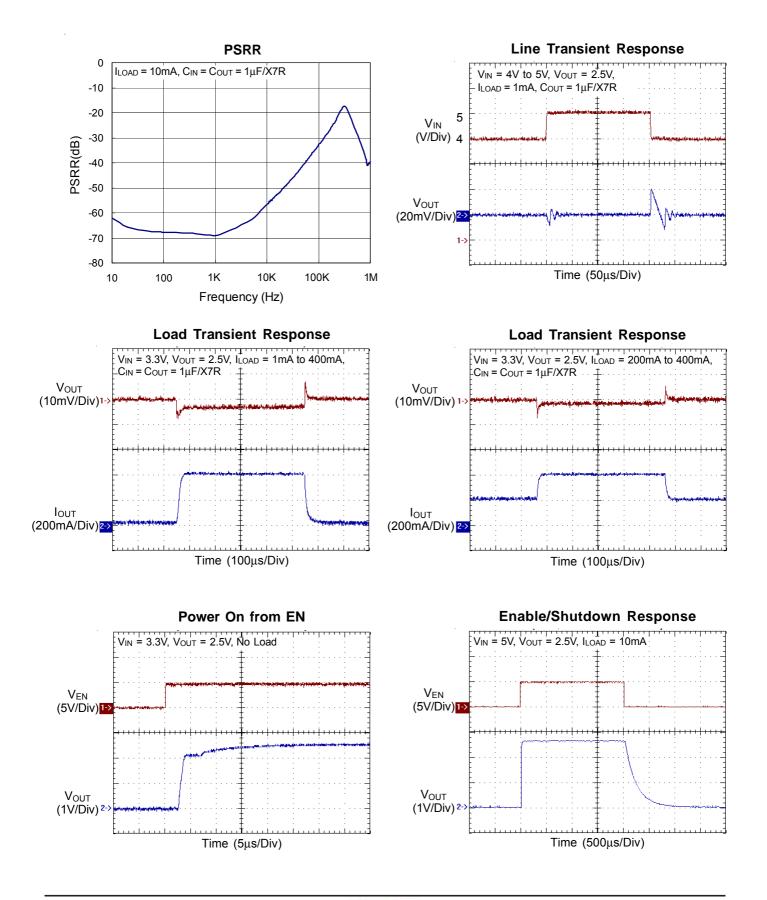

| D0                                    |                    |                   | f = 1kHz, l <sub>OUT</sub> = 10mA                               |       | 67    |       | dB                |

| Power Supply Rejection Ratio          |                    | PSRR              | f = 10kHz, I <sub>OUT</sub> = 10mA                              |       | 56    |       | dB                |

| Output Noise Voltage                  |                    | V <sub>ON</sub>   | $V_{OUT}$ = 1.5V, $C_{OUT}$ = 1 $\mu$ F, $I_{OUT}$ = 0mA        |       | 30    |       | μV <sub>RMS</sub> |

| Thermal Shutdown Temperature          |                    | T <sub>SD</sub>   |                                                                 |       | 160   |       | °C                |

| Thermal Shutdown Recovery Temperature |                    |                   |                                                                 |       | 110   |       | °C                |

- **Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

- Note 2.  $\theta_{JA}$  is measured in the natural convection at  $T_A$  = 25°C on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9043-03 April 2015 www.richtek.com

# **Typical Operating Characteristics**

**Quiescent Current vs. Temperature**

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9043-03 April 2015 www.richtek.com

## **Application Information**

### **Input Capacitor Selection**

Like any low-dropout linear regulator, the external capacitors used with the RT9043 must be carefully selected for stability and performance. The input capacitance is recommended to be at least  $1\mu F$ , and can be increased without limit. The input capacitor must be located at a distance of less than 0.5 inch from the input pin of the IC and returned to a clean ground plane. Any high-quality ceramic capacitor or tantalum capacitor can be used for the input capacitor. Using input capacitor with larger capacitance and lower ESR (equivalent series resistance) can obtain better PSRR and line transient response.

### **Output Capacitor Selection**

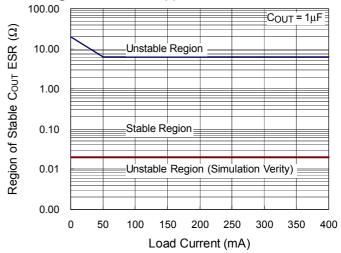

The output capacitor must meet both the requirements for minimum capacitance and minimum ESR value in all applications. The RT9043 is designed specifically to work with low ESR ceramic output capacitor to save board space and have better performance. Figure 1 shows the allowable ESR range for stable operation as a function of load current and output capacitance value. Use at least  $1\mu F$  ceramic output capacitor which ESR is within the stable operation range to ensure stability. Larger capacitance can reduce noise and improve load transient response, stability, and PSRR. The RT9043 can operate with other types of output capacitor due to its wide stable operation range. The output capacitor should be placed less than 0.5 inch from the  $V_{\text{OUT}}$  and returned to a clean ground plane.

### Region of Stable Cout ESR vs. Load Current

Figure 1

## **Output Voltage Setting**

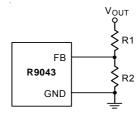

The output voltage divider R1 and R2 allows to adjust the output voltage for various application as shown in Figure 2.

Figure 2. Output Voltage Setting

The output voltage is set according to the following equation:

$$V_{OUT} = V_{FB} \left( 1 + \frac{R1}{R2} \right)$$

Where  $V_{FB}$  is the feedback reference voltage (1.2V typical).

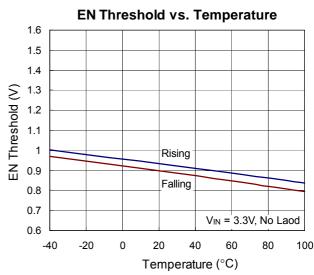

#### **Enable Function**

The RT9043 features enable/shutdown function. The voltage at the EN pin determines the enable/shutdown state of the regulator. To ensure the regulator will switch on, the enable control voltage must be greater than 1.6V. The regulator will enter shutdown mode when the voltage at EN pin falls below 0.6 volt. If the enable function is not needed, EN pin should be pulled high or simply tied to  $V_{\text{IN}}$  to keep the regulator in on state.

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

### **PSRR**

RT9043 features high power supply rejection ratio (PSRR), which is defined as the ratio of output voltage change against input voltage change.

$$PSRR = 20 \times log \left( \frac{\Delta V_{OUT}}{\Delta V_{IN}} \right)$$

A low-dropout regulator with higher PSRR can provide better line transient performance.

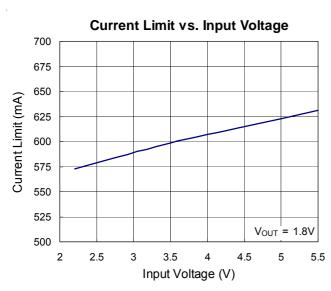

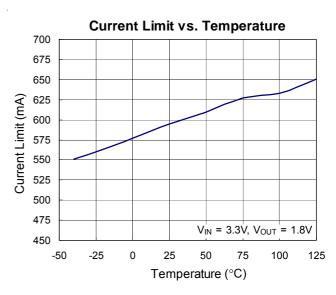

#### **Current Limit**

The RT9043 implements an independent current limit circuit, which monitors and controls the pass element's gate voltage to limit the output current at 650mA (typ.). If the current limit condition lasts for a long time, the regulator temperature may increase high enough to damage the regulator itself. There fore, RT9043 implements current limit function and thermal protection function to prevent the regulator from damaging when the output is shorted to ground.

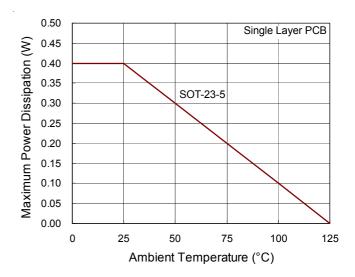

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum operation junction temperature. The maximum power dissipation depends on the thermal resistance of IC package, PCB layout, the rate of surroundings airflow and temperature difference between junction to ambient. The maximum power dissipation can be calculated by following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

Where  $T_{J(MAX)}$  is the maximum operation junction temperature,  $T_A$  is the ambient temperature and the  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating conditions specification of RT9043, the maximum junction temperature is 125°C. The junction to ambient thermal resistance  $\theta_{JA}$  is layout dependent. For SOT-23-5 packages, the thermal resistance  $\theta_{JA}$  is 250°C/W on the standard JEDEC 51-3 single layer thermal test board. The maximum power dissipation at  $T_A$  = 25°C can be calculated by following formula :

$P_{D(MAX)}$  = (125°C - 25°C) / (250°C/W) = 0.4W for SOT-23-5 packages

The maximum power dissipation depends on operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance  $\theta_{JA}$ . For RT9043 packages, the Figure 3 of derating curves allows the designer to see the effect of rising ambient temperature on the maximum power allowed.

Figure 3. Derating Curves for RT9043 Packages

Copyright ©2015 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

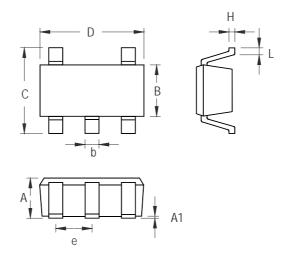

## **Outline Dimension**

| Compleal | Dimensions In Millimeters |       | Dimensions In Inches |       |  |

|----------|---------------------------|-------|----------------------|-------|--|

| Symbol   | Min                       | Max   | Min                  | Max   |  |

| Α        | 0.889                     | 1.295 | 0.035                | 0.051 |  |

| A1       | 0.000                     | 0.152 | 0.000                | 0.006 |  |

| В        | 1.397                     | 1.803 | 0.055                | 0.071 |  |

| b        | 0.356                     | 0.559 | 0.014                | 0.022 |  |

| С        | 2.591                     | 2.997 | 0.102                | 0.118 |  |

| D        | 2.692                     | 3.099 | 0.106                | 0.122 |  |

| е        | 0.838                     | 1.041 | 0.033                | 0.041 |  |

| Н        | 0.080                     | 0.254 | 0.003                | 0.010 |  |

| L        | 0.300                     | 0.610 | 0.012                | 0.024 |  |

**SOT-23-5 Surface Mount Package**

## **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

www.richtek.com DS9043-03 April 2015

8