# **Table of Contents**

| 1. Simplified application diagrams                | 3   |

|---------------------------------------------------|-----|

| 2. Orderable part                                 | 7   |

| 3. Internal block diagrams                        | 9   |

| 4. Pin Connections                                | 11  |

| 4.1. Pinout diagram                               | 11  |

| 5. Electrical characteristics                     | 16  |

| 5.1. Maximum ratings                              | 16  |

| 5.2. Static electrical characteristics            | 18  |

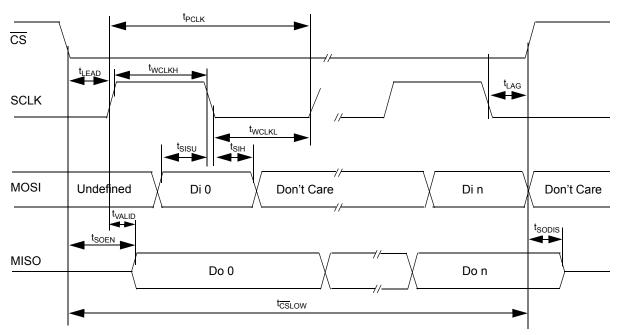

| 5.3. Dynamic electrical characteristics           |     |

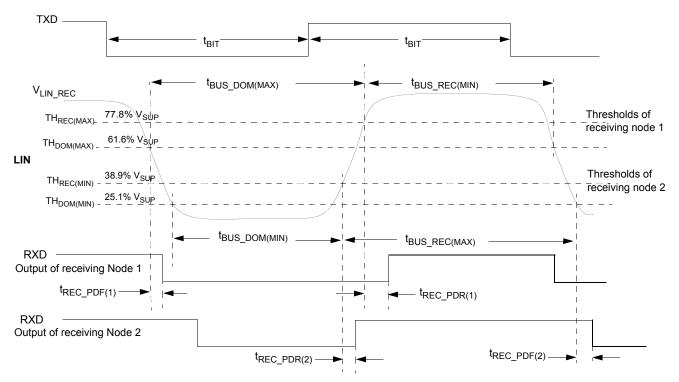

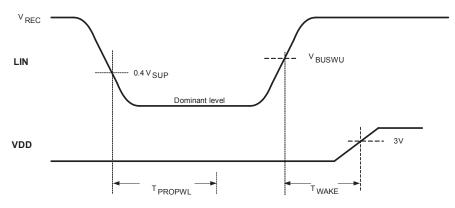

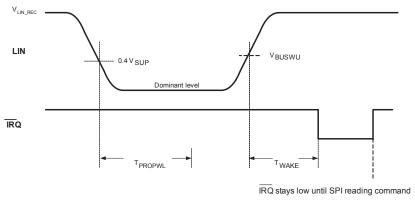

| 5.4. Timing diagrams                              | 29  |

| 6. Functional description                         | 32  |

| 6.1. Introduction                                 |     |

| 6.2. Functional pin description                   | 32  |

| 7. Functional device operation                    | 36  |

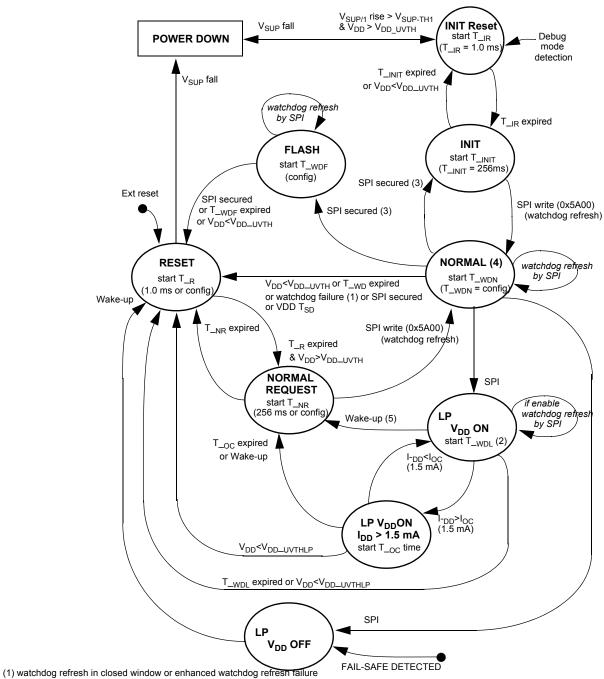

| 7.1. Mode and state description                   |     |

| 7.2. LP modes                                     |     |

| 7.3. State diagram                                |     |

| 7.4. Mode change                                  |     |

| 7.5. Watchdog operation                           |     |

| 7.6. Functional block operation versus mode       |     |

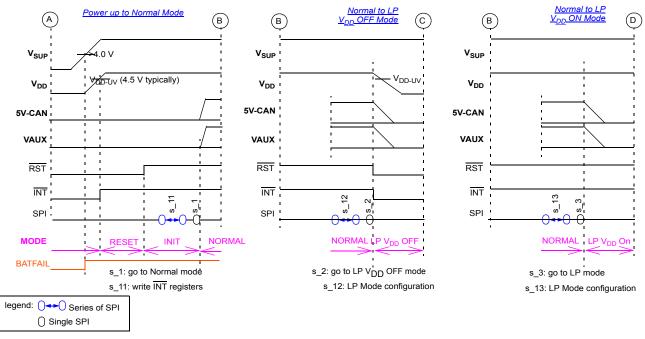

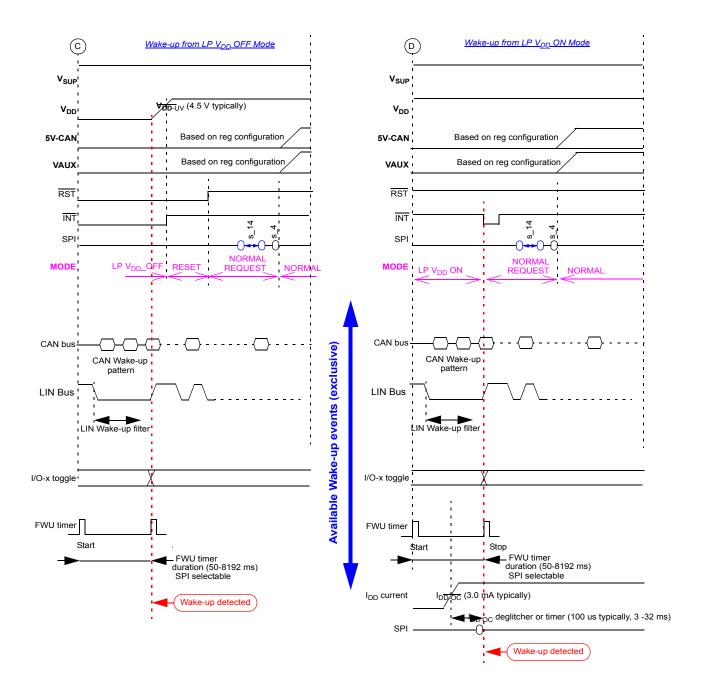

| 7.7. Illustration of device mode transitions      |     |

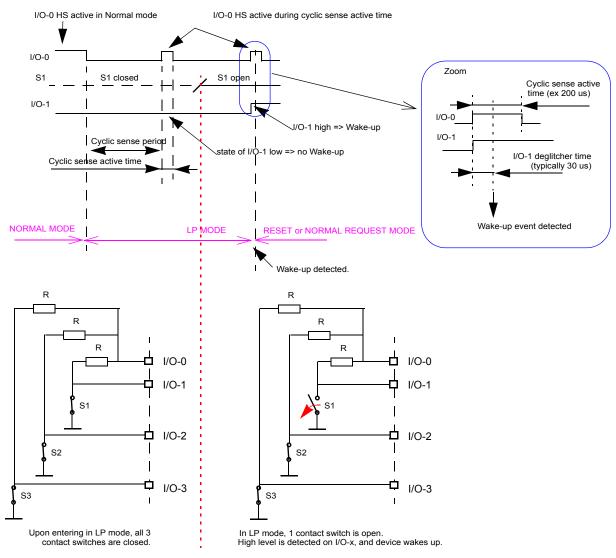

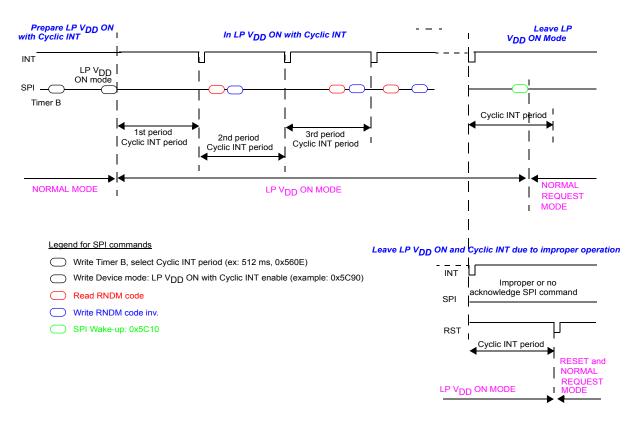

| 7.9. Cyclic Serise operation during LP modes      |     |

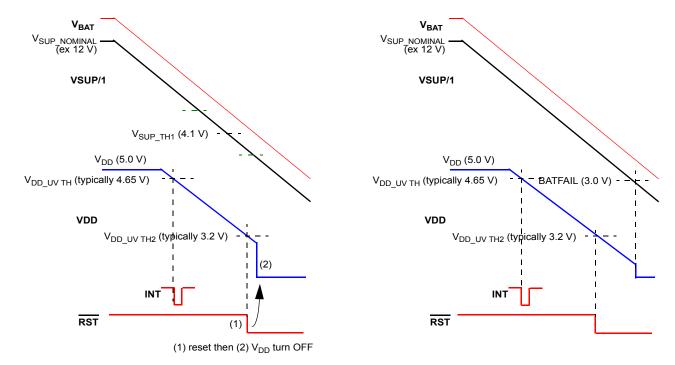

| 7.10. Behavior at power up and power down         |     |

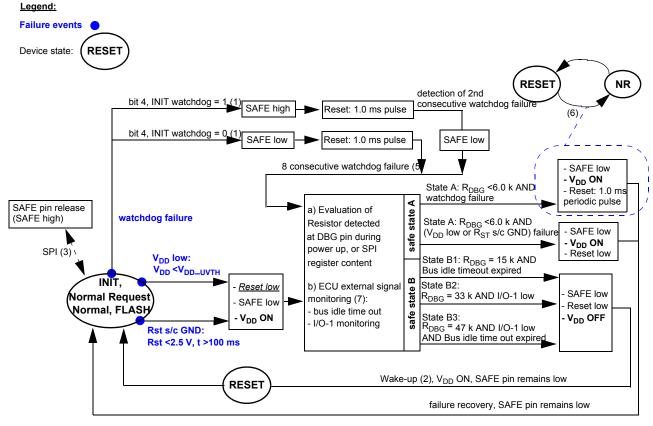

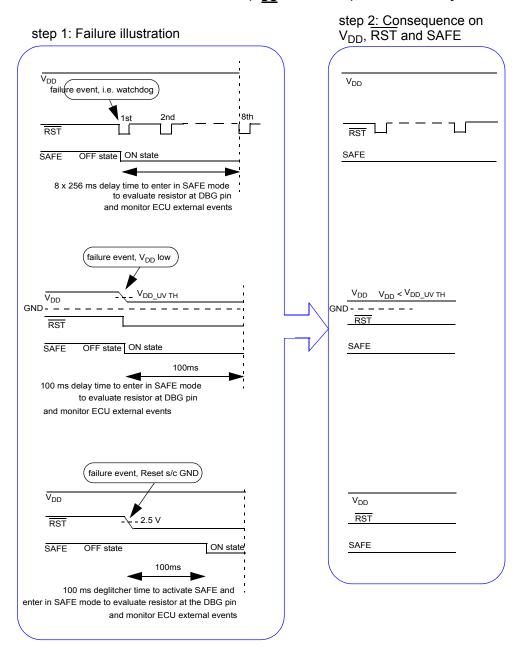

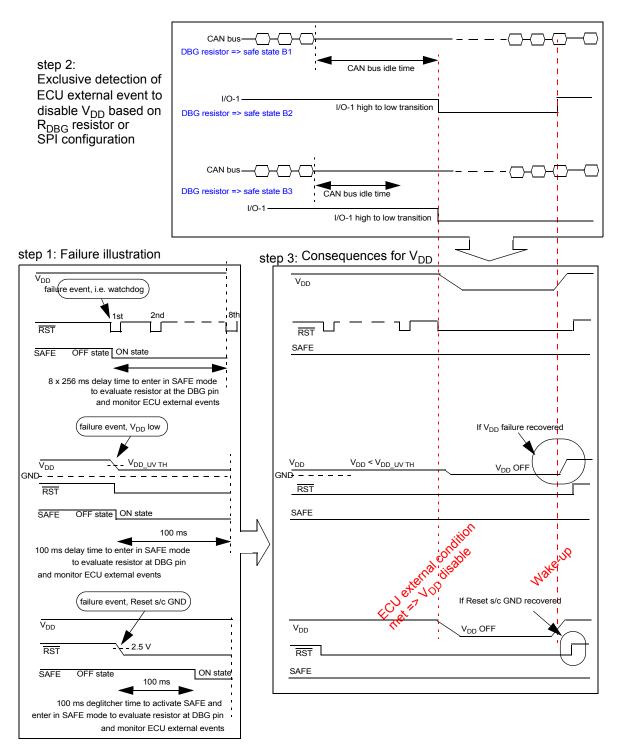

| 7.11. Fail-safe operation                         |     |

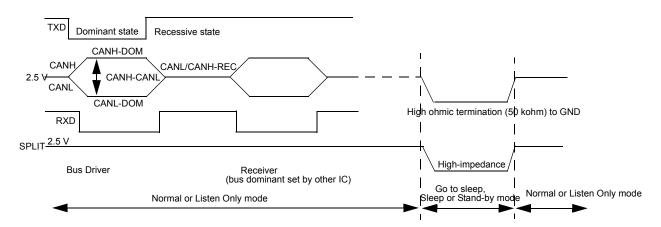

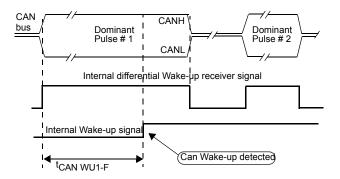

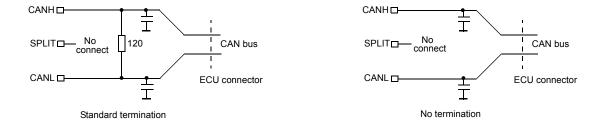

| 8. CAN interface                                  |     |

| 8.1. CAN interface description                    |     |

| 8.2. CAN bus fault diagnostic                     |     |

| 9. LIN block                                      |     |

| 9.1. LIN interface description                    |     |

| 9.2. LIN operational modes                        |     |

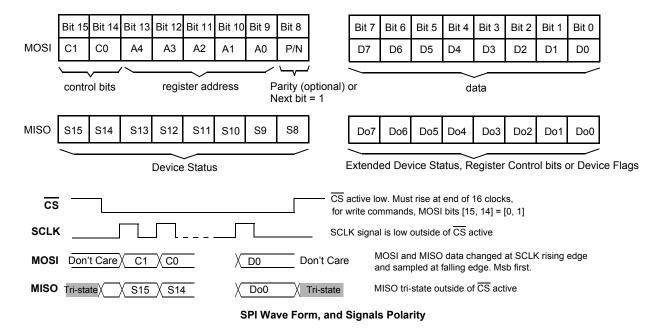

| 10. Serial peripheral interface                   |     |

| 10.1. High level overview                         |     |

| 10.2. Detail operation                            |     |

| 10.3. Detail of control bits and register mapping |     |

| 10.4. Flags and device status                     |     |

| 11. Typical applications                          | 92  |

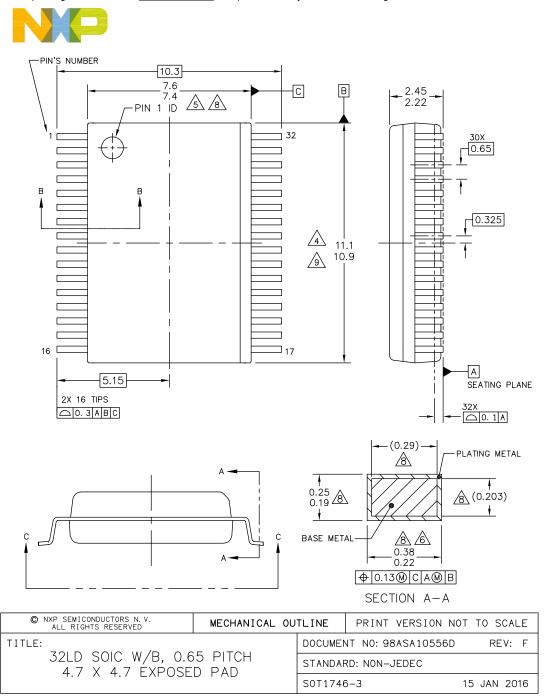

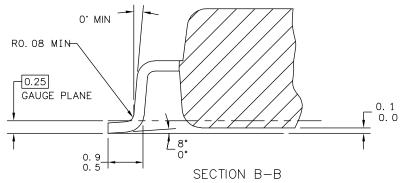

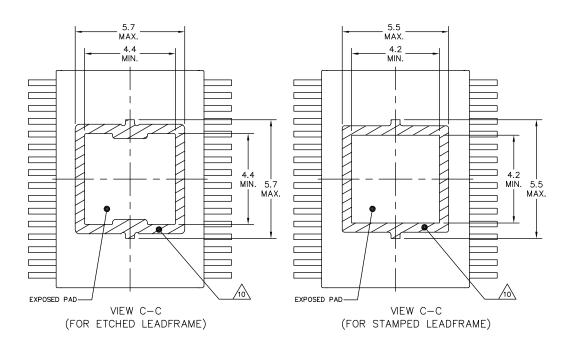

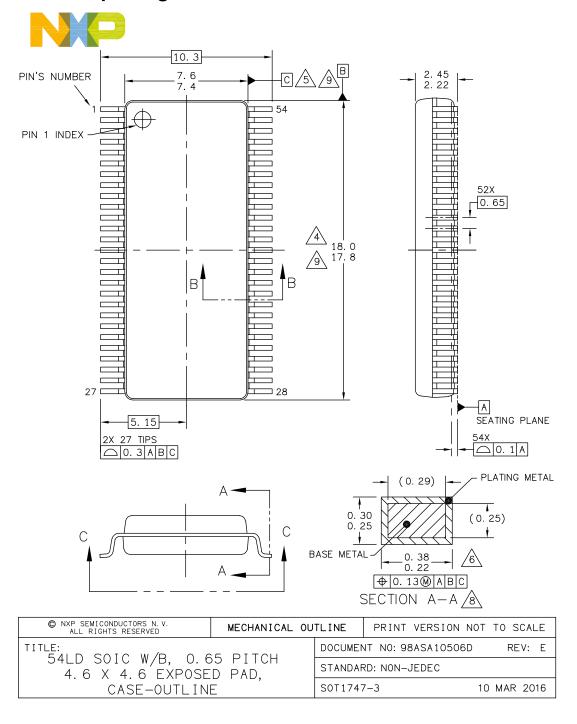

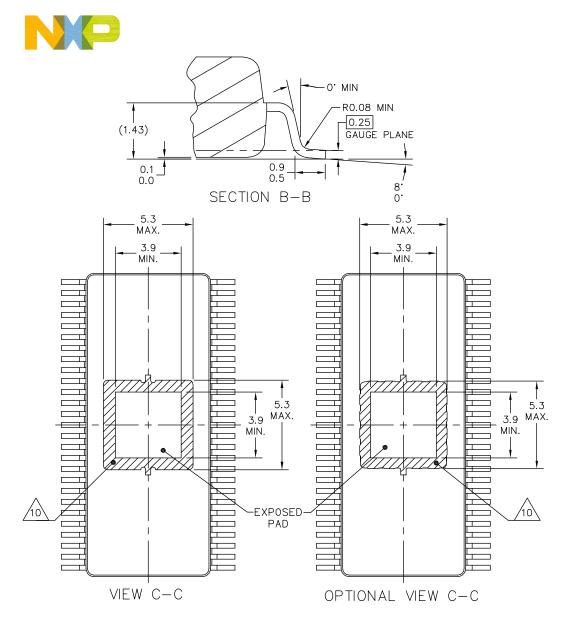

| 12. Packaging                                     |     |

| 12.1. SOIC 32 package dimensions                  |     |

| 12.2. SOIC 54 package dimensions                  |     |

| 13 Pevision history                               | 106 |

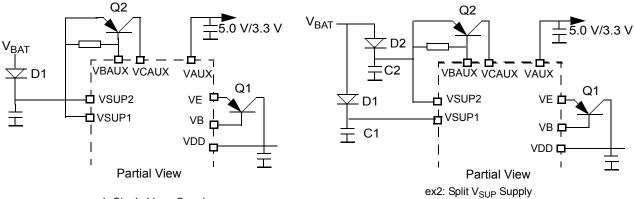

# 1 Simplified application diagrams

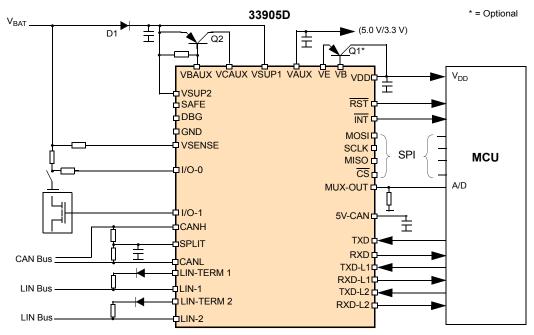

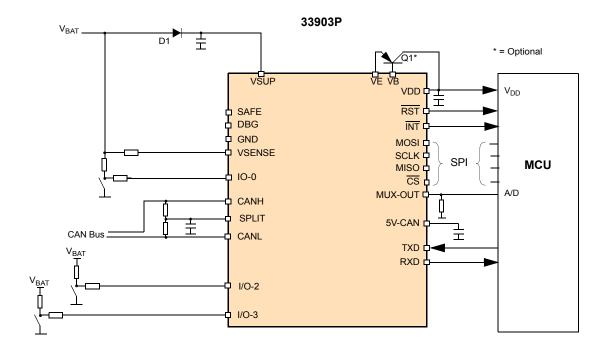

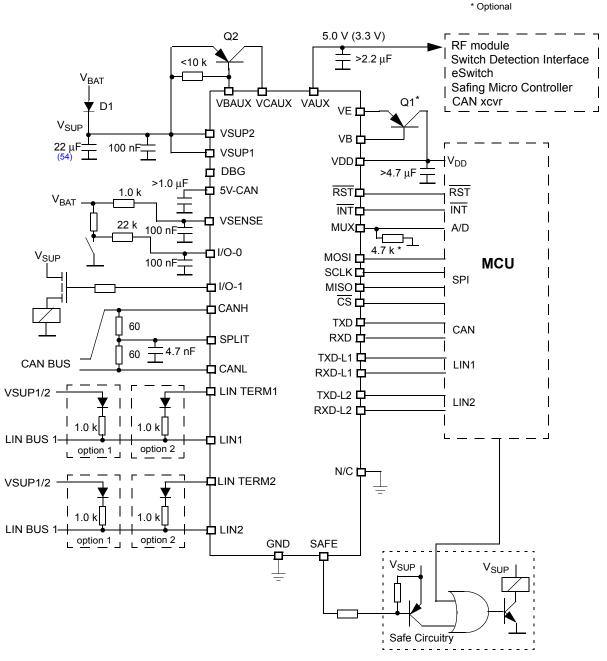

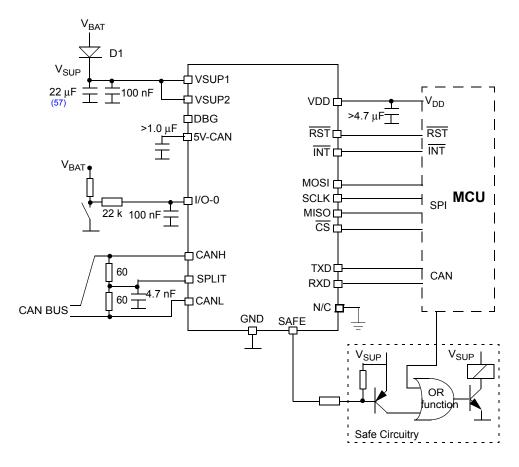

Figure 1. 33905D simplified application diagram

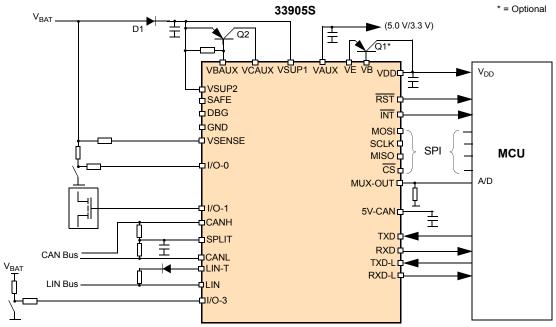

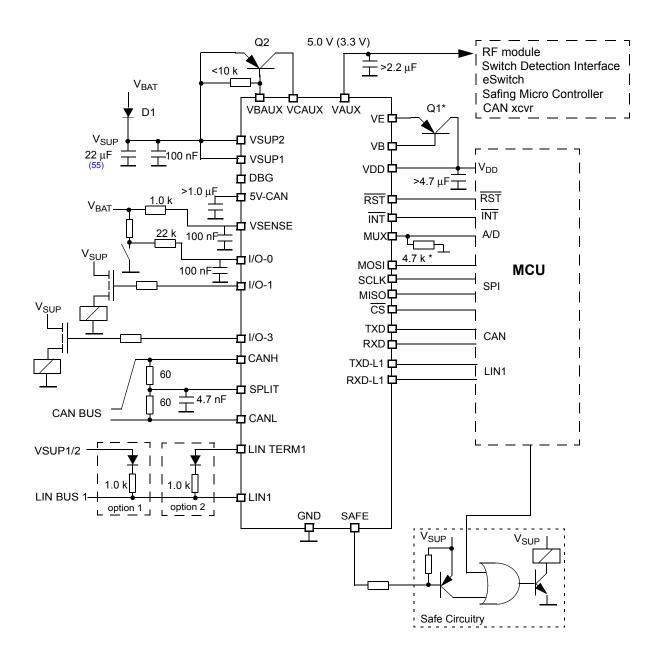

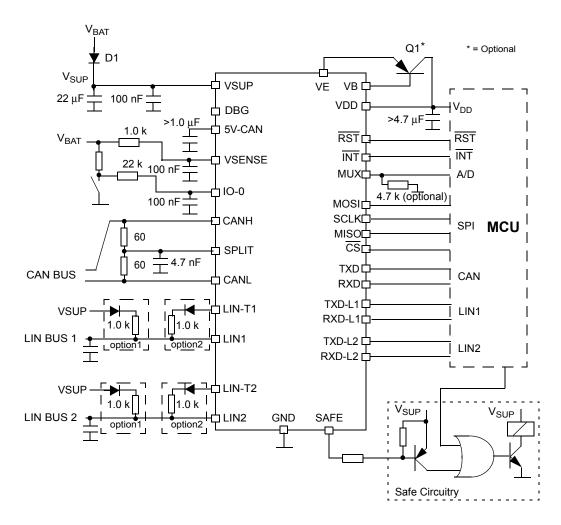

Figure 2. 33905S simplified application diagram

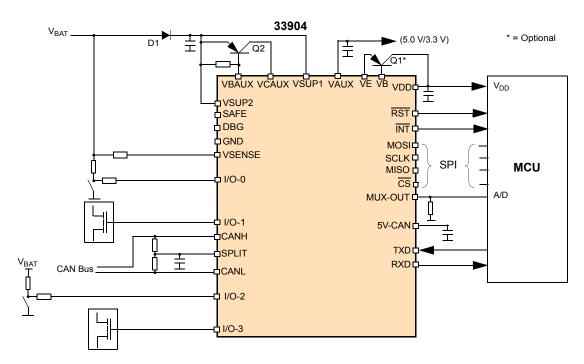

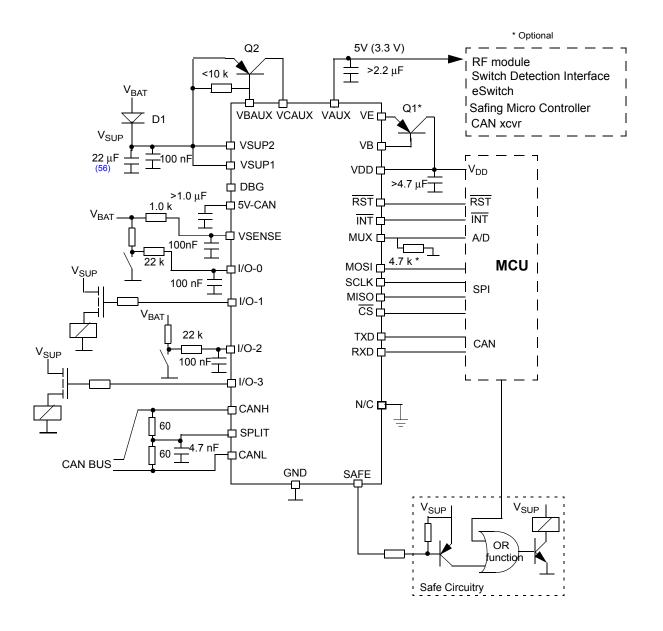

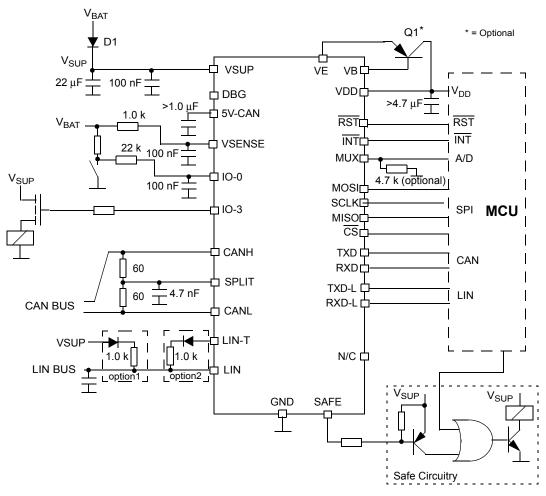

Figure 3. 33904 simplified application diagram

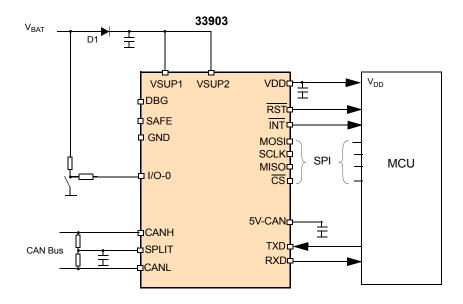

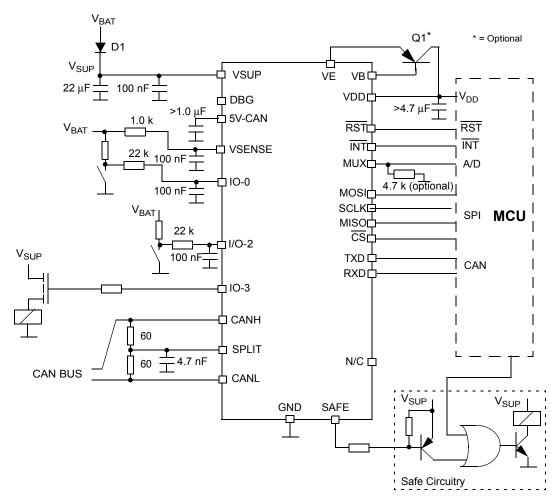

Figure 4. 33903 simplified application diagram

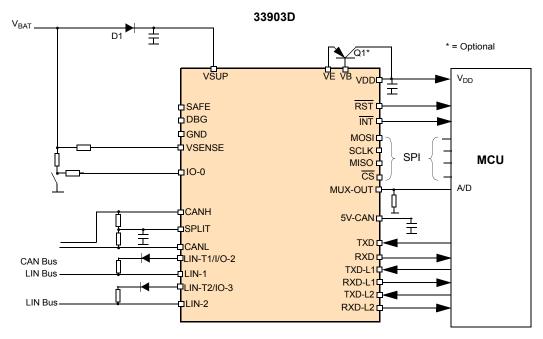

Figure 5. 33903D simplified application diagram

Figure 6. 33903S simplified application diagram

Figure 7. 33903P simplified application diagram

# 2 Orderable part

Table 1. MC33905 orderable part variations - (all devices rated at  $T_A$  = -40 °C TO 125 °C)

| NXP part number       | <b>Version</b> (1), (2), (3) | V <sub>DD</sub> output<br>voltage | LIN interface(s) | Wake-up input / LIN master termination | Package                 | V <sub>AUX</sub> | V <sub>SENSE</sub> | MUX |

|-----------------------|------------------------------|-----------------------------------|------------------|----------------------------------------|-------------------------|------------------|--------------------|-----|

| MC33905D (Dual LIN)   |                              |                                   |                  |                                        |                         | <u>'</u>         |                    |     |

| MCZ33905BD3EK/R2      | В                            |                                   |                  |                                        |                         |                  |                    |     |

| MCZ33905CD3EK/R2      | С                            | 3.3 V                             |                  |                                        |                         |                  |                    |     |

| MCZ33905DD3EK/R2      | D                            |                                   |                  | 2 Wake-up + 2 LIN terms<br>or          |                         |                  |                    |     |

| MCZ33905D5EK/R2       |                              |                                   | 2                | 3 Wake-up + 1 LIN terms                | SOIC 54-pin exposed pad | Yes              | Yes                | Yes |

| MCZ33905BD5EK/R2      | В                            | 5.0 V                             |                  | or<br>4 Wake-up + no LIN terms         |                         |                  |                    |     |

| MCZ33905CD5EK/R2      | С                            | 5.0 V                             |                  |                                        |                         |                  |                    |     |

| MCZ33905DD5EK/R2      | D                            |                                   |                  |                                        |                         |                  |                    |     |

| MC33905S (Single LIN) | _                            |                                   | <u> </u>         |                                        |                         |                  | <u> </u>           |     |

| MCZ33905BS3EK/R2      | В                            |                                   |                  |                                        |                         |                  |                    |     |

| MCZ33905CS3EK/R2      | С                            | 3.3 V                             |                  |                                        |                         |                  |                    |     |

| MCZ33905DS3EK/R2      | D                            |                                   |                  | 3 Wake-up + 1 LIN terms                |                         |                  |                    |     |

| MCZ33905S5EK/R2       |                              |                                   | 1                | or                                     | SOIC 32-pin exposed pad | Yes              | Yes                | Yes |

| MCZ33905BS5EK/R2      | В                            | 5.0 V                             |                  | 4 Wake-up + no LIN terms               | exposed pad             |                  |                    |     |

| MCZ33905CS5EK/R2      | С                            |                                   |                  |                                        |                         |                  |                    |     |

| MCZ33905DS5EK/R2      | D                            |                                   |                  |                                        |                         |                  |                    |     |

#### Notes

- Design changes in the 'B' version resolved V<sub>SUP</sub> slow ramp up issues, enhanced device current consumption and improved oscillator stability. 'B' version has an errata linked to the SPI operation.

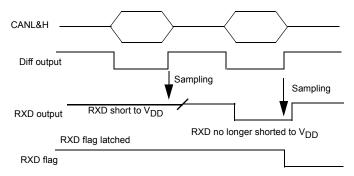

- 2. Design changes in the 'C' version resolve the SPI deviation of all prior versions, and does not have the RxD short to ground detection feature.

- 3. 'C' versions are no longer recommended for new design.

- 'D' versions are recommended for new design, and include quality improvement, and has no electrical parameters specification changes.

Table 2. MC33904 orderable part variations - (all devices rated at  $T_A$  = -40 °C TO 125 °C)

| NXP part number | <b>Version</b> (4), (5), (6) | V <sub>DD</sub> output<br>voltage | LIN interface(s) | Wake-up input / LIN master termination | Package                 | V <sub>AUX</sub> | V <sub>SENSE</sub> | MUX |

|-----------------|------------------------------|-----------------------------------|------------------|----------------------------------------|-------------------------|------------------|--------------------|-----|

| MC33904         |                              |                                   |                  |                                        |                         |                  |                    |     |

| MCZ33904B3EK/R2 | В                            |                                   |                  |                                        |                         |                  |                    |     |

| MCZ33904C3EK/R2 | С                            | 3.3 V                             | 0                | 4 Wake-up                              | SOIC 32 pin exposed pad | Yes              | Yes                |     |

| MCZ33904D3EK/R2 | D                            |                                   |                  |                                        |                         |                  |                    |     |

| MCZ33904A5EK/R2 | Α                            |                                   |                  |                                        |                         |                  |                    | Yes |

| MCZ33904B5EK/R2 | В                            | 5.0 V                             |                  |                                        |                         |                  |                    |     |

| MCZ33904C5EK/R2 | С                            | 5.0 V                             |                  |                                        |                         |                  |                    |     |

| MCZ33904D5EK/R2 | D                            |                                   |                  |                                        |                         |                  |                    |     |

#### Notes

- 4. Design changes in the "B" version resolved V<sub>SUP</sub> slow ramp up issues, enhanced device current consumption and improved oscillator stability. 'B' version has an errata linked to the SPI operation.

- 5. Design changes in the "C" version resolve the SPI deviation of all prior versions, and does not have the RxD short to ground detection feature.

- 6. 'C' versions are no longer recommended for new design.

- 'D' versions are recommended for new design, and include quality improvement, and has no electrical parameters specification changes.

Table 3. MC33903 orderable part variations - (all devices rated at  $T_A$  = -40 °C TO 125 °C)

| NXP part number       | <b>Version</b> (8), (9), (10) | V <sub>DD</sub> output<br>voltage | LIN interface(s) | Wake-up input / LIN master termination                                                     | Package                 | V <sub>AUX</sub> | V <sub>SENSE</sub> | MUX |

|-----------------------|-------------------------------|-----------------------------------|------------------|--------------------------------------------------------------------------------------------|-------------------------|------------------|--------------------|-----|

| MC33903               |                               |                                   |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903B3EK/R2       | В                             |                                   |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903C3EK/R2       | С                             | 3.3 V <sup>(7)</sup>              |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903D3EK/R2       | D                             |                                   | 0                | 1 Wake-up                                                                                  | SOIC 32 pin             | No               | No                 | No  |

| MCZ33903B5EK/R2       | В                             |                                   | - 0              | i wake-up                                                                                  | exposed pad             | INO              | INO                | INO |

| MCZ33903C5EK/R2       | С                             | 5.0 V <sup>(7)</sup>              |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903D5EK/R2       | D                             |                                   |                  |                                                                                            |                         |                  |                    |     |

| MC33903D (Dual LIN)   |                               |                                   |                  |                                                                                            |                         | <u> </u>         |                    |     |

| MCZ33903BD3EK/R2      | В                             |                                   |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903CD3EK/R2      | С                             | 3.3 V                             |                  | 1 Wake-up + 2 LIN terms<br>or<br>2 Wake-up + 1 LIN terms<br>or<br>3 Wake-up + no LIN terms |                         |                  |                    |     |

| MCZ33903DD3EK/R2      | D                             |                                   | 2                |                                                                                            | SOIC 32 pin             | No               | Yes                | Yes |

| MCZ33903BD5EK/R2      | В                             |                                   | - 2              |                                                                                            | exposed pad             | INO              | 165                | 103 |

| MCZ33903CD5EK/R2      | С                             | 5.0 V                             |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903DD5EK/R2      | D                             |                                   |                  |                                                                                            |                         |                  |                    |     |

| MC33903S (Single LIN) |                               |                                   |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903BS3EK/R2      | В                             |                                   |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903CS3EK/R2      | С                             | 3.3 V                             |                  |                                                                                            |                         |                  |                    | Yes |

| MCZ33903DS3EK/R2      | D                             |                                   | 1                | 2 Wake-up + 1 LIN terms<br>or                                                              | SOIC 32 pin             | No               | Yes                |     |

| MCZ33903BS5EK/R2      | В                             |                                   | - '              | 3 Wake-up + no LIN terms                                                                   | exposed pad             | INO              | 168                | 165 |

| MCZ33903CS5EK/R2      | С                             | 5.0 V                             |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903DS5EK/R2      | D                             |                                   |                  |                                                                                            |                         |                  |                    |     |

| MC33903P              |                               |                                   |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903CP5EK/R2      | С                             | 5.0 V                             |                  |                                                                                            |                         |                  |                    |     |

| MCZ33903DP5EK/R2      | D                             | J.U V                             | 0                | 3 Wake-up                                                                                  | SOIC 32 pin exposed pad | No               | Yes                | Yes |

| MCZ33903CP3EK/R2      | С                             | 3.3 V                             | 0                | 3 wane-up                                                                                  |                         | INO              |                    | 169 |

| MCZ33903DP3EK/R2      | D                             | J.J V                             |                  |                                                                                            |                         |                  |                    |     |

#### Notes

- 7.  $V_{DD}$  does not allow usage of an external PNP on the 33903.

- 8. Design changes in the 'B' version resolved V<sub>SUP</sub> slow ramp up issues, enhanced device current consumption and improved oscillator stability. 'B' version has an errata linked to the SPI operation.

- 9. Design changes in the "C" version resolve the SPI deviation of all prior versions, and does not have the RxD short to ground detection feature.

- 10. 'C' versions are no longer recommended for new design.

- 'D' versions are recommended for new design, and include quality improvement, and has no electrical parameters specification changes.

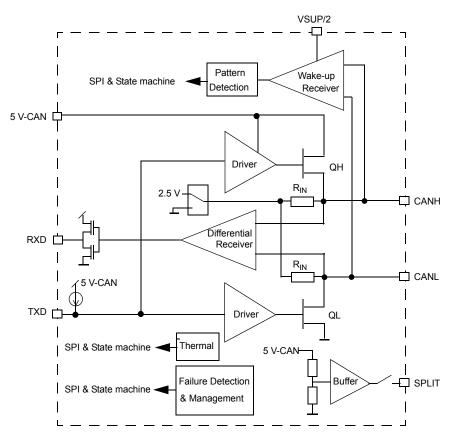

# 3 Internal block diagrams

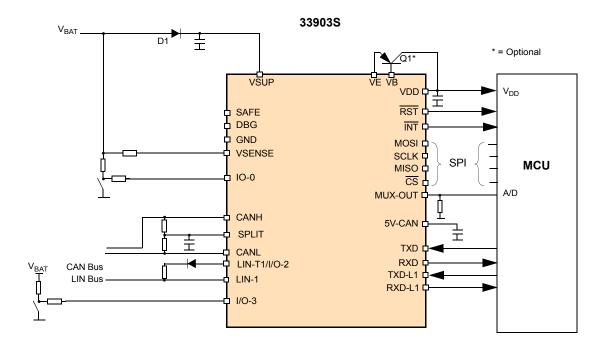

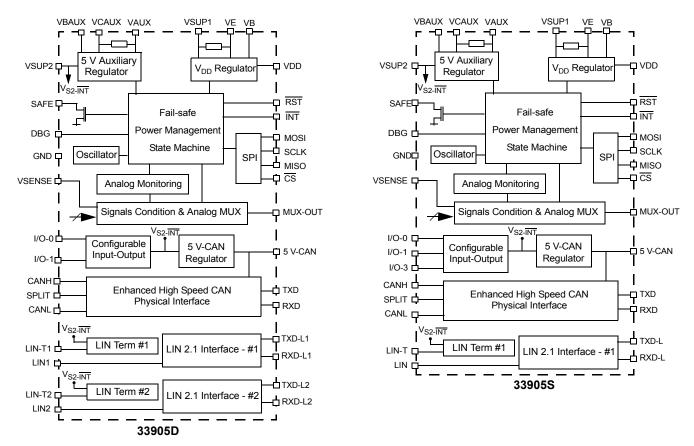

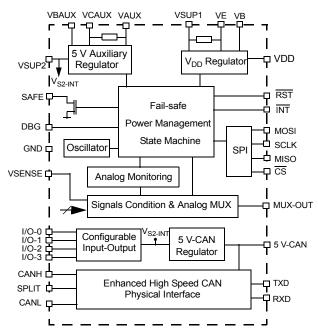

Figure 8. 33905 internal block diagram

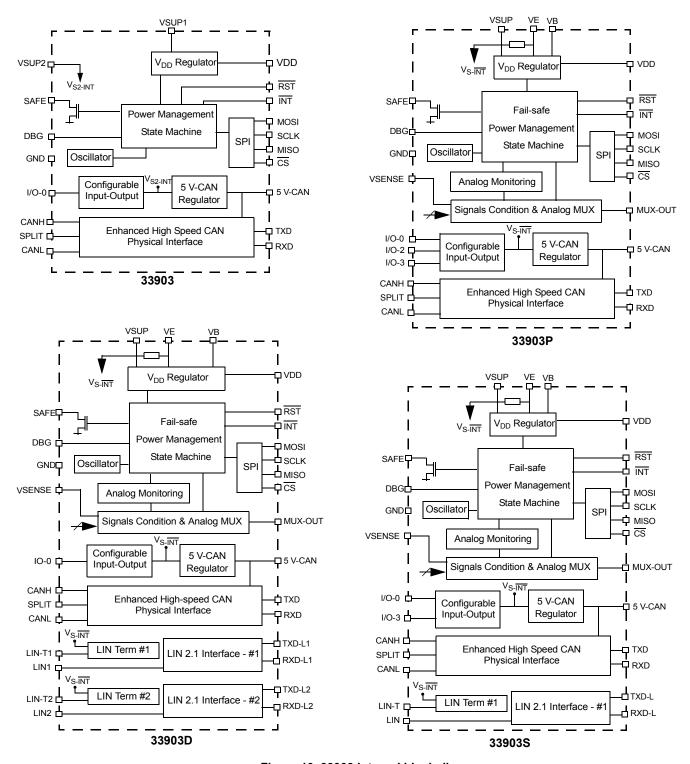

Figure 9. 33904 internal block diagram

Figure 10. 33903 internal block diagram

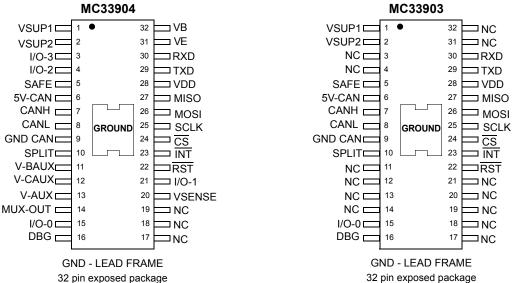

### 4 Pin Connections

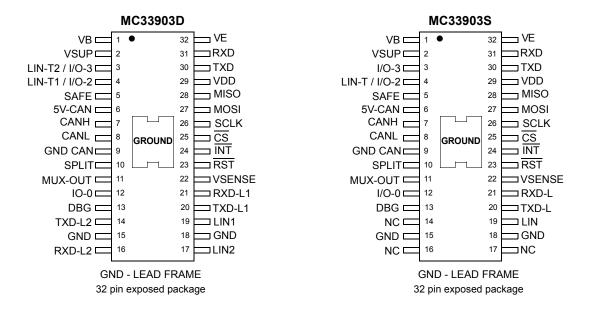

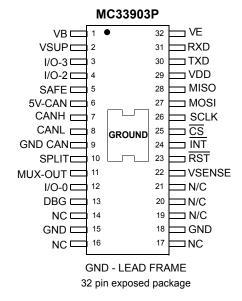

### 4.1 Pinout diagram

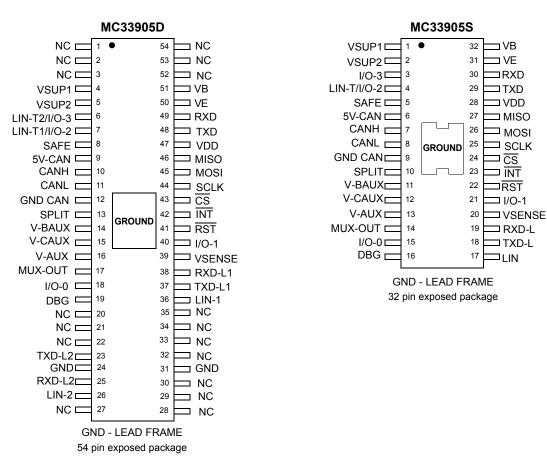

Note: MC33905D, MC33905S, MC33904 and MC33903 are footprint compatible,

Figure 11. 33905D, MC33905S, MC33904 and MC33903 pin connections

Note: MC33903D, MC33903S, and MC33903P are footprint compatible.

Figure 12. 33905D, MC33905S, MC33904 and MC33903 pin connections

# 4.2 Pin definitions

A functional description of each pin can be found in the Functional pin description section beginning on page 32.

Table 4. 33903/4/5 pin definitions

| 54 Pin<br>33905D                                | 32 Pin<br>33905S | 32 Pin<br>33904 | 32 Pin<br>33903                     | 32 Pin<br>33903D | 32 Pin<br>33903S | 32 Pin<br>33903P         | Pin Name                             | Pin<br>Function                  | Formal<br>Name                                     | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------|------------------|-----------------|-------------------------------------|------------------|------------------|--------------------------|--------------------------------------|----------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-3, 20-<br>22, 27-<br>30, 32-<br>35, 52-<br>54 | N/A              | 17, 18,<br>19   | 3-4,11-<br>14, 17-<br>21, 31,<br>32 | N/A              | N/A              | N/A                      | N/C                                  | No<br>Connect                    | -                                                  | Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| N/A                                             | N/A              | N/A             | N/A                                 | N/A              | 14, 16,<br>17    | 14, 16,<br>17, 19-<br>21 | N/C                                  | No<br>Connect                    |                                                    | Do NOT connect the N/C pins to GND. Leave these pins Open.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 4                                               | 1                | 1               | 1                                   | 2                | 2                | 2                        | VSUP/1                               | Power                            | Battery<br>Voltage<br>Supply 1                     | Supply input for the device internal supplies, power on reset circuitry and the $V_{DD}$ regulator. VSUP and VSUP1 supplies are internally connected on part number MC33903BDEK and MC33903BSEK                                                                                                                                                                                                                                                                                                |

| 5                                               | 2                | 2               | 2                                   | N/A              | N/A              | N/A                      | VSUP2                                | Power                            | Battery<br>Voltage<br>Supply 2                     | Supply input for 5 V-CAN regulator, V <sub>AUX</sub> regulator, I/O and LIN pins. VSUP1 and VSUP2 supplies are internally connected on part number MC33903BDEK and MC33903BSEK                                                                                                                                                                                                                                                                                                                 |

| 6                                               | 3                | 3               | N/A                                 | 3                | 3                | 3                        | LIN-T2<br>or<br>I/O-3                | Output<br>or<br>Input/<br>Output | LIN<br>Termination 2<br>or<br>Input/Output<br>3    | 33903D and 33905D - Output pin for the LIN2 master node termination resistor. or 33903P, 33903S, 33903D, 33904, 33905S and 33905D - Configurable pin as an input or HS output, for connection to external circuitry (switched or small load). The input can be used as a programmable Wake-up input in (LP) mode. When used as a HS, no overtemperature protection is implemented. A basic short to GND protection function, based on switch drain-source overvoltage detection, is available. |

| 7                                               | 4                | 4               | N/A                                 | 4                | 4                | 4                        | LIN-T1<br>or<br>LIN-T<br>or<br>I/O-2 | Output<br>or<br>Input/<br>Output | LIN<br>Termination<br>1<br>or<br>Input/Output<br>2 | 33905D - Output pin for the LIN1 master node termination resistor. or 33903P, 33903S, 33903D, 33904, 33905S and 33905D - Configurable pin as an input or HS output, for connection to external circuitry (switched or small load). The input can be used as a programmable Wake-up input in (LP) mode. When used as a HS, no overtemperature protection is implemented. A basic short to GND protection function, based on switch drain-source overvoltage detection, is available.            |

| 8                                               | 5                | 5               | 5                                   | 5                | 5                | 5                        | SAFE                                 | Output                           | Safe Output<br>(Active LOW)                        | Output of the safe circuitry. The pin is asserted LOW if a fault event occurs (e.g.: software watchdog is not triggered, V <sub>DD</sub> low, issue on the RST pin, etc.). Open drain structure.                                                                                                                                                                                                                                                                                               |

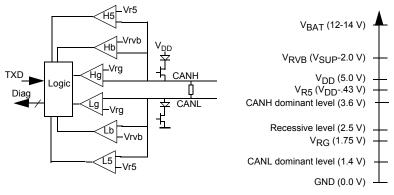

| 9                                               | 6                | 6               | 6                                   | 6                | 6                | 6                        | 5 V-CAN                              | Output                           | 5V-CAN                                             | Output voltage for the embedded CAN interface. A capacitor must be connected to this pin.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 10                                              | 7                | 7               | 7                                   | 7                | 7                | 7                        | CANH                                 | Output                           | CAN High                                           | CAN high output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11                                              | 8                | 8               | 8                                   | 8                | 8                | 8                        | CANL                                 | Output                           | CAN Low                                            | CAN low output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 12                                              | 9                | 9               | 9                                   | 9                | 9                | 9                        | GND-CAN                              | Ground                           | GND-CAN                                            | Power GND of the embedded CAN interface                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

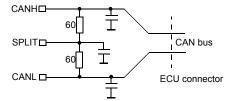

| 13                                              | 10               | 10              | 10                                  | 10               | 10               | 10                       | SPLIT                                | Output                           | SPLIT Output                                       | Output pin for connection to the middle point of the split CAN termination                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 4. 33903/4/5 pin definitions (continued)

| 54 Pin<br>33905D | 32 Pin<br>33905S | 32 Pin<br>33904 | 32 Pin<br>33903 | 32 Pin<br>33903D | 32 Pin<br>33903S | 32 Pin<br>33903P | Pin Name                                   | Pin<br>Function  | Formal<br>Name           | Definition                                                                                                                                                                                                                                                                                                                                                     |

|------------------|------------------|-----------------|-----------------|------------------|------------------|------------------|--------------------------------------------|------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14               | 11               | 11              | N/A             | N/A              | N/A              | N/A              | VBAUX                                      | Output           | VB Auxiliary             | Output pin for external path PNP transistor base                                                                                                                                                                                                                                                                                                               |

| 15               | 12               | 12              | N/A             | N/A              | N/A              | N/A              | VCAUX                                      | Output           | VCOLLECT<br>OR Auxiliary | Output pin for external path PNP transistor collector                                                                                                                                                                                                                                                                                                          |

| 16               | 13               | 13              | N/A             | N/A              | N/A              | N/A              | VAUX                                       | Output           | VOUT<br>Auxiliary        | Output pin for the auxiliary voltage.                                                                                                                                                                                                                                                                                                                          |

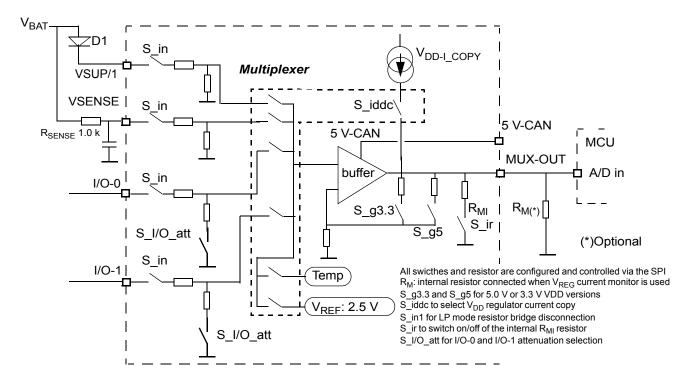

| 17               | 14               | 14              | N/A             | 11               | 11               | 11               | MUX-OUT                                    | Output           | Multiplex<br>Output      | Multiplexed output to be connected to an MCU A/D input. Selection of the analog parameter available at MUX-OUT is done via the SPI. A switchable internal pull-down resistor is integrated for V <sub>DD</sub> current sense measurements.                                                                                                                     |

| 18               | 15               | 15              | 15              | 12               | 12               | 12               | I/O-0                                      | Input/<br>Output | Input/Output<br>0        | Configurable pin as an input or output, for connection to external circuitry (switched or small load). The voltage level can be read by the SPI and via the MUX output pin. The input can be used as a programmable Wake-up input in LP mode. In LP, when used as an output, the High-side (HS) or Low-side (LS) can be activated for a cyclic sense function. |

| 19               | 16               | 16              | 16              | 13               | 13               | 13               | DBG                                        | Input            | Debug                    | Input to activate the Debug mode. In Debug mode, no watchdog refresh is necessary. Outside of Debug mode, connection of a resistor between DBG and GND allows the selection of Safe mode functionality.                                                                                                                                                        |

| 23               | N/A              | N/A             | N/A             | 14               | N/A              | N/A              | TXD-L2                                     | Input            | LIN Transmit<br>Data 2   | LIN bus transmit data input. Includes an internal pull-up resistor to VDD.                                                                                                                                                                                                                                                                                     |

| 24,31            | N/A              | N/A             | N/A             | 15, 18           | 15, 18           | 15, 18           | GND                                        | Ground           | Ground                   | Ground of the IC.                                                                                                                                                                                                                                                                                                                                              |

| 25               | N/A              | N/A             | N/A             | 16               | N/A              | N/A              | RXD-L2                                     | Output           | LIN Receive<br>Data      | LIN bus receive data output.                                                                                                                                                                                                                                                                                                                                   |

| 26               | N/A              | N/A             | N/A             | 17               | N/A              | N/A              | LIN2                                       | Input/<br>Output | LIN bus                  | LIN bus input output connected to the LIN bus.                                                                                                                                                                                                                                                                                                                 |

| 36               | 17               | N/A             | N/A             | 19               | 19               | N/A              | 33903D/5D<br>LIN-1<br>33903S/5S<br>LIN     | Input/<br>Output | LIN bus                  | LIN bus input output connected to the LIN bus.                                                                                                                                                                                                                                                                                                                 |

| 37               | 18               | N/A             | N/A             | 20               | 20               | N/A              | 33903D/5D<br>TXD-L11<br>33903S/5S<br>TXD-L | Input            | LIN Transmit<br>Data     | LIN bus transmit data input. Includes an internal pull-up resistor to VDD.                                                                                                                                                                                                                                                                                     |

| 38               | 19               | N/A             | N/A             | 21               | 21               | N/A              | 33903D/5D<br>RXD-L1<br>33903S/5S<br>RXD-L  | Output           | LIN Receive<br>Data      | LIN bus receive data output.                                                                                                                                                                                                                                                                                                                                   |

| 39               | 20               | 20              | N/A             | 22               | 22               | 22               | VSENSE                                     | Input            | Sense input              | Direct battery voltage input sense. A serial resistor is required to limit the input current during high voltage transients.                                                                                                                                                                                                                                   |

| 40               | 21               | 21              | N/A             | N/A              | N/A              | N/A              | I/O-1                                      | Input/<br>Output | Input Output<br>1        | Configurable pin as an input or output, for connection to external circuitry (switched or small load). The voltage level can be read by the SPI and the MUX output pin. The input can be used as a programmable Wake-up input in (LP) mode. It can be used in association with I/O-0 for a cyclic sense function in (LP) mode.                                 |

Table 4. 33903/4/5 pin definitions (continued)

|                  |                  |                 |                 | (                | ,                |                  |          |                 |                                     |                                                                                                                                                                                                                    |

|------------------|------------------|-----------------|-----------------|------------------|------------------|------------------|----------|-----------------|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 54 Pin<br>33905D | 32 Pin<br>33905S | 32 Pin<br>33904 | 32 Pin<br>33903 | 32 Pin<br>33903D | 32 Pin<br>33903S | 32 Pin<br>33903P | Pin Name | Pin<br>Function | Formal<br>Name                      | Definition                                                                                                                                                                                                         |

| 41               | 22               | 22              | 22              | 23               | 23               | 23               | RST      | Output          | Reset Output<br>(Active LOW)        | This is the device reset output whose main function is to reset the MCU. This pin has an internal pull-up to VDD. The reset input voltage is also monitored in order to detect external reset and safe conditions. |

| 42               | 23               | 23              | 23              | 24               | 24               | 24               | ĪNT      | Output          | Interrupt<br>Output<br>(Active LOW) | This output is asserted low when an enabled interrupt condition occurs. This pin is an open drain structure with an internal pull up resistor to VDD.                                                              |

| 43               | 24               | 24              | 24              | 25               | 25               | 25               | cs       | Input           | Chip Select<br>(Active LOW)         | Chip select pin for the SPI. When the $\overline{\text{CS}}$ is low the device is selected. In (LP) mode with V <sub>DD</sub> ON, a transition on $\overline{\text{CS}}$ is a Wake-up condition                    |

| 44               | 25               | 25              | 25              | 26               | 26               | 26               | SCLK     | Input           | Serial Data<br>Clock                | Clock input for the Serial Peripheral Interface (SPI) of the device                                                                                                                                                |

| 45               | 26               | 26              | 26              | 27               | 27               | 27               | MOSI     | Input           | Master Out/<br>Slave In             | SPI data received by the device                                                                                                                                                                                    |

| 46               | 27               | 27              | 27              | 28               | 28               | 28               | MISO     | Output          | Master In/<br>Slave Out             | SPI data sent to the MCU. When the $\overline{\text{CS}}$ is high MISO is high-impedance                                                                                                                           |

| 47               | 28               | 28              | 28              | 29               | 29               | 29               | VDD      | Output          | Voltage<br>Digital Drain            | 5.0 or 3.3 V output pin of the main regulator for the Microcontroller supply.                                                                                                                                      |

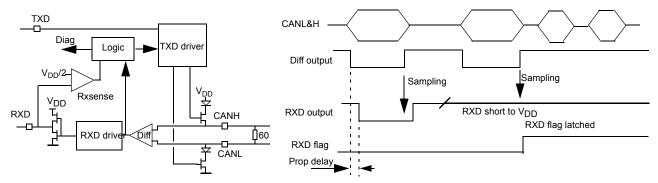

| 48               | 29               | 29              | 29              | 30               | 30               | 30               | TXD      | Input           | Transmit<br>Data                    | CAN bus transmit data input. Internal pull-up to VDD                                                                                                                                                               |

| 49               | 30               | 30              | 30              | 31               | 31               | 31               | RXD      | Output          | Receive Data                        | CAN bus receive data output                                                                                                                                                                                        |

| 50               | 31               | 31              | N/A             | 32               | 32               | 32               | VE       |                 | Voltage<br>Emitter                  | Connection to the external PNP path transistor This is an intermediate current supply source for the V <sub>DD</sub> regulator                                                                                     |

| 51               | 32               | 32              | N/A             | 1                | 1                | 1                | VB       | Output          | Voltage Base                        | Base output pin for connection to the external PNP pass transistor                                                                                                                                                 |

| EX PAD           | EX PAD           | EX PAD          | EX PAD          | EX PAD           | EX PAD           | EX PAD           | GND      | Ground          | Ground                              | Ground                                                                                                                                                                                                             |

# 5 Electrical characteristics

# 5.1 Maximum ratings

### Table 5. Maximum ratings

All voltages are referenced to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                        | Ratings                                                                                                      | Value                        | Unit | Notes |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------|------|-------|

| Electrical rating                             | s <sup>(11)</sup>                                                                                            | <u> </u>                     |      |       |

| V <sub>SUP1/2</sub><br>V <sub>SUP1/2</sub> TR | Supply Voltage at VSUP/1 and VSUP2 Normal Operation (DC) Transient Conditions (Load Dump)                    | -0.3 to 28<br>-0.3 to 40     | V    |       |

| V <sub>BUSLIN</sub><br>V <sub>BUSLINTR</sub>  | DC voltage on LIN/1 and LIN2 Normal Operation (DC) Transient Conditions (Load Dump)                          | -28 to 28<br>-28 to 40       | V    |       |

| V <sub>BUS</sub><br>V <sub>BUSTR</sub>        | DC voltage on CANL, CANH, SPLIT Normal Operation (DC) Transient Conditions (Load Dump)                       | -28 to 28<br>-32 to 40       | V    |       |

| V <sub>SAFE</sub><br>V <sub>SAFETR</sub>      | DC Voltage at SAFE Normal Operation (DC) Transient Conditions (Load Dump)                                    | -0.3 to 28<br>-0.3 to 40     | V    |       |

| V <sub>I/O</sub><br>V <sub>I/OTR</sub>        | DC Voltage at I/O-0, I/O-1, I/O-2, I/O-3 (LIN-T Pins) Normal Operation (DC) Transient Conditions (Load Dump) | -0.3 to 28<br>-0.3 to 40     | V    |       |

| $V_{DIGLIN}$                                  | DC voltage on TXD-L, TXD-L1 TXD-L2, RXD-L, RXD-L1, RXD-L2                                                    | -0.3 to V <sub>DD</sub> +0.3 | V    |       |

| $V_{DIG}$                                     | DC voltage on TXD, RXD                                                                                       | -0.3 to V <sub>DD</sub> +0.3 | V    | (13)  |

| V <sub>INT</sub>                              | DC Voltage at INT                                                                                            | -0.3 to 10                   | V    |       |

| V <sub>RST</sub>                              | DC Voltage at RST                                                                                            | -0.3 to V <sub>DD</sub> +0.3 | V    |       |

| V <sub>RST</sub>                              | DC Voltage at MOSI, MSIO, SCLK and CS                                                                        | -0.3 to V <sub>DD</sub> +0.3 | V    |       |

| $V_{MUX}$                                     | DC Voltage at MUX-OUT                                                                                        | -0.3 to V <sub>DD</sub> +0.3 | V    |       |

| $V_{DBG}$                                     | DC Voltage at DBG                                                                                            | -0.3 to 10                   | V    |       |

| ILH                                           | Continuous current on CANH and CANL                                                                          | 200                          | mA   |       |

| V <sub>REG</sub>                              | DC voltage at VDD, 5V-CAN, VAUX, VCAUX                                                                       | -0.3 to 5.5                  | V    |       |

| V <sub>REG</sub>                              | DC voltage at VBASE and VBAUX                                                                                | -0.3 to 40                   | V    | (12)  |

| VE                                            | DC voltage at VE                                                                                             | -0.3 to 40                   | V    | (13)  |

| V <sub>SENSE</sub>                            | DC voltage at VSENSE                                                                                         | -28 to 40                    | V    | 1     |

#### Notes

- 11. The voltage on non-VSUP pins should never exceed the  $V_{SUP}$  voltage at any time or permanent damage to the device may occur.

- 12. If the voltage delta between VSUP/1/2 and VBASE is greater than 6.0 V, the external  $V_{DD}$  ballast current sharing functionality may be damaged.

- 13. Potential Electrical Over Stress (EOS) damage may occur if RXD is in contact with VE while the device is ON.

#### Table 5. Maximum ratings (continued)

All voltages are referenced to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                                                    | Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Value                                              | Unit | Notes |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------|-------|

| VESD1-1<br>VESD1-2<br>VESD2-1<br>VESD2-2<br>VESD3-1<br>VESD3-2<br>VESD3-3 | ESD Capability $AECQ100^{(14)}$ Human Body Model - JESD22/A114 (C <sub>ZAP</sub> = 100 pF, R <sub>ZAP</sub> = 1500 $\Omega$ ) $CANH \text{ and CANL. LIN1 and LIN2, Pins versus all GND pins}$ all other Pins including CANH and CANL $Charge \text{ Device Model - JESD22/C101 (C_{ZAP} = 4.0 \text{ pF})}$ $Corner \text{ Pins (Pins 1, 16, 17, and 32)}$ $All other \text{ Pins (Pins 2-15, 18-31)}$ $Tested \text{ per IEC 61000-4-2 (C_{ZAP} = 150 \text{ pF, R}_{ZAP} = 330 } \Omega$ ) $Device \text{ unpowered, CANH and CANL pin without capacitor, versus GND}$ $Device \text{ unpowered, LIN, LIN1 and LIN2 pin, versus GND}$ $Device \text{ unpowered, VS1/VS2 (100 nF to GND), versus GND}$ $Tested \text{ per specific OEM EMC requirements for CAN and LIN with additional capacitor on VSUP/1/2 pins (See Typical applications on page)}$ | ±8000<br>±2000<br>±750<br>±500<br>±15000<br>±15000 | V    |       |

| $V_{\mathrm{ESD4-1}}$ $V_{\mathrm{ESD4-2}}$ $V_{\mathrm{ESD4-3}}$         | 92) CANH, CANL without bus filter LIN, LIN1 and LIN2 with and without bus filter I/O with external components (22 k - 10 nF)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ±9000<br>±12000<br>±7000                           |      |       |

#### Thermal ratings

| T <sub>J</sub>  | Junction temperature | 150        | °C |  |

|-----------------|----------------------|------------|----|--|

| T <sub>A</sub>  | Ambient temperature  | -40 to 125 | °C |  |

| T <sub>ST</sub> | Storage temperature  | -50 to 150 | °C |  |

#### Thermal resistance

| $R_{\theta JA}$   | Thermal resistance junction to ambient        | 50      | °C/W | (17)       |

|-------------------|-----------------------------------------------|---------|------|------------|

| T <sub>PPRT</sub> | Peak package reflow temperature during reflow | Note 16 | °C   | (15), (16) |

#### Notes

- 14. ESD testing is performed in accordance with the Human Body Model (HBM) ( $C_{ZAP} = 100 \text{ pF}$ ,  $R_{ZAP} = 1500 \Omega$ ), the Charge Device Model (CDM), and Robotic ( $C_{ZAP} = 4.0 \text{ pF}$ ).

- 15. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

- 16. NXP's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL), go to www.nxp.com, search by part number (remove prefixes/suffixes) and enter the core ID to view all orderable parts, and review parametrics.

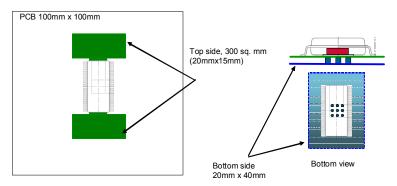

- 17. This parameter was measured according to Figure 13:

Figure 13. PCB with top and bottom layer dissipation area (dual layer)

### 5.2 Static electrical characteristics

#### Table 6. Static electrical characteristics

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  28 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                               | Characteristic                                                                                                                                                                                                                                                                                                                                                                                  | Min.             | Тур.             | Max.                     | Unit | Notes      |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|--------------------------|------|------------|

| Power input                          |                                                                                                                                                                                                                                                                                                                                                                                                 |                  |                  |                          |      |            |

| V <sub>SUP1</sub> /V <sub>SUP2</sub> | Nominal DC Voltage Range                                                                                                                                                                                                                                                                                                                                                                        | 5.5              | -                | 28                       | V    | (18)       |

| V <sub>SUP1</sub> /V <sub>SUP2</sub> | Extended DC Low Voltage Range                                                                                                                                                                                                                                                                                                                                                                   | 4.0              | -                | 5.5                      | V    | (19)       |

| V <sub>S1_LOW</sub>                  | Undervoltage Detector Thresholds, at the VSUP/1 pin, Low threshold (VSUP/1 ramp down) High threshold (VSUP/1 ramp up) Hysteresis Note: function not active in LP mode                                                                                                                                                                                                                           | 5.5<br>-<br>0.22 | 6.0<br>-<br>0.35 | 6.5<br>6.6<br>0.5        | V    |            |

| V <sub>S2_LOW</sub>                  | Undervoltage Detector Thresholds, at the VSUP2 pin: Low threshold (VSUP2 ramp down) High threshold (VSUP2 ramp up) Hysteresis Note: function not active in LP modes                                                                                                                                                                                                                             | 5.5<br>-<br>0.22 | 6.0<br>-<br>0.35 | 6.5<br>6.6<br>0.5        | V    |            |

| V <sub>S_HIGH</sub>                  | V <sub>SUP</sub> Overvoltage Detector Thresholds, at the VSUP/1 pin: Not active in LP modes                                                                                                                                                                                                                                                                                                     | 16.5             | 17               | 18.5                     | V    |            |

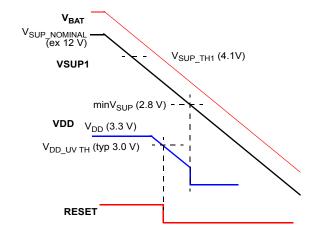

| BATFAIL                              | Battery loss detection threshold, at the VSUP/1 pin.                                                                                                                                                                                                                                                                                                                                            | 2.0              | 2.8              | 4.0                      | V    |            |

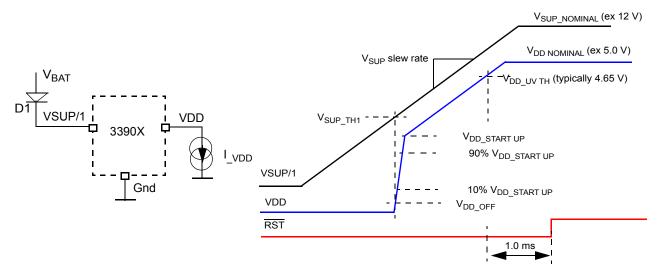

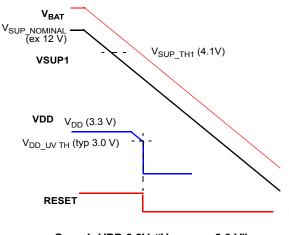

| V <sub>SUP-TH1</sub>                 | VSUP/1 to turn V <sub>DD</sub> ON, VSUP/1 rising                                                                                                                                                                                                                                                                                                                                                | -                | 4.1              | 4.5                      | V    |            |

| V <sub>SUP-TH1HYST</sub>             | VSUP/1 to turn V <sub>DD</sub> ON, hysteresis (Guaranteed by design)                                                                                                                                                                                                                                                                                                                            | 150              | 180              |                          | mV   |            |

| I <sub>SUP1</sub>                    | Supply current - from VSUP/1 - from VSUP2, (5V-CAN V <sub>AUX</sub> , I/O OFF)                                                                                                                                                                                                                                                                                                                  |                  | 2.0<br>0.05      | 4.0<br>0.85              | mA   | (20), (21) |

| I <sub>SUP1+2</sub>                  | Supply current, I <sub>SUP1</sub> + I <sub>SUP2</sub> , Normal mode, V <sub>DD</sub> ON - 5 V-CAN OFF, V <sub>AUX</sub> OFF - 5 V-CAN ON, CAN interface in Sleep mode, V <sub>AUX</sub> OFF - 5 V-CAN OFF, Vaux ON - 5 V-CAN ON, CAN interface in TXD/RXD mode, V <sub>AUX</sub> OFF, I/O-x disabled                                                                                            | -<br>-<br>-      | 2.8              | 4.5<br>5.0<br>5.5<br>8.0 | mA   |            |

| I <sub>LPM_OFF</sub>                 | LP mode $V_{DD}$ OFF. Wake-up from CAN, I/O-x inputs $V_{SUP} \le 18 \text{ V}$ , -40 to 25 °C $V_{SUP} \le 18 \text{ V}$ , 125 °C                                                                                                                                                                                                                                                              |                  | 15<br>-          | 35<br>50                 | μА   |            |

| I <sub>LPM_ON</sub>                  | LP mode V <sub>DD</sub> ON (5.0 V) with V <sub>DD</sub> undervoltage and V <sub>DD</sub> overcurrent monitoring, Wake-up from CAN, I/O-x inputs $V_{SUP} \leq 18 \text{ V}, -40 \text{ to } 25 \text{ °C}, I_{DD} = 1.0 \mu\text{A}$ $V_{SUP} \leq 18 \text{ V}, -40 \text{ to } 25 \text{ °C}, I_{DD} = 100 \mu\text{A}$ $V_{SUP} \leq 18 \text{ V}, 125 \text{ °C}, I_{DD} = 100 \mu\text{A}$ | -<br>-           | 20<br>40<br>-    | -<br>65<br>85            | μА   |            |

| losc                                 | LP mode, additional current for oscillator (used for: cyclic sense, forced Wake-up, and in LP $V_{DD}$ ON mode cyclic interruption and watchdog) $V_{SUP} \leq 18 \text{ V}, -40 \text{ to } 125 \text{ °C}$                                                                                                                                                                                    | -                | 5.0              | 9.0                      | μА   |            |

| $V_{DBG}$                            | Debug mode DBG voltage range                                                                                                                                                                                                                                                                                                                                                                    | 8.0              | -                | 10                       | V    |            |

#### Notes

- 18. All parameters in spec (ex: V<sub>DD</sub> regulator tolerance).

- 19. Device functional, some parameters could be out of spec. V<sub>DD</sub> is active, device is not in Reset mode if the lowest V<sub>DD</sub> undervoltage reset threshold is selected (approx. 3.4 V). CAN and I/Os are not operational.

- 20. In Run mode, CAN interface in Sleep mode, 5 V-CAN and  $V_{AUX}$  turned OFF.  $I_{OUT}$  at  $V_{DD}$  < 50 mA. Ballast: turned OFF or not connected.

- 21. VSUP1 and VSUP2 supplies are internally connected on part number MC33903BDEK and MC33903BSEK. Therefore, I<sub>SUP1</sub> and I<sub>SUP2</sub> cannot be measured individually.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  28 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                                           | Characteristic                                                                                                | Min.       | Тур.       | Max.  | Unit | Notes |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------|------------|-------|------|-------|

| V <sub>DD</sub> Voltage regu                     | lator, VDD pin                                                                                                |            |            | 1     |      |       |

| V                                                | Output Voltage<br>V <sub>DD</sub> = 5.0 V, V <sub>SUP</sub> 5.5 to 28 V, I <sub>OUT</sub> 0 to 150 mA         | 4.9        | 5.0        | 5.1   |      |       |

| V <sub>OUT-5.0</sub><br>V <sub>OUT-5.0-EMC</sub> | V <sub>DD</sub> = 5.0 V, under EMC immunity test condition                                                    | 4.9        | 5.0        | 5.15  | V    | (22)  |

| V <sub>OUT-3.3</sub>                             | $V_{DD} = 3.3 \text{ V}, V_{SUP} 5.5 \text{ to } 28 \text{ V}, I_{OUT} 0 \text{ to } 150 \text{ mA}$          | 3.234      | 3.3        | 3.4   |      |       |

| $V_{DROP}$                                       | Drop voltage without external PNP pass transistor $V_{DD} = 5.0 \text{ V}, I_{OUT} = 100 \text{ mA}$          | -          | 330        | 450   | mV   | (23)  |

| DIOI                                             | V <sub>DD</sub> = 5.0 V, I <sub>OUT</sub> = 150 mA                                                            | -          | -          | 500   |      |       |

| V <sub>DROP-B</sub>                              | Drop voltage with external transistor I <sub>OUT</sub> = 200 mA (I_BALLAST + I_INTERNAL)                      | -          | 350        | 500   | mV   | (23)  |

| V <sub>SUP1-3.3</sub>                            | VSUP/1 to maintain $V_{DD}$ within $V_{OUT-3.3}$ specified voltage range $V_{DD} = 3.3$ V, $I_{OUT} = 150$ mA | 4.0        | -          | -     | V    |       |

|                                                  | $V_{DD} = 3.3 \text{ V}, I_{OUT} = 200 \text{ mA}, \text{ external transistor implemented}$                   | 4.0        | -          | -     |      |       |

| K                                                | External ballast versus internal current ratio (I_BALLAST = K x Internal current)                             | 1.5        | 2.0        | 2.5   |      |       |

| I <sub>LIM</sub>                                 | Output Current limitation, without external transistor                                                        | 150        | 350        | 550   | mA   |       |

| $T_PW$                                           | Temperature pre-warning (Guaranteed by design)                                                                | -          | 140        | -     | °C   |       |

| T <sub>SD</sub>                                  | Thermal shutdown (Guaranteed by design)                                                                       | 160        | -          | -     | °C   |       |

| $C_{EXT}$                                        | Range of decoupling capacitor (Guaranteed by design)                                                          | 4.7        | -          | 100   | μF   | (24)  |

| $V_{\mathrm{DDLP}}$                              | LP mode $V_{DD}$ ON, $I_{OUT} \le 50$ mA (time limited)<br>$V_{DD} = 5.0$ V, $5.6$ V $\le V_{SUP} \le 28$ V   | 4.75       | 5.0        | 5.25  | V    |       |

| DDLP                                             | $V_{DD} = 3.3 \text{ V}, 5.6 \text{ V} \le V_{SUP} \le 28 \text{ V}$                                          | 3.135      | 3.3        | 3.465 | •    |       |

| L <sub>P-IOUTDC</sub>                            | LP mode V <sub>DD</sub> ON, dynamic output current capability (Limited duration. Ref. to device description). | -          | -          | 50    | mA   |       |

| L <sub>P-ITH</sub>                               | LP V <sub>DD</sub> ON mode: Overcurrent Wake-up threshold. Hysteresis                                         | 1.0<br>0.1 | 3.0<br>1.0 |       | mA   |       |

| L <sub>P-VDROP</sub>                             | LP mode $V_{DD}$ ON, drop voltage, at $I_{OUT}$ = 30 mA (Limited duration. Ref. to device description)        | -          | 200        | 400   | mV   | (23)  |

| L <sub>P-MINVS</sub>                             | LP mode $V_{DD}$ ON, min $V_{SUP}$ operation (Below this value, a $V_{DD}$ , undervoltage reset may occur)    | 5.5        | -          | -     | V    |       |

| $V_{DD\_OFF}$                                    | $V_{DD}$ when $V_{SUP}$ < $V_{SUP-TH1}$ , at I_ $V_{DD}$ ≤ 10 μA (Guaranteed by design)                       | -          | -          | 0.3   | V    |       |

| V <sub>DD_START UP</sub>                         | $V_{DD}$ when $V_{SUP} \ge V_{SUP-TH1}$ , at $I\_V_{DD} \le 40$ mA (Guaranteed with parameter $V_{SUP-TH1}$   | 3.0        | -          | -     | ٧    |       |

### Notes

- 22. Guaranteed by design. During immunity tests, according to IEC62132-4, with RF injection applied to CAN or LIN pins. No filter components on CAN or LIN pins. When immunity tests are performed with a CAN filter component (common mode choke) or LIN filter component (capacitor), the V<sub>DD</sub> specification is 5.0 V ±2%.

- For 3.3 V V<sub>DD</sub> devices, the drop-out voltage test condition leads to a V<sub>SUP</sub> below the min V<sub>SUP</sub> threshold (4.0 V). As a result, the dropout voltage parameter cannot be specified.

- 24. The regulator is stable without an external capacitor. Usage of an external capacitor is recommended for AC performance.

Characteristics noted under conditions 5.5 V  $\leq$  V<sub>SUP</sub>  $\leq$  28 V, -40 °C  $\leq$  T<sub>A</sub>  $\leq$  125 °C, unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25 °C under nominal conditions, unless otherwise noted.

| Symbol                 | Characteristic                                                                                                   | Min.  | Тур. | Max.  | Unit | Notes      |

|------------------------|------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|------------|

| oltage regulato        | r for CAN interface supply, 5.0 V-CAN pin                                                                        |       | I    | 1     |      | 1          |

| E\/                    | Output voltage, V <sub>SUP/2</sub> = 5.5 to 40 V                                                                 | 4.75  | 5.0  | 5.25  | V    |            |

| 5V <sub>-C OUT</sub>   | I <sub>OUT</sub> 0 to 160 mA                                                                                     | 4.75  | 5.0  | 5.25  | V    |            |

| 5V <sub>-C ILIM</sub>  | Output Current limitation                                                                                        | 160   | 280  | -     | mA   | (25)       |

| 5V <sub>-C UV</sub>    | Undervoltage threshold                                                                                           | 4.1   | 4.5  | 4.7   | V    |            |

| 5V <sub>-CTS</sub>     | Thermal shutdown (Guaranteed by design)                                                                          | 160   | -    | -     | °C   |            |

| C <sub>EXT-CAN</sub>   | External capacitance (Guaranteed by design)                                                                      | 1.0   | -    | 100   | μF   |            |

|                        | ut, 5.0 and 3.3 V selectable pin VB-Aux, VC-Aux, Vaux                                                            |       |      |       |      |            |

|                        | VAUX output voltage                                                                                              |       |      |       |      |            |

| $V_{AUX}$              | $V_{AUX} = 5.0 \text{ V}, V_{SUP} = V_{SUP2} 5.5 \text{ to } 40 \text{ V}, I_{OUT} 0 \text{ to } 150 \text{ mA}$ | 4.75  | 5.0  | 5.25  | V    |            |

| , tox                  | $V_{AUX}$ = 3.3 V, $V_{SUP}$ = $V_{SUP2}$ 5.5 to 40 V, $I_{OUT}$ 0 to 150 mA                                     | 3.135 | 3.3  | 3.465 |      |            |

|                        | VAUX undervoltage detector (VAUX configured to 5.0 V)                                                            |       |      |       |      |            |

|                        | Low Threshold                                                                                                    | 4.2   | 4.5  | 4.70  |      |            |

| $V_{AUX-UVTH}$         | Hysteresis                                                                                                       | 0.06  | 4.5  | 0.12  | V    |            |

|                        | VAUX undervoltage detector (VAUX configured to 3.3 V, default                                                    | 2.75  | 3.0  | 3.135 |      |            |

|                        | value)                                                                                                           | 2.73  | 3.0  | 3.133 |      |            |

|                        | VAUX overcurrent threshold detector                                                                              |       |      |       |      |            |

| $V_{AUX-ILIM}$         | V <sub>AUX</sub> set to 3.3 V                                                                                    | 250   | 360  | 450   | mA   |            |

|                        | V <sub>AUX</sub> set to 5.0 V                                                                                    | 230   | 330  | 430   |      |            |

| V <sub>AUX CAP</sub>   | External capacitance (Guaranteed by design)                                                                      | 2.2   | -    | 100   | μF   |            |

| ndervoltage re         | set and reset function, RST pin                                                                                  | "     | J.   |       |      |            |

|                        | V <sub>DD</sub> undervoltage threshold down - 90% V <sub>DD</sub> (V <sub>DD</sub> 5.0 V)                        | 4.5   | 4.65 | 4.85  |      | (26), (28) |

| \/                     | V <sub>DD</sub> undervoltage threshold up - 90% V <sub>DD</sub> (V <sub>DD</sub> 5.0 V)                          | -     | -    | 4.90  | V    |            |

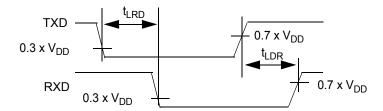

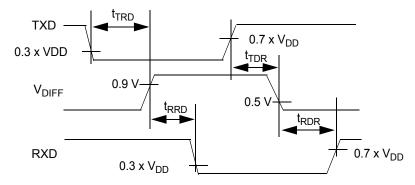

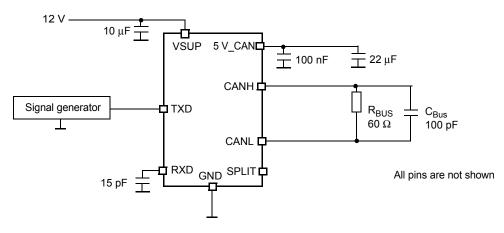

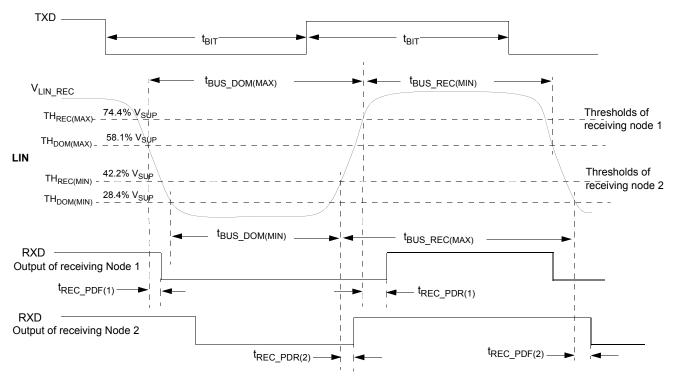

| V <sub>RST-TH1</sub>   | V <sub>DD</sub> undervoltage threshold down - 90% V <sub>DD</sub> (V <sub>DD</sub> 3.3 V)                        | 2.75  | 3.0  | 3.135 | V    | (26), (28) |