# **Table of Contents**

| 1  | Orderable Parts                                      |

|----|------------------------------------------------------|

| 2  | Internal Block Diagram                               |

| 3  | Pin Connections                                      |

|    | 3.1 Pinout                                           |

|    | 3.2 Pin Definitions                                  |

| 4  | General Product Characteristics                      |

|    | 4.1 Maximum Ratings                                  |

|    | 4.2 Thermal Characteristics                          |

|    | 4.3 Operating Conditions                             |

|    | 4.4 Electrical Characteristics                       |

| 5  | General Description                                  |

|    | 5.1 Features                                         |

|    | 5.2 Functional Block Diagram                         |

| 6  | General IC Functional Description                    |

|    | 6.1 Battery Voltage Ranges                           |

|    | 6.2 Power Sequencing Conditions                      |

| 7  | Functional Block Description                         |

|    | 7.1 State Diagram                                    |

|    | 7.2 Low-power Mode Operation                         |

|    | 7.3 Input Functional Block                           |

|    | 7.4 Oscillator and Timer Control Functional Block    |

|    | 7.5 Temperature Monitor and Control Functional Block |

|    | 7.6 WAKE_B Control Functional Block                  |

|    | 7.7 INT_B Functional Block                           |

|    | 7.8 AMUX Functional Block                            |

|    | 7.9 Serial Peripheral Interface (SPI)                |

|    | 7.10 SPI Control Register Definition                 |

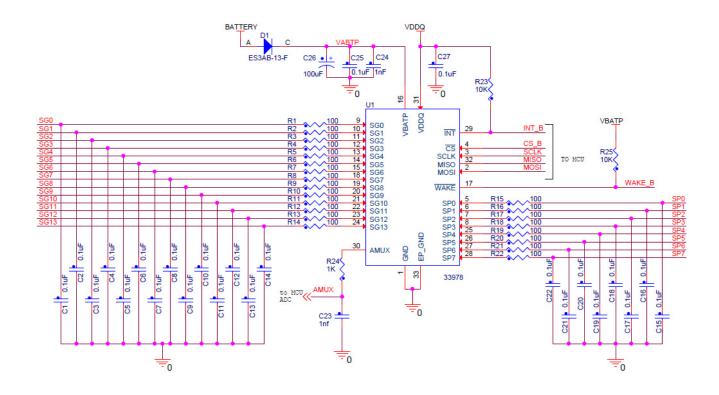

| 8  | Typical Applications                                 |

|    | 8.1 Application Diagram                              |

|    | 8.2 Bill of Materials                                |

|    | 8.3 Abnormal Operation                               |

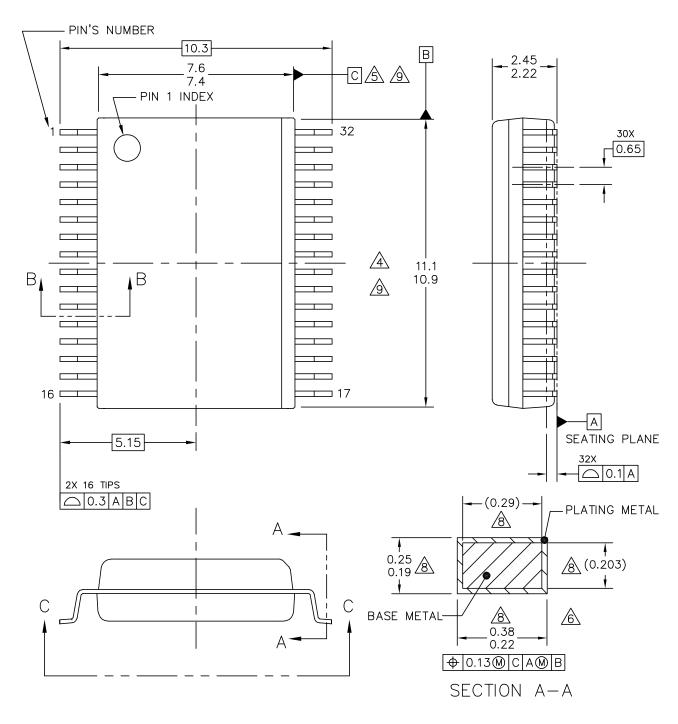

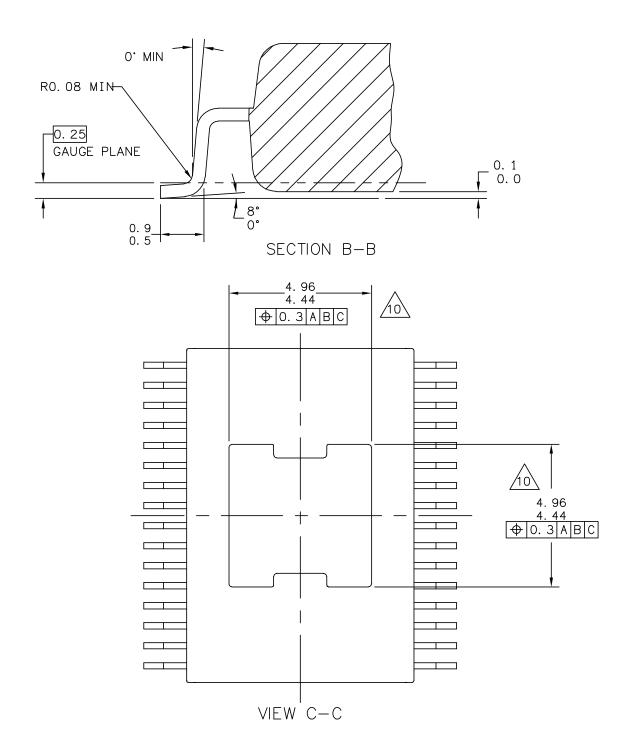

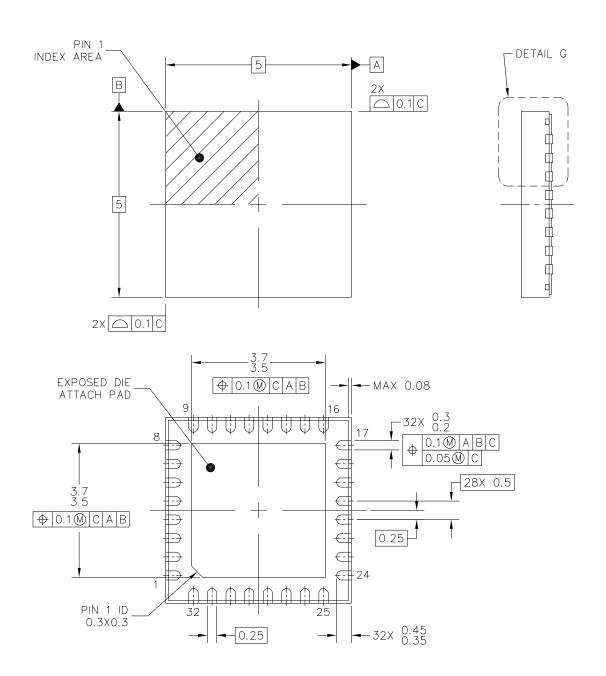

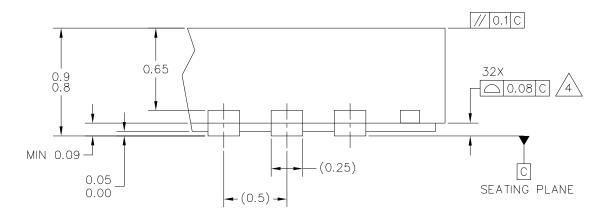

| 9  | Packaging                                            |

|    | 9.1 Package Mechanical Dimensions                    |

| 10 | Reference Section                                    |

| 11 | Revision History 63                                  |

# 1 Orderable Parts

This section describes the part numbers available to be purchased along with their differences.

#### **Table 1. Orderable Part Variations**

| Part Number | Temperature (T <sub>A</sub> ) | Package               | Notes |

|-------------|-------------------------------|-----------------------|-------|

| MC33978EK   |                               | SOICW-EP 32 pins      | (1)   |

| PC33978ES   | -40 °C to 125 °C              | QFN (WF-TYPE) 32 pins | (1)   |

| MC34978EK   |                               | SOICW-EP 32 pins      | (1)   |

| PC34978ES   | -40 °C to 85 °C               | QFN (WF-TYPE) 32 pins | (1)   |

#### Notes

<sup>1.</sup> To order parts in Tape & Reel, add the R2 suffix to the part number.

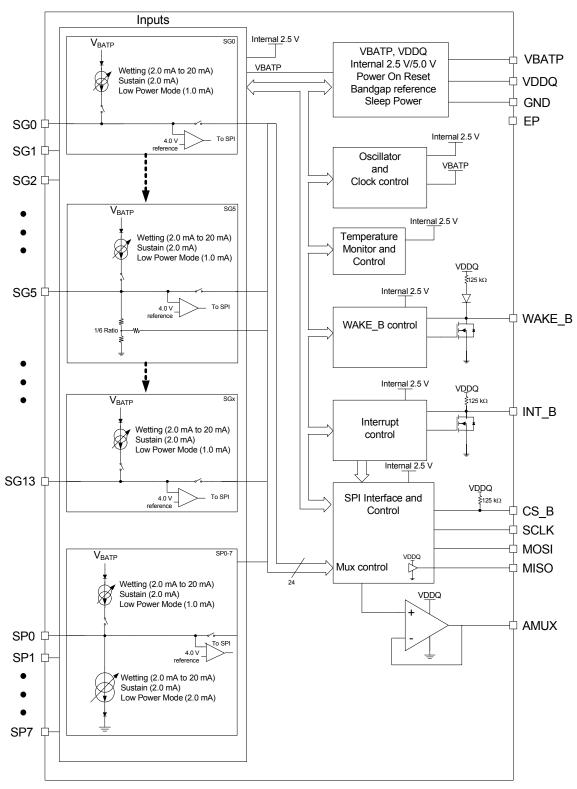

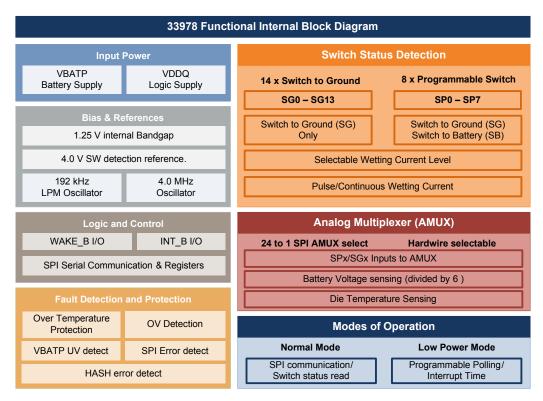

# 2 Internal Block Diagram

Figure 2. 33978 Internal Block Diagram

# 3 Pin Connections

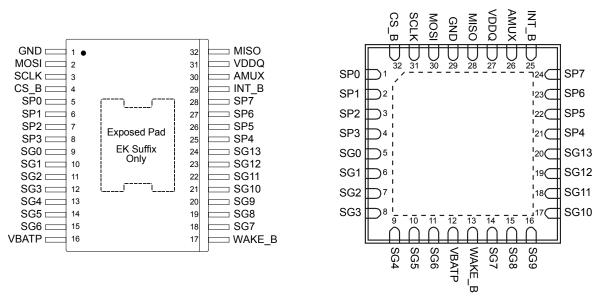

#### 3.1 Pinout

#### **Transparent Top View**

Figure 3. 33978 SOICW-EP and QFN (WF-Type) Pinouts

### 3.2 Pin Definitions

Table 2. 33978 Pin Definitions

| Pin Number<br>SOIC | Pin Number<br>QFN | Pin Name         | Pin Function | Formal Name                     | Definition                                                                                                                                                  |

|--------------------|-------------------|------------------|--------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | 29                | GND              | Ground       | Ground                          | Ground for logic, analog                                                                                                                                    |

| 2                  | 30                | MOSI             | Input/SPI    | SPI Slave In                    | SPI control data input pin from the MCU                                                                                                                     |

| 3                  | 31                | SCLK             | Input/SPI    | Serial Clock                    | SPI control clock input pin                                                                                                                                 |

| 4                  | 32                | CS_B             | Input/SPI    | Chip Select                     | SPI control chip select input pin                                                                                                                           |

| 5–8<br>25–28       | 1 - 4<br>21 - 24  | SP0-3<br>SP4-7   | Input        | Programmable<br>Switches 0–7    | Switch to programmable input pins (SB or SG)                                                                                                                |

| 9–15,<br>18–24     | 5 - 11<br>14 - 20 | SG0-6,<br>SG7-13 | Input        | Switch-to-Ground<br>Inputs 0–13 | Switch-to-ground input pins                                                                                                                                 |

| 16                 | 12                | VBATP            | Power        | Battery Input                   | Battery supply input pin. Pin requires external reverse battery protection                                                                                  |

| 17                 | 13                | WAKE_B           | Input/Output | Wake-up                         | Open drain wake-up output. Designed to control a power supply enable pin. Input used to allow a wake-up from an external event.                             |

| 29                 | 25                | INT_B            | Input/Output | Interrupt                       | Open-drain output to MCU. Used to indicate an input switch change of state. Used as an input to allow wake-up from LPM via an external INT_B falling event. |

| 30                 | 26                | AMUX             | Output       | Analog Multiplex Output         | Analog multiplex output.                                                                                                                                    |

| 31                 | 27                | VDDQ             | Input        | Voltage Drain Supply            | 3.3 V/5.0 V supply. Sets SPI communication level for the MISO driver and I/O level buffer                                                                   |

#### Table 2. 33978 Pin Definitions (continued)

| Pin Number<br>SOIC | Pin Number<br>QFN | Pin Name | Pin Function | Formal Name   | Definition                                                                             |

|--------------------|-------------------|----------|--------------|---------------|----------------------------------------------------------------------------------------|

| 32                 | 28                | MISO     | Output/SPI   | SPI Slave Out | Provides digital data from the 33978 to the MCU.                                       |

|                    |                   | EP       | Ground       | Exposed Pad   | It is recommended that the exposed pad is terminated to GND (pin 1) and system ground. |

### 4 General Product Characteristics

## 4.1 Maximum Ratings

#### **Table 3. Maximum Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                                                                                                          | Description (Rating)                                                                                                                                                                                                                                                                                | Min.     | Max.                                   | Unit | Notes |

|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------|------|-------|

| ELECTRICAL RA                                                                                                   | TINGS                                                                                                                                                                                                                                                                                               | <b>"</b> | 1                                      |      |       |

| VBATP                                                                                                           | Battery Voltage                                                                                                                                                                                                                                                                                     | -0.3     | 40                                     | V    |       |

| VDDQ                                                                                                            | Supply Voltage                                                                                                                                                                                                                                                                                      | -0.3     | 7.0                                    | V    |       |

| CS_B, MOSI,<br>MISO, SCLK                                                                                       | SPI Inputs/Outputs                                                                                                                                                                                                                                                                                  | -0.3     | 7.0                                    | V    |       |

| SGx, SPx                                                                                                        | Switch Input Range                                                                                                                                                                                                                                                                                  | -14      | 38                                     | V    |       |

| AMUX                                                                                                            | AMUX                                                                                                                                                                                                                                                                                                | -0.3     | 7.0                                    | V    |       |

| INT_B                                                                                                           | INT_B                                                                                                                                                                                                                                                                                               | -0.3     | 7.0                                    | V    |       |

| WAKE_B                                                                                                          | WAKE_B                                                                                                                                                                                                                                                                                              | -0.3     | 40                                     | V    |       |

| V <sub>ESD1-2</sub><br>V <sub>ESD1-3</sub><br>V <sub>ESD3-1</sub><br>V <sub>ESD2-1</sub><br>V <sub>ESD2-2</sub> | ESD Voltage  • Human Body Model (HBM) (VBATP versus GND)  • Human Body Model (HBM) (All other pins)  • Machine Model (MM)  • Charge Device Model (CDM) (Corners pins)  • Charge Device Model (CDM) (All other pins)                                                                                 |          | ±2000<br>±2000<br>±200<br>±750<br>±500 | V    | (2)   |

| VESD5-3<br>VESD5-4<br>VESD6-1<br>VESD6-2                                                                        | <ul> <li>Contact Discharge</li> <li>VBATP <sup>(5)</sup></li> <li>WAKE_B (series resistor 10 kΩ)</li> <li>SGx and SPx pins with 100 nF capacitor (100 Ω series R) based on external protection performance<sup>(4)</sup></li> <li>SGx and SPx pins with 100 nF capacitor (50 Ω series R)</li> </ul> |          | ±8000<br>±8000<br>±15000<br>±8000      | V    | (3)   |

#### Notes

- 2. ESD testing is performed in accordance AEC Q100, with the Human Body Model (HBM) ( $C_{ZAP}$  = 100 pF,  $R_{ZAP}$  = 1500  $\Omega$ ), the Machine Model (MM) ( $C_{ZAP}$  = 200 pF,  $R_{ZAP}$  = 0  $\Omega$ ), and the Charge Device Model (CDM).

- 3.  $C_{ZAP}$  = 330 pF,  $R_{ZAP}$  = 2.0 k $\Omega$  (Powered and unpowered) /  $C_{ZAP}$  = 150 pF,  $R_{ZAP}$  = 330  $\Omega$  (Unpowered)

- 4. ±15000V capability in powered condition, ±8000V in all other conditions.

- External component requirements at system level: C<sub>bulk</sub> = 100uF aluminum electrolytic capacitor

C<sub>bypass</sub>=100nF ±37% ceramic capacitor

Reverse blocking diode from Battery to VBATP (0.6 V <  $V_F$  < 1 V). see <u>Figure 24, Typical Application Diagram</u>.

#### 4.2 Thermal Characteristics

#### **Table 4. Thermal Ratings**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol            | Description (Rating)                          | Min.       | Max.       | Unit | Notes |

|-------------------|-----------------------------------------------|------------|------------|------|-------|

| THERMAL RAT       | INGS                                          |            |            |      |       |

| T <sub>A</sub>    | Operating Temperature                         | -40<br>-40 | 125<br>150 | °C   |       |

| T <sub>STG</sub>  | Storage Temperature                           | -65        | 150        | °C   |       |

| T <sub>PPRT</sub> | Peak Package Reflow Temperature During Reflow | _          | _          | °C   |       |

| THERMAL DEC       | 10741105                                      |            |            |      |       |

#### THERMAL RESISTANCE

| $R_{\ThetaJA}$  | Junction-to-Ambient, Natural Convection, Single-Layer Board • 32 SOIC-EP • 32 QFN | 79<br>TBD | °C/W | (6),(7) |

|-----------------|-----------------------------------------------------------------------------------|-----------|------|---------|

| $R_{\Theta JB}$ | Junction-to-Board                                                                 | 9         | °C/W | (8)     |

| $R_{\ThetaJC}$  | Junction-to-Case (Bottom)  • 32 SOIC-EP  • 32 QFN                                 | 3<br>TBD  | °C/W | (9)     |

| $\Psi_{JT}$     | Junction-to-Package (Top), Natural convection  • 32 SOIC-EP  • 32 QFN             | 11<br>TBD | °C/W | (10)    |

#### **PACKAGE DISSIPATION RATINGS**

| T <sub>SD</sub>  | Thermal Shutdown  • 32 SOIC-EP  • 32 QFN            | 155 | 185 | °C |  |

|------------------|-----------------------------------------------------|-----|-----|----|--|

| T <sub>SDH</sub> | Thermal Shutdown Hysteresis  • 32 SOIC-EP  • 32 QFN | 3.0 | 15  | °C |  |

#### Notes

- 6. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 7. Per JEDEC JESD51-2 with natural convection for horizontally oriented board. Board meets JESD51-9 specification for 1s or 2s2p board, respectively.

- 8. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 9. Thermal resistance between the die and the solder pad on the bottom of the package based on simulation without any interface resistance.

- 10. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

# 4.3 Operating Conditions

This section describes the operating conditions of the device. Conditions apply to all the following data, unless otherwise noted.

#### **Table 5. Operating Conditions**

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Symbol                    | Ratings              | Min  | Max  | Unit | Notes |

|---------------------------|----------------------|------|------|------|-------|

| VBATP                     | Battery Voltage      | 4.5  | 36   | V    |       |

| VDDQ                      | Supply Voltage       | 3.0  | 5.25 | V    |       |

| CS_B, MOSI,<br>MISO, SCLK | SPI Inputs / Outputs | 3.0  | 5.25 | V    |       |

| SGx, SPx                  | Switch Input Range   | -1.0 | 36   | V    |       |

| AMUX, INT_B               | AMUX, INT_B          | 0.0  | 5.25 | V    |       |

| WAKE_B                    | WAKE_B               | 0.0  | 36   | V    |       |

### 4.4 Electrical Characteristics

#### 4.4.1 Static Electrical Characteristics

**Table 6. Static Electrical Characteristics**

$T_A$  = -40 °C to +125 °C, VDDQ = 3.1 V to 5.25 V, VBATP = 6 V to 28.0 V, unless otherwise noted.

| Symbol                     | Characteristic                                                                                                                                                                                                                          | Min  | Тур | Max      | Units | Notes |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|----------|-------|-------|

| ower Input                 |                                                                                                                                                                                                                                         |      | 1   |          |       |       |

| V <sub>BATP(POR)</sub>     | VBATP Supply Voltage POR  • VBATP Supply Power on Reset voltage.                                                                                                                                                                        | 2.7  | 3.3 | 3.8      | V     |       |

| V <sub>BATPUV</sub>        | VBATP Undervoltage Rising Threshold                                                                                                                                                                                                     | _    | 4.3 | 4.5      | V     |       |

| V <sub>BATPUVHYS</sub>     | VBATP Undervoltage Hysteresis                                                                                                                                                                                                           | 250  | _   | 500      | mV    |       |

| V <sub>BATPOV</sub>        | VBATP Overvoltage Rising Threshold                                                                                                                                                                                                      | 32   | _   | 37       | V     |       |

| V <sub>BATPOVHYS</sub>     | VBATP Overvoltage Hysteresis                                                                                                                                                                                                            | 1.5  | _   | 3.0      | V     |       |

| I <sub>BAT(ON)</sub>       | VBATP Supply Current • All switches open, Normal mode, Tri-state disabled (all channels)                                                                                                                                                | _    | 7.0 | 12       | mA    |       |

| I <sub>BATP,IQ,LPM,P</sub> | <ul> <li>VBATP Low-power Mode Supply Current (polling disabled)</li> <li>Parametric V<sub>BATP</sub>, 6.0 V &lt; V<sub>BATP</sub> &lt; 28 V</li> <li>Functional Low V<sub>BATP</sub>, 4.5 V &lt; V<sub>BATP</sub> &lt; 6.0 V</li> </ul> | _    |     | 40<br>40 | μА    |       |

| I <sub>POLLING,IQ</sub>    | VBATP Polling Current • Polling 64 ms, 11 inputs of wake enabled                                                                                                                                                                        | _    | _   | 20       | μА    | (11)  |

| I <sub>VDDQ,NORMAL</sub>   | Normal Mode (I <sub>VDDQ</sub> ) • SCLK, MOSI, WakeB = 0 V, CS_B, INT_B =V <sub>DDQ</sub> , no SPI communication, AMUX selected no input                                                                                                | _    | _   | 500      | uA    |       |

| $I_{VDDQ,LPM}$             | Logic Low-power Mode Supply Current  • SCLK, MOSI = 0 V, CS_B, INT_B, WAKE_B = V <sub>DDQ</sub> , no SPI communication                                                                                                                  | _    | _   | 10       | μА    |       |

| V <sub>GNDOFFSET</sub>     | Ground Offset Ground offset of Global pins to IC ground                                                                                                                                                                                 | -1.0 | _   | 1.0      | V     |       |

| VDDQ <sub>UV</sub>         | VDDQ Undervoltage Falling Threshold                                                                                                                                                                                                     | 2.2  | _   | 2.8      | V     |       |

| VDDQ <sub>UVHYS</sub>      | VDDQ Undervoltage Hysteresis                                                                                                                                                                                                            | 150  | _   | 350      | mV    |       |

#### Table 6. Static Electrical Characteristics (continued)

$T_A$  = -40 °C to +125 °C, VDDQ = 3.1 V to 5.25 V, VBATP = 6 V to 28.0 V, unless otherwise noted.

| Symbol                    | Characteristic                                                                                                                                                                          | Min                                           | Тур                                  | Max                                                | Units | Notes      |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------|----------------------------------------------------|-------|------------|

| Switch Input              |                                                                                                                                                                                         |                                               |                                      |                                                    |       | 1          |

| I <sub>LEAKSG_GND</sub>   | Leakage (SGx/SPx pins) to GND  • Inputs tri-stated, analog mux selected for each input, voltage at SGx = VBATP                                                                          | _                                             | _                                    | 2.0                                                | μΑ    |            |

| I <sub>LEAKSG_BAT</sub>   | Leakage (SGx/SPx pins) to Battery Inputs tri-stated, analog mux selected for each input, voltage at SGx = GND                                                                           | _                                             | _                                    | 2.0                                                | μА    |            |

| I <sub>SUSSG</sub>        | SG Sustain current / Mode 0 Wetting current  • VBATP 6.0 to 28 V                                                                                                                        | 1.6                                           | 2.0                                  | 2.4                                                | mA    |            |

| I <sub>SUSSGLV</sub>      | SG Sustain current / Mode 0 Wetting current LV (12)  • VBATP 4.5 V to 6.0 V                                                                                                             | 1.0                                           | _                                    | 2.4                                                | mA    |            |

| I <sub>SUSSB</sub>        | SB Sustain current / Mode 0 Wetting current                                                                                                                                             | 1.75                                          | 2.2                                  | 2.85                                               | mA    |            |

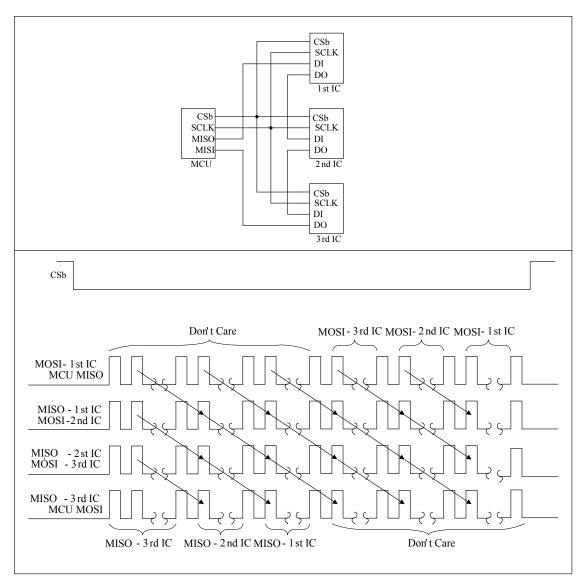

| I <sub>WET</sub>          | Wetting current level (SG & SB)  • Mode 1 = 6mA  • Mode 2 = 8mA  • Mode 3 = 10mA  • Mode 4 = 12mA  • Mode 5 = 14mA  • Mode 6 = 16mA  • Mode 7 = 20mA                                    | _                                             | 6<br>8<br>10<br>12<br>14<br>16<br>20 | _                                                  | mA    |            |

| I <sub>WETSG</sub>        | SG wetting current tolerance • Mode 1 to 7                                                                                                                                              | -10                                           |                                      | 10                                                 | %     |            |

| I <sub>WETSGLV</sub>      | SG wetting current tolerance LV (VBATP 4.5 to 6.0V) <sup>(12)</sup> • Mode 1 = 6mA  • Mode 2 = 8mA  • Mode 3 = 10mA  • Mode 4 = 12mA  • Mode 5 = 14mA  • Mode 6 = 16mA  • Mode 7 = 20mA | 2.0<br>2.0<br>2.0<br>2.0<br>2.0<br>2.0<br>2.0 | -<br>-<br>-<br>-<br>-                | 6.6<br>8.8<br>11.0<br>13.2<br>15.4<br>17.6<br>22.0 | mA    |            |

| I <sub>WETSB</sub>        | SB wetting current tolerance • Mode 1 to 7                                                                                                                                              | -20                                           |                                      | 20                                                 | %     |            |

| I <sub>MATCH(SUS)</sub>   | Sustain Current Matching Between Channels                                                                                                                                               | _                                             | _                                    | 10                                                 | %     | (13), (14) |

| I <sub>MATCH(WET)</sub>   | Wetting Current Matching Between Channels                                                                                                                                               | _                                             | _                                    | 6.0                                                | %     | (15), (16) |

| V <sub>ICTHR</sub>        | Switch Detection Threshold                                                                                                                                                              | 3.7                                           | 4.0                                  | 4.3                                                | V     | (17)       |

| V <sub>ICTHRLV</sub>      | Switch Detection Threshold Low Battery  • VBATP 4.5 V to 6.0 V                                                                                                                          | 0.55 *<br>V <sub>BATP</sub>                   | _                                    | 4.3                                                | V     |            |

| V <sub>ICTHRLPM</sub>     | Switch Detection Threshold Low Power Mode (SG only)                                                                                                                                     | 100                                           |                                      | 300                                                | mV    | (18)       |

| V <sub>ICTHRH</sub>       | Switch Detection Threshold Hysteresis (4.0 V threshold)                                                                                                                                 | 80                                            | _                                    | 300                                                | mV    |            |

| V <sub>ICTH2P5</sub>      | Input Threshold 2.5 V,  • Used for Comp Only and for AMUX Hardwired Select (SG1/2/3)                                                                                                    | 2.0                                           | 2.5                                  | 3.0                                                | V     |            |

| I <sub>ACTIVEPOLLSG</sub> | Low-power Mode Polling Current SG  • VBATP 4.5 V to 28 V                                                                                                                                | 0.7                                           | 1.0                                  | 1.44                                               | mA    |            |

| I <sub>ACTIVEPOLLSB</sub> | Low-power Mode Polling Current SB                                                                                                                                                       | 1.75                                          | 2.2                                  | 2.85                                               | mA    |            |

#### Table 6. Static Electrical Characteristics (continued)

$T_A$  = -40 °C to +125 °C, VDDQ = 3.1 V to 5.25 V, VBATP = 6 V to 28.0 V, unless otherwise noted.

| Symbol                               | Characteristic                                                                                                          | Min                     | Тур  | Max                    | Units | Notes |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------------------|------|------------------------|-------|-------|

| DIGITAL INTERF                       | ACE                                                                                                                     |                         |      |                        |       |       |

| I <sub>HZ</sub>                      | Tri-state Leakage Current (MISO)  • VDDQ = 0.0 to VDDQ                                                                  | -2.0                    | _    | 2.0                    | μA    |       |

| V <sub>INLOGIC</sub>                 | Input Logic Voltage Thresholds • SI, SCLK, CS_B, INT_B                                                                  | V <sub>DDQ</sub> * 0.25 | _    | V <sub>DDQ</sub> * 0.7 | V     |       |

| V <sub>INLOGICHYS</sub>              | Input Logic Hysteresis • SI, SCLK, CS_B, INT_B                                                                          | 300                     | _    | _                      | mV    |       |

| V <sub>INLOGICWAKE</sub>             | Input Logic Voltage Threshold WAKE_B                                                                                    | 0.8                     | 1.25 | 1.7                    | V     |       |

| V <sub>INWAKEBHYS</sub>              | Input Logic Voltage Hysteresis WAKE_B                                                                                   | 200                     | _    | 800                    | mV    |       |

| I <sub>SCLK,</sub> I <sub>MOSI</sub> | SCLK / MOSI Input Current • SCLK / MOSI = 0 V                                                                           | -3.0                    | _    | 3.0                    | μA    |       |

| I <sub>SCLK,</sub> I <sub>MOSI</sub> | SCLK / MOSI Pull-down Current • SCLK / MOSI = VDDQ                                                                      | 30                      | _    | 100                    | μA    |       |

| I <sub>CS_BH</sub>                   | CS_B Input Current • CS_B = VDDQ                                                                                        | -10                     | _    | 10                     | μΑ    |       |

| R <sub>CS_BL</sub>                   | CS_B Pull-up Resistor to VDDQ • CS_B = 0.0 V                                                                            | 40                      | 125  | 270                    | kΩ    |       |

| V <sub>OHMISO</sub>                  | MISO High-side Output Voltage • I <sub>OHMISO</sub> = -1.0 mA                                                           | V <sub>DDQ</sub> - 0.8  | _    | $V_{\mathrm{DDQ}}$     | ٧     |       |

| V <sub>OLMISO</sub>                  | MISO Low-side Output Voltage • I <sub>OLMISO</sub> = 1.0 mA                                                             | _                       | _    | 0.4                    | ٧     |       |

| C <sub>IN</sub>                      | Input Capacitance on SCLK, MOSI, Tri-state MISO (GBD)                                                                   |                         | _    | 20                     | pF    |       |

| Analog MUX Out                       | put                                                                                                                     | l l                     |      |                        |       |       |

| V <sub>OFFSET</sub>                  | Input Offset Voltage When Selected as Analog                                                                            | -10                     | _    | 10                     | mV    |       |

| V <sub>OLAMUX</sub>                  | Analog Operational Amplifier Output Voltage • Sink 1.0 mA                                                               | _                       | _    | 50                     | mV    |       |

| V <sub>OHAMUX</sub>                  | Analog Operational Amplifier Output Voltage • Source 1.0 mA                                                             | V <sub>DDQ</sub> – 0.1  | _    | _                      | ٧     |       |

| AMUX Selectable                      | Outputs                                                                                                                 |                         |      |                        |       |       |

| Temp-Coeff                           | Chip Temperature Sensor Coefficient                                                                                     | _                       | 8.0  | _                      | mV/°C |       |

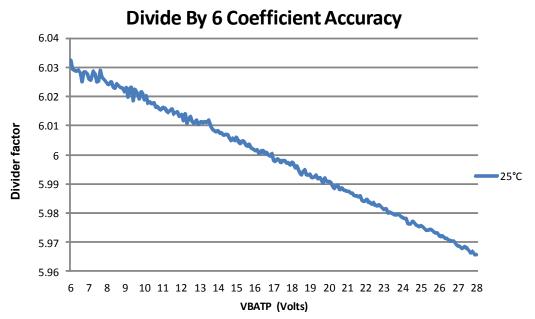

| V <sub>BATSNSACC</sub>               | Battery Sense (SG5 config) Accuracy  • Battery voltage (SG5 input) divided by 6  • Accuracy over full temperature range | -5.0                    | _    | 5.0                    | %     |       |

| V <sub>BATSNSDIV</sub>               | Divider By 6 coefficient accuracy  • Offset over operating voltage range (VBATP=6V to 28V)                              | -3.0                    | _    | 3.0                    | %     | (19)  |

| NT_B                                 | •                                                                                                                       |                         |      |                        |       |       |

| V <sub>OLINT</sub>                   | INT_B Output Low Voltage  • I <sub>OUT</sub> = 1.0 mA                                                                   | _                       | 0.2  | 0.5                    | V     |       |

| V <sub>OHINT</sub>                   | INT_B Output High Voltage • INT_B = Open-circuit                                                                        | V <sub>DDQ</sub> - 0.5  | _    | V <sub>DDQ</sub>       | V     |       |

| R <sub>PU</sub>                      | Pull-up Resistor to VDDQ                                                                                                | 40                      | 125  | 270                    | kΩ    |       |

| I <sub>LEAKINT_B</sub>               | Leakage Current INT_B • INT_B pulled up to VDDQ                                                                         | _                       | _    | 1.0                    | μA    |       |

#### Table 6. Static Electrical Characteristics (continued)

$T_A$  = - 40 °C to +125 °C, VDDQ = 3.1 V to 5.25 V, VBATP = 6 V to 28.0 V, unless otherwise noted.

| Symbol                   | Characteristic                                                                     | Min                   | Тур | Max                | Units | Notes |

|--------------------------|------------------------------------------------------------------------------------|-----------------------|-----|--------------------|-------|-------|

| Temperature Limi         | it                                                                                 | 1                     |     | I                  | I     |       |

| t <sub>FLAG</sub>        | Temperature Warning • First flag to trip                                           | 105                   | 120 | 135                | °C    |       |

| t <sub>LIM</sub>         | Temperature Monitor                                                                | 155                   | _   | 185                | °C    | (20)  |

| t <sub>LIM(HYS)</sub>    | Temperature Monitor Hysteresis                                                     | 5.0                   | _   | 15                 | °C    | (20)  |

| VAKE_B                   |                                                                                    |                       |     |                    |       |       |

| R <sub>WAKE_B(RPU)</sub> | WAKE_B Internal pull-up Resistor to VDDQ                                           | 40                    | 125 | 270                | kΩ    |       |

| V <sub>WAKE_B(VOH)</sub> | WAKE_B Voltage High  • WAKE_B = Open-circuit                                       | V <sub>DDQ</sub> -1.0 | _   | $V_{\mathrm{DDQ}}$ | V     |       |

| V <sub>WAKE_B(VOL)</sub> | WAKE_B Voltage Low • WAKE_B = 1.0 mA (R <sub>PU</sub> to V <sub>BATP</sub> = 16 V) | _                     | _   | 0.4                | ٧     |       |

| I <sub>WAKE_BLEAK</sub>  | WAKE_B Leakage • WAKE_B pulled up to V <sub>BATP</sub> = 16 V through 10 kΩ        | _                     | _   | 1.0                | μΑ    |       |

#### Notes

- 11. Guaranteed by design

- 12. During low voltage range operation SG wetting current may be limited when there is not enough headroom between VBATP and SG pin voltage.

- 13.  $(I_{SUS(MAX)} I_{SUS(MIN)}) \times 100/I_{SUS(MIN)}$

- 14. Sustain current source (SGs only)

- 15. (I<sub>WET(MAX)</sub> I<sub>WET(MIN)</sub>) X 100/I<sub>WET(MIN)</sub>

- 16. Wetting current source (SGs only)

- 17. The input comparator threshold decreases when  $V_{BATP} \le 6.0 \text{ V}$ .

- 18. SP (as SB) only use the 4.0 V  $V_{\mbox{\scriptsize ICTHR}}$  for LPM wake-up detection.

- 19. Calibration of divider ratio can be done at V<sub>BAT</sub> = 12 V, 25 °C to achieve a higher accuracy. See <u>Figure 4</u> for AMUX offset linearity waveform through the operating voltage range.

- 20. Guaranteed by Characterization in the Development Phase, parameter not tested.

# 4.4.2 Dynamic Electrical Characteristics

#### **Table 7. Dynamic Electrical Characteristics**

$T_A$  = -40 °C to +125 °C. VDDQ = 3.1 V to 5.25 V, VBATP = 4.5 V to 28 V, unless otherwise specified. All SPI timing is performed with a 100 pF load on MISO, unless otherwise noted.

| Symbol                        | Parameter                                                                                                           | Min         | Тур       | Max         | Units    | Notes |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------|-----------|-------------|----------|-------|

| General                       |                                                                                                                     |             |           |             |          |       |

| t <sub>ACTIVE</sub>           | POR to Active time  • Undervoltage to Normal mode                                                                   | 250         | 340       | 450         | μs       |       |

| Switch Input                  |                                                                                                                     | •           |           |             |          | •     |

| t <sub>PULSE(ON)</sub>        | Pulse Wetting Current Timer  • Normal mode                                                                          | 17          | 20        | 23          | ms       |       |

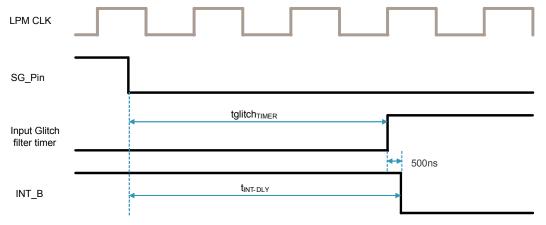

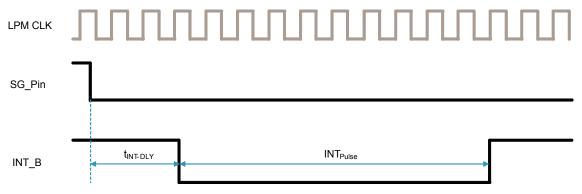

| t <sub>INT-DLY</sub>          | Interrupt Delay Time • Normal mode                                                                                  | _           | _         | 18.5        | μs       |       |

| t <sub>POLLING_TIMER</sub>    | Polling Timer Accuracy • Low-power mode                                                                             | _           | _         | 15          | %        |       |

| t <sub>INT-TIMER</sub>        | Interrupt Timer Accuracy  • Low-power mode                                                                          | _           | _         | 15          | %        |       |

| t <sub>ACTIVEPOLLSGTIME</sub> | Tactivepoll Timer SG                                                                                                | 49.5        | 58        | 66.5        | μs       |       |

| tactivepollsbtime             | Tactivepoll Timer SB  • SBPOLLTIME=0  • SBPOLLTIME=1                                                                | 1.0<br>49.5 | 1.2<br>58 | 1.4<br>66.5 | ms<br>µs |       |

| t <sub>GLITCHTIMER</sub>      | Input Glitch Filter Timer  • Normal mode                                                                            | 5.0         | _         | 18          | μs       |       |

| t <sub>DEBOUNCE</sub>         | LPM Debounce Additional Time  • Low-power mode                                                                      | 1.0         | 1.2       | 1.4         | ms       |       |

| AMUX Output                   |                                                                                                                     |             | l         | l           |          |       |

| AMUX <sub>VALID</sub>         | AMUX Access Time (Selected Output to Selected Output)  • C <sub>MUX</sub> = 1.0 nF, Rising edge of CS_B to selected | _           | (22)      | _           | μs       |       |

| AMUX <sub>VALIDTS</sub>       | AMUX Access Time (Tristate to ON) • C <sub>MUX</sub> = 1.0 nF, Rising edge of CS_B to selected                      | _           | _         | 20          | μs       |       |

| Oscillator                    |                                                                                                                     | <b>'</b>    | •         | •           |          | •     |

| OSC <sub>TOLLPM</sub>         | Oscillator Tolerance at 192 kHz in Low-power Mode                                                                   | -15         | _         | 15          | %        |       |

| OSC <sub>TOLNOR</sub>         | Oscillator Tolerance Normal Mode at 4.0 MHz                                                                         | -15         | _         | 15          | %        |       |

| Interrupt                     |                                                                                                                     | <u>.</u>    |           |             |          |       |

| INT <sub>PULSE</sub>          | INTPulse Duration • Interrupt occurs or INT_B request                                                               | 90          | 100       | 110         | μs       |       |

| SPI Interface                 |                                                                                                                     |             |           |             |          |       |

| f <sub>OP</sub>               | Transfer Frequency                                                                                                  | _           | _         | 8.0         | MHz      |       |

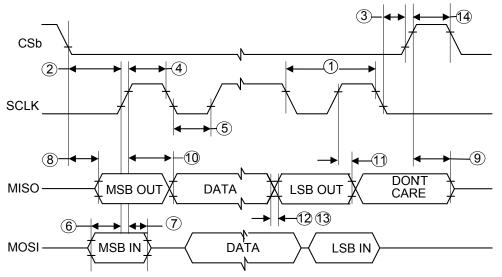

| t <sub>SCK</sub>              | SCLK Period • Figure 7 - 1                                                                                          | 160         | _         | _           | ns       |       |

| t <sub>LEAD</sub>             | Enable Lead Time • Figure 7 - 2                                                                                     | 140         | _         | _           | ns       |       |

| t <sub>LAG</sub>              | Enable Lag Time • Figure 7 - 3                                                                                      | 50          | _         | _           | ns       |       |

| t <sub>SCKHS</sub>            | SCLK High Time • Figure 7 - 4                                                                                       | 56          | _         | _           | ns       |       |

#### Table 7. Dynamic Electrical Characteristics (continued)

$T_A$  = -40 °C to +125 °C. VDDQ = 3.1 V to 5.25 V, VBATP = 4.5 V to 28 V, unless otherwise specified. All SPI timing is performed with a 100 pF load on MISO, unless otherwise noted.

| Symbol             | Parameter                                               | Min | Тур | Max | Units | Notes |

|--------------------|---------------------------------------------------------|-----|-----|-----|-------|-------|

| Interface (C       | ontinued)                                               | 1   | 1   |     |       |       |

| t <sub>SCKLS</sub> | SCLK Low Time • Figure 7 - 5                            | 56  | _   | _   | ns    |       |

| t <sub>SUS</sub>   | MOSI Input Setup Time • Figure 7 - 6                    | 16  | _   | _   | ns    |       |

| t <sub>HS</sub>    | MOSI Input Hold Time • Figure 7 - 7                     | 20  | _   | _   | ns    |       |

| t <sub>A</sub>     | MISO Access Time • Figure 7 - 8                         | _   | _   | 116 | ns    |       |

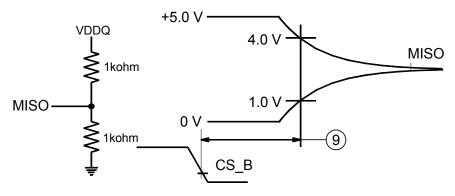

| t <sub>DIS</sub>   | MISO Disable Time <sup>(21)</sup> • Figure 7 - 9        | _   | _   | 100 | ns    |       |

| t <sub>VS</sub>    | MISO Output Valid Time • Figure 7 - 10                  | _   | _   | 116 | ns    |       |

| t <sub>HO</sub>    | MISO Output Hold Time (No cap on MISO)  • Figure 7 - 11 | 20  | _   | _   | ns    |       |

| t <sub>RO</sub>    | Rise Time • Figure 7 - 12                               | _   | _   | 30  | ns    | (21)  |

| t <sub>FO</sub>    | Fall Time • Figure 7 - 13                               | _   | _   | 30  | ns    | (21)  |

| t <sub>CSN</sub>   | CS_B Negated Time • Figure 7 - 14                       | 500 | _   | _   | ns    |       |

#### Notes

- 21. Guaranteed by characterization.

- 22. AMUX settling time to be within the 10 mV offset specification. AMUX<sub>VALID</sub> is dependant of the voltage step applied on the input SGx/SPx pin or the difference between the first and second channel selected as the multiplexed analog output. See <u>Figure 9</u> for a typical AMUX access time VS voltage step waveform.

Figure 4. Divide by 6 Coefficient Accuracy

Figure 5. Glitch Filter and Interrupt Delay timers

Figure 6. Interrupt Pulse Timer

Figure 7. SPI Timing Diagram

Figure 8. MISO Loading for Disable Time Measurement

#### **AMUX Settling time vs Voltage Step** Settling time (us) AMUX Access Time Step Size (mV)

Figure 9. AMUX Access Time Waveform

# 5 General Description

The 33978 is designed to detect the closing and opening of up to 22 switch contacts. The switch status, either open or closed, is transferred to the microprocessor unit (MCU) through a serial peripheral interface (SPI). Individually selectable input currents are available in Normal and Low-power (LPM) modes, as needed for the application.

It also features a 24-to-1 analog multiplexer for reading inputs as analog. The analog input signal is buffered and provided on the AMUX output pin for the MCU to read. A battery and temperature monitor are included in the IC and available via the AMUX pin.

The 33978 device has two modes of operation, Normal and Low Power mode (LPM). Normal mode allows programming of the device and supplies switch contacts with pull-up or pull-down current as it monitors the change of state of switches. The LPM provides low quiescent current, which makes the 33978 ideal for automotive and industrial products requiring low sleep-state currents.

#### 5.1 Features

- Fully functional operation from 4.5 V to 36 V

- Full parametric operation from 6.0 V to 28 V

- Low-power mode current  $I_{BATP}$  = 30  $\mu A$  and  $I_{DDQ}$  = 10  $\mu A$

- 22 Switch detection channels

- 14 Switch-to-Ground (SG) inputs

- · Eight Programmable switch (SP) inputs

- Switch-to-Ground (SG) or Switch-to-Battery (SB)

- Operating switch input voltage range from -1.0 V to 36 V

- Selectable wetting current (2, 6, 8, 10, 12, 14, 16, or 20 mA)

- Programmable wetting operation (Pulse or Continuous)

- Selectable wake-up on change of state

- · 24 to 1 Analog Multiplexer

- · Buffered AMUX output from SG/SP channels

- Integrated divider by 6 on SG5 for battery voltage sensing

- Integrated die temperature sensing through AMUX output

- · Two or three pin hardwire AMUX selection.

- · Active interrupt (INT B) on change-of-switch state

- Direct MCU Interface through 3.3 V / 5.0 V SPI protocol

# 5.2 Functional Block Diagram

Figure 10. Functional Block Diagram

# **6** General IC Functional Description

The 33978 device interacts with many connections outside the module and near the end user. The IC detects changes in switch state and reports the information to the MCU via the SPI protocol. The input pins generally connected to switches located outside the module and in proximity to battery in car harnesses. Consequently, the IC must have some external protection including an ESD capacitor and series resistors, to ensure the energy from the various pulses are limited at the IC.

The IC requires a blocking diode be used on the VBATP pin to protect from a reverse battery condition. The inputs are capable of surviving reverse battery without a blocking diode and also contain an internal blocking diode from the input to the power supply (V<sub>BATP</sub>), to ensure there is no backfeeding of voltage/current into the IC, when the voltage on the input is higher than the VBATP pin.

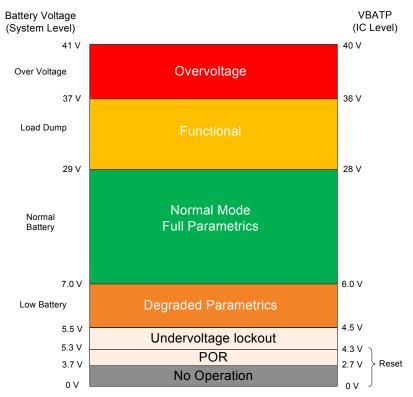

#### 6.1 Battery Voltage Ranges

The 33978 device operates from  $4.5 \text{ V} \le \text{V}_{\text{BATP}} \le 36 \text{ V}$  and is capable to withstand up to 40 V. The IC operates functionally from  $4.5 \text{ V} < \text{V}_{\text{BATP}} < 6.0 \text{ V}$ , but with degraded parametrics values. Voltages in excess of 40 V must be clamped externally in order to protect the IC from destruction. The VBATP pin must be isolated from the main battery node by a diode.

#### 6.1.1 Load Dump (Over voltage)

During load dump the 33978 operates properly up to the  $V_{BATP}$  overvoltage. Voltages greater than load dump (~32 V) causes the current sources to be limited to ~2.0 mA, but the register values are maintained. Upon leaving this overvoltage condition, the original setup is returned and normal operation begins again.

### 6.1.2 Jump Start (Double Battery)

During a jump start (double battery) condition, the device functions normally and meets all the specified parametric values. No internal faults are set and no abnormal operation noted as a result of operating in this range.

#### 6.1.3 Normal Battery Range

The normal voltage range is fully functional with all parametrics in the given specification.

## 6.1.4 Low Voltage Range (Degraded Parametrics)

In the  $V_{BATP}$  range between 4.5 V to 6.0 V the 33978 functions normally, but has some degraded parametric values. The SPI functions normally with no false reporting. The degraded parameters are noted in <u>Table 6</u> and <u>Table 7</u>. During this condition, the input comparator threshold is reduced from 4.0 V and remain ratiometrically adjusted, according to the battery level.

## 6.1.5 Undervoltage Lockout

During undervoltage lockout, the MISO output is tri-stated to avoid any data from being transmitted from the 33978. Any CS\_B pulses are ignored in this voltage range. If the battery enters this range at any point (even during a SPI word), the 33978 ignores the word and enters lockout mode. A SPI bit register is available to notify the MCU that the 33978 has seen an undervoltage lockout condition once the battery is high enough to leave this range.

### 6.1.6 Power On Reset (POR) Activated

The Power on Reset is activated when the VBATP is within the 2.7 V to 3.8 V range. During the POR all SPI registers are reset to default values and SPI operation is disabled. The 33978 is initialized after the POR is de-asserted. A SPI bit in the device configuration register is used to note a POR occurrence and all SPI registers are reset to the default values.

## 6.1.7 No Operation

The device does not function and no switch detection is possible.

Figure 11. Battery Voltage Range

### 6.2 Power Sequencing Conditions

The chip uses two supplies as inputs into the device for various usage. The pins are VBATP and VDDQ. The VBATP pin is the power supply for the chip where the internal supplies are generated and power supply for the SG circuits. The VDDQ pin is used for the I/O buffer supply to talk to the MCU or other logic level devices, as well as AMUX. The INT\_B pin is held low upon POR until the IC is ready to operate and communicate. Power can be applied in various ways to the 33978 and the following states are possible:

### 6.2.1 V<sub>BATP</sub> Before V<sub>DDQ</sub>

The normal condition for operation is the application of  $V_{BATP}$  and then  $V_{DDQ}$ . The chip begin to operate logically in the default state but without the ability to drive logic pins. When the  $V_{DDQ}$  supply is available the chip is able to communicate correctly. The IC maintains its logical state (register settings) with functional behavior consistent with logical state. No SPI communications can occur.

# 6.2.2 V<sub>DDQ</sub> Before V<sub>BATP</sub>

The  $V_{DDQ}$  supply in some cases may be available before the  $V_{BATP}$  supply is ready. In this scenario, there is no back feeding current into the VDDQ pin that could potentially turn on the device into an unknown state. VDDQ is isolated from VBATP circuits and the device is off until VBATP is applied; when  $V_{BATP}$  is available the device powers up the internal rails and logic within  $t_{ACTIVE}$  time. Communication is undefined until the  $t_{ACTIVE}$  time and becomes available after this time frame.

## 6.2.3 V<sub>BATP</sub> Okay, V<sub>DDQ</sub> Lost

After power up, it is possible that the V<sub>DDQ</sub> may turn off or be lost. In this case, the chip will remain in the current state but is not able to communicate. After the VDDQ pin is available again, the chip is ready to communicate.

## 6.2.4 V<sub>DDQ</sub> Okay, V<sub>BATP</sub> Lost

After power up, the V<sub>BATP</sub> supply could be lost. The operation is consistent as when V<sub>DDO</sub> is available before V<sub>BATP</sub>.

# 7 Functional Block Description

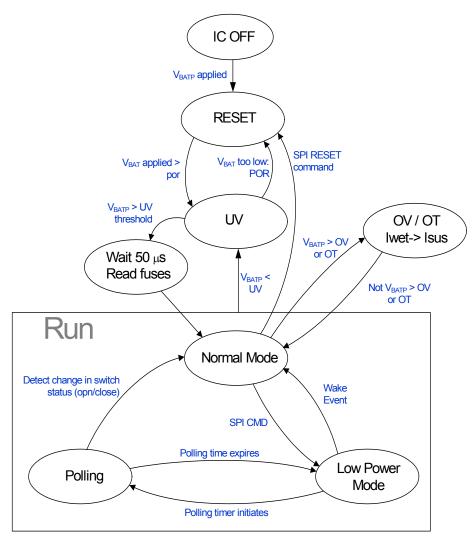

## 7.1 State Diagram

Figure 12. 33978 State Diagram

### 7.1.1 State Machine

After power up, the IC enters into the device state machine, as illustrated in <u>Figure 12</u>. The voltage on VBATP begins to power the internal oscillators and regulator supplies. The POR is based on the internal 2.5 V digital core rail. When the internal logic regulator reaches approximately 1.8 V (typically 3.3 V on the VBATP node), the IC enters into the UV range. Below the POR threshold, the IC is in RESET mode where no activity occurs.

#### 7.1.2 UV: Undervoltage Lockout

After the POR circuit has reset the logic, the IC is in undervoltage. In this state, the IC remembers all register conditions, but is in a lockout mode, where no SPI communication is allowed. The AMUX is inactive and the current sources are off. The user does not receive a valid response from the MISO, as it is disabled in this state. The chip oscillators (4.0 MHz for most normal mode activities, 192 kHz for LPM, and limited normal mode functions) are turned on in the UV state. The chip moves to the Read fuses state when the  $V_{BATP}$  voltage rises above the UV threshold (~4.3 V rising). The internal fuses read in approximately 50  $\mu$ s and the chip enters the Normal mode.

#### 7.1.3 Normal Mode

In normal mode, the chip operates as selected in the available registers. Any command may be loaded in normal mode, although not all (Low-power mode) registers are used in the Normal mode. All the LPM registers must be programmed in Normal mode as the SPI is not active in LPM. The Normal mode of the chip is used to operate the AMUX, communicate via the SPI, Interrupt the IC, wetting and sustain currents, as well as the thresholds available to use. The WAKE\_B pin is asserted (low) in Normal mode and can be used to enable a power supply (ENABLE\_B). Various fault detections are available in this mode including overvoltage, overtemperature, thermal warning, SPI errors, and Hash faults.

#### 7.1.4 Low Power Mode

When the user needs to lower the IC current consumption, a low-power mode is used. The only method to enter LPM is through a SPI word. After the chip is in low-power mode, the majority of circuitry is turned off including most power rails, the 4.0 MHz oscillator, and all the fault detection circuits. This mode is the lowest current consumption mode on the chip. If a fault occurs while the chip is in this mode, the chip does not see or register the fault (does not report via the SPI when awakened). Some items may wake the IC in this mode, including the interrupt timer, falling edge of INT\_B, CS\_B, or WAKE\_B (configurable), or a comparator only mode switch detection.

### 7.1.5 Polling Mode

The 33978 uses a polling mode which periodically (selectable in LPM config register) interrogates the input pins to determine in what state the pins are, and decide if there was a change of state from when the chip was in Normal mode. There are various configurations for this mode, which allow the user greater flexibility in operation. This mode uses the current sources to pull-up (SG) or down (SB) to determine if a switch is open or closed. More information is available on section 7.2, "Low-power Mode Operation".

In the case of a low  $V_{BATP}$ , the polling pauses and waits until the  $V_{BATP}$  rises out of UV or a POR occurs. The pause of the polling ensures all of the internal rails, currents, and thresholds are up at the required levels to accurately detect open or closed switches. The chip does not wake-up in this condition and simply waits for the  $V_{BATP}$  voltage to rise or cause a POR.

After the polling ends, the chip either returns to the low-power mode, or enters Normal mode when a wake event was detected. Other events may wake the chip as well, such as the falling edge of CS\_B, INT\_B, or WAKE\_B (configurable). A comparator only mode switch detection is always on in LPM or Polling mode, so a change of state for those inputs would effectively wake the IC in Polling mode as well. If the Wake-up enable bits are disable on all channels (SG and SP) the device will not wake up with a change of state on any of the input pins; in this case, the device will disable the polling timer to allow the lowest current consumption during low power mode.

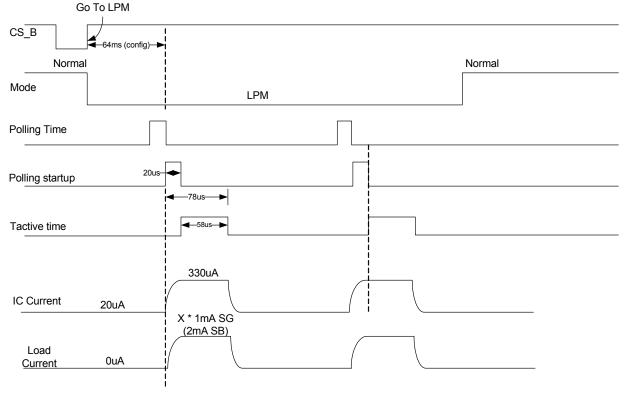

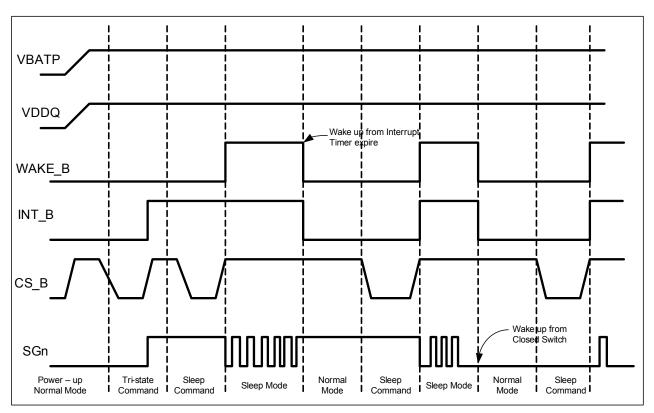

## 7.2 Low-power Mode Operation

Low-power mode (LPM) is used to reduce system quiescent currents. LPM may be entered only by sending the Enter Low-power mode command. All register settings programmed in Normal mode are maintained while in LPM.

The 33978 exits LPM and enter Normal mode when any of the following events occur:

- Input switch change of state (when enabled)

- Interrupt timer expire

- Falling edge of WAKE\_B (as set by the device configuration register)

- Falling edge of INT\_B (with V<sub>DDQ</sub> = 5.0 V)

- Falling edge of CS\_B (with V<sub>DDQ</sub> = 5.0 V)

- · Power-ON Reset (POR)

The  $V_{DDQ}$  supply may be removed from the device during LPM, however removing  $V_{DDQ}$  from the device disables a wake-up from falling edge of INT\_B and CS\_B. The IC checks the status of VDDQ after a falling edge of WAKE\_B (as selected in the device configuration register), INT\_B and CS\_B. The IC returns to LPM and does not report a Wake event, if  $V_{DDQ}$  is low. If the  $V_{DDQ}$  is high, the IC wakes up and reports the Wake event. In cases where CS\_B is used to wake the device, the first MISO data message is not valid.

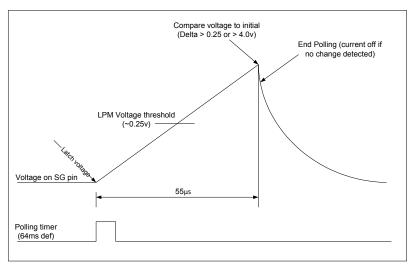

The LPM command contains settings for two programmable registers: the interrupt timer and the polling timer, as shown in <u>Table 26</u>. The interrupt timer is used as a periodic wake-up timer. When the timer expires, an interrupt is generated and the device enters Normal mode. The polling timer is used periodically to poll the inputs during Low-power mode to check for change of states. The t<sub>ACTIVEPOLL</sub> time is the length of time the part is active during the polling timer to check for change of state. The Low-power mode voltage threshold allows the user to determine the noise immunity versus lower current levels that polling allows. <u>Figure 14</u> shows the polling operation.

When polling and Interrupt timer coincide, the Interrupt timer wakes the device and the polling does not occur. When an input is determined to meet the condition Open (when entering LPM), yet while Open (on polling event) the chip does not continue the polling event for that input(s) to lower current in the chip (Figure 13 shows SG, SB is logically the same).

Figure 13. Low-power mode polling check

Figure 14. Low-power Mode Typical Timing

Figure 15. Low-power Mode to Normal Mode Operation

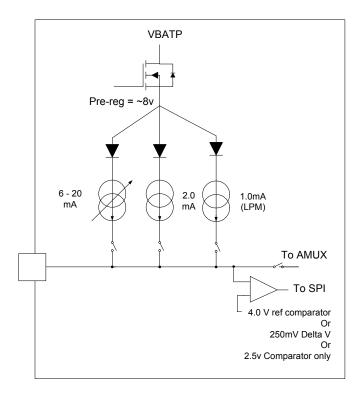

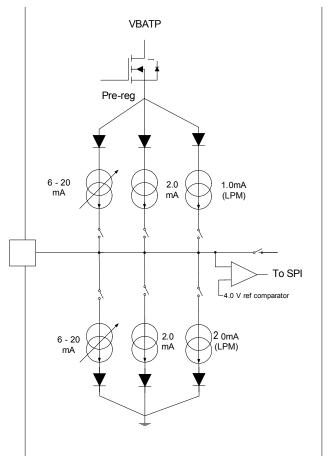

## 7.3 Input Functional Block

The SGx pins are switch-to-ground inputs only (pull-up current sources).

The SPx pins are configurable as either switch to ground or switch to battery (pull-up and pull-down current sources).

The input is compared with a 4.0 V (input comparator threshold configurable) reference. Voltages greater than the input comparator threshold value are considered open for SG pins and closed for SB configuration.

Voltages less than the input comparator threshold value are considered closed for SG pins and open for the SB configurations.

Programming features are defined in the SPI Control Register Definition section of this datasheet.

The input comparator has hysteresis with the thresholds based on the closing of the switch (falling on SG, rising on SB).

The user must take care to keep power conditions within acceptable limits (package is capable of 2.0 W). Using many of the inputs with continuous wetting current levels causes overheating of the IC and may cause an overtemperature (OT) event to occur.

Figure 16. SG Block diagram

Figure 17. SP Block diagram Figure 18.

### 7.4 Oscillator and Timer Control Functional Block

Two oscillators are generated in this block. A 4.0 MHz clock is used in Normal mode only, as well as a Low-power mode 192 kHz clock, which is on all the time. All timers are generated from these oscillators. The oscillator accuracy is 15% for both, the 4.0 MHz clock and the 192 kHz clock. No calibration is needed and the accuracy is over voltage and temperature.

### 7.5 Temperature Monitor and Control Functional Block

The device has multiple thermal limit ( $t_{LIM}$ ) cells to detect thermal excursions in excess of 155 °C. The  $t_{LIM}$  cells from various locations on the IC are logically ORed together and communicated to the MCU as one  $t_{LIM}$  fault. When the  $t_{LIM}$  value is seen, the wetting current is lowered to 2.0 mA until the temperature has decreased beyond the  $t_{LIM(HYS)}$  value (the sustain current remains on or as selected). A hysteresis value of 15 °C exists to keep the device from cycling.

A thermal flag also exists to alert the system to increasing temperatures more than approximately 120 °C.

## 7.6 WAKE\_B Control Functional Block

The WAKE\_B is an input/output pin. As an output, this pin can be used to control the ENABLE pin of an external power supply, to provide the VDDQ voltage. In the Normal mode, the WAKE\_B pin is low. In the Low-power mode, the WAKE\_B pin is high. The WAKE\_B pin has an internal pull-up to VDDQ supply, with a series diode to allow an external pull-up to VBATP if the specific application requires it.

As an input, when the device is in the Low Power mode and WAKE\_B is pulled high, the device can be programmed to wake the 33978 up from LPM with the falling edge of WAKE\_B pin by setting the WAKE\_B bit to 1 on the Device Configuration Register register.

#### 7.7 INT\_B Functional Block

INT\_B is an input/output pin in the 33978 device to indicate an interrupt event has occurred, as well as receiving interrupts from other devices when the INT\_B pins are wired ORed. The INT\_B pin is an open-drain output with an internal pull-up to  $V_{DDQ}$ . In Normal mode, a switch state change triggers the INT\_B pin (when enabled). The INT\_B pin and INT\_B bit in the SPI register are latched on the falling edge of CS\_B. This permits the MCU to determine the origin of the interrupt. When two 33978 devices are used, only the device initiating the interrupt has the INT\_B bit set. The INT\_B pin and INTflg bit are cleared 1.0  $\mu$ s after the falling edge of CS\_B. The INT\_B pin does not clear with the rising edge of CS\_B if a switch contact change has occurred while CS\_B was Low.

In a multiple 33978 device system with WAKE\_B High and  $V_{DDQ}$  on (Low-power mode), the falling edge of INT\_B places all 33978s in Normal mode. The INT\_B has the option of a pulsed output (pulsed low for INT<sub>pulse</sub> duration) or a latched low output. The default case is the latched low operation; the pulsed option is selectable via the SPI.

An INT\_B request by the MCU can be done by a SPI word and results in an INT\_BULSE of 100 µs duration on the INT\_B pin.

The chip causes an INT\_B assertion for the following cases:

- 1. A change of state is detected

- 2. Interrupt timer expires

- Any Wake-up event

- 4. Any faults detected

- 5. After a POR, the INT\_B pin states asserted during startup until the chip is ready to communicate

#### 7.8 AMUX Functional Block

The analog voltage on switch inputs may be read by the MCU using the analog command ( $\underline{\text{Table 43}}$ ). Internal to the IC is a 24-to-1 analog multiplexer. The voltage present on the selected input pin is buffered and made available on the AMUX output pin. The output pin is clamped to a maximum of  $V_{DDQ}$  regardless of the higher voltages present on the input pin. After an input has been selected as the analog, the corresponding bit in the next MISO data stream is logic [0]. When selecting a channel to be read as analog input, the user can also set the current level allowed in the AMUX output. Current level can be set to the programmed wetting current for the selected channel or set to high-impedance as defined in  $\underline{\text{Table 42}}$ .

When selecting an input to be sent to the AMUX output, that input is not polled or a wake-up enabled input from Low-power mode. The user should set the AMUX to "No input selected" or "Temp diode" before entering Low-power mode. The AMUX pin is not active during Low-power mode. The SG5 pin can also be used as a VBATP sense pin. An internal resistor divider of 1/6 is provided for conditioning the  $V_{BATP}$  higher voltage to a level within the 0 V to  $V_{DDQ}$  range.

Besides the default SPI input selection method, the AMUX has two hardwire operation such that the user can select an specific input channel by physically driving the SG1, SG2 or SG3 pin (HW 3-bit), or by driving the SG1 and SG2 pins (HW 2-bit) as shown in <u>Table 9</u> and <u>Table 10</u>. When using the AMUX hardwired options, the SG1, SG2, and SG3 inputs use a 2.5 V input voltage threshold to read a logic 0 or logic 1.

Table 8 shows the AMUX selection methods configurable by the Aconfig0 and Aconfig1 bits in the Device Configuration register.

Т

Table 8. AMUX Selection Method

| Aconfig1 | Aconfig0 AMUX Selection method |          |  |  |  |  |  |

|----------|--------------------------------|----------|--|--|--|--|--|

| 0        | 0 SPI (def)                    |          |  |  |  |  |  |

| 0        | 1                              | SPI      |  |  |  |  |  |

| 1        | 0                              | HW 2-bit |  |  |  |  |  |

| 1        | 1                              | HW 3-bit |  |  |  |  |  |

Table 9. AMUX Hardware 3-bit

| Pins [SG3, SG2, SG1] | Output of AMUX |

|----------------------|----------------|

| 000                  | SG0            |

| 001                  | SG5            |

| 010                  | SG6            |

| 011                  | SG7            |

Table 9. AMUX Hardware 3-bit

| 100 | SG8               |

|-----|-------------------|

| 101 | SG9               |

| 110 | Temperature Diode |

| 111 | Battery Sense     |

Table 10. AMUX Hardware 2-bit

| Pins [SG2, SG1] | Output of AMUX |

|-----------------|----------------|

| 00              | SG0            |

| 01              | SG5            |

| 10              | SG6            |

| 11              | SG7            |

Since the device is required to meet the ±1.0 V offset with ground, it is imperative that the user bring the sensor ground back to the 33978 when using the AMUX for accurate measurements to ensure any ground difference does not impact the device operation.

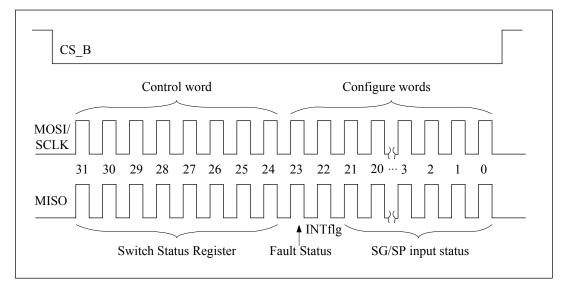

### 7.9 Serial Peripheral Interface (SPI)

The 33978 contains a serial peripheral interface consisting of Serial Clock (SCLK), Serial Data Out (MISO), Serial Data In (MOSI), and Chip Select Bar (CS\_B). The SPI interface is used to provide configuration, control, and status functions; the user may read the registers contents as well as read some status bits of the IC. This device is configured as an SPI slave.

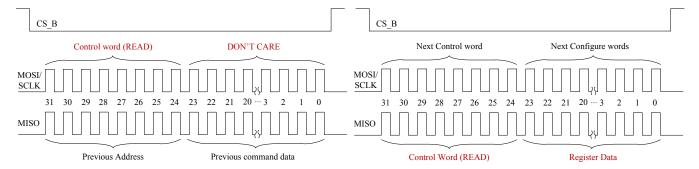

All SPI transmissions to the 33978 must be done in exact increments of 32 bits (modulo 0 is ignored as well). The 33978 contains a data valid method via SCLK input to keep non-modulo-32 bit transmissions from being written into the IC. The SPI module also provides a daisy chain capability to accommodate MOSI to MISO wrap around (see <u>Figure 22</u>).

The SPI registers have a hashing technique to ensure that the registers are consistent with the programmed values. If the hashed value does not match the register status, a SPI bit is set as well as an interrupt to alert the MCU to this issue.

### 7.9.1 Chip Select Low (CS\_B)

The CS\_B input selects this device for serial transfers. On the falling edge of CS\_B, the MISO pin is released from tri-state mode, and all status information are latched in the SPI shift register. While CS\_B is asserted, register data is shifted in the MOSI pin and shifted out the MISO pin on each subsequent SCLK. On the rising edge of CS\_B, the MISO pin is tri-stated and the fault register reloaded (latched) with the current filtered status data. To allow sufficient time to reload the fault registers, the CS\_B pin must remain low for a minimum of t<sub>CSN</sub> prior to going high again.

The CS\_B input contains a pull-up current source to VDDQ to command the de-asserted state should an open-circuit condition occur. This pin has threshold compatible voltages allowing proper operation with microprocessors using a 3.3 V to 5.0 V supply.

## 7.9.2 Serial Clock (SCLK)

The SCLK input is the clock signal input for synchronization of serial data transfer. This pin has a threshold compatible voltages allowing proper operation with microprocessors using a 3.3 V to 5.0 V supply.

When CS\_B is asserted, both the Master Microprocessor and this device latch input data on the rising edge of SCLK. The SPI master typically shifts data out on the falling edge of SCLK, while this device shifts data out on the rising edge of SCLK, to allow more time to drive the MISO pin to the proper level.

This input is used as the input for the modulo-32 bit counter validation. Any SPI transmissions which are NOT exact multiples of 32 bits (i.e. clock edges) is treated as an illegal transmission. The entire frame is aborted and no information is changed in the configuration or control registers.

### 7.9.3 Serial Data Output (MISO)

The MISO output pin is in a tri-state condition when CS\_B is negated. When CS\_B is asserted, MISO is driven to the state of the MSB of the internal register and start shifting out the requested data from the MSB to the LSB. This pin supplies a "rail to rail" output, depending on the voltage at the VDDQ pin.

#### 7.9.4 Serial Data Input (MOSI)

The MOSI input takes data from the master microprocessor while CS\_B is asserted. The MSB is the first bit of each word received on MOSI and the LSB is the last bit of each word received on MOSI. This pin has threshold level compatible input voltages allowing proper operation with microprocessors using a 3.3 V to 5.0 V (V<sub>DDQ</sub>) supply.

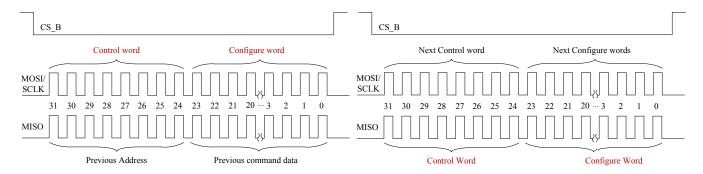

Figure 19. First SPI Operation (After POR)

Figure 20. SPI Write Operation

Figure 21. SPI Read Operation

Figure 22. Daisy Chain SPI Operation

### 7.10 SPI Control Register Definition

A 32-bit SPI allows the system microprocessor to configure the 33978 for each input as well as read out the status of each input. The SPI also allows the Fault Status and INTflg bits to be read via the SPI. The SPI MOSI bit definitions are given in <u>Table 11</u>:

Table 11. MOSI Input Register Bit Definition

| Register # | Register Name                          |   |   |   | Addres | S |   |   | Rb/W |

|------------|----------------------------------------|---|---|---|--------|---|---|---|------|

| 0          | SPI Check                              | 0 | 0 | 0 | 0      | 0 | 0 | 0 | 0    |

| 02/03      | Device Configuration Register          | 0 | 0 | 0 | 0      | 0 | 0 | 1 | 0/1  |

| 04/05      | Tri-state SP Register                  | 0 | 0 | 0 | 0      | 0 | 1 | 0 | 0/1  |

| 06/07      | Tri-state SG Register                  | 0 | 0 | 0 | 0      | 0 | 1 | 1 | 0/1  |

| 08/09      | Wetting Current Level SP Register      | 0 | 0 | 0 | 0      | 1 | 0 | 0 | 0/1  |

| 0A/0B      | Wetting Current Level SG Register 0    | 0 | 0 | 0 | 0      | 1 | 0 | 1 | 0/1  |

| 0C/0D      | Wetting Current Level SG Register 1    | 0 | 0 | 0 | 0      | 1 | 1 | 0 | 0/1  |

| 16/17      | Continuous Wetting Current SP Register | 0 | 0 | 0 | 1      | 0 | 1 | 1 | 0/1  |

| 18/19      | Continuous Wetting Current SG Register | 0 | 0 | 0 | 1      | 1 | 0 | 0 | 0/1  |

| 1A/1B      | Interrupt Enable SP Register           | 0 | 0 | 0 | 1      | 1 | 0 | 1 | 0/1  |

| 1C/1D      | Interrupt Enable SG Register           | 0 | 0 | 0 | 1      | 1 | 1 | 0 | 0/1  |

| 1E/1F      | Low-power Mode Configuration           | 0 | 0 | 0 | 1      | 1 | 1 | 1 | 0/1  |

| 20/21      | Wake-up Enable Register SP             | 0 | 0 | 1 | 0      | 0 | 0 | 0 | 0/1  |

| 22/23      | Wake-up Enable Register SG             | 0 | 0 | 1 | 0      | 0 | 0 | 1 | 0/1  |

| 24/25      | Comparator Only SP                     | 0 | 0 | 1 | 0      | 0 | 1 | 0 | 0/1  |