#### **ABSOLUTE MAXIMUM RATINGS**

| (All voltages referenced to GND.) |                                  | CRESET0.3V to (V <sub>CC</sub> + 0.3V)           |

|-----------------------------------|----------------------------------|--------------------------------------------------|

| V <sub>C</sub> C                  | 0.3V to +30V                     | Input/Output Current (all pins)±20mA             |

| EN1-EN4                           |                                  | Continuous Power Dissipation ( $T_A = +70$ °C)   |

| OUT1-OUT4 (push-pull)             | 0.3V to (V <sub>CC</sub> + 0.3V) | 16-Pin TQFN (derate 25mW/°C above +70°C)2000mW   |

| OUT1-OUT4 (open-drain)            | 0.3V to +30V                     | 20-Pin TQFN (derate 25.6mW/°C above +70°C)2051mW |

| RESET (push-pull)                 | 0.3V to (V <sub>CC</sub> + 0.3V) | 24-Pin TQFN (derate 27.8mW/°C above +70°C)2222mW |

| RESET (open-drain)                | 0.3V to 30V                      | Operating Temperature Range40°C to +125°C        |

| IN1–IN4                           | 0.3V to (V <sub>CC</sub> + 0.3V) | Storage Temperature Range65°C to +150°C          |

| MR, TOL, TH1, TH0                 | 0.3V to (V <sub>CC</sub> + 0.3V) | Junction Temperature+150°C                       |

| CDLY1-CDLY4                       |                                  | Lead Temperature (soldering, 10s) +300°C         |

g, 10s).....+300°C Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 2.2V \text{ to } 28V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise specified.}$  Typical values are at  $V_{CC} = 3.3V \text{ and } T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                       | SYMBOL               | CONDITI                     | MIN                      | TYP   | MAX   | UNITS |    |

|---------------------------------|----------------------|-----------------------------|--------------------------|-------|-------|-------|----|

| SUPPLY                          | •                    |                             |                          | •     |       |       |    |

| Operating Voltage Range         | Vcc                  | (Note 2)                    | 2.2                      |       | 28.0  | V     |    |

| Undervoltage Lockout            | UVLO                 | (Note 2)                    |                          | 1.8   | 1.9   | 2.0   | V  |

| Undervoltage-Lockout Hysteresis | UVLO <sub>HYST</sub> | V <sub>CC</sub> falling     |                          | 50    |       | mV    |    |

|                                 |                      | All OUT_ and RESET at       | $V_{CC} = 3.3V$          |       | 40    | 75    |    |

| V <sub>CC</sub> Supply Current  | Icc                  | logic-high (IN_ current     | V <sub>CC</sub> = 12V    |       | 47    | 75    | μΑ |

|                                 |                      | excluded)                   | V <sub>CC</sub> = 28V    |       | 52    | 80    | 1  |

| INPUTS (IN_)                    |                      |                             |                          |       |       |       |    |

|                                 | Vтн                  | 3.3V threshold, TOL = G     | 2.970                    | 3.052 | 3.135 | V     |    |

|                                 |                      | 3.3V threshold, TOL = V(    | 2.805                    | 2.888 | 2.970 |       |    |

|                                 |                      | 2.5V threshold, TOL = G     | 2.250                    | 2.313 | 2.375 |       |    |

|                                 |                      | 2.5V threshold, TOL = V(    | 2.125                    | 2.187 | 2.250 |       |    |

| INI Thursday (INI Fallings)     |                      | 1.8V threshold, TOL = G     | 1.620                    | 1.665 | 1.710 |       |    |

| IN_ Thresholds (IN_ Falling)    |                      | 1.8V threshold, TOL = Vo    | 1.530                    | 1.575 | 1.620 |       |    |

|                                 |                      | 1.5V threshold, TOL = G     | 1.350                    | 1.387 | 1.425 |       |    |

|                                 |                      | 1.5V threshold, $TOL = V_0$ | 1.275                    | 1.312 | 1.350 |       |    |

|                                 |                      | 1.2V threshold, TOL = G     | 1.080                    | 1.110 | 1.140 |       |    |

|                                 |                      | 1.2V threshold, TOL = Vo    | 1.020                    | 1.050 | 1.080 |       |    |

| Adjustable Threshold (IN_       |                      | TOL = GND                   | 0.492                    | 0.5   | 0.508 | .,    |    |

| Falling)                        | V <sub>TH</sub>      | TOL = V <sub>CC</sub>       | 0.463                    | 0.472 | 0.481 | V     |    |

| IN_ Hysteresis (IN_ Rising)     | V <sub>H</sub> YST   |                             |                          |       | 0.5   |       | %  |

| IN_ Input Resistance            |                      | Fixed threshold             |                          | 500   | 918   |       | kΩ |

| IN_ Input Current               | ΙL                   | Adjustable threshold only   | y (V <sub>IN</sub> = 1V) | -100  |       | +100  | nA |

MIXIM

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = 2.2V \text{ to } 28V, T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise specified.}$  Typical values are at  $V_{CC} = 3.3V \text{ and } T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                                    | SYMBOL                | CONDITIONS                                                                      | MIN                    | TYP   | MAX   | UNITS |

|----------------------------------------------|-----------------------|---------------------------------------------------------------------------------|------------------------|-------|-------|-------|

| CRESET AND CDLY_                             | •                     |                                                                                 | •                      |       |       | •     |

| CRESET Threshold                             | V <sub>TH-RESET</sub> | CRESET rising, V <sub>CC</sub> = 3.3V                                           | 0.465                  | 0.5   | 0.535 | V     |

| CRESET Charge Current                        | I <sub>CH-RESET</sub> | V <sub>CC</sub> = 3.3V                                                          | 380                    | 500   | 620   | nA    |

| CDLY_ Threshold                              | V <sub>TH-CDLY</sub>  | CDLY_ rising, V <sub>CC</sub> = 3.3V                                            | 0.95                   | 1     | 1.05  | V     |

| CDLY_ Charge Current                         | ICH-CDLY              | V <sub>CC</sub> = 3.3V                                                          | 200                    | 250   | 300   | nA    |

| DIGITAL LOGIC INPUTS (EN_, M                 | R, TOL, TH1,          | TH0)                                                                            |                        |       |       |       |

| Input Low Voltage                            | V <sub>I</sub> L      |                                                                                 |                        |       | 0.4   | V     |

| Input High Voltage                           | VIH                   |                                                                                 | 1.4                    |       |       | V     |

| TH1, TH0 Logic-Input Floating                |                       |                                                                                 |                        | 0.6   |       | V     |

| TOL, TH1, TH0 Logic-Input<br>Current         |                       | V <sub>TOL</sub> , V <sub>TH1</sub> , V <sub>TH0</sub> = GND or V <sub>CC</sub> | -1                     |       | +1    | μΑ    |

| EN_ Input Leakage Current                    |                       | V <sub>EN</sub> _ = V <sub>CC</sub> or GND                                      | -100                   |       | +100  | nA    |

| MR Internal Pullup Current                   |                       | V <sub>CC</sub> = 3.3V                                                          | 250                    | 535   | 820   | nA    |

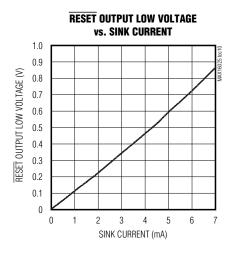

| OUTPUTS (OUT_, RESET)                        |                       |                                                                                 |                        |       |       |       |

|                                              |                       | V <sub>CC</sub> ≥ 1.2V, I <sub>SINK</sub> = 90µA                                |                        |       | 0.3   |       |

| Output Low Voltage (Open-Drain or Push-Pull) | V <sub>OL</sub>       | V <sub>CC</sub> ≥ 2.25V, I <sub>SINK</sub> = 0.5mA                              |                        |       | 0.3   | V     |

| or Push-Pull)                                |                       | V <sub>CC</sub> ≥ 4.5V, I <sub>SINK</sub> = 1mA                                 | 0.35                   |       |       |       |

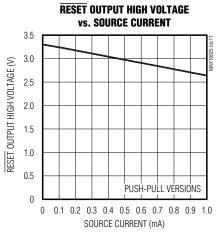

| Outrout High Voltage (Duch Dull)             | V                     | VCC ≥ 3V, ISOURCE = 500µA                                                       | 0.8 x V <sub>C</sub> ( | )     |       | V     |

| Output High Voltage (Push-Pull)              | VoH                   | V <sub>CC</sub> ≥ 4.5V, I <sub>SOURCE</sub> = 800µA                             | 0.8 x V <sub>C</sub> ( | )     |       | V     |

| Output Leakage Current (Open-<br>Drain)      | I <sub>LKG</sub>      | Output not asserted low, V <sub>OUT</sub> = 28V                                 |                        |       | 1     | μΑ    |

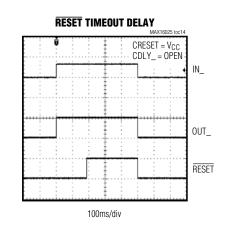

| D 17 10 11                                   |                       | CRESET = V <sub>CC</sub> , V <sub>CC</sub> = 3.3V                               | 140                    | 190   | 260   |       |

| Reset Timeout Period                         | t <sub>RP</sub>       | CRESET open                                                                     |                        | 0.030 |       | ms    |

| TIMING                                       |                       |                                                                                 |                        |       |       |       |

| IN to OUT Propagation Delay                  | tDELAY+               | IN_ rising, CDLY_ open                                                          |                        | 35    |       |       |

| IN_ to OUT_ Propagation Delay                | t <sub>DELAY</sub> -  | IN_ falling, CDLY_ open                                                         |                        | 20    |       | μs    |

| IN_ to RESET Propagation Delay               | trst-delay            | IN_ falling                                                                     |                        | 35    |       | μs    |

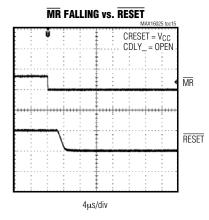

| MR Minimum Input Pulse Width                 |                       | (Note 3)                                                                        | 2                      |       |       | μs    |

| EN_ or MR Glitch Rejection                   |                       |                                                                                 |                        | 280   |       | ns    |

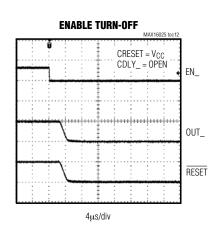

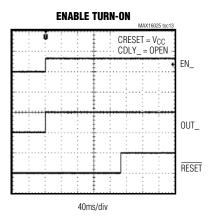

|                                              | toff                  | From device enabled to device disabled                                          | 3                      |       |       |       |

| EN_ to OUT_ Delay                            | ton                   | From device disabled to device enabled (CDLY_ open) 30                          |                        |       | μs    |       |

| MR to RESET Delay                            |                       | MR falling                                                                      |                        | 3     |       | μs    |

Note 1: Devices are production tested at  $T_A = +25$ °C. Limits over temperature are guaranteed by design.

Note 2: Operating below the UVLO causes all outputs to go low. The outputs are guaranteed to be in the correct state for V<sub>CC</sub> down to 1.2V.

Note 3: In order to guarantee an assertion, the minimum input pulse width must be greater than 2 us.

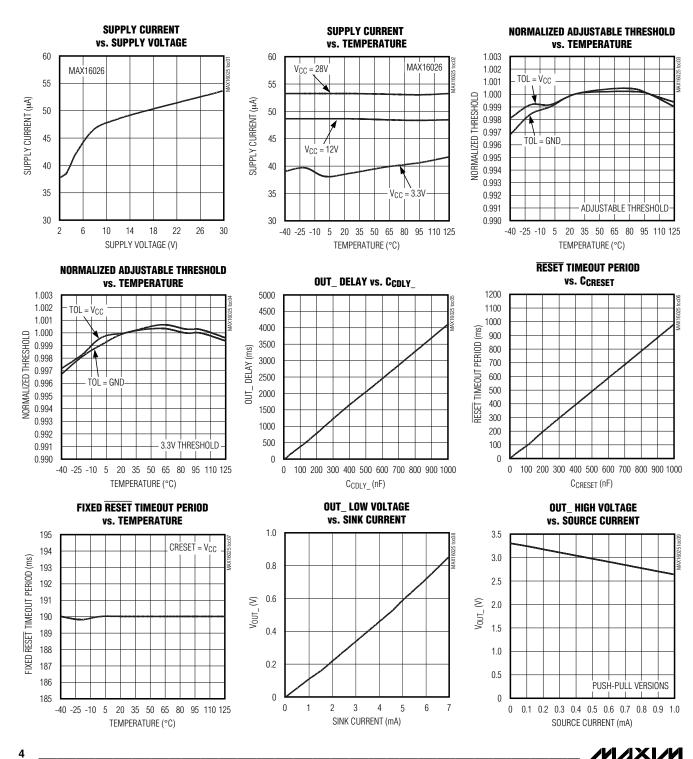

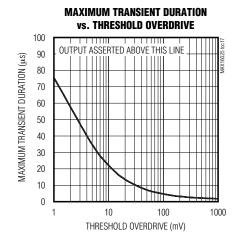

Typical Operating Characteristics

$(V_{CC} = 3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

## Typical Operating Characteristics (continued)

( $V_{CC} = 3.3V$ ,  $T_A = +25$ °C, unless otherwise noted.)

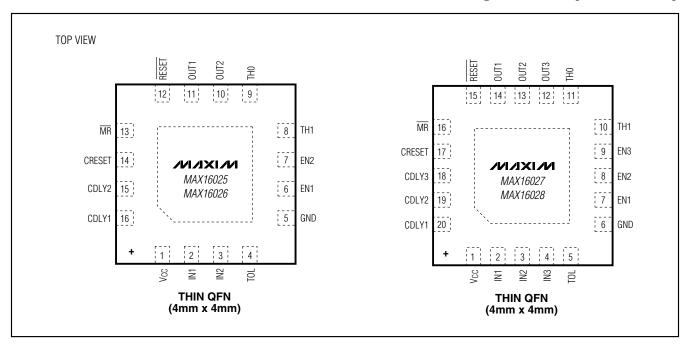

## **Pin Description**

| PIN                   |                       |                       |      |                                                                                                                                                                                                                           |  |  |  |  |

|-----------------------|-----------------------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| MAX16025/<br>MAX16026 | MAX16027/<br>MAX16028 | MAX16029/<br>MAX16030 | NAME | FUNCTION                                                                                                                                                                                                                  |  |  |  |  |

| 1                     | 1                     | 1                     | VCC  | Supply Voltage Input. Connect a 2.2V to 28V supply voltage to power the device. All outputs are low when V <sub>CC</sub> is below the UVLO. For noisy systems, bypass V <sub>CC</sub> to GND with a 0.1µF capacitor.      |  |  |  |  |

| 2                     | 2                     | 2                     | IN1  | Monitored Input 1. When the voltage at IN1 exceeds its threshold, OUT1 goes high after the capacitor-adjustable delay period. When the voltage at IN1 falls below its threshold, OUT1 goes low after a propagation delay. |  |  |  |  |

| 3                     | 3                     | 3                     | IN2  | Monitored Input 2. When the voltage at IN2 exceeds its threshold, OUT2 goes high after the capacitor-adjustable delay period. When the voltage at IN2 falls below its threshold, OUT2 goes low after a propagation delay. |  |  |  |  |

| _                     | 4                     | 4                     | IN3  | Monitored Input 3. When the voltage at IN3 exceeds its threshold, OUT3 goes high after the capacitor-adjustable delay period. When the voltage at IN3 falls below its threshold, OUT3 goes low after a propagation delay. |  |  |  |  |

| _                     | _                     | 5                     | IN4  | Monitored Input 4. When the voltage at IN4 exceeds its threshold, OUT4 goes high after the capacitor-adjustable delay period. When the voltage at IN4 falls below its threshold, OUT4 goes low after a propagation delay. |  |  |  |  |

| 4                     | 5                     | 6                     | TOL  | Threshold Tolerance Input. Connect TOL to GND to select thresholds 5% below nominal. Connect TOL to $V_{\rm CC}$ to select thresholds 10% below nominal.                                                                  |  |  |  |  |

| 5                     | 6                     | 7                     | GND  | Ground                                                                                                                                                                                                                    |  |  |  |  |

| 6                     | 7                     | 8                     | EN1  | Active-High Logic-Enable Input 1. Driving EN1 low causes OUT1 to go low regardless of the input voltage. Drive EN1 high to enable the monitoring comparator.                                                              |  |  |  |  |

| 7                     | 8                     | 9                     | EN2  | Active-High Logic-Enable Input 2. Driving EN2 low causes OUT2 to go low regardless of the input voltage. Drive EN2 high to enable the monitoring comparator.                                                              |  |  |  |  |

| _                     | 9                     | 10                    | EN3  | Active-High Logic-Enable Input 3. Driving EN3 low causes OUT3 to go low regardless of the input voltage. Drive EN3 high to enable the monitoring comparator.                                                              |  |  |  |  |

| _                     | _                     | 11                    | EN4  | Active-High Logic-Enable Input 4. Driving EN4 low causes OUT4 to go low regardless of the input voltage. Drive EN4 high to enable the monitoring comparator.                                                              |  |  |  |  |

| 8                     | 10                    | 12                    | TH1  | Threshold Select Input 1. Connect TH1 to V <sub>CC</sub> or GND, or leave it open to select the input-voltage threshold option in conjunction with TH0 (see Table 2).                                                     |  |  |  |  |

| 9                     | 11                    | 13                    | TH0  | Threshold Select Input 0. Connect TH0 to V <sub>CC</sub> or GND, or leave it open to select the input-voltage threshold option in conjunction with TH1 (see Table 2).                                                     |  |  |  |  |

| _                     | _                     | 14                    | OUT4 | Output 4. When the voltage at IN4 is below its threshold or EN4 goes low, OUT4 goes low.                                                                                                                                  |  |  |  |  |

| _                     | 12                    | 15                    | OUT3 | Output 3. When the voltage at IN3 is below its threshold or EN3 goes low, OUT3 goes low.                                                                                                                                  |  |  |  |  |

| 10                    | 13                    | 16                    | OUT2 | Output 2. When the voltage at IN2 is below its threshold or EN2 goes low, OUT2 goes low.                                                                                                                                  |  |  |  |  |

6 \_\_\_\_\_\_ M/XI/M

## **Pin Description (continued)**

|                       | PIN                   |                       |        |                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------|-----------------------|-----------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX16025/<br>MAX16026 | MAX16027/<br>MAX16028 | MAX16029/<br>MAX16030 | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                             |

| 11                    | 14                    | 17                    | OUT1   | Output 1. When the voltage at IN1 is below its threshold or EN1 goes low, OUT1 goes low.                                                                                                                                                                                                                                                             |

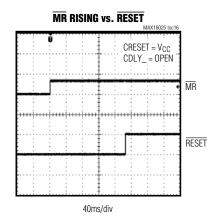

| 12                    | 15                    | 18                    | RESET  | Active-Low Reset Output. RESET asserts low when any of the monitored voltages (IN_) falls below its respective threshold, any EN_ goes low, or MR is asserted. RESET remains asserted for the reset timeout period after all of the monitored voltages exceed their respective threshold, all EN_ are high, all OUT_ are high, and MR is deasserted. |

| 13                    | 16                    | 19                    | MR     | Active-Low Manual Reset Input. Pull $\overline{\text{MR}}$ low to assert $\overline{\text{RESET}}$ low. $\overline{\text{RESET}}$ remains low for the reset timeout period after $\overline{\text{MR}}$ is deasserted (as long as all OUT_ are high).                                                                                                |

| 14                    | 17                    | 20                    | CRESET | Capacitor-Adjustable Reset Delay Input. Connect an external capacitor from CRESET to GND to set the reset timeout period or connect to V <sub>CC</sub> for the default 140ms minimum reset timeout period. Leave CRESET open for internal propagation delay.                                                                                         |

| _                     | _                     | 21                    | CDLY4  | Capacitor-Adjustable Delay Input 4. Connect an external capacitor from CDLY4 to GND to set the IN4 to OUT4 (and EN4 to OUT4) delay period. Leave CDLY4 open for internal propagation delay.                                                                                                                                                          |

| _                     | 18                    | 22                    | CDLY3  | Capacitor-Adjustable Delay Input 3. Connect an external capacitor from CDLY3 to GND to set the IN3 to OUT3 (and EN3 to OUT3) delay period. Leave CDLY3 open for internal propagation delay.                                                                                                                                                          |

| 15                    | 19                    | 23                    | CDLY2  | Capacitor-Adjustable Delay Input 2. Connect an external capacitor from CDLY2 to GND to set the IN2 to OUT2 (and EN2 to OUT2) delay period. Leave CDLY2 open for internal propagation delay.                                                                                                                                                          |

| 16                    | 20                    | 24                    | CDLY1  | Capacitor-Adjustable Delay Input 1. Connect an external capacitor from CDLY1 to GND to set the IN1 to OUT1 (and EN1 to OUT1) delay period. Leave CDLY1 open for internal propagation delay.                                                                                                                                                          |

| _                     | _                     | _                     | EP     | Exposed Pad. EP is internally connected to GND. Connect EP to the ground plane.                                                                                                                                                                                                                                                                      |

### Table 1. Output State\*

| EN_   | IN_                                 | OUT_                                                      |  |  |

|-------|-------------------------------------|-----------------------------------------------------------|--|--|

| Low   | $V_{IN} < V_{TH}$                   | Low                                                       |  |  |

| High  | V <sub>IN_</sub> < V <sub>TH</sub>  | Low                                                       |  |  |

| Low   | $V_{IN} > V_{TH}$                   | Low                                                       |  |  |

| Lliab | Vive > V <del>iv</del> e            | OUT_ = high<br>(MAX16026/MAX16028/<br>MAX16030)           |  |  |

| High  | V <sub>IN</sub> _ > V <sub>TH</sub> | OUT_ = high impedance<br>(MAX16025/MAX16027/<br>MAX16029) |  |  |

<sup>\*</sup>When  $V_{CC}$  falls below the UVLO, all outputs go low regardless of the state of EN\_ and  $V_{IN}$ . The outputs are guaranteed to be in the correct state for  $V_{CC}$  down to 1.2V.

## **Table 2. Input-Voltage Threshold Selector**

| TH1/TH0<br>LOGIC | IN1 (ALL<br>VERSIONS)<br>(V) | IN2 (ALL<br>VERSIONS)<br>(V) | IN3<br>(MAX16027/<br>MAX16028)<br>(V) | IN4<br>(MAX16029/<br>MAX16030)<br>(V) |

|------------------|------------------------------|------------------------------|---------------------------------------|---------------------------------------|

| Low/Low          | 3.3                          | 2.5                          | 1.8                                   | 1.5                                   |

| Low/High         | 3.3                          | 1.8                          | Adj                                   | Adj                                   |

| Low/Open         | 3.3                          | 1.5                          | Adj                                   | Adj                                   |

| High/Low         | 3.3                          | 1.2                          | 1.8                                   | 2.5                                   |

| High/High        | 2.5                          | 1.8                          | Adj                                   | Adj                                   |

| High/Open        | 3.3                          | Adj                          | 2.5                                   | Adj                                   |

| Open/Low         | 3.3                          | Adj                          | Adj                                   | Adj                                   |

| Open/High        | 2.5                          | Adj                          | Adj                                   | Adj                                   |

| Open/Open        | Adj                          | Adj                          | Adj                                   | Adj                                   |

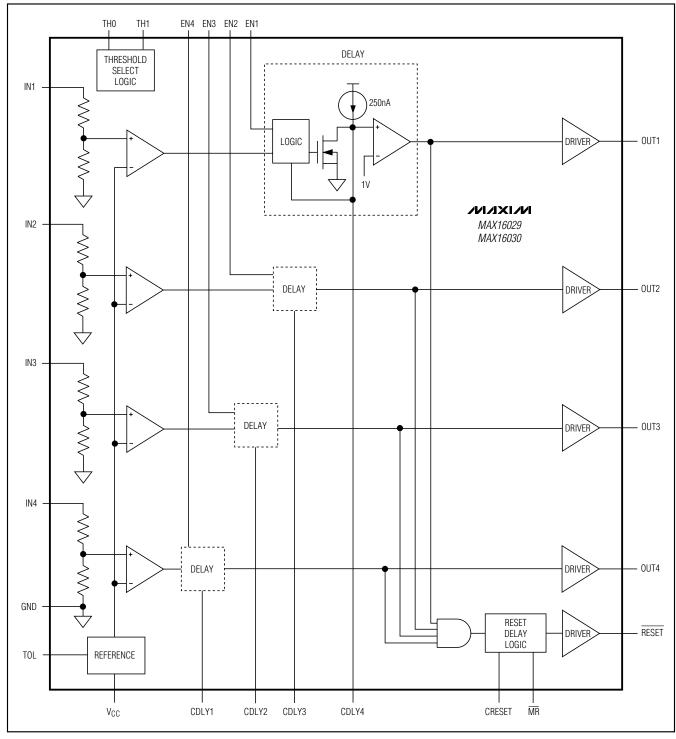

Figure 1. MAX16029/MAX16030 Simplified Functional Diagram

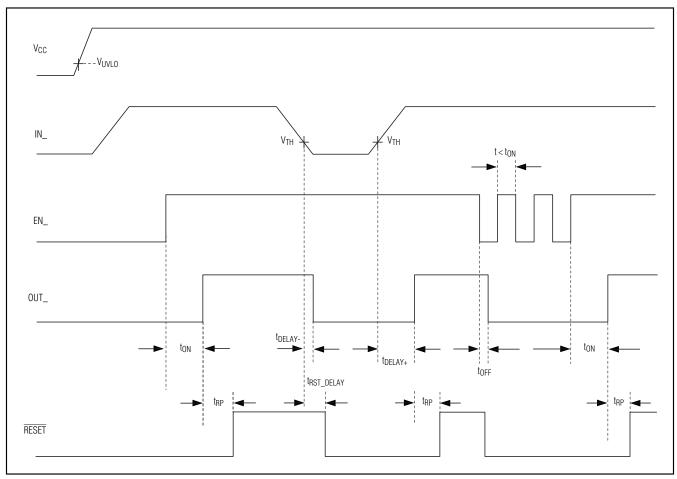

Figure 2. Timing Diagram (CDLY\_ Open)

## **Detailed Description**

The MAX16025–MAX16030 are low-voltage, accurate, dual-/triple-/quad-voltage microprocessor ( $\mu$ P) supervisors in a small TQFN package. These devices provide supervisory and sequencing functions for complex multivoltage systems. The MAX16025/MAX16026 monitor two voltages, the MAX16027/MAX16028 monitor three voltages, and the MAX16029/MAX16030 monitor four voltages.

The MAX16025–MAX16030 offer independent outputs and enable functions for each monitored voltage. This configuration allows the device to operate as four separate supervisory circuits or be daisy-chained together to allow controlled sequencing of power supplies during

power-up initialization. When all of the monitored voltages exceed their respective thresholds, an independent reset output deasserts to allow the system processor to operate.

These devices offer enormous flexibility as there are nine threshold options that are selected through two threshold-select logic inputs. Each monitor circuit also offers an independent enable input to allow both digital and analog control of each monitor output. A tolerance select input allows these devices to be used in systems requiring 5% or 10% power-supply tolerances. In addition, the time delays and reset timeout can be adjusted using small capacitors. There is also a fixed 140ms minimum reset timeout feature.

### **Applications Information**

#### **Tolerance**

The MAX16025–MAX16030 feature a pin-selectable threshold tolerance. Connect TOL to GND to select the thresholds 5% below the nominal value. Connect TOL to  $V_{\rm CC}$  to select the threshold tolerance 10% below the nominal voltage. Do not leave TOL unconnected.

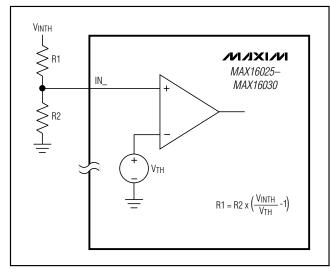

#### Adjustable Input

These devices offer several monitoring options with both fixed and/or adjustable reset thresholds (see Table 2). For the adjustable threshold inputs, the threshold voltage (V<sub>TH</sub>) at each adjustable IN\_ input is typically 0.5V (TOL = GND) or 0.472V (TOL = V<sub>CC</sub>). To monitor a voltage V<sub>INTH</sub>, connect a resistive divider network to the circuit as shown in Figure 3 and use the following equation to calculate the threshold voltage:

$$V_{INTH} = V_{TH} \times \left(1 + \frac{R1}{R2}\right)$$

Choosing the proper external resistors is a balance between accuracy and power use. The input to the voltage monitor is a high-impedance input with a small 100nA leakage current. This leakage current contributes to the overall error of the threshold voltage where the output is asserted. This induced error is proportional to the value of the resistors used to set the threshold. With lower value resistors, this error is reduced, but the amount of power consumed in the resistors increases.

Figure 3. Setting the Adjustable Input

The following equation is provided to help estimate the value of the resistors based on the amount of acceptable error:

$$R_1 = \frac{e_A \times V_{INTH}}{I_I}$$

where eA is the fraction of the maximum acceptable absolute resistive divider error attributable to the input leakage current (use 0.01 for  $\pm 1\%$ ), V<sub>INTH</sub> is the voltage at which the output (OUT\_) should assert, and I<sub>L</sub> is the worst-case IN\_ leakage current (see the *Electrical Characteristics*). Calculate R2 as follows:

$$R_2 = \frac{V_{TH} \times R1}{V_{INTH} - V_{TH}}$$

#### **Unused Inputs**

Connect any unused IN\_ and EN\_ inputs to VCC.

#### **OUT\_ Output**

An OUT\_ goes low when its respective IN\_ input voltage drops below its specified threshold or when its EN\_ goes low (see Table 1). OUT\_ goes high when EN\_ is high and VIN\_ is above its threshold after a time delay. The MAX16025/MAX16027/MAX16029 feature open-drain, outputs while the MAX16026/MAX16028/MAX16030 have push-pull outputs. Open-drain outputs require an external pullup resistor to any voltage from 0 to 28V.

#### **RESET Output**

RESET asserts low when any of the monitored voltages (IN\_) falls below its respective threshold, any EN\_ goes low, or MR is asserted. RESET remains asserted for the reset timeout period after all of the monitored voltages exceed their respective threshold, all EN\_ are high, all OUT\_ are high, and MR is deasserted. The MAX16025/MAX16027/MAX16029 have an open-drain, active-low reset output, while the MAX16026/MAX16028/MAX16030 have a push-pull, active-low reset output. Open-drain RESET requires an external pullup resistor to any voltage from 0 to 28V.

# Adjustable Reset Timeout Period (CRESET)

All of these parts offer an internally fixed reset timeout (140ms min) by connecting CRESET to V<sub>CC</sub>. The reset timeout can also be adjusted by connecting a capacitor from CRESET to GND. When the voltage at CRESET reaches 0.5V, RESET goes high. When RESET goes high, CRESET is immediately held low.

Calculate the reset timeout period as follows:

$$t_{RP} = \frac{V_{TH-RESET}}{I_{CH-RESET}} \times C_{CRESET} + 35 \times 10^{-6}$$

where V<sub>TH-RESET</sub> is 0.5V, I<sub>CH-RESET</sub> is 0.5 $\mu$ A, t<sub>RP</sub> is in seconds, and C<sub>CRESET</sub> is in Farads. To ensure timing accuracy and proper operation, minimize leakage at C<sub>CRESET</sub>.

#### Adjustable Delay (CDLY\_)

When  $V_{IN}$  rises above  $V_{TH}$  with EN\_ high, the internal 250nA current source begins charging an external capacitor connected from CDLY\_ to GND. When the voltage at CDLY\_ reaches 1V, OUT\_ goes high. When OUT\_ goes high, CDLY\_ is immediately held low. Adjust the delay (tDELAY) from when  $V_{IN}$  rises above  $V_{TH}$  (with EN\_ high) to OUT\_ going high according to the equation:

$$t_{DELAY} = \frac{V_{TH-CDLY}}{I_{CH-CDLY}} \times C_{CDLY} + 35 \times 10^{-6}$$

where V<sub>TH-CDLY</sub> is 1V, I<sub>CH-CDLY</sub> is 0.25 $\mu$ A, C<sub>CDLY</sub> is in Farads, t<sub>DELAY</sub> is in seconds, and t<sub>DELAY+</sub> is the internal propagation delay of the device. To ensure timing accuracy and proper operation, minimize leakage at CDLY.

#### Manual-Reset Input (MR)

Many  $\mu P$ -based products require manual-reset capability, allowing the operator, a test technician, or external logic circuitry to initiate a reset. A logic-low on  $\overline{MR}$  asserts  $\overline{RESET}$  low.  $\overline{RESET}$  remains asserted while  $\overline{MR}$  is low and during the reset timeout period (140ms fixed or capacitor adjustable) after  $\overline{MR}$  returns high. The  $\overline{MR}$  input has a 500nA internal pullup, so it can be left unconnected, if not used.  $\overline{MR}$  can be driven with TTL or CMOS logic levels, or with open-drain/collector outputs. Connect a normally open momentary switch from  $\overline{MR}$  to GND to create a manual-reset function. External

debounce circuitry is not required. If  $\overline{\text{MR}}$  is driven from long cables or if the device is used in a noisy environment, connect a  $0.1\mu\text{F}$  capacitor from  $\overline{\text{MR}}$  to GND to provide additional noise immunity.

#### **Pullup Resistor Values**

The exact value of the pullup resistors for the opendrain outputs is not critical, but some consideration should be made to ensure the proper logic levels when the device is sinking current. For example, if  $V_{CC} = 2.25V$  and the pullup voltage is 28V, keep the sink current less than 0.5mA as shown in the *Electrical Characteristics* table. As a result, the pullup resistor should be greater than  $56k\Omega$ . For a 12V pullup, the resistor should be larger than  $24k\Omega$ . Note that the ability to sink current is dependent on the  $V_{CC}$  supply voltage.

#### **Power-Supply Bypassing**

The device operates with a VCC supply voltage from 2.2V to 28V. When VCC falls below the UVLO threshold, all the outputs go low and stay low until VCC falls below 1.2V. For noisy systems or fast rising transients on VCC, connect a  $0.1\mu F$  ceramic capacitor from VCC to GND as close to the device as possible to provide better noise and transient immunity.

# Ensuring Valid Output with Vcc Down to OV (MAX16026/MAX16028/MAX16030 Only)

When V<sub>CC</sub> falls below 1.2V, the ability for the output to sink current decreases. In order to ensure a valid output as V<sub>CC</sub> falls to 0V, connect a 100k $\Omega$  resistor from OUT/RESET to GND.

#### **Typical Application Circuits**

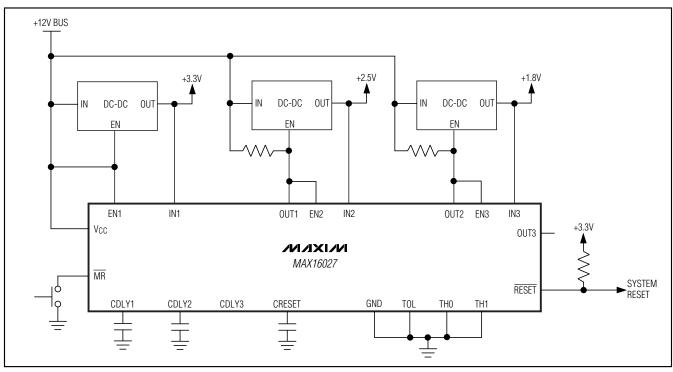

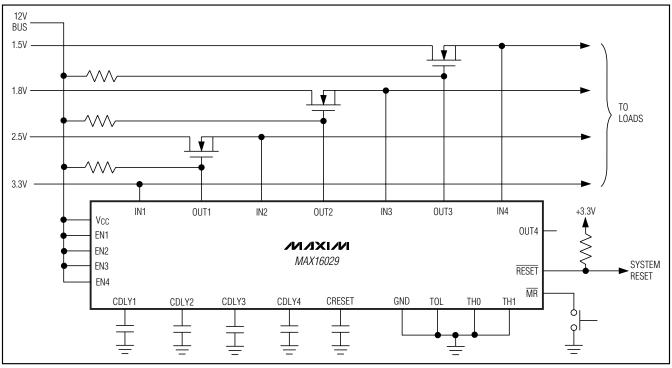

Figures 4 and 5 show typical applications for the MAX16025–MAX16030. In high-power applications, using an n-channel device reduces the loss across the MOSFETs as it offers a lower drain-to-source on-resistance. However, an n-channel MOSFET requires a sufficient VGs voltage to fully enhance it for a low RDS\_ON. The application in Figure 4 shows the MAX16027 configured in a multiple-output sequencing application. Figure 5 shows the MAX16029 in a power-supply sequencing application using n-channel MOSFETs.

Figure 4. Sequencing Multiple-Voltage System

Figure 5. Multiple-Voltage Sequencing Using n-Channel FETs

## Pin Configurations (continued)

\_Chip Information

PROCESS: BICMOS

**TRANSISTOR COUNT: 3642**

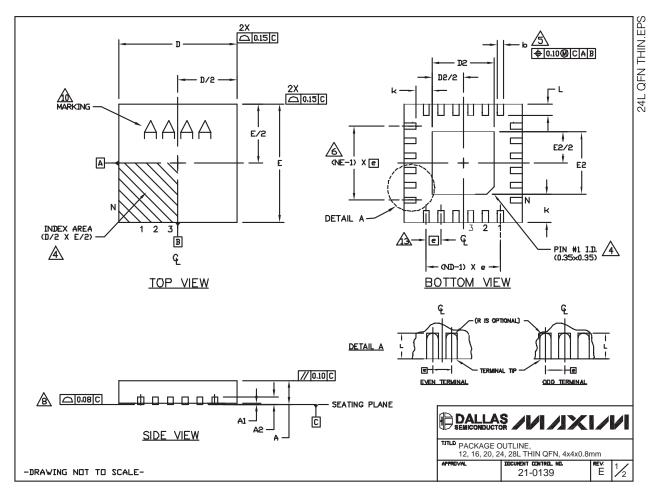

### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

|               | COMMON DIMENSIONS |         |      |      |       |      |           |                   |           |         |           |          |         |      |      |

|---------------|-------------------|---------|------|------|-------|------|-----------|-------------------|-----------|---------|-----------|----------|---------|------|------|

| PKG           | 12                | 2L 4x   | 4    | 16   | L 4x  | 4    | 20L 4×4   |                   |           | 24L 4×4 |           |          | 28L 4x4 |      |      |

| REF.          | MIN.              | NDM.    | MAX. | MIN. | NDM.  | MAX. | MIN.      | NDM.              | MAX.      | MIN.    | NDM.      | MAX.     | MIN.    | NDM. | MAX. |

| Α             | 0.70              | 0.75    | 0.80 | 0.70 | 0.75  | 0.80 | 0.70      | 0.75              | 0.80      | 0.70    | 0.75      | 0.80     | 0.70    | 0.75 | 0.80 |

| A1            | 0.0               | 0.02    | 0.05 | 0.0  | 0.02  | 0.05 | 0.0       | 0.02              | 0.05      | 0.0     | 0.02      | 0.05     | 0.0     | 20.0 | 0.05 |

| A2            | -                 | .20 RE  | F    | 0    | 20 RE | F    | 0         | 0.20 REF 0.20 REF |           |         | F         | 0.20 REF |         |      |      |

| b             | 0.25              | 0.30    | 0.35 | 0.25 | 0.30  | 0.35 | 0.20      | 0.25              | 0.30      | 0.18    | 0.23      | 0.30     | 0.15    | 0.20 | 0.25 |

| D             | 3,90              | 4.00    | 4,10 | 3.90 | 4.00  | 4.10 | 3.90      | 4.00              | 4.10      | 3.90    | 4.00      | 4.10     | 3.90    | 4.00 | 4.10 |

| E             | 3.90              | 4.00    | 4.10 | 3.90 | 4.00  | 4.10 | 3.90      | 4.00              | 4.10      | 3.90    | 4.00      | 4.10     | 3.90    | 4.00 | 4.10 |

| e             |                   | 0.80 BS | C.   | 0.   | 65 BS | C.   | 0.50 BSC. |                   | 0.50 BSC. |         | 0.40 BSC. |          |         |      |      |

| k             | 0.25              | -       | -    | 0.25 | -     | -    | 0.25      | -                 | -         | 0.25    | -         | -        | 0.25    | ı    | -    |

| L             | 0.45              | 0.55    | 0.65 | 0.45 | 0.55  | 0.65 | 0.45      | 0.55              | 0.65      | 0.30    | 0.40      | 0.50     | 0.30    | 0.40 | 0.50 |

| N             |                   | 12      |      |      | 16    |      | 20        |                   | 24        |         | 28        |          |         |      |      |

| NID           |                   | 3       |      |      | 4     |      | 5         |                   | 6         |         | 7         |          |         |      |      |

| NE            |                   | 3       |      |      | 4     |      |           | 5                 |           | 6       |           |          | 7       |      |      |

| Jedec<br>Var. |                   | WGG3    |      |      | WGGC  |      | ١         | wggD-             | 1         |         | WGGD-     | .5       |         | WGGE |      |

| E       | EXPOSED PAD VARIATIONS |      |      |      |      |      |               |  |  |  |

|---------|------------------------|------|------|------|------|------|---------------|--|--|--|

| PKG.    |                        | D2   |      |      | E5   |      | DOWN<br>BONDS |  |  |  |

| CODES   | MIN.                   | NOM. | MAX. | MIN. | NOM. | MAX. | ALLOVED       |  |  |  |

| T1244-3 | 1.95                   | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES           |  |  |  |

| T1244-4 | 1.95                   | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | NO            |  |  |  |

| T1644-3 | 1.95                   | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES           |  |  |  |

| T1644-4 | 1.95                   | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | NO            |  |  |  |

| T2044-2 | 1.95                   | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES           |  |  |  |

| T2044-3 | 1.95                   | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | NO            |  |  |  |

| T2444-2 | 1.95                   | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 | YES           |  |  |  |

| T2444-3 | 2.45                   | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 | YES           |  |  |  |

| T2444-4 | 2.45                   | 2.60 | 2.63 | 2.45 | 2.60 | 2.63 | ND            |  |  |  |

| T2844-1 | 2.50                   | 2.60 | 2.70 | 2.50 | 2.60 | 2.70 | ND            |  |  |  |

#### NOTES:

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

- 2. ALL DIMENSIONS ARE IN MILLINETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- ⚠ THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO

JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN

THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR MARKED FEATURE.

- DIMENSION 6 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm and 0.30 mm from terminal tip.

- ⚠ ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- 7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

- 9. DRAWING CONFORMS TO JEDEC MO220, EXCEPT FOR T2444-3, T2444-4 AND T2844-1.

- MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- 11. COPLANARITY SHALL NOT EXCEED 0.08mm

- 12. WARPAGE SHALL NOT EXCEEND 0.10mm

- LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION "6", ±0.05.

- 14. NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY

TITLE PACKAGE OUTLINE,

12, 16, 20, 24, 28L THIN QFN, 4x4x0.8mm

APPROVAL

21-0139

EV

2/2

-DRAWING NOT TO SCALE-

## Revision History

Pages changed at Rev 1: 1, 3, 15

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

\_ 15

© 2007 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products, Inc.