# EZ-USB *FX*<sup>™</sup> USB Microcontroller

Cypress Semiconductor Corporation Document #: 38-08005 Rev. \*C

٠

٠

San Jose, CA 95134 • 408-943-2600 Revised April 22, 2003

Downloaded from Arrow.com.

## TABLE OF CONTENTS

| 1.0 FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| 1.1 EZ-USB <i>FX</i> Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4                                                                                                  |

| 1.2 Example Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                                                                  |

| 1.3 Other Resources                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6                                                                                                  |

| 2.0 FUNCTIONAL OVERVIEW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                                                                  |

| 2.1 Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                                                  |

| 2.2 USB SIE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6                                                                                                  |

| 2.3 GPIF (General Programmable InterFace)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6                                                                                                  |

| 2.4 Slave FIFOs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 6                                                                                                  |

| 2. <mark>5 D</mark> MA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                    |

| 2.6 Flexible Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                    |

| 2.7 Endpoints                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                    |

| 2.8 Default USB Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                    |

| 2.9 IBN (In-Bulk-NAK) Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

| 3.0 PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                    |

| 3.1 Pin Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                    |

| 3.2 General Notes About the Pin Description Table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                    |

| 3.3 CY7C64613 Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                    |

| 4.0 REGISTER SUMMARY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                    |

| 5.0 INPUT/OUTPUT PIN SPECIAL CONSIDERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 29                                                                                                 |

| 6.0 ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 29                                                                                                 |

| 7.0 OPERATING CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 29                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                    |

| 8.0 DC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 29                                                                                               |

| 8.0 DC CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                    |

| 9.0 AC ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30                                                                                                 |

| 9.0 AC ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | <b>30</b><br>30                                                                                    |

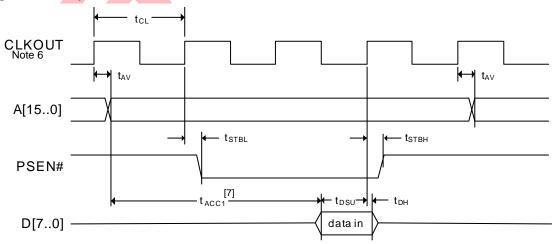

| 9.0 AC ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30<br>30<br>30                                                                                     |

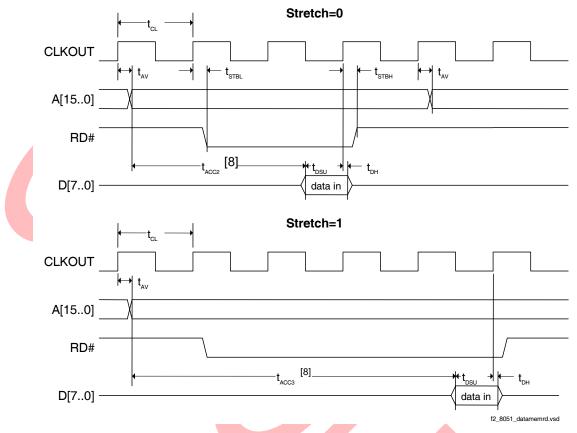

| 9.0 AC ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30<br>30<br>30<br>31                                                                               |

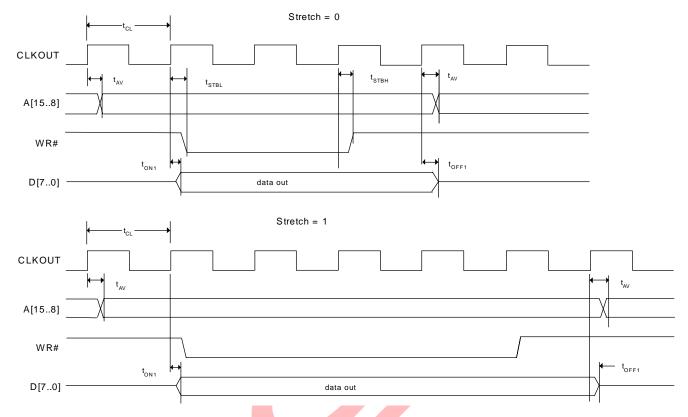

| 9.0 AC ELECTRICAL CHARACTERISTICS<br>9.1 USB Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30<br>30<br>31<br>32<br>33                                                                         |

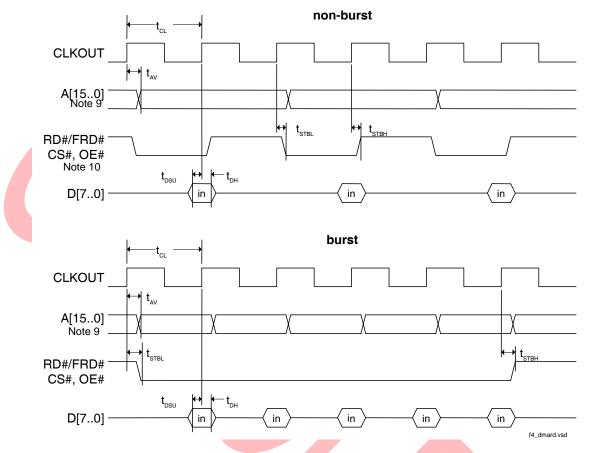

| 9.0 AC ELECTRICAL CHARACTERISTICS         9.1 USB Transceiver         9.2 Program Memory Read         9.3 Data Memory Read         9.4 Data Memory Write         9.5 DMA Read         9.6 DMA Write                                                                                                                                                                                                                                                                                                                                                                                                   | 30<br>30<br>31<br>32<br>33<br>34                                                                   |

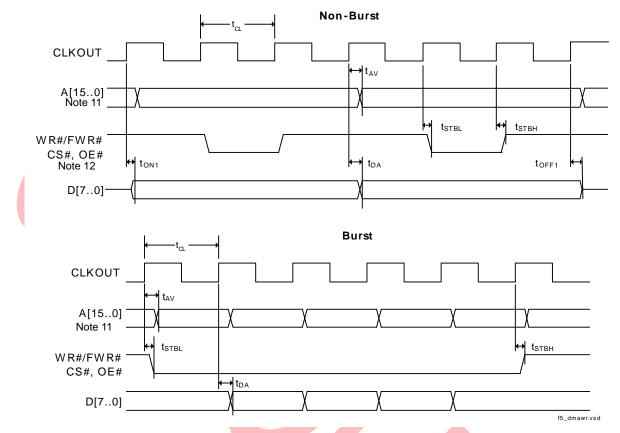

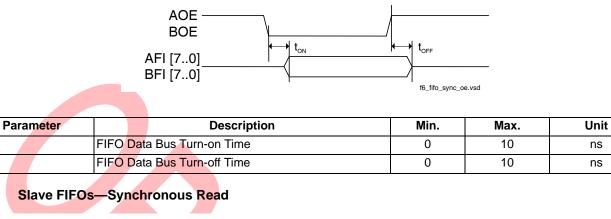

| 9.0 AC ELECTRICAL CHARACTERISTICS         9.1 USB Transceiver         9.2 Program Memory Read         9.3 Data Memory Read         9.4 Data Memory Write         9.5 DMA Read         9.6 DMA Write         9.7 Slave FIFOs—Output Enables                                                                                                                                                                                                                                                                                                                                                            | 30<br>30<br>31<br>32<br>33<br>34<br>35                                                             |

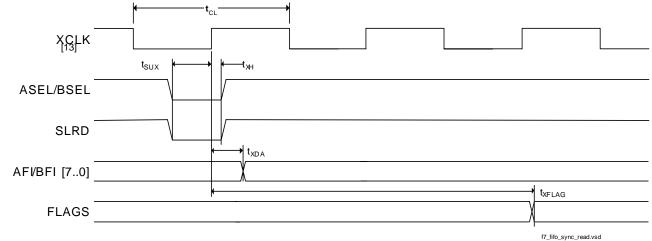

| 9.0 AC ELECTRICAL CHARACTERISTICS<br>9.1 USB Transceiver<br>9.2 Program Memory Read<br>9.3 Data Memory Read<br>9.4 Data Memory Write<br>9.5 DMA Read<br>9.6 DMA Write<br>9.7 Slave FIFOs—Output Enables<br>9.8 Slave FIFOs—Synchronous Read                                                                                                                                                                                                                                                                                                                                                           | 30<br>30<br>31<br>32<br>33<br>34<br>35<br>35                                                       |

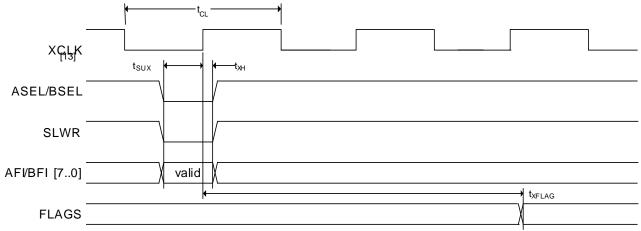

| 9.0 AC ELECTRICAL CHARACTERISTICS<br>9.1 USB Transceiver<br>9.2 Program Memory Read<br>9.3 Data Memory Read<br>9.4 Data Memory Write<br>9.5 DMA Read<br>9.6 DMA Write<br>9.7 Slave FIFOs—Output Enables<br>9.8 Slave FIFOs—Synchronous Read<br>9.9 Slave FIFOs—Synchronous Write                                                                                                                                                                                                                                                                                                                      | 30<br>30<br>31<br>32<br>33<br>34<br>35<br>35<br>36                                                 |

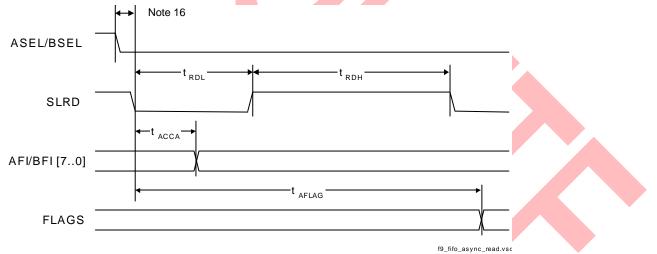

| 9.0 AC ELECTRICAL CHARACTERISTICS<br>9.1 USB Transceiver<br>9.2 Program Memory Read<br>9.3 Data Memory Read<br>9.4 Data Memory Write<br>9.5 DMA Read<br>9.6 DMA Write<br>9.7 Slave FIFOs—Output Enables<br>9.8 Slave FIFOs—Synchronous Read<br>9.9 Slave FIFOs—Synchronous Write<br>9.10 Slave FIFOs—Asynchronous Read                                                                                                                                                                                                                                                                                | 30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>36                                                 |

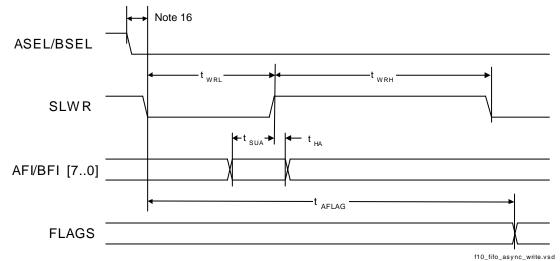

| 9.0 AC ELECTRICAL CHARACTERISTICS<br>9.1 USB Transceiver<br>9.2 Program Memory Read<br>9.3 Data Memory Read<br>9.4 Data Memory Write<br>9.5 DMA Read<br>9.6 DMA Write<br>9.7 Slave FIFOs—Output Enables<br>9.8 Slave FIFOs—Output Enables<br>9.9 Slave FIFOs—Synchronous Read<br>9.9 Slave FIFOs—Synchronous Write<br>9.10 Slave FIFOs—Asynchronous Read<br>9.11 Slave FIFOs—Asynchronous Write                                                                                                                                                                                                       | 30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>36<br>37                                           |

| 9.0 AC ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>36<br>37<br>37                                     |

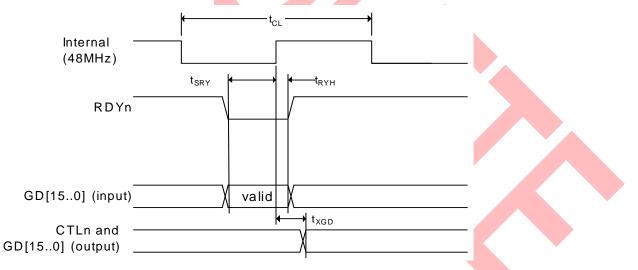

| 9.0 AC ELECTRICAL CHARACTERISTICS<br>9.1 USB Transceiver<br>9.2 Program Memory Read<br>9.3 Data Memory Read<br>9.4 Data Memory Write<br>9.5 DMA Read<br>9.6 DMA Write<br>9.7 Slave FIFOs—Output Enables<br>9.8 Slave FIFOs—Output Enables<br>9.8 Slave FIFOs—Synchronous Read<br>9.9 Slave FIFOs—Synchronous Write<br>9.10 Slave FIFOs—Asynchronous Write<br>9.11 Slave FIFOs—Asynchronous Write<br>9.12 GPIF – Clocked with Fixed 48-MHz Internal Clock<br>9.13 GPIF Signals Externally Clocked – XCLK                                                                                               | 30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>36<br>37<br>37<br>38                               |

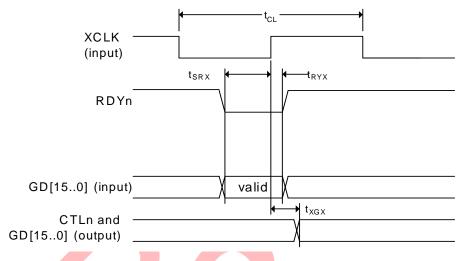

| 9.0 AC ELECTRICAL CHARACTERISTICS         9.1 USB Transceiver         9.2 Program Memory Read         9.3 Data Memory Read         9.4 Data Memory Write         9.5 DMA Read         9.6 DMA Write         9.7 Slave FIFOs—Output Enables         9.8 Slave FIFOs—Synchronous Read         9.9 Slave FIFOs—Synchronous Write         9.10 Slave FIFOs—Asynchronous Read         9.11 Slave FIFOs—Asynchronous Write         9.12 GPIF – Clocked with Fixed 48-MHz Internal Clock         9.13 GPIF Signals Externally Clocked – XCLK                                                                 | 30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>36<br>37<br>38<br>38<br>38                         |

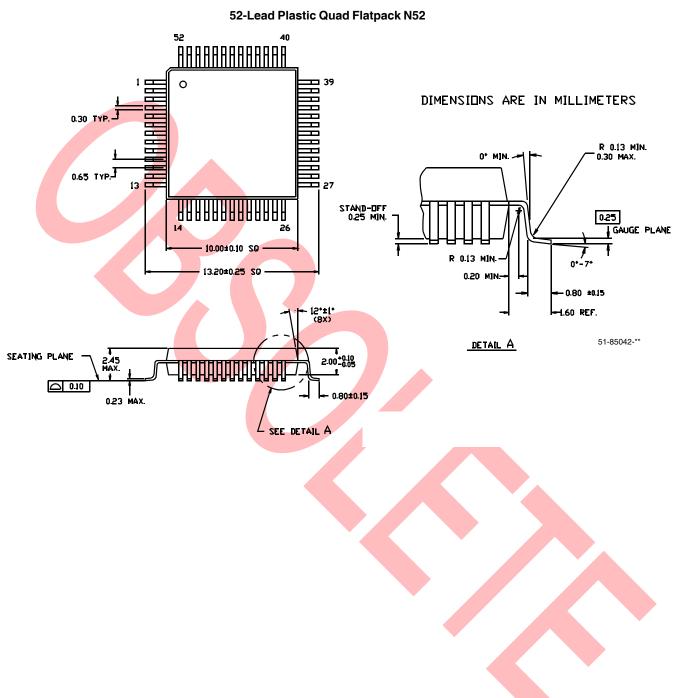

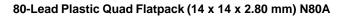

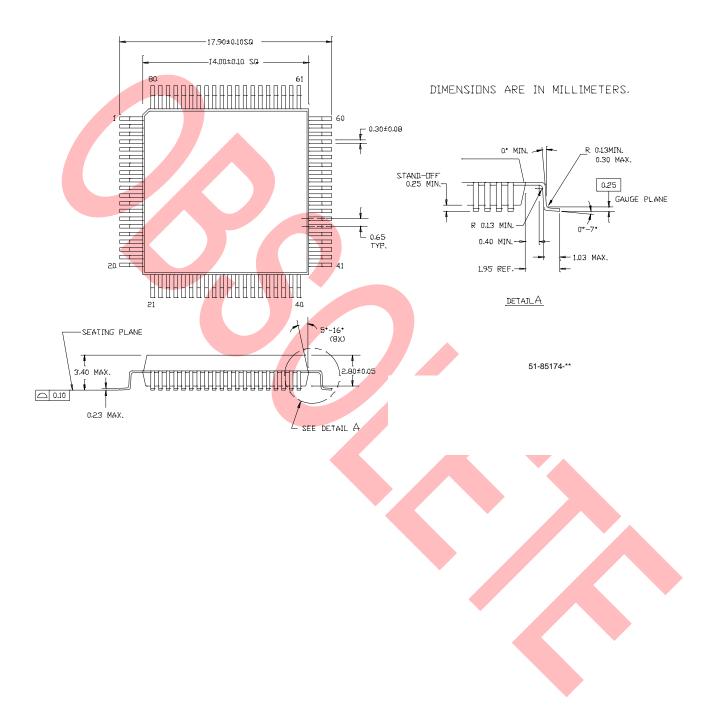

| 9.0 AC ELECTRICAL CHARACTERISTICS         9.1 USB Transceiver         9.2 Program Memory Read         9.3 Data Memory Read         9.4 Data Memory Write         9.5 DMA Read         9.6 DMA Write         9.7 Slave FIFOs—Output Enables         9.8 Slave FIFOs—Synchronous Read         9.9 Slave FIFOs—Synchronous Write         9.10 Slave FIFOs—Asynchronous Read         9.11 Slave FIFOs—Asynchronous Write         9.12 GPIF – Clocked with Fixed 48-MHz Internal Clock         9.13 GPIF Signals Externally Clocked – XCLK         10.0 ORDERING INFORMATION         11.0 PACKAGE DIAGRAMS | 30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>36<br>37<br>38<br>38<br>38<br>38                   |

| 9.0 AC ELECTRICAL CHARACTERISTICS         9.1 USB Transceiver         9.2 Program Memory Read         9.3 Data Memory Read         9.4 Data Memory Write         9.5 DMA Read         9.6 DMA Write         9.7 Slave FIFOs—Output Enables         9.8 Slave FIFOs—Synchronous Read         9.9 Slave FIFOs—Synchronous Read         9.10 Slave FIFOs—Asynchronous Read         9.11 Slave FIFOs—Asynchronous Write         9.12 GPIF – Clocked with Fixed 48-MHz Internal Clock         9.13 GPIF Signals Externally Clocked – XCLK         10.0 ORDERING INFORMATION         11.1 52 PQFP           | 30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>36<br>37<br>38<br>37<br>38<br>38<br>38<br>38<br>39 |

| 9.0 AC ELECTRICAL CHARACTERISTICS         9.1 USB Transceiver         9.2 Program Memory Read         9.3 Data Memory Read         9.4 Data Memory Write         9.5 DMA Read         9.6 DMA Write         9.7 Slave FIFOs—Output Enables         9.8 Slave FIFOs—Synchronous Read         9.9 Slave FIFOs—Synchronous Write         9.10 Slave FIFOs—Asynchronous Read         9.11 Slave FIFOs—Asynchronous Write         9.12 GPIF – Clocked with Fixed 48-MHz Internal Clock         9.13 GPIF Signals Externally Clocked – XCLK         10.0 ORDERING INFORMATION         11.0 PACKAGE DIAGRAMS | 30<br>30<br>31<br>32<br>33<br>34<br>35<br>36<br>36<br>36<br>37<br>38<br>38<br>38<br>38<br>39<br>40 |

## LIST OF FIGURES

\_\_\_\_\_

| Figure 1-1. CY7C64613 Block Diagram                                      | 4 |

|--------------------------------------------------------------------------|---|

| Figure 2-1. General Scheme of Multiplexed Pins for the 128-pin CY7C64613 |   |

| Figure 3-1. CY7C64613 52-pin PQFP Assignment                             |   |

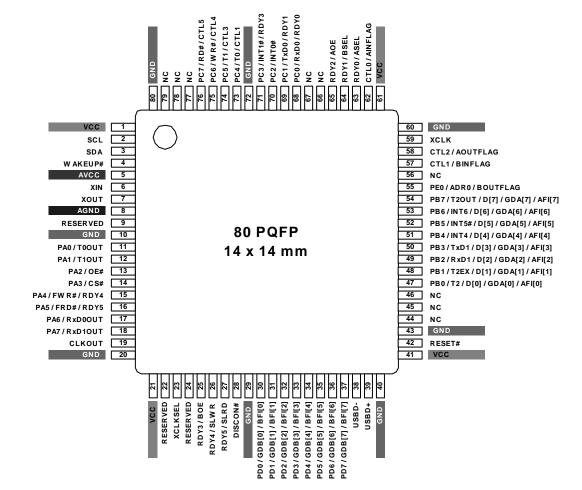

| Figure 3-2. CY7C64613 80 Pin PQFP Assignment                             |   |

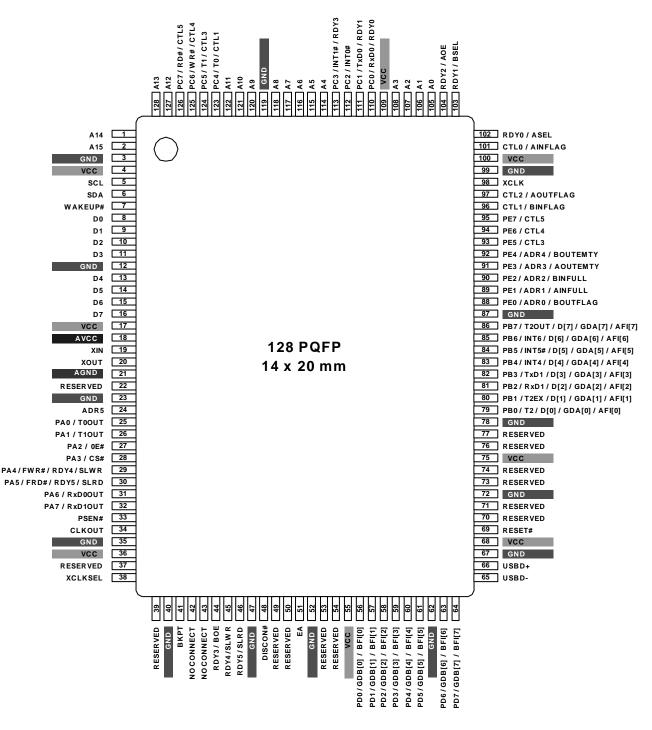

| Figure 3-3. CY7C64613 128 Pin PQFP Assignment                            |   |

## 1.0 Features

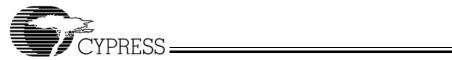

The CY7C64613 (EZ-USB *FX*<sup>™</sup>) is Cypress Semiconductor's second-generation full-speed USB family. FX products offer higher performance and a higher level of integration than first-generation EZ-USB<sup>®</sup> products. FX builds on the EZ-USB feature set, including an intelligent USB core, enhanced 8051, 8-Kbyte RAM, and high-performance I/O while maintaining upward code compatibility. The CY7C64613 enhances the EZ-USB family by providing faster operation and more ways to transfer data into and out of the chip at very high speed.

### Figure 1-1. CY7C64613 Block Diagram

### 1.1 EZ-USB FX Features

- Single-chip integrated USB Transceiver, Serial Interface Engine (SIE), and enhanced 8051 microprocessor

- Certified compliant with USB Specifications 1.1 and 2.0 (full-speed device)

- Software operation: 8051 runs code from internal RAM or external RAM. Code can be:

- Downloaded via USB

- Loaded from EEPROM

- Executed in-place from external memory (e.g., Flash)

- Abundant endpoints and buffers

- —14 Bulk/Interrupt endpoints, each with a maximum packet size of 64 bytes (per USB specification)

- 16 Isochronous endpoints, with 2 KB of buffer space (1 KB, double buffered) which may be divided among the 16 isochronous endpoints

- One control endpoint (bidirectional)

- Integrated, industry standard 8051 with enhanced features:

- -Four clocks per instruction cycle

- -48-MHz or 24-MHz 8051, selectable by EEPROM configuration bit

- Two UARTS (115 K baud)

- Three counter/timers

- Expanded interrupt system

- Two data pointers

- 3.3V operation

- Smart SIE

- -Handles much of the low-level USB protocol in logic, simplifying 8051 code

- General Programmable InterFace (GPIF)

- -Allows direct connection to most parallel interfaces: 8- and 16-bit wide

- Eliminates external glue logic in most applications

- Programmable Waveform Instructions and Configuration Registers to define waveforms

- -Six Ready (RDY) inputs and six Control (CTL) outputs

- Vectored interrupt system expanded for USB, FIFO flags and DMA interrupts

- Separate buffers for SETUP and DATA portions of a CONTROL transfer

- Integrated I2C-compatible controller

- 400-KHz or 100-KHz operation

- Enhanced I/O

- -I/O port registers mapped to 8051 SFRs (Special Function Registers) for high-speed bit operations

- -Port bits can be controlled using 8051 bit addressing instructions

- Up to five 8-bit I/O ports

- Four integrated 8-bit-wide FIFOs

- Each 64 bytes deep

- -Automatic conversion to and from 16-bit buses

- Easy, glueless interface to ASIC, DSP ICs and external logic

- -Brings glue FIFOs inside for lower system cost

- —Internal or external clock

- Synchronous (using strobes and a clock) or asynchronous (using strobes only)

- DMA controller

- Moves data between slave FIFOs, memory, and ports

- Very fast transfers-one clock (20.8 ns = 48 MHz) per byte for internal transfers

- -Can use external RAM as additional FIFO (accessed via Address and Data buses)

- Special Autovectors for DMA and FIFO interrupts

- Glueless external memory expansion

- Up to 16-bit address bus and 8-bit data bus

- -Strobes RD#, WR#, OE#, CS#, and PSEN#

- -Buses not multiplexed (as in standard 8051), saving one clock per external memory cycle

- Three package options–128-pin PQFP, 80-pin PQFP, and 52-pin PQFP

### 1.2 Example Applications

- DSL modems

- ATAPI interface

- · Memory card readers

- Legacy conversion devices

- Cameras

- Scanners

- Home PNA

- Wireless LAN

- MP3 players

- Networking

#### 1.3 Other Resources

Other sources of EZ-USB FX information include:

- EZ-USB FX Technical Reference Manual (TRM), Version 1.2 or higher

- CY3671 EZ-USB FX Development Kit

- The web site www.cypress.com, which includes information about many Reference Designs, such as USB Mass Storage Device, ADSL modem, MPEG.2 players, etc.

### 2.0 Functional Overview

#### 2.1 Microprocessor

The CY7C64613 uses a 12-MHz crystal for low EMI. An internal oscillator and PLL develops an internal 48-MHz clock for use by the USB Serial Interface Engine and the 8051 microprocessor. The 8051 can run at either 24 MHz or 48 MHz, controlled by a bit in the EEPROM attached to the I<sup>2</sup>C-compatible bus. The default rate (with no EEPROM connected) is 24 MHz.

The internal microprocessor is an enhanced version of the industry-standard 8051. Enhancements include four clocks per instruction cycle operation, a second data pointer, and an enhanced interrupt system. The 8051 includes two UARTS, three counter-timers, and 256 bytes of register RAM.

The EZ-USB family implements I/O differently than the standard 8051 by having its I/O control registers in external memory space. The CY7C64613 preserves this addressing for backward EZ-USB compatibility, and adds the ability to control I/O registers using 8051 Special Function Registers (SFRs). This improves I/O access time. For example, an I/O pin may be toggled using one 8051 instruction, e.g., CPL (bit).

The 8051 CODE and XDATA memory consists of an internal 8 KB RAM. This RAM is normally downloaded via the USB cable at plug-in, followed by the 8051 starting up and executing the downloaded code. This gives the CY7C64613 family its "soft" operation feature, whereby permanent memory such as ROM or Flash memory is not required. Program code updates can easily be done in the field since the code is loaded from the PC, not by physically changing or reprogramming a memory device. The 8051 program memory can also be loaded from the EEPROM connected to the I<sup>2</sup>C compatible bus on reset for stand-alone use without the USB connected.

The 128-pin version of the CY7C64613 brings out the full 8051 address and data buses, plus decoded control signals OE#, CS#, RD#, PSEN#, and WR# to allow glueless connection to external memory devices. The 80- and 52-pin packages allow smaller footprints and more cost effective solutions for certain designs, but do not have external access to the 8051 buses.

### 2.2 USB SIE

The CY7C64613 uses the EZ-USB family enhanced SIE (Serial Interface Engine). This SIE has the intelligence to perform full USB enumeration, creating a default USB device with predefined endpoints and alternate settings. This enhanced SIE is essential in achieving the family's soft operation, since it provides the mechanism to download firmware prior to the 8051 running.

Once the 8051 is in control, it can use advanced features of the SIE to simplify its USB firmware. Endpoint zero SETUP data is placed in a separate 8-byte RAM space for easy access. GET\_DESCRIPTOR requests are simplified by using a special Setup Data Pointer. The 8051 simply loads a descriptor address into this 16-bit register, and the SIE takes care of the remaining overhead, i.e., dividing the descriptor into packets, sending them via endpoint 0 in response to IN tokens, and providing the necessary handshakes. The 8051 can do other chores while the SIE completes this USB transfer.

#### 2.3 **GPIF (General Programmable InterFace)**

The GPIF is a flexible 8- or 16-bit parallel interface driven by a user-programmable set of vectors that operate similarly to a finite state machine. It allows the CY7C64613 to perform local bus mastering, and can implement a wide variety of protocols such as ATAPI, printer parallel port, PCMCIA and Utopia.

The GPIF has six programmable Control Outputs (CTL), six Address Outputs (ADR), and six general purpose Ready Inputs (RDY). The data bus width can be 8 or 16 bits. Each GPIF instruction defines the state of the control outputs, or determines what state a ready input (or multiple inputs) must be before proceeding. A sequence of the GPIF instructions make up a single waveform that will be executed to perform the desired data move between the CY7C64613 and the external circuit.

#### 2.4 Slave FIFOs

Many high-bandwidth USB designs use a FIFO between the USB interface chip and external logic to match data rates, or to smooth the USB data delivery (which, being packet oriented, occurs in bursts). The CY7C64613 moves this glue logic into the part by providing four 64-byte internal slave FIFOs. The FIFOs also provide two important interface functions, external clocking and bus width conversion.

Using external clocking, external logic (such as a DSP or ASIC) can clock data into or out of the slave FIFOs under control of its own clock, rather than synchronizing with the clock supplied by the CY7C64613 (24 or 48 MHz). The externally supplied clock

must be free running. The FIFOs can be controlled either synchronously (using strobe signals and a clock) or asynchronously (using strobe signals only). The slave FIFO data is available as two 8-bit buses, which may be used simultaneously to operate as a single 16-bit data bus. The 16-bit connection, along with fast double-byte mode, combine to give fast conversion between 8- and 16-bit buses. A flexible set of FIFO flags (full, empty, and programmable) provide FIFO flow control.

### 2.5 DMA

With many sources and destinations for USB data, such as endpoint buffers, slave FIFOs, and internal/external RAM buffers, it is important to move blocks of data between them quickly. Using internal DMA, the 8051 sets up source, destination, and transfer length registers, and then initiates a DMA transfer. The maximum DMA transfer rate occurs between internal resources, such as endpoint buffers and slave FIFOs. This maximum rate is one byte per 48-MHz clock, or 48 Mbytes per second.

### 2.6 Flexible Configuration

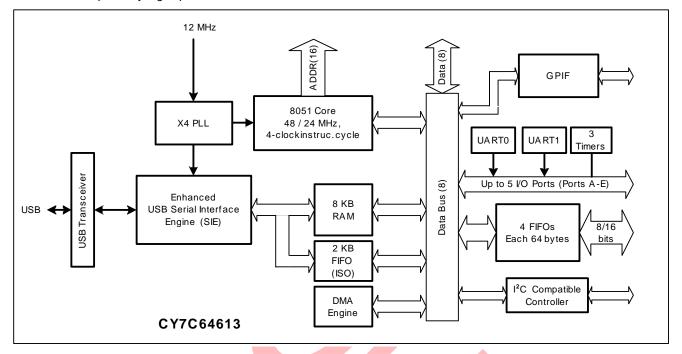

The EZ-USB *FX* supports a highly configurable I/O structure. *Figure 2-1* on page 8 shows the general scheme of the assignment of pins to I/O ports. The 80- and 56-pin products are subsets of the 128-pin products, hence they follow a similar scheme. For details of how to set the configuration registers to configure the I/O ports, consult "CY7C64613 Pin Descriptions" on page 14 of this data sheet and the EZ-USB *FX* TRM.

Figure 2-1. General Scheme of Multiplexed Pins for the 128-pin CY7C64613

### 2.7 Endpoints

| Endpoint | Туре           | Buffer Size<br>(Bytes)             |

|----------|----------------|------------------------------------|

| EP0-IN   | Control        | 64                                 |

| EP0-OUT  | Control        | 64                                 |

| EP1-IN   | Bulk/Interrupt | 64                                 |

| EP1-OUT  | Bulk/Interrupt | 64                                 |

| EP2-IN   | Bulk/Interrupt | 64                                 |

| EP2-OUT  | Bulk/Interrupt | 64                                 |

| EP3-IN   | Bulk/Interrupt | 64                                 |

| EP3-OUT  | Bulk/Interrupt | 64                                 |

| EP4-IN   | Bulk/Interrupt | 64                                 |

| EP4-OUT  | Bulk/Interrupt | 64                                 |

| EP5-IN   | Bulk/Interrupt | 64                                 |

| EP5-OUT  | Bulk/Interrupt | 64                                 |

| EP6-IN   | Bulk/Interrupt | 64                                 |

| EP6-OUT  | Bulk/Interrupt | 64                                 |

| EP7-IN   | Bulk/Interrupt | 64                                 |

| EP7-OUT  | Bulk/Interrupt | 64                                 |

| EP8-IN   | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP8-OUT  | Isochronous    | 0-1023 <sup>[1]</sup>              |

| EP9-IN   | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP9-OUT  | Isochronous    | 0–10 <mark>23<sup>[1]</sup></mark> |

| EP10-IN  | Isochronous    | 0–1 <mark>023<sup>[1]</sup></mark> |

| EP10-OUT | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP11-IN  | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP11-OUT | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP12-IN  | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP12-OUT | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP13-IN  | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP13-OUT | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP14-IN  | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP14-OUT | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP15-IN  | Isochronous    | 0–1023 <sup>[1]</sup>              |

| EP15-OUT | Isochronous    | 0–1023 <sup>[1]</sup>              |

The CY7C64613 has 16 Control, Bulk, and Interrupt endpoints. One endpoint pair is dedicated to endpoint zero, with separate EP0-IN and EP0-OUT buffers. Fourteen additional 64-byte buffers may be used as Bulk or Interrupt endpoints. These endpoints may be double-buffered by using an endpoint pairing mechanism. Double buffering allows the 8051 to access a packet as another packet is being transmitted or received over USB. This technique is essential in high-bandwidth applications where NAKs by the USB device would reduce performance.

The CY7C64613 also has sixteen Isochronous (ISO) endpoints which share 1024 bytes of double-buffered endpoint memory (2 KB total). The ISO buffer sizes are programmable in 16-byte increments. The Isochronous endpoint buffers are accessed as FIFOs.

Endpoint data is serviced either directly by the 8051, or moved on- or off-chip using the built in DMA controller. Bulk data is visible either in 64-byte random access buffers, or as FIFOs (using the AutoPointer feature).

Each endpoint has its own interrupt vector, allowing ISRs (Interrupt Service Routines) to be called automatically, with minimum overhead and latency. Note:

1. A total of 1024 FIFO bytes can be divided among all Isochronous endpoints. (1023 is the maximum USB-specified Isochronous Full-speed packet size.)

### 2.8 Default USB Machine

When the CY7C64613 is plugged into the USB with no EEPROM attached to its I<sup>2</sup>C compatible port (but with the SCL and SDA pull-ups installed), the intelligent SIE enumerates as a generic USB device with the following characteristics.

| ID Bytes         |       |

|------------------|-------|

| VID (Vendor ID)  | 0547h |

| PID (Product ID) | 2235h |

| DID (Device ID)  | 0000h |

|                  |       |

#### **Default Endpoints**

| Endpoint | Туре | Alternate Setting |             |       |  |  |

|----------|------|-------------------|-------------|-------|--|--|

|          |      | 0                 | 1           | 2     |  |  |

|          |      | Max Pac           | ket Size (b | ytes) |  |  |

| 0        | CTL  | 64                | 64          | 64    |  |  |

| 1 IN     | INT  | 0                 | 16          | 64    |  |  |

| 2 IN     | BULK | 0                 | 64          | 64    |  |  |

| 2 OUT    | BULK | 0                 | 64          | 64    |  |  |

| 4 IN     | BULK | 0                 | 64          | 64    |  |  |

| 4 OUT    | BULK | 0                 | 64          | 64    |  |  |

| 6 IN     | BULK | 0                 | 64          | 64    |  |  |

| 6 OUT    | BULK | 0                 | 64          | 64    |  |  |

| 8 IN     | ISO  | 0                 | 16          | 256   |  |  |

| 8 OUT    | ISO  | 0                 | 16          | 256   |  |  |

| 9 IN     | ISO  | 0                 | 16          | 16    |  |  |

| 9 OUT    | ISO  | 0                 | 16          | 16    |  |  |

| 10 IN    | ISO  | 0                 | 16          | 16    |  |  |

| 10 OUT   | ISO  | 0                 | 16          | 16    |  |  |

## 2.9 IBN (In-Bulk-NAK) Interrupts

The CY7C64613 has a special interrupt called In-Bulk-NAK. IBN is triggered when an IN token has been received by an endpoint (the host is attempting to read data), but the SIE has NAK'd the host (because there is no data in the endpoint). The 8051 program can identify which endpoint triggered the interrupt by reading the IBNIRQ register, where a bit is set for the endpoint (EP1-IN to EP7-IN) that caused the NAK.

## 3.0 Pins

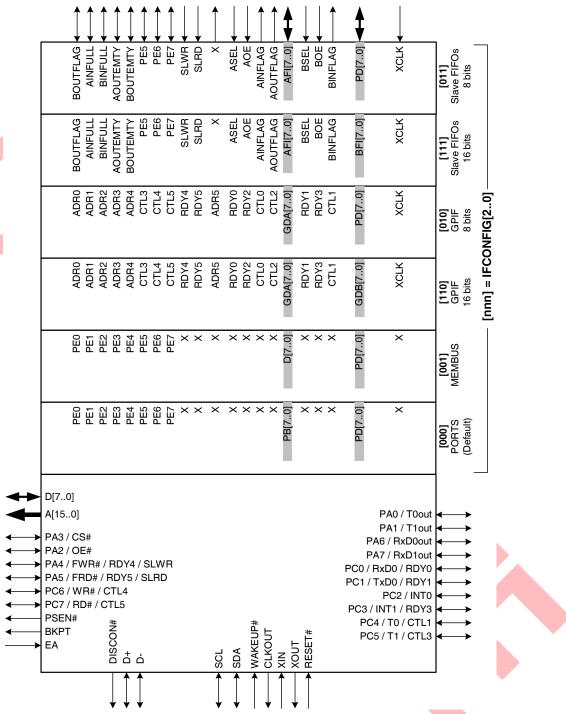

3.1 Pin Diagrams

Figure 3-1. CY7C64613 52-pin PQFP Assignment

## 3.1 **Pin Diagrams** (continued)

Figure 3-2. CY7C64613 80 Pin PQFP Assignment

### 3.1 Pin Diagrams (continued)

Figure 3-3. CY7C64613 128 Pin PQFP Assignment

### 3.2 General Notes About the Pin Description Table

- 1. See the EZ-USB FX TRM: For multiplexed pins, consult the EZ-USB FX TRM (primarily Chapter 4) for details of setting the configuration registers.

- 2. **Multiple Routed Signals**: In some cases, an internal signal can be routed to more than one pin. For example, in the 80 and 128-pin packages RDY4 can be routed to any combination of (neither, either or both) pins 15 and 26.

- 3. **Tie Up Unused Inputs**: It is important that the recommendations in the Pin Description Table be followed, especially for inputs. Unused CMOS inputs can oscillate if they are left open (floating), which can cause higher power usage and decreased reliability.

- 4. **Tie Up Certain Outputs That Are Initially Inputs**: Many alternate functions of the *FX* multiplexed pins are *similar* to the WR# alternate functions (see the PC6 / WR# / CTL4 pin below) in the following respect:

If WR# is chosen as the function of PC6, it should be pulled up to VCC through a pull-up resistor. This is to ensure that WR# is inactive (pulled HIGH) at power-up, since, before the 8051 can configure this pin to WR#, it defaults to 'PC6 an input' (not driven by the FX pin).

All multiplexed pins that you use should be carefully considered in your circuit design for the effects of the transition through their default configuration at power-up. These are typically (though not always) active LOW signals such as WR#.

The critical time interval to be considered is between RESET# deasserted and the pin driven as an output (immediately after the 8051 code has initialized the port to be an alternate function that it is an output).

| 128 | 80 | 52 | Name    | Туре   | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|----|----|---------|--------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | 5  | 5  | AVCC    | Power  | N/A     | Analog V <sub>CC</sub> . This signal provides power to the analog section of the chip.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 21  | 8  | 8  | AGND    | Power  | N/A     | Analog Ground. Connect to ground with as short a path as possible.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 48  | 28 | 18 | DISCON# | O/Z    | F       | <b>Disconnect.</b> This pin can drive HIGH, LOW, or float. DISCON# pin floats when the register bit USBCS.2 is LOW, and drives when it is HIGH. The drive level of the DISCON# pin is the invert of register bit USBCS.3. The DISCON# pin is normally connected to the USB D+ line through a 1500 $\Omega$ resistor. The CY7C64613 signals a USB connection by setting USBCS.3=0 (drive 3.3V) and USBCS.2=1 (output enable). The CY7C64613 signals a USB disconnect by setting USBCS.2=0 which floats the pin and disconnects the 1500 $\Omega$ resistor from D+. |

| 65  | 38 | 24 | USBD-   | I/O/Z  | Z       | <b>USB D</b> – Connect to the USB D– signal through a $22 \pm 5\%$ ohm resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 66  | 39 | 25 | USBD+   | I/O/Z  | Z       | <b>USB D+</b> Connect to the USB D+ signal through a 22 ±5% ohm resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 105 |    |    | A0      | Output | L       | 8051 Address Bus. This bus is driven at all times. When the 8051 is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 106 |    |    | A1      | Output | L       | addressing internal RAM it reflects the internal address. During DMA transfers that use the RD# and WR# strobes, the address bus contains                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 107 |    |    | A2      | Output | L       | the incrementing DMA source or destination address for data trans-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 108 |    |    | A3      | Output | L       | ferred over D[7.0].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 114 |    |    | A4      | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 115 |    |    | A5      | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 116 |    |    | A6      | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 117 |    |    | A7      | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 118 |    |    | A8      | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 120 |    |    | A9      | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 121 |    |    | A10     | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 122 |    |    | A11     | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 127 |    |    | A12     | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 128 |    |    | A13     | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1   |    |    | A14     | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2   |    |    | A15     | Output | L       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### 3.3 CY7C64613 Pin Descriptions

| 128 | 80 | 52 | Name   | Туре   | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|----|----|--------|--------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8   |    |    | D0     | I/O/Z  | Z       | 8051 Data Bus. This bidirectional bus is:                                                                                                                                                                                                                                                                                                                                                                                        |

| 9   |    |    | D1     | I/O/Z  | Z       | <ul> <li>input for bus reads</li> <li>output for bus writes</li> </ul>                                                                                                                                                                                                                                                                                                                                                           |

| 10  |    |    | D2     | I/O/Z  | Z       | – high-impedance when inactive.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 11  |    |    | D3     | I/O/Z  | Z       | The data bus is active only for external bus accesses, and is driven                                                                                                                                                                                                                                                                                                                                                             |

| 13  |    |    | D4     | I/O/Z  | Z       | LOW in suspend.<br>The data bus is used for:                                                                                                                                                                                                                                                                                                                                                                                     |

| 14  |    |    | D5     | I/O/Z  | Z       | <ul> <li>– external 8051 program and data memory.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                     |

| 15  |    |    | D6     | I/O/Z  | Z       | -DMA transfers that use the RD#, FRD#, WR#, FWR# pins as strobes.                                                                                                                                                                                                                                                                                                                                                                |

| 16  |    |    | D7     | I/O/Z  | Z       |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 33  |    |    | PSEN#  | Output | Ξ       | Program Store Enable PSEN# strobes LOW when the 8051 fetches<br>a CODE byte from external memory.<br>If EA = 0, the 8051 fetches CODE from external memory from<br>0x1B40 to 0xFFFF.<br>If EA = 1, the 8051 fetches CODE from external memory from<br>0x0000 to 0xFFFF.<br>See EA pin.                                                                                                                                           |

| 41  |    |    | ВКРТ   | Output | L       | <b>Breakpoint</b> . This pin goes active (HIGH) when the 8051 address bus matches the BPADDRH/L registers and breakpoints are enabled in the USBBAV register (BPEN=1). If the BPPULSE bit in the USBBAV register is HIGH, BKPT pulses HIGH for eight 24-/48-MHz clocks. If the BPPULSE bit is LOW, BKPT stays HIGH until the 8051 clears the BREAK bit (by writing a 1 to it) in the USBBAV register.                            |

| 69  | 42 | 28 | RESET# | Input  | N/A     | Active LOW Reset. This pin resets the entire chip. It is normally tied to $V_{CC}$ through a 10K resistor and to GND through a 1-µF capacitor. Hysteresis input.                                                                                                                                                                                                                                                                 |

| 51  |    |    | EA     | Input  | N/A     | External Access. This pin determines where the 8051 fetches code<br>between addresses 0x0000 and 0x1B3F.<br>If EA=0 the 8051 fetches this code from its internal RAM.<br>If EA=1 the 8051 fetches this code from external memory.<br>(normally used to boot from external memory, for example, boot from<br>Flash). This pin is "live".<br>See PSEN# pin.<br>(EA is tied to GND internally in both the 80- and 52-pin packages.) |

| 19  | 6  | 6  | XIN    | Input  | N/A     | <b>Crystal Input</b> . Connect this signal to a 12-MHz series-resonant, fundamental mode crystal and 22–33 pF capacitor to GND. Also connect a $1-M\Omega$ resistor between XIN and XOUT.<br>It is also correct to drive XIN with an external 12-MHz square wave derived from another clock source.                                                                                                                              |

| 20  | 7  | 7  | XOUT   | Output | N/A     | <b>Crystal Output</b> . Connect this signal to a 12-MHz series-resonant, fundamental mode crystal and 22–33 pF capacitor to GND. Also connect a $1-M\Omega$ resistor between XIN and XOUT. If an external clock is used to drive XIN, leave this pin open.                                                                                                                                                                       |

|     |    |    |        |        |         |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 128    | 80 | 52 | Name                                 | Туре  | Default    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|----|----|--------------------------------------|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 34     | 19 | 12 | CLKOUT                               | O/Z   | 24 MHz     | <b>Clock Output.</b> This is the 24- or 48-MHz clock, the master clock for<br>the 8051, phase locked to the 12-MHz XIN/XOUT clock.<br>(Note: the GPIF always uses a 48-MHz clock or XCLK, regardless of<br>the 8051 clock. See XCLK and XCLKSEL.)<br>The frequency of the 8051 clock is set via a boot EEPROM bit:<br>If Config 0.2 = 0, CLKOUT is 24 MHz.<br>If Config 0.2 = 1, CLKOUT is 48 MHz.<br>CLKOUT may be inverted by setting a boot EEPROM bit CONFIG0.1<br>= 1.<br>If no EEPROM is connected to the I <sup>2</sup> C compatible port (the required<br>pull-up resistors must be present), the Config0 bits default to zero,<br>hence<br>- CLKOUT is 24 MHz<br>- CLKOUT is 24 MHz<br>- CLKOUT is non-inverted.<br>The 8051 may three-state this output by setting CPUCS.1 = 1. |

| Port A | 1  |    |                                      |       |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 25     | 11 |    | PA0 or<br>TOOUT                      | I/O/Z | l<br>(PA0) | Multiplexed pin whose function is selected by two bits:<br>PORTACFG.0 and IFCONFIG.3.<br><b>PA0</b> is a bidirectional IO port pin.<br><b>TOOUT</b> is an active-HIGH signal from 8051 Timer-counter0. TOOUT<br>outputs a high level for one CLKOUT clock cycle when Timer0<br>overflows. If Timer0 is operated in mode 3 (two separate<br>timer/counters), TOOUT is active when the low byte timer/counter<br>overflows.                                                                                                                                                                                                                                                                                                                                                                 |

| 26     | 12 |    | PA1 or<br>T1OUT                      | 1/O/Z | l<br>(PA1) | Multiplexed pin whose function is selected by two bits:<br>PORTACFG.1 and IFCONFIG.3.<br>PA1 is a bidirectional IO port pin.<br>T1OUT is an active-HIGH signal from 8051 Timer-counter1. T1OUT<br>outputs a high level for one CLKOUT clock cycle when Timer1<br>overflows. If Timer1 is operated in mode 3 (two separate<br>timer/counters), T1OUT is active when the low byte timer/counter<br>overflows.                                                                                                                                                                                                                                                                                                                                                                               |

| 27     | 13 |    | PA2 or<br>OE# or                     | I/O/Z | l<br>(PA2) | Multiplexed pin whose function is selected by two bits:<br>PORTACFG.2 and IFCONFIG.3.<br><b>PA2</b> is a bidirectional IO port pin.<br><b>OE#</b> is an active-LOW output enable for external memory.<br>If the OE# function is chosen for this pin, it should be externally pulled<br>up to $V_{CC}$ through a pull-up resistor. This is to ensure that OE# is<br>inactive (pulled HIGH) at power up, since, before the 8051 can<br>configure this pin to OE#, it defaults to 'PA2 an input'                                                                                                                                                                                                                                                                                             |

| 28     | 14 |    | PA3 or<br>CS#                        | I/O/Z | l<br>(PA3) | Multiplexed pin whose function is selected by the PORTACFG.3 bit.<br><b>PA3</b> is a bidirectional I/O port pin.<br><b>CS#</b> is an active-LOW chip select for external memory.<br>If the CS# function is chosen for this pin, it should be externally pulled<br>up to $V_{CC}$ . This is to ensure that CS# is inactive (pulled HIGH) at power<br>up, since, before the 8051 can configure this pin to CS#, it defaults to<br>'PA3 an input'.                                                                                                                                                                                                                                                                                                                                           |

| 29     | 15 | 10 | PA4 or<br>FWR# or<br>RDY4 or<br>SLWR | I/O/Z | I<br>(PA4) | Multiplexed pin whose function is selected by the following bits:<br>PORTACFG.4, PORTACF2.4, and IFCONFIG[10].<br><b>PA4</b> is a bidirectional I/O port pin.<br><b>FWR#</b> is the write strobe output for an external FIFO connected to the<br>data bus D[70]. <b>RDY4</b> is a GPIF input signal.<br><b>RDY4</b> is a GPIF input signal.<br><b>SLWR</b> is the write strobe input for the slave FIFOs connected to<br>AFI[70] and/or BFI[70].<br>If the FWR# pin is used, it should be externally pulled up to V <sub>CC.</sub> This<br>is to ensure that FWR# is inactive (pulled HIGH) at power up, since,<br>before the 8051 can configure this pin to FWR#, it defaults to 'PA4 an<br>input'.                                                                                      |

| 128    | 80 | 52 | Name                                                 | Туре  | Default    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |