# Automotive 3-Phase MOSFET Driver

#### **Selection Guide**

| A4937KLPTR-A-T4000 pieces per 13-in. reel4.4 mm × 9.7 mm, 1.2 mm maximum height TSSOP<br>with exposed thermal pad | Part Number    | Packing*                    | Package |

|-------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|---------|

|                                                                                                                   | A4937KLPTR-A-T | 4000 pieces per 13-in. reel |         |

\*Contact Allegro<sup>TM</sup> for additional packing options.

#### **Absolute Maximum Ratings\***

| Characteristic                             | Symbol               | Notes                                                                                                                           | Rating                                              | Unit |

|--------------------------------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|

| Load Supply Voltage                        | V <sub>BB</sub>      |                                                                                                                                 | -0.3 to 50                                          | V    |

| Logic Supply Voltage                       | V <sub>DD</sub>      |                                                                                                                                 | -0.3 to 6                                           | V    |

| Terminal VREG                              | V <sub>REG</sub>     |                                                                                                                                 | -0.3 to 16                                          | V    |

| Terminal CP1                               | V <sub>CP1</sub>     |                                                                                                                                 | -0.3 to 16                                          | V    |

| Terminal CP2                               | V <sub>CP2</sub>     |                                                                                                                                 | V <sub>CP1</sub> – 0.3 to<br>V <sub>REG</sub> + 0.3 | V    |

| L e sie lanute                             | VI                   | STRn, SCK, SDI, PWMH, PWML                                                                                                      | -0.3 to 6                                           | V    |

| Logic Inputs                               |                      | RESETn; can be pulled to $V_{BB}$ with >22 k $\Omega$                                                                           | -0.3 to 6                                           | V    |

| Logic Outputs                              | Vo                   | SDO                                                                                                                             | -0.3 to V <sub>DD</sub> + 0.3                       | V    |

| Terminal DIAG                              | V <sub>DIAG</sub>    |                                                                                                                                 | -0.3 to V <sub>DD</sub> + 0.3                       | V    |

| Terminal VBRG                              | V <sub>BRG</sub>     |                                                                                                                                 | –5 to 55                                            | V    |

| Terminals CA, CB, CC                       | V <sub>Cx</sub>      |                                                                                                                                 | –0.3 to V <sub>REG</sub> + 50                       | V    |

| Terminals GHA, GHB, GHC                    | V <sub>GHx</sub>     |                                                                                                                                 | V <sub>Cx</sub> – 16 to<br>V <sub>Cx</sub> + 0.3    | V    |

| Terminals SA, SB, SC                       | V <sub>Sx</sub>      |                                                                                                                                 | V <sub>Cx</sub> – 16 to<br>V <sub>Cx</sub> + 0.3    | V    |

| Terminals GLA, GLB, GLC                    | V <sub>GLx</sub>     |                                                                                                                                 | V <sub>REG</sub> – 16 to 18                         | V    |

| Terminal LSS                               | V <sub>LSS</sub>     |                                                                                                                                 | V <sub>REG</sub> – 16 to 18                         | V    |

| Ambient Operating Temperature<br>Range     | T <sub>A</sub>       | Limited by power dissipation                                                                                                    | -40 to 150                                          | °C   |

| Maximum Continuous Junction<br>Temperature | T <sub>J</sub> (max) |                                                                                                                                 | 150                                                 | °C   |

| Transient Junction Temperature             | T <sub>tJ</sub>      | Overtemperature event not exceeding 10s,<br>lifetime duration not exceeding 10 hours,<br>guaranteed by design characterization. | 175                                                 | °C   |

| Storage Temperature Range                  | T <sub>stg</sub>     |                                                                                                                                 | -55 to 150                                          | °C   |

\*With respect to GND. Ratings apply when no other circuit operating constraints are present.

#### Thermal Characteristics may require derating at maximum conditions

| Characteristic                               | Symbol          | Test Conditions*                                               | Value | Unit |

|----------------------------------------------|-----------------|----------------------------------------------------------------|-------|------|

| Package Thermal Resistance (Junction         | $R_{\theta JA}$ | On 4-layer PCB based on JEDEC standard                         | 28    | °C/W |

| to Ambient)                                  |                 | 2-layer PCB with 3.8 in. <sup>2</sup> of copper area each side | 32    | °C/W |

| Package Thermal Resistance (Junction to Pad) | $R_{\theta JP}$ |                                                                | 2     | °C/W |

\*Additional thermal information available on the Allegro website.

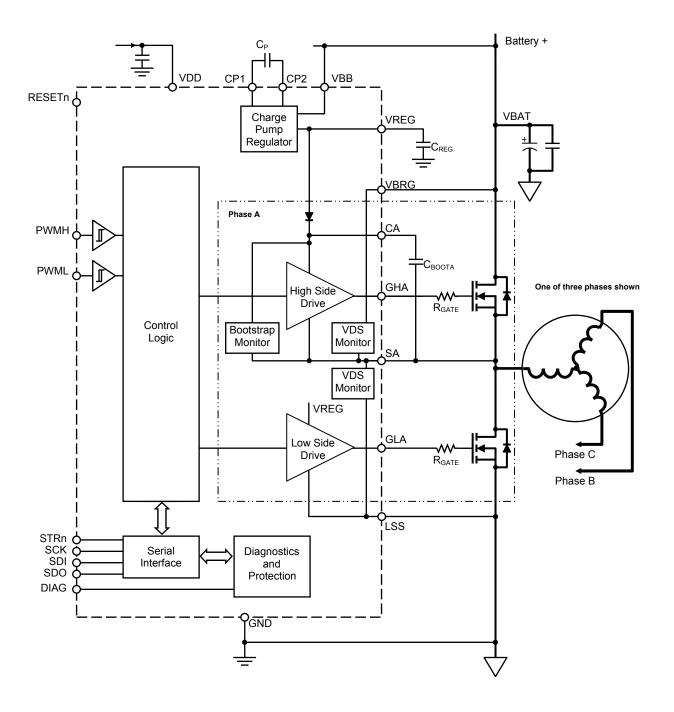

### **Functional Block Diagram**

## **Automotive 3-Phase MOSFET Driver**

**Revision Table**

| Number | Date             | Description             |

|--------|------------------|-------------------------|

| 2      | January 29, 2019 | Minor editorial updates |

| 3      | February 6, 2020 | Minor editorial updates |

Copyright 2020, Allegro MicroSystems.

Allegro MicroSystems reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

<u>Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of</u> <u>Allegro's product can reasonably be expected to cause bodily harm.</u>

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

Copies of this document are considered uncontrolled documents.