The AT17LV configurators can be programmed with industry-standard programmers, the Atmel ATDH2200E Programming Kit, or the Atmel ATDH2225 ISP Cable.

Table 1. AT17LV Packages

| Package      | AT17LV65/128/256 <sup>(4)</sup> | AT17LV512/010                 | AT17LV002                     | AT17LV040 |

|--------------|---------------------------------|-------------------------------|-------------------------------|-----------|

| 8-lead LAP   | Yes                             | Yes                           | Yes                           | (3)       |

| 8-lead PDIP  | Yes                             | Yes                           | _                             | _         |

| 8-lead SOIC  | Yes                             | Use 8-lead LAP <sup>(1)</sup> | Use 8-lead LAP <sup>(1)</sup> | (3)       |

| 20-lead PLCC | Yes                             | Yes                           | Yes                           | _         |

| 20-lead SOIC | Yes <sup>(2)</sup>              | _                             | Yes <sup>(2)</sup>            | _         |

| 44-lead TQFP | _                               | <del>_</del>                  | Yes                           | Yes       |

#### Notes:

- 1. The 8-lead LAP package has the same footprint as the 8-lead SOIC. Since an 8-lead SOIC package is not available for the AT17LV512/010/002 devices, it is possible to use an 8-lead LAP package instead.

- 2. The pinout for the AT17LV65 (NRND), AT17LV128 (NRND), and AT17LV256 is not pin-for-pin compatible with the AT17LV512/010/002 devices.

- 3. Refer to the AT17F datasheet which is available on the Atmel website.

- 4. The AT17LV65 and AT17LV128 are not recommended for new designs (NRND).

# 1. Pin Configuration and Descriptions

Table 1-1. Pin Descriptions

| Pin             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATA            | <b>Three-state Data Output for Configuration.</b> Open-collector bi-directional pin for programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CLK             | <b>Clock Input.</b> Used to increment the internal address and bit counter for reading and programming.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WP1             | <b>Write Protect (1)</b> . Used to protect portions of memory during programming. Disabled by default due to internal pull-down resistor. This input pin is not used during FPGA loading operations. This pin is only available on AT17LV512/010/002 devices.                                                                                                                                                                                                                                                                                                                      |

| RESET/OE        | RESET (Active Low) / Output Enable (Active High) when SER_EN is High. A Low level on RESET/OE resets both the address and bit counters. A High level (with CE Low) enables the data output driver. The logic polarity of this input is programmable as either RESET/OE or RESET/OE. For most applications, RESET should be programmed active Low. This document describes the pin as RESET/OE.                                                                                                                                                                                     |

| WP              | <b>Write Protect Input</b> (when $\overline{\text{CE}}$ is Low) during programming only ( $\overline{\text{SER}}$ _EN Low). When WP is Low, the entire memory can be written. When WP is enabled (High), the lowest block of the memory cannot be written. This pin is only available on the AT17LV65 (NRND), AT17LV128 (NRND), and the AT17LV256.                                                                                                                                                                                                                                 |

| WP2             | <b>Write Protect (2).</b> Used to protect portions of memory during programming. Disabled by default due to internal pull-down resistor. This input pin is not used during FPGA loading operations. This pin is only available on the AT17LV512/010.                                                                                                                                                                                                                                                                                                                               |

| CE              | Chip Enable Input (Active Low). A Low level (with OE High) allows CLK to increment the address counter and enables the data output driver. A High level on CE disables both the address and bit counters and forces the device into a low-power standby mode. Note that this pin will not enable/disable the device in the Two-Wire Serial Programming mode (SER_EN Low).                                                                                                                                                                                                          |

| GND             | $\textbf{Ground}.$ A 0.2µF decoupling capacitor between $V_{\text{CC}}$ and GND is recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CEO             | Chip Enable Output (Active Low). This output goes Low when the address counter has reached its maximum value. In a daisy chain of AT17LV devices, the $\overline{\text{CEO}}$ pin of one device must be connected to the $\overline{\text{CE}}$ input of the next device in the chain. It will stay Low as long as $\overline{\text{CE}}$ is Low and OE is High. It will then follow CE until OE goes Low; thereafter, $\overline{\text{CEO}}$ will stay High until the entire EEPROM is read again. This $\overline{\text{CEO}}$ feature is not available on the AT17LV65 (NRND). |

| A2              | <b>Device Selection Input, A2</b> . This is used to enable (or select) the device during programming (i.e., when SER_EN is Low). A2 has an internal pull-down resistor.                                                                                                                                                                                                                                                                                                                                                                                                            |

| READY           | Open Collector Reset State Indicator. Driven Low during power-up reset, released when power-up is complete. It is recommended to use a $4.7k\Omega$ pull-up resistor when this pin is used.                                                                                                                                                                                                                                                                                                                                                                                        |

| SER_EN          | <b>Serial Enable</b> must be held High during FPGA loading operations. Bringing $\overline{SER}$ EN Low enables the 2-wire Serial Programming Mode. For non-ISP applications, $\overline{SER}$ EN should be tied to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>cc</sub> | Power Supply. 3.3V (±10%) and 5.0V (±10%) power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 1-2. Pin Configurations

|                    |     | AT17L                      | .V65/128/       | <b>256</b> <sup>(2)</sup> | AT17LV                | 512/010         |               | AT17L\          | /002            |                 | AT17LV040       |

|--------------------|-----|----------------------------|-----------------|---------------------------|-----------------------|-----------------|---------------|-----------------|-----------------|-----------------|-----------------|

| Name               | I/O | 8-lead<br>DIP/LAP/<br>SOIC | 20-lead<br>PLCC | 20-lead<br>SOIC           | 8-lead<br>DIP/<br>LAP | 20-lead<br>PLCC | 8-lead<br>LAP | 20-lead<br>PLCC | 20-lead<br>SOIC | 44-lead<br>TQFP | 44-lead<br>TQFP |

| DATA               | I/O | 1                          | 2               | 2                         | 1                     | 2               | 1             | 2               | 1               | 40              | 40              |

| CLK                | I   | 2                          | 4               | 4                         | 2                     | 4               | 2             | 4               | 3               | 43              | 43              |

| WP1                | I   | _                          | -               | _                         | _                     | 5               | _             | 5               | _               | 7               | _               |

| RESET/ <b>OE</b>   | I   | 3                          | 6               | 6                         | 3                     | 6               | 3             | 6               | 8               | 13              | 13              |

| WP2                | I   | _                          | -               | _                         | _                     | 7               | -             | 7               | _               | _               | -               |

| CE                 | I   | 4                          | 8               | 8                         | 4                     | 8               | 4             | 8               | 10              | 15              | 15              |

| GND                |     | 5                          | 10              | 10                        | 5                     | 10              | 5             | 10              | 11              | 18              | 18              |

| CEO <sup>(1)</sup> | 0   | 6                          | 14              | 14                        | 6                     | 14              | 6             | 14              | 13              | 21              | 21              |

| A2                 | I   | 0                          | 14              | 14                        | 0                     | 14              | O             | 14              | _               | 21              | 21              |

| READY              | 0   | _                          | _               | _                         | _                     | 15              | _             | 15              | _               | 23              | 23              |

| SER_EN             | I   | 7                          | 17              | 17                        | 7                     | 17              | 7             | 17              | 18              | 35              | 35              |

| V <sub>CC</sub>    |     | 8                          | 20              | 20                        | 8                     | 20              | 8             | 20              | 20              | 38              | 38              |

Notes: 1. The  $\overline{\text{CEO}}$  feature is not available on the AT17LV65 (NRND).

2. The AT17LV65 and AT17LV128 are not recommended for new designs.

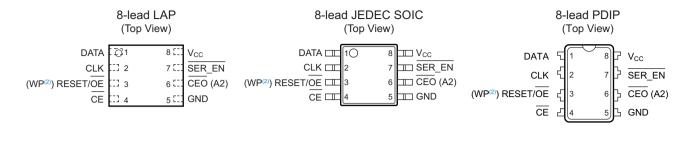

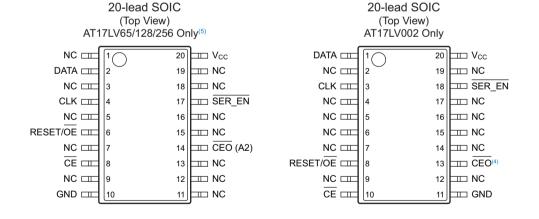

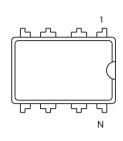

Figure 1-1. Pinouts<sup>(1)</sup>

Notes: 1. Drawings are not to scale.

- 2. This pin is only available on the AT17LV65 (NRND), AT17LV128 (NRND), and AT17LV256.

- 3. This pin is only available on the AT17LV512/010/002.

- 4. This pin is not available on the AT17LV65 (NRND).

- 5. The AT17LV65 and AT17LV128 are not recommended for new designs.

# 2. Block Diagram

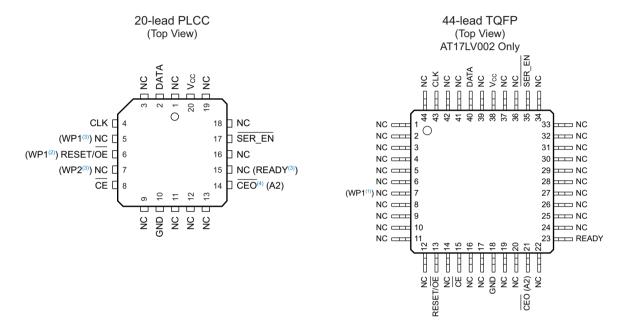

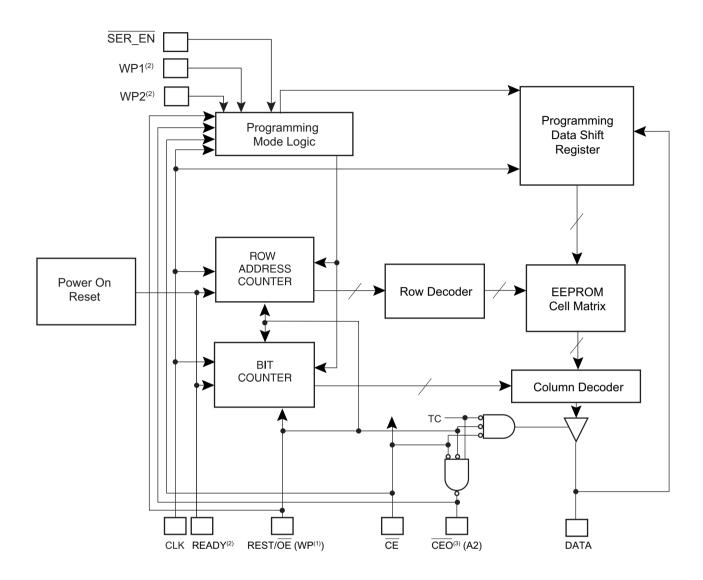

Figure 2-1. Block Diagram

Notes: 1. This pin is only available on the AT17LV65 (NRND), AT17LV128 (NRND), and AT17LV256.

- 2. This pin is only available on AT17LV512, AT17LV010, and AT17LV002.

- 3. The CEO feature is not available on the AT17LV65 (NRND).

# 3. Device Description

The control signals for the configuration EEPROM ( $\overline{\text{CE}}$ , RESET/ $\overline{\text{OE}}$  and CCLK) interface directly with the FPGA device control signals. All FPGA devices can control the entire configuration process and retrieve data from the configuration EEPROM without requiring an external intelligent controller.

The configuration EEPROM RESET/ $\overline{OE}$  and  $\overline{CE}$  pins control the tri-state buffer on the DATA output pin and enable the address counter. When RESET/ $\overline{OE}$  is driven High, the configuration EEPROM resets its address counter and tri-states its DATA pin. The  $\overline{CE}$  pin also controls the output of the AT17LV configurator. If  $\overline{CE}$  is held High after the RESET/ $\overline{OE}$  reset pulse, the counter is disabled and the DATA output pin is tri-stated. When  $\overline{OE}$  is subsequently driven Low, the counter and the DATA output pin are enabled. When RESET/ $\overline{OE}$  is driven High again, the address counter is reset and the DATA output pin is tri-stated, regardless of the state of  $\overline{CE}$ .

When the configurator has driven out all of its data and  $\overline{\text{CEO}}$  is driven Low, the device tri-states the DATA pin to avoid contention with other configurators. Upon power-up, the address counter is automatically reset.

This is the default setting for the device. Since almost all FPGAs use RESET Low and OE High, this document will describe RESET/OE.

# 4. FPGA Master Serial Mode Summary

The I/O and logic functions of any SRAM-based FPGA are established by a configuration program. The program is loaded either automatically upon power-up, or on command, depending on the state of the FPGA mode pins. In Master mode, the FPGA automatically loads the configuration program from an external memory. The AT17LV Serial Configuration EEPROM has been designed for compatibility with the Master Serial mode.

This document discusses the Atmel AT40K, AT40KAL and AT94KAL applications as well as Xilinx applications.

# 5. Control of Configuration

Most connections between the FPGA device and the AT17LV Serial EEPROM are simple and self-explanatory.

- The DATA output of the AT17LV configurator drives DIN of the FPGA devices.

- The master FPGA CCLK output drives the CLK input of the AT17LV configurator.

- The  $\overline{\text{CEO}}$  output of any AT17LV configurator drives the  $\overline{\text{CE}}$  input of the next configurator in a cascaded chain of EEPROMs.

- SER EN must be connected to V<sub>CC</sub> (except during ISP).

- The READY<sup>(1)</sup> pin is available as an open-collector indicator of the device's reset status; it is driven Low while the device is in its power-on reset cycle and released (tri-stated) when the cycle is complete.

Note: 1. This pin is not available for the AT17LV65 (NRND), AT17LV128 (NRND), and AT17LV256.

# 6. Cascading Serial Configuration EEPROMs

For multiple FPGAs configured as a daisy-chain, or for FPGAs requiring larger configuration memories, cascaded configurators provide additional memory.

After the last bit from the first configurator is read, the clock signal to the configurator asserts its  $\overline{\text{CEO}}$  output Low and disables its DATA line driver. The second configurator recognizes the Low level on its  $\overline{\text{CE}}$  input and enables its DATA output.

After configuration is complete, the address counters of all cascaded configurators are reset if the RESET/OE on each configurator is driven to its active (Low) level.

If the address counters are not to be reset upon completion, then the  $\overline{\text{RESET}}/\text{OE}$  input can be tied to its inactive (High) level.

The AT17LV65 (NRND) devices do not have the CEO feature to perform cascaded configurations.

# 7. AT17LV Reset Polarity

The AT17LV configurator allows the user to program the reset polarity as either RESET/OE or RESET/OE. This feature is supported by industry-standard programmer algorithms.

# 8. Programming Mode

The programming mode is entered by bringing  $\overline{SER\_EN}$  Low. In this mode the chip can be programmed by the 2-wire serial bus. The programming is done at  $V_{CC}$  supply only. Programming super voltages are generated inside the chip.

# 9. Standby Mode

The AT17LV configurators enter a low-power standby mode whenever  $\overline{\text{CE}}$  is asserted High. In this mode, the AT17LV65 (NRND), AT17LV128 (NRND), or the AT17LV256 configurator consumes less than 50 $\mu$ A of current at 3.3V (100 $\mu$ A for the AT17LV512/010 and 200 $\mu$ A for the AT17LV002/040). The output remains in a high-impedance state regardless of the state of the  $\overline{\text{OE}}$  input.

# 10. Electrical Specifications

## 10.1 Absolute Maximum Ratings\*

| Operating Temperature                                                  |

|------------------------------------------------------------------------|

| Storage Temperature                                                    |

| Voltage on Any Pin with Respect to Ground0.1V to V <sub>CC</sub> +0.5V |

| Supply Voltage (V <sub>CC</sub> )0.5V to +7.0V                         |

| Maximum Soldering Temp. (10s @ 1/16 in.) 260°C                         |

| ESD (R <sub>ZAP</sub> = 1.5K, C <sub>ZAP</sub> = 100pF)                |

|                                                                        |

\*Notice: Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those listed under operating conditions is not implied. Exposure to Absolute Maximum Rating conditions for extended periods of time may affect device reliability.

## 10.2 Operating Conditions

Table 10-1. Operating Conditions

|                 |             |                                               | 3.  | 3V  | 5.0V |     |       |

|-----------------|-------------|-----------------------------------------------|-----|-----|------|-----|-------|

| Symbol          | Description |                                               | Min | Max | Min  | Max | Units |

| V <sub>CC</sub> | Industrial  | Supply voltage relative to GND -40°C to +85°C | 3.0 | 3.6 | 4.5  | 5.5 | V     |

## 10.3 DC Characteristics

Table 10-2. DC Characteristics for  $V_{CC} = 3.3V \pm 10\%$

|                  |                                                                            | AT17LV65 | AT17LV65/128/256 <sup>(1)</sup> |     | /512/010        | AT17LV002/40 |                 |       |

|------------------|----------------------------------------------------------------------------|----------|---------------------------------|-----|-----------------|--------------|-----------------|-------|

| Symbol           | Description                                                                | Min      | Max                             | Min | Max             | Min          | Max             | Units |

| V <sub>IH</sub>  | High-level Input Voltage                                                   | 2.0      | V <sub>CC</sub>                 | 2.0 | V <sub>CC</sub> | 2.0          | V <sub>CC</sub> | V     |

| V <sub>IL</sub>  | Low-level Input Voltage                                                    | 0        | 0.8                             | 0   | 0.8             | 0            | 0.8             | V     |

| V <sub>OH</sub>  | High-level Output Voltage (I <sub>OH</sub> = -2mA)                         | 2.4      |                                 | 2.4 |                 | 2.4          |                 | V     |

| V <sub>OL</sub>  | Low-level Output Voltage (I <sub>OL</sub> = +3mA)                          |          | 0.4                             |     | 0.4             |              | 0.4             | V     |

| I <sub>CCA</sub> | Supply Current, Active Mode                                                |          | 5                               |     | 5               |              | 5               | mA    |

| IL               | Input or Output Leakage Current (V <sub>IN</sub> = V <sub>CC</sub> or GND) | -10      | 10                              | -10 | 10              | -10          | 10              | μA    |

| I <sub>ccs</sub> | Supply Current, Standby Mode                                               |          | 100                             |     | 100             |              | 150             | μA    |

Note: 1. The AT17LV65 and AT17LV128 are not recommended for new designs.

Table 10-3. DC Characteristics for  $V_{CC} = 5.0V \pm 10\%$

|                  |                                                                    | AT17LV65/128/256 <sup>(1)</sup> |                 | AT17LV512/010 |                 | AT17LV002/040 |                 |       |

|------------------|--------------------------------------------------------------------|---------------------------------|-----------------|---------------|-----------------|---------------|-----------------|-------|

| Symbol           | Description                                                        | Min                             | Max             | Min           | Max             | Min           | Max             | Units |

| V <sub>IH</sub>  | High-level Input Voltage                                           | 2.0                             | V <sub>CC</sub> | 2.0           | V <sub>CC</sub> | 2.0           | V <sub>CC</sub> | V     |

| V <sub>IL</sub>  | Low-level Input Voltage                                            | 0                               | 0.8             | 0             | 0.8             | 0             | 0.8             | V     |

| V <sub>OH</sub>  | High-level Output Voltage (I <sub>OH</sub> = -2mA)                 | 3.60                            |                 | 3.76          |                 | 3.76          |                 | V     |

| V <sub>OL</sub>  | Low-level Output Voltage (I <sub>OL</sub> = +3mA)                  |                                 | 0.37            |               | 0.37            |               | 0.37            | V     |

| I <sub>CCA</sub> | Supply Current, Active Mode                                        |                                 | 10              |               | 10              |               | 10              | mA    |

| IL               | Input or Output Leakage Current $(V_{IN} = V_{CC} \text{ or GND})$ | -10                             | 10              | -10           | 10              | -10           | 10              | μA    |

| I <sub>CCS</sub> | Supply Current, Standby Mode                                       |                                 | 150             |               | 200             |               | 350             | μA    |

Note: 1. The AT17LV65 and AT17LV128 are not recommended for new designs.

## 10.4 AC Characteristics

Table 10-4. AC Characteristics for  $V_{CC} = 3.3V \pm 10\%$

|                                 |                                                      | AT17LV65/128/256 <sup>(3)</sup> |     | AT17LV512 | /010/002/040 |       |

|---------------------------------|------------------------------------------------------|---------------------------------|-----|-----------|--------------|-------|

| Symbol                          | Description                                          | Min                             | Max | Min       | Max          | Units |

| T <sub>OE</sub> <sup>(1)</sup>  | OE to Data Delay                                     |                                 | 55  |           | 55           | ns    |

| T <sub>CE</sub> <sup>(1)</sup>  | CE to Data Delay                                     |                                 | 60  |           | 60           | ns    |

| T <sub>CAC</sub> <sup>(1)</sup> | CLK to Data Delay                                    |                                 | 80  |           | 60           | ns    |

| T <sub>OH</sub>                 | Data Hold from $\overline{\text{CE}}$ , OE, or CLK   | 0                               |     | 0         |              | ns    |

| T <sub>DF</sub> <sup>(2)</sup>  | CE or OE to Data Float Delay                         |                                 | 55  |           | 50           | ns    |

| T <sub>LC</sub>                 | CLK Low Time                                         | 25                              |     | 25        |              | ns    |

| T <sub>HC</sub>                 | CLK High Time                                        | 25                              |     | 25        |              | ns    |

| T <sub>SCE</sub>                | CE Setup Time to CLK (to guarantee proper counting)  | 60                              |     | 35        |              | ns    |

| T <sub>HCE</sub>                | CE Hold Time from CLK (to guarantee proper counting) | 0                               |     | 0         |              | ns    |

| T <sub>HOE</sub>                | OE High Time (guarantees counter is reset)           | 25                              |     | 25        |              | ns    |

| F <sub>MAX</sub>                | Maximum Clock Frequency                              |                                 | 10  |           | 10           | MHz   |

Notes: 1. AC test lead = 50pF.

- 2. Float delays are measured with 5pF AC loads. Transition is measured  $\pm$  200mV from steady-state active levels.

- 3. The AT17LV65 and AT17LV128 are not recommended for new designs.

Table 10-5. AC Characteristics when Cascading for  $V_{CC} = 3.3V \pm 10\%$

|                                 |                         | AT17LV65/128/256 <sup>(3)</sup> |     | AT17LV512/010/002/040 |     |       |

|---------------------------------|-------------------------|---------------------------------|-----|-----------------------|-----|-------|

| Symbol                          | Description             | Min                             | Max | Min                   | Max | Units |

| T <sub>CDF</sub> <sup>(2)</sup> | CLK to Data Float Delay |                                 | 60  |                       | 50  | ns    |

| T <sub>OCK</sub> <sup>(1)</sup> | CLK to CEO Delay        |                                 | 60  |                       | 55  | ns    |

| T <sub>OCE</sub> <sup>(1)</sup> | CE to CEO Delay         |                                 | 60  |                       | 40  | ns    |

| T <sub>OOE</sub> <sup>(1)</sup> | RESET/OE to CEO Delay   |                                 | 45  |                       | 35  | ns    |

| F <sub>MAX</sub>                | Maximum Clock Frequency |                                 | 8   |                       | 10  | MHz   |

Notes: 1. AC test lead = 50pF.

- 2. Float delays are measured with 5pF AC loads. Transition is measured ± 200mV from steady-state active levels.

- 3. The AT17LV65 and AT17LV128 are not recommended for new designs.

Table 10-6. AC Characteristics for  $V_{CC} = 5V \pm 10\%$

|                                 |                                                      | AT17LV65/128/256 <sup>(3)</sup> AT17LV512/010/002/040 |      | /010/002/040 |     |       |

|---------------------------------|------------------------------------------------------|-------------------------------------------------------|------|--------------|-----|-------|

| Symbol                          | Description                                          | Min                                                   | Max  | Min          | Max | Units |

| T <sub>OE</sub> <sup>(1)</sup>  | OE to Data Delay                                     |                                                       | 35   |              | 35  | ns    |

| T <sub>CE</sub> <sup>(1)</sup>  | CE to Data Delay                                     |                                                       | 45   |              | 45  | ns    |

| T <sub>CAC</sub> <sup>(1)</sup> | CLK to Data Delay                                    |                                                       | 55   |              | 50  | ns    |

| T <sub>OH</sub>                 | Data Hold from $\overline{\text{CE}}$ , OE, or CLK   | 0                                                     |      | 0            |     | ns    |

| T <sub>DF</sub> <sup>(2)</sup>  | CE or OE to Data Float Delay                         |                                                       | 50   |              | 50  | ns    |

| T <sub>LC</sub>                 | CLK Low Time                                         | 20                                                    |      | 20           |     | ns    |

| T <sub>HC</sub>                 | CLK High Time                                        | 20                                                    |      | 20           |     | ns    |

| T <sub>SCE</sub>                | CE Setup Time to CLK (To Guarantee Proper Counting)  | 40                                                    |      | 25           |     | ns    |

| T <sub>HCE</sub>                | CE Hold Time from CLK (To Guarantee Proper Counting) | 0                                                     |      | 0            |     | ns    |

| T <sub>HOE</sub>                | OE High Time<br>(Guarantees Counter is Reset)        | 20                                                    |      | 20           |     | ns    |

| F <sub>MAX</sub>                | Maximum Clock Frequency                              |                                                       | 12.5 |              | 15  | MHz   |

Notes: 1. AC test lead = 50pF.

- 2. Float delays are measured with 5pF AC loads. Transition is measured  $\pm$  200mV from steady-state active levels.

- 3. The AT17LV65 and AT17LV128 are not recommended for new designs.

Table 10-7. AC Characteristics When Cascading for  $V_{CC} = 5V \pm 10\%$

|                                 |                         | AT17LV65/128/256 <sup>(3)</sup> AT17 |     | AT17LV512 | 7LV512/010/002/040 |       |  |

|---------------------------------|-------------------------|--------------------------------------|-----|-----------|--------------------|-------|--|

| Symbol                          | Description             | Min                                  | Max | Min       | Max                | Units |  |

| T <sub>CDF</sub> <sup>(2)</sup> | CLK to Data Float Delay |                                      | 50  |           | 50                 | ns    |  |

| T <sub>OCK</sub> <sup>(1)</sup> | CLK to CEO Delay        |                                      | 40  |           | 40                 | ns    |  |

| T <sub>OCE</sub> <sup>(1)</sup> | CE to CEO Delay         |                                      | 35  |           | 35                 | ns    |  |

| T <sub>OOE</sub> <sup>(1)</sup> | RESET/OE to CEO Delay   |                                      | 35  |           | 30                 | ns    |  |

| F <sub>MAX</sub>                | Maximum Clock Frequency |                                      | 10  |           | 12.5               | MHz   |  |

Notes: 1. AC test lead = 50pF.

- 2. Float delays are measured with 5pF AC loads. Transition is measured ± 200mV from steady-state active levels.

- 3. The AT17LV65 and AT17LV128 are not recommended for new designs.

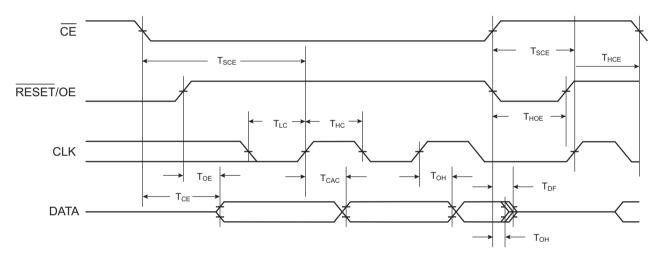

Figure 10-1. AC Waveforms

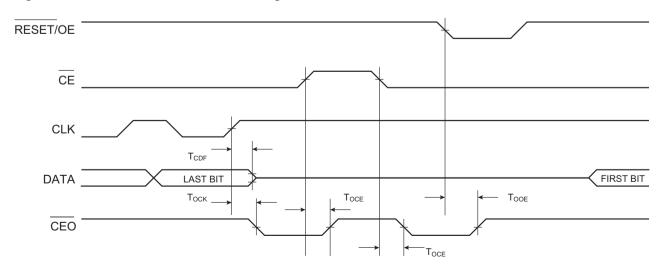

Figure 10-2. AC Waveforms when Cascading

## 10.5 Thermal Resistance Coefficients

Table 10-8. Thermal Resistance Coefficients

| Packag | е Туре               |                                       | AT17LV65/128/256 <sup>(2)</sup> | AT17LV512/010 | AT17LV002    | AT17LV040 |

|--------|----------------------|---------------------------------------|---------------------------------|---------------|--------------|-----------|

| 8CN4   | Leadless Array       | θ <sub>JC</sub> [°C/W]                | 45                              | 45            | 45           | _         |

| OCINA  | Package (LAP)        | θ <sub>JA</sub> [°C/W] <sup>(1)</sup> | 115.71                          | 135.71        | 159.60       | _         |

| 8P3    | Plastic Dual Inline  | θ <sub>JC</sub> [°C/W]                | 37                              | 37            | _            | _         |

| 0.5    | Package (PDIP)       | θ <sub>JA</sub> [°C/W] <sup>(1)</sup> | 107                             | 107           | <del>_</del> | _         |

| 8S1    | Plastic Gull Wing    | θ <sub>JC</sub> [°C/W]                | 45                              | _             | <del>_</del> | _         |

| 001    | Small Outline (SOIC) | θ <sub>JA</sub> [°C/W] <sup>(1)</sup> | 150                             | _             | <del>_</del> | _         |

| 20J    | Plastic Leaded Chip  | θ <sub>JC</sub> [°C/W]                | 35                              | 35            | 35           | _         |

| 200    | Carrier (PLCC)       | θ <sub>JA</sub> [°C/W] <sup>(1)</sup> | 90                              | 90            | 90           | _         |

| 20S2   | Plastic Gull Wing    | θ <sub>JC</sub> [°C/W]                |                                 |               |              | _         |

| 2002   | Small Outline (SOIC) | θ <sub>JA</sub> [°C/W] <sup>(1)</sup> |                                 |               |              | _         |

| 44A    | Thin Plastic Quad    | θ <sub>JC</sub> [°C/W]                | _                               | _             | 17           | 17        |

| 44/1   | Flat Package (TQFP)  | θ <sub>JA</sub> [°C/W] <sup>(1)</sup> | _                               | _             | 62           | 62        |

Notes: 1. Airflow = 0ft/min.

2. The AT17LV65 and AT17LV128 are not recommended for new designs.

#### 11. **Ordering Information**

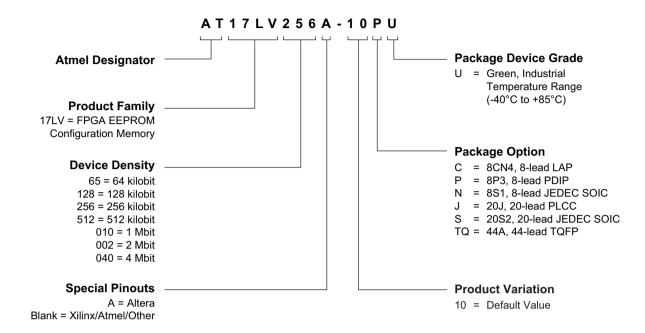

#### 11.1 **Ordering Code Detail**

# 11.2 Ordering Information

| Memory Size | Atmel Ordering Code | Lead Finish                        | Package | Voltage      | Operation Range               |  |

|-------------|---------------------|------------------------------------|---------|--------------|-------------------------------|--|

|             | AT17LV256-10CU      | CuNiAu<br>(Lead-free/Halogen-free) | 8CN4    |              | Industrial<br>(-40°C to 85°C) |  |

|             | AT17LV256-10JU      |                                    | 20J     | 3.0V to 5.5V |                               |  |

| 256-Kbit    | AT17LV256-10NU      | Sn                                 | 8S1     |              |                               |  |

|             | AT17LV256-10PU      | (Lead-free/Halogen-free)           | 8P3     |              |                               |  |

|             | AT17LV256-10SU      |                                    | 20S2    |              |                               |  |

|             |                     |                                    |         |              |                               |  |

| 512-Kbit    | AT17LV512-10CU      | CuNiAu<br>(Lead-free/Halogen-free) | 8CN4    | 3.0V to 5.5V | Industrial                    |  |

| 312-Kbit    | AT17LV512-10JU      | Sn<br>(Lead-free/Halogen-free)     | 20J     |              | (-40°C to 85°C)               |  |

|             |                     |                                    |         |              |                               |  |

|             | AT17LV010-10CU      | CuNiAu<br>(Lead-free/Halogen-free) | 8CN4    |              | Industrial<br>(-40°C to 85°C) |  |

| 1-Mbit      | AT17LV010-10JU      | Sn                                 | 20J     | 3.0V to 5.5V |                               |  |

|             | AT17LV010-10PU      | (Lead-free/Halogen-free)           | 8P3     |              |                               |  |

|             |                     |                                    |         | '            |                               |  |

|             | AT17LV002-10CU      | CuNiAu<br>(Lead-free/Halogen-free) | 8CN4    |              | Industrial<br>(-40°C to 85°C) |  |

| 2-Mbit      | AT17LV002-10JU      |                                    | 20J     | 3.0V to 5.5V |                               |  |

|             | AT17LV002-10SU      | Sn<br>(Lead-free/Halogen-free)     | 20S2    |              |                               |  |

|             | AT17LV002-10TQU     |                                    | 44A     |              |                               |  |

|             |                     |                                    |         |              |                               |  |

| 4-Mbit      | AT17LV040-10TQU     | Sn<br>(Lead-free/Halogen-free)     | 44A     | 3.0V to 5.5V | Industrial<br>(-40°C to 85°C) |  |

|              | Package Type                                                                                     |  |  |

|--------------|--------------------------------------------------------------------------------------------------|--|--|

| 8CN4         | 8-lead, 6mm x 6mm x 1mm, Leadless Array Package (LAP) (Pin-compatible with 8-lead SOIC Packages) |  |  |

| 8P3          | 8-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)                                          |  |  |

| 8 <b>S</b> 1 | 8-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)                                |  |  |

| 20J          | 20-lead, Plastic J-leaded Chip Carrier (PLCC)                                                    |  |  |

| 20S2         | 20-lead, 0.300" Wide, Plastic Gull Wing Small Outline (SOIC)                                     |  |  |

| 44A          | 44-lead, Thin (1.0mm) Plastic Quad Flat Package Carrier (TQFP)                                   |  |  |

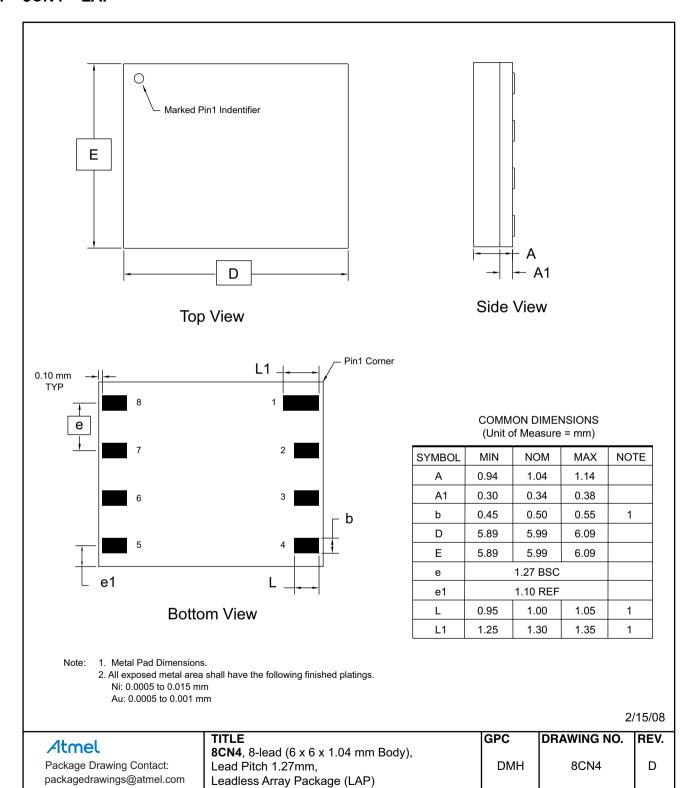

# 12. Packaging Information

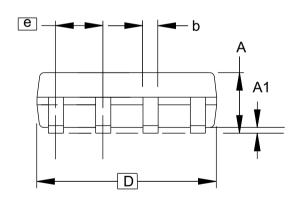

## 12.1 8CN4 - LAP

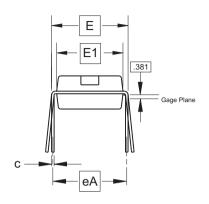

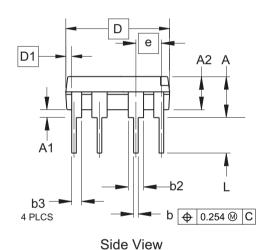

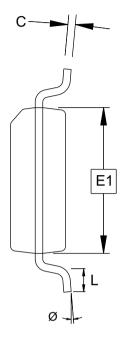

## 12.2 8P3 - PDIP

Top View

**End View**

COMMON DIMENSIONS (Unit of Measure = mm)

|        | •         |       |        |      |

|--------|-----------|-------|--------|------|

| SYMBOL | MIN       | NOM   | MAX    | NOTE |

| А      | -         | -     | 5.334  | 2    |

| A1     | 0.381     | -     | -      |      |

| A2     | 2.921     | 3.302 | 4.953  |      |

| b      | 0.356     | 0.457 | 0.559  | 5    |

| b2     | 1.143     | 1.524 | 1.778  | 6    |

| b3     | 0.762     | 0.991 | 1.143  | 6    |

| С      | 0.203     | 0.254 | 0.356  |      |

| D      | 9.017     | 9.271 | 10.160 | 3    |

| D1     | 0.127     | 0.000 | 0.000  | 3    |

| E      | 7.620     | 7.874 | 8.255  | 4    |

| E1     | 6.096     | 6.350 | 7.112  | 3    |

| е      | 2.540 BSC |       |        |      |

| eA     | 7.620 BSC |       | 4      |      |

| L      | 2.921     | 3.302 | 3.810  | 2    |

- This drawing is for general information only; refer to JEDEC Drawing MS-001, Variation BA for additional information.

Dimensions A and L are measured with the package seated in JEDEC seating plane Gauge GS-3.

D, D1 and E1 dimensions do not include mold Flash or protrusions. Mold Flash or protrusions shall not exceed 0.010 inch.

- 4. E and eA measured with the leads constrained to be perpendicular to datum.

5. Pointed or rounded lead tips are preferred to ease insertion.

6. b2 and b3 maximum dimensions do not include Dambar protrusions. Dambar protrusions shall not exceed 0.010 (0.25 mm).

07/31/14

| ∕Itmel                    | TITLE                                                                 | GPC | DRAWING NO. | REV. |

|---------------------------|-----------------------------------------------------------------------|-----|-------------|------|

| Package Drawing Contact:  | 8P3, 8-lead, 0.300" Wide Body, Plastic Dual<br>In-line Package (PDIP) | PTC | 8P3         | Е    |

| packagedrawings@atmel.com | in-line r ackage (r Dir )                                             |     |             |      |

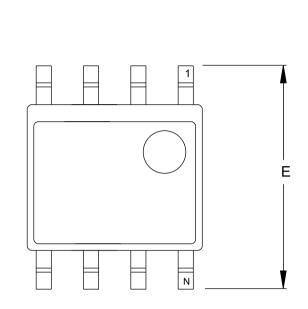

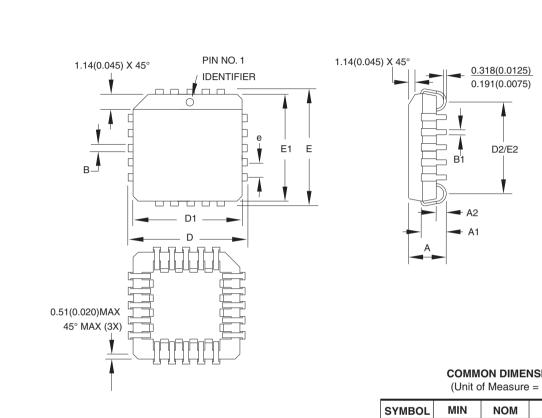

## 12.3 8S1 - SOIC

**TOP VIEW**

## SIDE VIEW

Notes: This drawing is for general information only. Refer to JEDEC Drawing MS-012, Variation AA for proper dimensions, tolerances, datums, etc.

# **END VIEW**

**COMMON DIMENSIONS** (Unit of Measure = mm)

| SYMBOL | MIN      | NOM | MAX  | NOTE |

|--------|----------|-----|------|------|

| Α      | 1.35     | _   | 1.75 |      |

| A1     | 0.10     | _   | 0.25 |      |

| b      | 0.31     | _   | 0.51 |      |

| С      | 0.17     | _   | 0.25 |      |

| D      | 4.80     | _   | 5.05 |      |

| E1     | 3.81     | _   | 3.99 |      |

| Е      | 5.79     | _   | 6.20 |      |

| е      | 1.27 BSC |     |      |      |

| L      | 0.40     | _   | 1.27 |      |

| Ø      | 0°       | _   | 8°   |      |

6/22/11

REV.

G

**Atmel**

Package Drawing Contact: packagedrawings@atmel.com **TITLE**

8S1, 8-lead (0.150" Wide Body), Plastic Gull Wing Small Outline (JEDEC SOIC)

**GPC** SWB

DRAWING NO. 8S1

## 12.4 20J - PLCC

Notes: 1. This package conforms to JEDEC reference MS-018, Variation AA

- 2. Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is .010"(0.254mm) per side. Dimension D1 and E1 include mold mismatch and are measured at the extreme material condition at the upper or lower parting line.

- 3. Lead coplanarity is 0.004" (0.102mm) maximum

| COMMON DIMENSIONS      |  |  |

|------------------------|--|--|

| (Unit of Measure = mm) |  |  |

|        | (Offic of Measure = Illill) |           |        |        |

|--------|-----------------------------|-----------|--------|--------|

| SYMBOL | MIN                         | NOM       | MAX    | NOTE   |

| Α      | 4.191                       | _         | 4.572  |        |

| A1     | 2.286                       | -         | 3.048  |        |

| A2     | 0.508                       | _         | _      |        |

| D      | 9.779                       | -         | 10.033 |        |

| D1     | 8.890                       | -         | 9.042  | Note 2 |

| Е      | 9.779                       |           | 10.033 |        |

| E1     | 8.890                       | _         | 9.042  | Note 2 |

| D2/E2  | 7.366                       | -         | 8.382  |        |

| В      | 0.660                       | _         | 0.813  |        |

| B1     | 0.330                       | _         | 0.533  |        |

| е      |                             | 1.270 TYF | )      |        |

10/04/01

**Atmel**

Package Drawing Contact: packagedrawings@atmel.com TITLE 20J, 20-lead, Plastic J-leaded Chip Carrier (PLCC) DRAWING NO. REV. 20J В

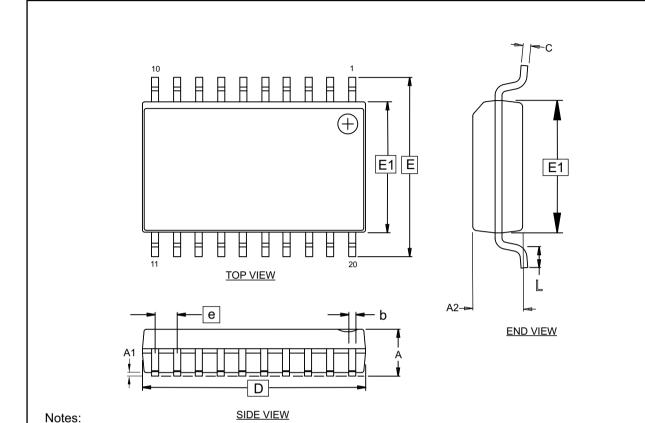

### 12.5 20S2 - SOIC

- This drawing is for general information only. Refer to JEDEC Drawing MS-013, Variation AC, for proper dimensions, tolerances, datums, etc.

- Dimension D does not include mold flash, protrusions or gate burrs. Mold flash, protrustions or gate burrs shall not exceed 0.15 mm per end. Diminsion E1 does not include interlead flash or protursion. Interlead flash or protrusion shall not exceed 0.25 mm per side.

- 3. The package top may be smaller than the package bottom. Dimensions D and E1 are determinded at the outermost extremes of the plastic body exclusive of mold flash, the bar burrs, gate burrs and interlead flash, but including any mismatch between the top and bottom of the plastic body.

- 4. The dimensions apply to the flat section of the lead between 0.10 to 0.25 mm from the lead tip.

- Dimension 'b' does not include the dambar protrusion. Allowable dambar protrusion shall be 0.10 mm total in excess of the 'b' dimension at maximum material condition. The dambar may not be located on the lower radius of the foot.

- 'A1' is defined as the vertical distance from the seating plane to the lowest point on the package body excluding the lid or thermal enhancement on the cavity down package configuration.

## COMMON DIMENSIONS (Unit of Measure = mm)

| (      |      |          |      |      |

|--------|------|----------|------|------|

| SYMBOL | MIN  | NOM      | MAX  | NOTE |

| D      | ,    | 12.80 BS | SC . | 2,3  |

| E1     |      | 7.50 BS  | С    | 2,3  |

| E      | ,    | 10.30 BS | SC   |      |

| Α      | ı    | -        | 2.65 |      |

| A1     | 0.10 | -        | 0.30 | 6    |

| A2     | 2.05 | -        | -    |      |

| е      |      | 1.27 BS  | С    |      |

| b      | 0.31 | -        | 0.51 | 4,5  |

| L      | 0.40 | -        | 1.27 |      |

| С      | 0.20 | -        | 0.33 | 4    |

7/1/14

| ∕Itmel                                                | TITLE                                                                                   | GPC | DRAWING NO. | REV. |

|-------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-------------|------|

| Package Drawing Contact:<br>packagedrawings@atmel.com | <b>20S2</b> , 20-lead, 0.300" Wide Body, Plastic Gull Wing Small Outline Package (SOIC) | SRJ | 20S2        | Е    |

*A*tmel

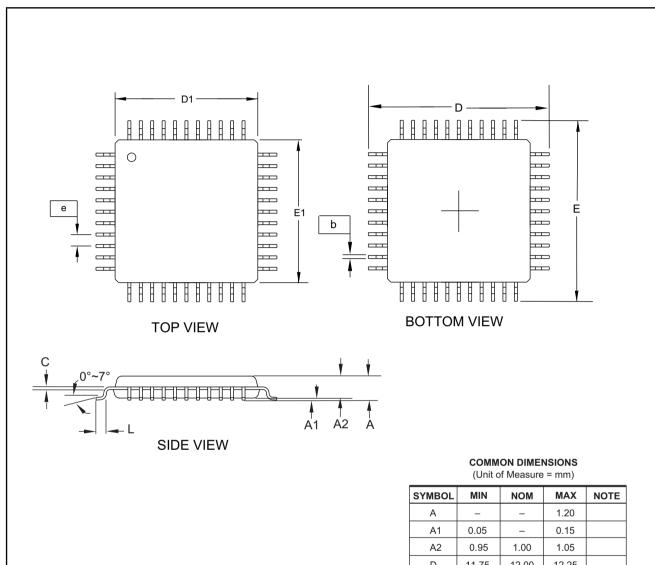

## 12.6 44A - TQFP

Notes:

- This package conforms to JEDEC reference MS-026, Variation ACB.

- Dimensions D1 and E1 do not include mold protrusion.

Allowable protrusion is 0.25 mm per side. Dimensions D1 and E1 are maximum plastic body size dimensions including mold mismatch.

- 3. Lead coplanarity is 0.10 mm maximum.

D 11.75 12.00 12.25 D1 9.90 10.00 10.10 Note 2 12.00 12.25 Е 11.75 E1 9.90 10.00 10.10 Note 2 В 0.30 0.45 С 0.09 0.20 0.45 0.75 L 0.80 TYP

| Atmel                                              | TITLE                                                                                                                 | GPC | DRAWING NO. | REV. |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----|-------------|------|

| Package Drawing Contact: packagedrawings@atmel.com | <b>44A</b> , 44-lead 10.0 x 10.0x1.0 mm Body, 0.80 mm<br>Lead Pitch, Thin Profile Plastic Quad Flat<br>Package (TQFP) | AIX | 44A         | D    |

1/10/13

# 13. Revision History

| Rev. No. | Date    | History                                                                                                                                                      |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |         | The AT17LV65 and AT17LV128 are not recommended for new designs.                                                                                              |

| 2321J    | 10/2014 | Removed the commercial options.                                                                                                                              |

| 20210    |         | Updated the 8P3, 8S1, 20S2, and 44A package outline drawings, ordering code details, ordering code table, document's template, Atmel logos, disclaimer page. |

| 23211    | 02/2008 | Removed -10SC, 10SI, -10TQC, -10TQI, -10BJC and -10BJI devices from ordering information.                                                                    |

| 2321H    | 03/2006 | Added last-time buy for AT17LVXXX-10CC and AT17LVXXX-10Cl.                                                                                                   |

**Atmel Corporation**

1600 Technology Drive, San Jose, CA 95110 USA

T: (+1)(408) 441.0311

F: (+1)(408) 436.4200

www.atmel.com

© 2014 Atmel Corporation. / Rev.: Atmel-2321J-FPGA-AT17LV65-128-256-512-010-002-040-Datasheet\_102014.

Atmel®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.

DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death ("Safety-Critical Applications") without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems. Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.