**Data Sheet**

# ADT75

# **TABLE OF CONTENTS**

| Features                                                          | Functional Description                | 10 |

|-------------------------------------------------------------------|---------------------------------------|----|

| Applications1                                                     | Temperature Data Format               | 11 |

| Product Highlights                                                | One-Shot Mode                         | 12 |

| Functional Block Diagram                                          | Fault Queue                           | 12 |

| Revision History                                                  | Registers                             | 13 |

| General Description                                               | Serial Interface                      | 16 |

| Specifications                                                    | Writing Data                          | 17 |

| A Grade4                                                          | Reading Data                          | 18 |

| B Grade5                                                          | OS/Alert Output OverTemperature Modes | 19 |

| Timing Specifications and Diagram6                                | SMBus Alert                           | 20 |

| Absolute Maximum Ratings                                          | Applications Information              | 21 |

| ESD Caution                                                       | Thermal Response Time                 | 21 |

| Pin Configuration and Function Descriptions8                      | Self-Heating Effects                  | 21 |

| Typical Performance Characteristics                               | Supply Decoupling                     | 21 |

| Theory of Operation                                               | Temperature Monitoring                | 22 |

| Circuit Information10                                             | Outline Dimensions                    | 23 |

| Converter Details                                                 | Ordering Guide                        | 24 |

| REVISION HISTORY                                                  |                                       |    |

| 8/12—Rev. A to Rev. B                                             | 9/10—Rev. 0 to Rev. A                 |    |

| Changed 3 V to 2.7 V, Features Section and 3 V to 2.7 V,          | Changes to Figure 1                   |    |

| Product Highlights Section                                        | Updated Outline Dimensions            |    |

| Changed 3 V to 2.7 V, General Description Section                 | Changes to Ordering Guide             | 23 |

| Changed 3 V to 2.7 V, A Grade Section and 3 V to 2.7 V, Table 1 4 | 10/05—Revision 0: Initial Version     |    |

| Changed 3 V to 2.7 V, B Grade Section and 3 V to 2.7 V, Table 2 5 | 10/03 - ACVISION O. MINUM VCISION     |    |

| Changed 3 V to 2.7 V, Table 5                                     |                                       |    |

| Changes to Figure 7 and Figure 89                                 |                                       |    |

# **GENERAL DESCRIPTION**

The ADT75 is a complete temperature monitoring system in 8-lead MSOP and SOIC packages. It contains a band gap temperature sensor and a 12-bit analog-to-digital converter (ADC) to monitor and digitize the temperature to a resolution of 0.0625°C. The ADT75 is pin and register compatible with the LM75 and AD7416.

The ADT75 is guaranteed to operate at supply voltages from 2.7 V to 5.5 V. Operating at 3.3 V, the average supply current is typically 200  $\mu A.$

The ADT75 offers a shutdown mode that powers down the device, and this mode gives a shutdown current of typically 3  $\mu$ A. The ADT75 is rated for operation over the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range.

The A0, A1, and A2 pins are available for address selection. The OS/ALERT pin is an open-drain output that becomes active when temperature exceeds a programmable limit. The OS/ALERT pin can operate in either comparator or interrupt mode.

# **SPECIFICATIONS**

## **A GRADE**

$T_A = T_{MIN}$  to  $T_{MAX}$ ,  $V_{DD} = 2.7$  V to 5.5 V. All specifications for  $-55^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.

Table 1.

| Parameter                                               | Min                 | Тур    | Max                 | Unit | Test Conditions/Comments                                                      |

|---------------------------------------------------------|---------------------|--------|---------------------|------|-------------------------------------------------------------------------------|

| TEMPERATURE SENSOR AND ADC                              |                     |        |                     |      |                                                                               |

| Accuracy at $V_{DD} = 2.7 \text{ V}$ to 5.5 V           |                     |        | ±2                  | °C   | $T_A = -25^{\circ}\text{C to } +100^{\circ}\text{C}$                          |

|                                                         |                     |        | ±3                  | °C   | $T_A = -55^{\circ}C \text{ to } +100^{\circ}C$                                |

| Accuracy at $V_{DD} = 2.7 \text{ V}$ to $3.6 \text{ V}$ |                     |        | ±3                  | °C   | $T_A = 100^{\circ}\text{C to } 125^{\circ}\text{C}$                           |

| Accuracy at $V_{DD} = 4.5 \text{ V}$ to 5.5 V           |                     | ±2     |                     | °C   | $T_A = 100^{\circ}\text{C to } 125^{\circ}\text{C}$                           |

| ADC Resolution                                          |                     | 12     |                     | Bits |                                                                               |

| Temperature Resolution                                  |                     | 0.0625 |                     | °C   |                                                                               |

| Temperature Conversion Time                             |                     | 60     |                     | ms   |                                                                               |

| Update Rate                                             |                     | 100    |                     | ms   | Conversion started every 100 ms                                               |

| Long Term Drift                                         |                     | 0.08   |                     | °C   | Drift over 10 years, if part is operated at 55°C                              |

| Temperature Hysteresis                                  |                     | 0.03   |                     | °C   | Temperature cycle = 25°C to 125°C to 25°C                                     |

| OS/ALERT OUTPUT (OPEN DRAIN)                            |                     |        |                     |      |                                                                               |

| Output Low Voltage, V <sub>OI</sub>                     |                     |        | 0.4                 | V    | $I_{OL} = 3 \text{ mA}$                                                       |

| Pin Capacitance                                         |                     | 10     |                     | pF   |                                                                               |

| High Output Leakage Current, I <sub>OH</sub>            |                     | 0.1    | 5                   | μA   | OS/ALERT pin pulled up to 5.5 V                                               |

| R <sub>ON</sub> Resistance (Low Output)                 |                     | 15     |                     | Ω    | Supply and temperature dependent                                              |

| DIGITAL INPUTS                                          |                     |        |                     |      | 117                                                                           |

| Input Current                                           |                     |        | ±1                  | μΑ   | $V_{IN} = 0 V to V_{DD}$                                                      |

| Input Low Voltage, V <sub>II</sub>                      |                     |        | $0.3 \times V_{DD}$ | v    |                                                                               |

| Input High Voltage, V <sub>IH</sub>                     | $0.7 \times V_{DD}$ |        | 00                  | V    |                                                                               |

| SCL, SDA Glitch Rejection                               | 00                  |        | 50                  | ns   | Input filtering suppresses noise spikes of less than 50 ns                    |

| Pin Capacitance                                         | 3                   |        | 10                  | рF   |                                                                               |

| DIGITAL OUTPUT (OPEN DRAIN)                             |                     |        |                     | i i  |                                                                               |

| Output High Current, I <sub>OH</sub>                    |                     |        | 1                   | mA   | $V_{OH} = 5 V$                                                                |

| Output Low Voltage, V <sub>OL</sub>                     |                     |        | 0.4                 | V    | $I_{OL} = 3 \text{ mA}$                                                       |

| Output High Voltage, V <sub>OH</sub>                    | $0.7 \times V_{DD}$ |        |                     | V    | OL .                                                                          |

| Output Capacitance, C <sub>OUT</sub>                    | 3                   |        | 10                  | рF   |                                                                               |

| POWER REQUIREMENTS                                      |                     |        |                     | 1    |                                                                               |

| Supply Voltage                                          | 2.7                 |        | 5.5                 | V    |                                                                               |

| Supply Current at 3.3 V                                 |                     | 350    | 500                 | μΑ   | Peak current while converting and I <sup>2</sup> C interface inactive         |

| Supply Current at 5.0 V                                 |                     | 380    | 525                 | μΑ   | Peak current while converting and I <sup>2</sup> C interface inactive         |

| Average Current at 3.3 V                                |                     | 200    |                     | μΑ   | Part converting and I <sup>2</sup> C interface inactive                       |

| Average Current at 5.0 V                                |                     | 225    |                     | μΑ   | Part converting and I <sup>2</sup> C interface inactive                       |

| Shutdown Mode at 3.3 V                                  |                     | 3      | 8                   | μΑ   | Supply current in shutdown mode                                               |

| Shutdown Mode at 5.0 V                                  |                     | 5.5    | 12                  | μΑ   | Supply current in shutdown mode                                               |

| Average Power Dissipation                               |                     | 798.6  |                     | μW   | V <sub>DD</sub> = 3.3 V, normal mode at 25°C                                  |

| 1 SPS                                                   |                     | 78.6   |                     | μW   | Average power dissipated for $V_{DD} = 3.3 \text{ V}$ , shutdown mode at 25°C |

|                                                         |                     | 140    |                     | μW   | Average power dissipated for $V_{DD} = 5.0 \text{ V}$ , shutdown mode at 25°C |

## **B GRADE**

$T_A = T_{MIN}$  to  $T_{MAX}$ ,  $V_{DD} = 2.7$  V to 5.5 V. All specifications for  $-55^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.

Table 2.

| Parameter                                               | Min                 | Тур    | Max                 | Unit | Test Conditions/Comments                                                      |

|---------------------------------------------------------|---------------------|--------|---------------------|------|-------------------------------------------------------------------------------|

| TEMPERATURE SENSOR AND ADC                              |                     |        |                     |      |                                                                               |

| Accuracy at $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$  |                     |        | ±1                  | °C   | $T_A = 0$ °C to +70°C                                                         |

|                                                         |                     |        | ±2                  | °C   | $T_A = -25^{\circ}C \text{ to } +100^{\circ}C$                                |

|                                                         |                     |        | ±3                  | °C   | $T_A = -55^{\circ}C \text{ to } +100^{\circ}C$                                |

| Accuracy at $V_{DD} = 2.7 \text{ V}$ to $3.6 \text{ V}$ |                     |        | ±3                  | °C   | T <sub>A</sub> = 100°C to 125°C                                               |

| Accuracy at $V_{DD} = 4.5 \text{ V}$ to 5.5 V           |                     | ±2     |                     | °C   | $T_A = 100^{\circ}\text{C to } 125^{\circ}\text{C}$                           |

| ADC Resolution                                          |                     | 12     |                     | bits |                                                                               |

| Temperature Resolution                                  |                     | 0.0625 |                     | °C   |                                                                               |

| Temperature Conversion Time                             |                     | 60     |                     | ms   |                                                                               |

| Update Rate                                             |                     | 100    |                     | ms   | Conversion started every 100 ms                                               |

| Long Term Drift                                         |                     | 0.08   |                     | °C   | Drift over 10 years, if part is operated at 55°C                              |

| Temperature Hysteresis                                  |                     | 0.03   |                     | °C   | Temperature cycle = 25°C to 125°C to 25°C                                     |

| OS/ALERT OUTPUT (OPEN DRAIN)                            |                     |        |                     |      |                                                                               |

| Output Low Voltage, V <sub>ol</sub>                     |                     |        | 0.4                 | V    | $I_{OL} = 3 \text{ mA}$                                                       |

| Pin Capacitance                                         |                     | 10     |                     | рF   |                                                                               |

| High Output Leakage Current, I <sub>OH</sub>            |                     | 0.1    | 5                   | μΑ   | OS/ALERT pin pulled up to 5.5 V                                               |

| R <sub>ON</sub> Resistance (Low Output)                 |                     | 15     |                     | Ω    | Supply and temperature dependent                                              |

| DIGITAL INPUTS                                          |                     |        |                     |      |                                                                               |

| Input Current                                           |                     |        | ±1                  | μΑ   | $V_{IN} = 0 V \text{ to } V_{DD}$                                             |

| Input Low Voltage, V <sub>IL</sub>                      |                     |        | $0.3 \times V_{DD}$ | V    |                                                                               |

| Input High Voltage, V <sub>IH</sub>                     | $0.7 \times V_{DD}$ |        |                     | V    |                                                                               |

| SCL, SDA Glitch Rejection                               |                     |        | 50                  | ns   | Input filtering suppresses noise spikes of less than 50 ns                    |

| Pin Capacitance                                         | 3                   |        | 10                  | рF   |                                                                               |

| DIGITAL OUTPUT (OPEN DRAIN)                             |                     |        |                     |      |                                                                               |

| Output High Current, I <sub>OH</sub>                    |                     |        | 1                   | mA   | $V_{OH} = 5 V$                                                                |

| Output Low Voltage, V <sub>OL</sub>                     |                     |        | 0.4                 | V    | $I_{OL} = 3 \text{ mA}$                                                       |

| Output High Voltage, V <sub>OH</sub>                    | $0.7 \times V_{DD}$ |        |                     | V    |                                                                               |

| Output Capacitance, C <sub>OUT</sub>                    | 3                   |        | 10                  | рF   |                                                                               |

| POWER REQUIREMENTS                                      |                     |        |                     |      |                                                                               |

| Supply Voltage                                          | 2.7                 |        | 5.5                 | V    |                                                                               |

| Supply Current at 3.3 V                                 |                     | 350    | 500                 | μΑ   | Peak current while converting and I <sup>2</sup> C interface inactive         |

| Supply Current at 5.0 V                                 |                     | 380    | 525                 | μΑ   | Peak current while converting and I <sup>2</sup> C interface inactive         |

| Average Current at 3.3 V                                |                     | 200    |                     | μΑ   | Part converting and I <sup>2</sup> C interface inactive                       |

| Average Current at 5.0 V                                |                     | 225    |                     | μΑ   | Part converting and I <sup>2</sup> C interface inactive                       |

| Shutdown Mode at 3.3 V                                  |                     | 3      | 8                   | μΑ   | Supply current in shutdown mode                                               |

| Shutdown Mode at 5.0 V                                  |                     | 5.5    | 12                  | μΑ   | Supply current in shutdown mode                                               |

| Average Power Dissipation                               |                     | 798.6  |                     | μW   | V <sub>DD</sub> = 3.3 V, normal mode at 25°C                                  |

| 1 SPS                                                   |                     | 78.6   |                     | μW   | Average power dissipated for $V_{DD} = 3.3 \text{ V}$ , shutdown mode at 25°C |

|                                                         |                     | 140    |                     | μW   | Average power dissipated for $V_{DD} = 5.0 \text{ V}$ , shutdown mode at 25°C |

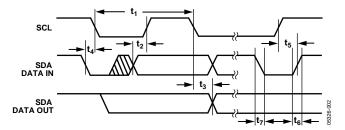

## **TIMING SPECIFICATIONS AND DIAGRAM**

Measure the SDA and SCL timing with the input filters turned on to meet the fast mode I<sup>2</sup>C specification. Switching off the input filters improves the transfer rate but has a negative effect on the EMC behavior of the part.

$T_{\rm A}$  =  $T_{\rm MIN}$  to  $T_{\rm MAX},\,V_{\rm DD}$  = 2.7 V to 5.5 V, unless otherwise noted.

Table 3.

| Parameter <sup>1</sup>                                          | Min | Тур | Max        | Unit | Test Conditions/Comments                     |

|-----------------------------------------------------------------|-----|-----|------------|------|----------------------------------------------|

| Serial Clock Period, t <sub>1</sub>                             | 2.5 |     |            | μs   | Fast mode I <sup>2</sup> C. See Figure 2     |

| Data In Setup Time to SCL High, t <sub>2</sub>                  | 50  |     |            | ns   | See Figure 2                                 |

| Data Out Stable After SCL Low, t <sub>3</sub>                   | 0   |     | $0.9^{2}$  | ns   | Fast mode I <sup>2</sup> C. See Figure 2     |

| Data Out Stable After SCL Low, t <sub>3</sub>                   | 0   |     | $3.45^{2}$ | μs   | Standard mode I <sup>2</sup> C. See Figure 2 |

| SDA Low Setup Time to SCL Low (Start Condition), t <sub>4</sub> | 50  |     |            | ns   | See Figure 2                                 |

| SDA High Hold Time After SCL High (Stop Condition), $t_5$       | 50  |     |            | ns   | See Figure 2                                 |

| SDA and SCL Rise Time, t <sub>6</sub>                           |     |     | 300        | ns   | Fast mode I <sup>2</sup> C. See Figure 2     |

| SDA and SCL Rise Time, t <sub>6</sub>                           |     |     | 1000       | ns   | Standard mode I <sup>2</sup> C. See Figure 2 |

| SDA and SCL Fall Time, t <sub>7</sub>                           |     |     | 300        | ns   | See Figure 2                                 |

| Capacitive Load for each Bus Line, C <sub>B</sub>               |     |     | 400        | рF   |                                              |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization; not production tested.

<sup>2</sup> This time has to be met only if the master does not stretch the low period of the SCL signal.

Figure 2. SMBus/I<sup>2</sup>C Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| 1 able 4.                                              |                                            |  |  |  |  |  |  |  |

|--------------------------------------------------------|--------------------------------------------|--|--|--|--|--|--|--|

| Parameter                                              | Rating                                     |  |  |  |  |  |  |  |

| V <sub>DD</sub> to GND                                 | -0.3 V to +7 V                             |  |  |  |  |  |  |  |

| SDA Input Voltage to GND                               | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |  |  |  |  |  |  |  |

| SDA Output Voltage to GND                              | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |  |  |  |  |  |  |  |

| SCL Input Voltage to GND                               | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |  |  |  |  |  |  |  |

| OS/ALERT Output Voltage to GND                         | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |  |  |  |  |  |  |  |

| Operating Temperature Range                            | −55°C to +150°C                            |  |  |  |  |  |  |  |

| Storage Temperature Range                              | −65°C to +160°C                            |  |  |  |  |  |  |  |

| Maximum Junction Temperature, T <sub>JMAX</sub>        | 150.7°C                                    |  |  |  |  |  |  |  |

| 8-Lead MSOP (RM-8)                                     |                                            |  |  |  |  |  |  |  |

| Power Dissipation 1, 2                                 | $W_{MAX} = (T_{JMAX} - T_{A})/\theta_{JA}$ |  |  |  |  |  |  |  |

| Thermal Impedance <sup>3</sup>                         |                                            |  |  |  |  |  |  |  |

| $\theta_{\text{JA}}$ , Junction-to-Ambient (Still Air) | 205.9°C/W                                  |  |  |  |  |  |  |  |

| $\theta_{JC}$ , Junction-to-Case                       | 43.74°C/W                                  |  |  |  |  |  |  |  |

| 8-Lead SOIC (R-8)                                      |                                            |  |  |  |  |  |  |  |

| Power Dissipation <sup>1, 2</sup>                      | $W_{MAX} = (T_{JMAX} - T_{A})/\theta_{JA}$ |  |  |  |  |  |  |  |

| Thermal Impedance <sup>3</sup>                         |                                            |  |  |  |  |  |  |  |

| $\theta_{\text{JA}}$ , Junction-to-Ambient (Still Air) | 157°C/W                                    |  |  |  |  |  |  |  |

| $\theta_{\text{JC}}$ , Junction-to-Case                | 56°C/W                                     |  |  |  |  |  |  |  |

| IR Reflow Soldering                                    |                                            |  |  |  |  |  |  |  |

| Peak Temperature                                       | 220°C (0°C/5°C)                            |  |  |  |  |  |  |  |

| Time at Peak Temperature                               | 10 sec to 20 sec                           |  |  |  |  |  |  |  |

| Ramp-Up Rate                                           | 3°C/sec maximum                            |  |  |  |  |  |  |  |

| Ramp-Down Rate                                         | −6°C/sec maximum                           |  |  |  |  |  |  |  |

| Time 25°C to Peak Temperature                          | 6 minutes maximum                          |  |  |  |  |  |  |  |

| IR Reflow Soldering (Pb-Free Package)                  |                                            |  |  |  |  |  |  |  |

| Peak Temperature                                       | 260°C (+0°C)                               |  |  |  |  |  |  |  |

| Time at Peak Temperature                               | 20 sec to 40 sec                           |  |  |  |  |  |  |  |

| Ramp-Up Rate                                           | 3°C/sec maximum                            |  |  |  |  |  |  |  |

| Ramp-Down Rate                                         | −6°C/sec maximum                           |  |  |  |  |  |  |  |

| Time 25°C to Peak Temperature                          | 8 minutes maximum                          |  |  |  |  |  |  |  |

|                                                        |                                            |  |  |  |  |  |  |  |

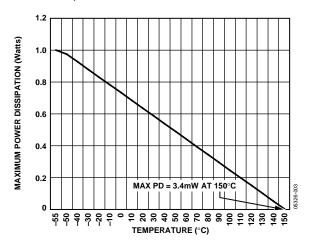

$<sup>^1</sup>$  Values relate to package being used on a standard 2-layer PCB. This gives a worst case  $\theta_{JA}$  and  $\theta_{JC}$ . Refer to Figure 3 for a plot of maximum power dissipation vs. ambient temperature ( $T_A$ ).

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Figure 3. MSOP Maximum Power Dissipation vs. Ambient Temperature

## **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$<sup>{}^{2}</sup>T_{A}$  = ambient temperature.

<sup>&</sup>lt;sup>3</sup> Junction-to-case resistance is applicable to components featuring a preferential flow direction, for example, components mounted on a heat sink. Junction-to-ambient resistance is more useful for air-cooled, PCB-mounted components.

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                                                                         |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SDA      | SMBus/l <sup>2</sup> C Serial Data Input/Output. Serial data that is loaded into and read from the ADT75 registers is provided on this pin. Open-drain configuration; needs a pull-up resistor.                     |

| 2       | SCL      | Serial Clock Input. This is the clock input for the serial port. The serial clock is used to clock in and clock out data to and from any register of the ADT75. Open-drain configuration; needs a pull-up resistor. |

| 3       | OS/ALERT | Over- and Undertemperature Indicator. Default power as an OS pin. Open-drain configuration; needs a pull-up resistor.                                                                                               |

| 4       | GND      | Analog and Digital Ground.                                                                                                                                                                                          |

| 5       | A2       | SMBus/I <sup>2</sup> C Serial Bus Address Selection Pin. Logic input. Can be set to GND or V <sub>DD</sub> .                                                                                                        |

| 6       | A1       | SMBus/I <sup>2</sup> C Serial Bus Address Selection Pin. Logic input. Can be set to GND or V <sub>DD</sub> .                                                                                                        |

| 7       | A0       | SMBus/I <sup>2</sup> C Serial Bus Address Selection Pin. Logic input. Can be set to GND or V <sub>DD</sub> .                                                                                                        |

| 8       | $V_{DD}$ | Positive Supply Voltage, 2.7 V to 5.5 V. Decouple the supply to ground.                                                                                                                                             |

# TYPICAL PERFORMANCE CHARACTERISTICS

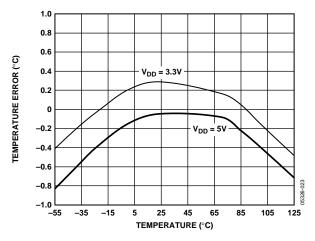

Figure 5. Temperature Accuracy at 3.3 V and 5 V

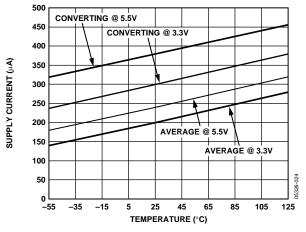

Figure 6. Operating Supply Current vs. Temperature

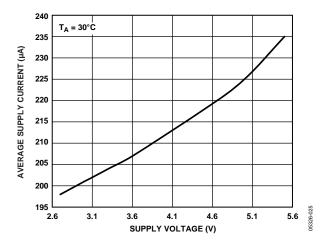

Figure 7. Average Operating Supply Current vs. Supply Voltage at 30°C

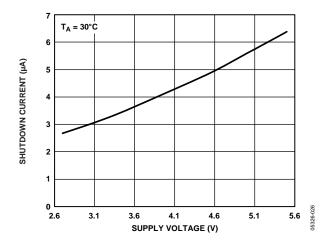

Figure 8. Shutdown Current vs. Supply Voltage at 30°C

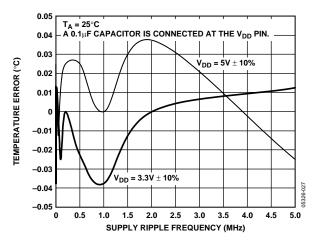

Figure 9. Temperature Accuracy vs. Supply Ripple Frequency

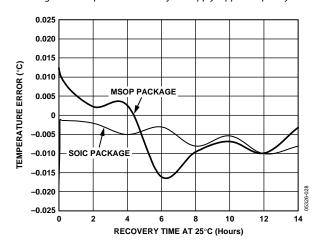

Figure 10. Response to Thermal Shock

## THEORY OF OPERATION

### CIRCUIT INFORMATION

The ADT75 is a 12-bit digital temperature sensor with the  $12^{th}$  bit acting as the sign bit. An on-board temperature sensor generates a voltage precisely proportional to absolute temperature that is compared to an internal voltage reference and input to a precision digital modulator. Overall accuracy for the ADT75 A Grade is  $\pm 2^{\circ}$ C from  $-25^{\circ}$ C to  $+100^{\circ}$ C and accuracy for the ADT75 B Grade is  $\pm 1^{\circ}$ C from  $0^{\circ}$ C to  $+70^{\circ}$ C. Both grades have excellent transducer linearity. The serial interface is SMBus /I<sup>2</sup>C- compatible and the open-drain output of the ADT75 is capable of sinking 3 mA.

The on-board temperature sensor has excellent accuracy and linearity over the entire rated temperature range without needing correction or calibration by the user.

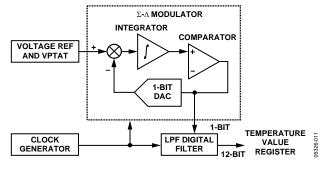

The sensor output is digitized by a first-order  $\Sigma$ - $\Delta$  modulator, also known as the charge balance type ADC. This type of converter uses time-domain oversampling and a high accuracy comparator to deliver 12 bits of effective accuracy in an extremely compact circuit.

## **CONVERTER DETAILS**

The  $\Sigma$ - $\Delta$  modulator consists of an input sampler, a summing network, an integrator, a comparator, and a 1-bit DAC. Similar to the voltage-to-frequency converter, this architecture creates a negative feedback loop and minimizes the integrator output by changing the duty cycle of the comparator output in response to input voltage changes. The comparator samples the output of the integrator at a much higher rate than the input sampling frequency; this is called oversampling. Oversampling spreads the quantization noise over a much wider band than that of the input signal, improving overall noise performance and increasing accuracy.

Figure 11. First-Order Σ-Δ Modulator

The modulated output of the comparator is encoded using a circuit technique that results in SMBus/I<sup>2</sup>C temperature data.

#### **FUNCTIONAL DESCRIPTION**

The conversion clock for the part is generated internally. No external clock is required except when reading from and writing to the serial port. In normal mode, the internal clock oscillator runs an automatic conversion sequence. During this automatic conversion sequence, a conversion is initiated every 100 ms. At this time, the part powers up its analog circuitry and performs a temperature conversion.

This temperature conversion typically takes 60 ms, after which time the analog circuitry of the part automatically shuts down. The analog circuitry powers up again 40 ms later, when the 100 ms timer times out and the next conversion begins. The result of the most recent temperature conversion is always available in the temperature value register because the SMBus/ $I^2$ C circuitry never shuts down.

The ADT75 can be placed in shutdown mode via the configuration register, in which case the on-chip oscillator is shut down and no further conversions are initiated until the ADT75 is taken out of shutdown mode. The ADT75 can be taken out of shutdown mode by writing 0 to Bit D0 in the configuration register. The ADT75 typically takes 1.7 ms to come out of shutdown mode. The conversion result from the last conversion prior to shutdown can still be read from the ADT75 even when it is in shutdown mode.

In normal conversion mode, the internal clock oscillator is reset after every read or write operation. This causes the device to start a temperature conversion, the result of which is typically available 60 ms later. Similarly, when the part is taken out of shutdown mode, the internal clock oscillator is started and a conversion is initiated.

The conversion result is typically available 60 ms later. Reading from the device before a conversion is complete causes the ADT75 to stop converting; the part starts again when serial communication is finished. This read operation provides the previous conversion result.

The measured temperature value is compared with a high temperature limit, stored in the 16-bit  $T_{\rm OS}$  read/write register and the hysteresis temperature limit, stored in the 16-bit  $T_{\rm HYST}$  read/write register. If the measured value exceeds these limits then the OS/ALERT pin is activated. This OS/ALERT pin is programmable for mode and polarity via the configuration register.

### Configuration register functions consist of

- Switching between normal operation and full power-down.

- Switching between comparator and interrupt event modes.

- Setting the OS/ALERT pin active polarity.

- Setting the number of faults that activate the OS/ALERT pin.

- Enabling the one-shot mode.

- Enabling the SMBus alert function mode on the OS/ALERT pin.

## **TEMPERATURE DATA FORMAT**

One LSB of the ADC corresponds to 0.0625°C. The ADC can theoretically measure a temperature range of 255°C (–128°C to +127°C), but the ADT75 is guaranteed to measure a low value temperature limit of –55°C to a high value temperature limit of +125°C. The temperature measurement result is stored in the 16-bit temperature value register and is compared with the high temperature limit stored in the  $T_{\rm DS}$  setpoint register and the hysteresis limit in the  $T_{\rm HYST}$  setpoint register.

Temperature data in the temperature value register, the  $T_{\rm OS}$  setpoint register and the  $T_{\rm HYST}$  setpoint register, is represented by a 12-bit twos complement word. The MSB is the temperature sign bit. The four LSBs, Bit DB0 to Bit DB3, are not part of the temperature conversion result and are always 0s. Table 6 shows the temperature data format without Bit DB0 to Bit DB3.

Reading back the temperature from the temperature value register requires a 2-byte read unless only a 1°C (8-bit) resolution is required, then a 1-byte read is required. Designers that use a 9-bit temperature data format can still use the ADT75 by ignoring the last three LSBs of the 12-bit temperature value. These three LSBs are Bit D4 to Bit D6 in Table 6.

Table 6. 12-Bit Temperature Data Format

| T           | Digital Output (Binary) | District Contract (U.S.) |

|-------------|-------------------------|--------------------------|

| Temperature | DB15 to DB4             | Digital Output (Hex)     |

| −55°C       | 1100 1001 0000          | 0xC90                    |

| −50°C       | 1100 1110 0000          | 0xCE0                    |

| −25°C       | 1110 0111 0000          | 0xE70                    |

| −0.0625°C   | 1111 1111 1111          | 0xFFF                    |

| 0°C         | 0000 0000 0000          | 0x000                    |

| +0.0625°C   | 0000 0000 0001          | 0x001                    |

| +10°C       | 0000 1010 0000          | 0x0A0                    |

| +25°C       | 0001 1001 0000          | 0x190                    |

| +50°C       | 0011 0010 0000          | 0x320                    |

| +75°C       | 0100 1011 0000          | 0x4B0                    |

| +100°C      | 0110 0100 0000          | 0x640                    |

| +125°C      | 0111 1101 0000          | 0x7D0                    |

## **Temperature Conversion Formulas**

## 12-Bit Temperature Data Format

- Positive Temperature = ADC Code(d)/16

- Negative Temperature = (ADC Code(d)<sup>1</sup> 4096)/16, or Negative Temperature = (ADC Code(d)<sup>2</sup> – 2048)/16

## 9-Bit Temperature Data Format

- Positive Temperature = ADC Code(d)/2

- Negative Temperature =  $(ADC Code(d)^3 512)/2$ , or Negative Temperature =  $(ADC Code(d)^4 - 256)/2$

#### 8-Bit Temperature Data Format

- Positive Temperature = ADC Code(d)

- Negative Temperature = ADC Code(d)<sup>5</sup> 256, or Negative Temperature = ADC Code(d)<sup>6</sup> 128

Bit DB7 (sign bit) is removed from the ADC code.

<sup>&</sup>lt;sup>1</sup> For ADC code, use all 12 bits of the data byte, including the sign bit.

<sup>&</sup>lt;sup>2</sup> For ADC code, Bit DB11 (sign bit) is removed from the ADC code.

<sup>&</sup>lt;sup>3</sup> For ADC code, use all 9 bits of the data byte, including the sign bit.

<sup>&</sup>lt;sup>4</sup> Bit DB8 (sign bit) is removed from the ADC code.

<sup>&</sup>lt;sup>5</sup> For the ADC code, use all 8 bits of the data byte, including the sign bit.

<sup>&</sup>lt;sup>6</sup> Bit DB7 (sign bit) is removed from the ADC code.

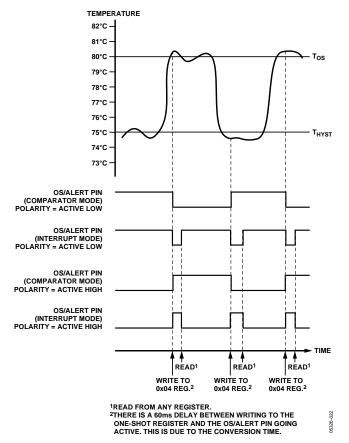

### **ONE-SHOT MODE**

Setting Bit D5 of the configuration register enables the one-shot mode. When this mode is enabled, the ADT75 goes immediately into shutdown mode and the current consumption is reduced to typically 3  $\mu A$  when  $V_{DD}$  is 3.3 V and 5.5  $\mu A$  when  $V_{DD}$  is 5 V. A one-shot temperature measurement is initiated when Address 0x04 is written to the address pointer register, which is writing to the one-shot register. The ADT75 powers up, does a temperature conversion, and powers down again.

Wait for a minimum of 60 ms after writing to the one-shot register before reading back the temperature. This time ensures the ADT75 has time to power up and do a conversion. Reading back from the one-shot register, Address 0x04, gives the resultant temperature conversion. Reading from the temperature value register also gives the same temperature value.

When either of the overtemperature detection modes is selected, a write to the one-shot register, Address 0x04, causes the OS/ALERT pin to go active if the temperature exceeds the overtemperature limits. Refer to Figure 12 for more information on one-shot OS/ALERT pin operation.

Note: In the interrupt mode, a read from any register resets the OS/ALERT pin after it is activated by a write to the one-shot register. In the comparator mode, once the temperature drops below the value in the  $T_{\rm HYST}$  register, a write to the one-shot register resets the OS/ALERT pin.

The one-shot mode is useful when one of the circuit design priorities is to reduce power consumption.

Figure 12. One-Shot OS/ALERT Pin Operation

## **FAULT QUEUE**

Bit D3 and Bit D4 of the configuration register are used to set up a fault queue. Up to six faults are provided to prevent false tripping of the OS/ALERT pin when the ADT75 is used in a noisy temperature environment. The number of faults set in the queue must occur consecutively to set the OS/ALERT output.

### **REGISTERS**

The ADT75 contains six registers: four are data registers, one is the address pointer register, and the final register is the one-shot register. The configuration register is the only data register that is 8 bits wide while the rest are 16 bits wide. The temperature value register is the only data register that is read only. Both a read and write can be performed on the rest of the data registers and on the one-shot register. On power-up, the address pointer register is loaded with 0x00 and points to the temperature value register.

**Table 7. ADT75 Registers**

| Pointer Address | Name                                                               | Power-On Default |

|-----------------|--------------------------------------------------------------------|------------------|

| 0x00            | Temperature value                                                  | 0x00             |

| 0x01            | Configuration                                                      | 0x00             |

| 0x02            | T <sub>HYST</sub> setpoint<br>T <sub>os</sub> setpoint<br>One-shot | 0x4B00 (75°C)    |

| 0x03            | T <sub>os</sub> setpoint                                           | 0x5000 (80°C)    |

| 0x04            | One-shot                                                           | 0xXX             |

## **Address Pointer Register**

This 8-bit write only register stores an address that points to one of the four data registers and selects the one-shot mode. P0 and P1 select the data register to which subsequent data bytes are written to or read from. P0, P1, and P2 are used to select the one-shot mode by writing 04h to this register. A zero should be written to the rest of the bits.

**Table 8. Address Pointer Register**

|                                 | P7 | P6 | P5 | P4 | Р3 | P2 | P1 | P0 |

|---------------------------------|----|----|----|----|----|----|----|----|

| Default Settings at<br>Power-Up | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

Table 9. Register Addresses

| P2 | P1 | P0 | Register Selected                         |

|----|----|----|-------------------------------------------|

| 0  | 0  | 0  | Temperature value                         |

| 0  | 0  | 1  | Configuration                             |

| 0  | 1  | 0  | T <sub>HYST</sub> setpoint                |

| 0  | 1  | 1  | T <sub>os</sub> setpoint<br>One-shot mode |

| 1  | 0  | 0  | One-shot mode                             |

## **Temperature Value Register**

This 16-bit read only register stores the temperature measured by the internal temperature sensor. The temperature is stored in twos complement format with the MSB being the temperature sign bit. When reading from this register, the eight MSBs (Bit D15 to Bit D8) are read first and then the eight LSBs (Bit D7 to Bit D0) are read. The control register settings are the default settings on power up.

## **Configuration Register**

This 8-bit read/write register stores various configuration modes for the ADT75. These modes are shutdown, overtemperature interrupt, one-shot, SMBus alert function enable, OS/ALERT pin polarity, and overtemperature fault queues. See Table 10.

MSB LSB

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3               | D2               | D1               | D0               |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|------------------|------------------|------------------|------------------|

| 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | N/A <sup>1</sup> | N/A <sup>1</sup> | N/A <sup>1</sup> | N/A <sup>1</sup> |

$<sup>^{1}</sup>$  N/A = not applicable.

#### Table 10.

| Bit | Configuration Mode    | Default Setting at Power-Up |   |

|-----|-----------------------|-----------------------------|---|

| D7  | OS/SMBus alert        | 0                           | _ |

| D6  | Reserved              | 0                           |   |

| D5  | One-shot              | 0                           |   |

| D4  | Fault queue           | 0                           |   |

| D3  | Fault queue           | 0                           |   |

| D2  | OS/ALERT pin polarity | 0                           |   |

| D1  | Cmp/Int               | 0                           |   |

| D0  | Shutdown              | 0                           |   |

#### Table 11.

| Bit            | Function                                                                                                                                                                                                                                       |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| D0             |                                                                                                                                                                                                                                                | tdown Bit. Setting this bit to 1 puts the ADT75 into shutdown mode. All circuitry except the SMBus/I <sup>2</sup> C interface is powered                          |  |  |  |  |  |  |  |  |

| Shutdown       | down. To power up the part again, write 0 to this bit.                                                                                                                                                                                         |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| D1             | This bit selects between comparator and interrupt mode.                                                                                                                                                                                        |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Cmp/Int        | D1                                                                                                                                                                                                                                             | Over Temperature Interrupt Modes                                                                                                                                  |  |  |  |  |  |  |  |  |

|                | 0                                                                                                                                                                                                                                              | Comparator mode                                                                                                                                                   |  |  |  |  |  |  |  |  |

|                | 1 Interrupt mode                                                                                                                                                                                                                               |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| D2             | This                                                                                                                                                                                                                                           | This bit selects the output polarity of the OS/ALERT pin.                                                                                                         |  |  |  |  |  |  |  |  |

| OS/ALERT       | D2                                                                                                                                                                                                                                             | OS/ALERT Pin Polarity                                                                                                                                             |  |  |  |  |  |  |  |  |

|                | 0                                                                                                                                                                                                                                              | Active low                                                                                                                                                        |  |  |  |  |  |  |  |  |

|                | 1                                                                                                                                                                                                                                              | Active high                                                                                                                                                       |  |  |  |  |  |  |  |  |

| D4:D3          | These two bits set the number of overtemperature faults that occur before setting the OS/ALERT pin. This helps to avoid false                                                                                                                  |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Fault<br>Oueue |                                                                                                                                                                                                                                                | gering due to temperature noise.                                                                                                                                  |  |  |  |  |  |  |  |  |

| Queue          | D [4                                                                                                                                                                                                                                           | Overtemperature Fault Queue                                                                                                                                       |  |  |  |  |  |  |  |  |

|                | 00                                                                                                                                                                                                                                             | 1 fault (default)                                                                                                                                                 |  |  |  |  |  |  |  |  |

|                | 01                                                                                                                                                                                                                                             | 2 faults                                                                                                                                                          |  |  |  |  |  |  |  |  |

|                | 10                                                                                                                                                                                                                                             | 4 faults                                                                                                                                                          |  |  |  |  |  |  |  |  |

|                | 11                                                                                                                                                                                                                                             | 6 faults                                                                                                                                                          |  |  |  |  |  |  |  |  |

| D5<br>One-Shot | One-shot Mode. Setting this bit puts the part into one-shot mode. In this mode, the part is normally powered down until a 0x04 is written to the address pointer register; then a conversion is performed, and the part returns to power down. |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|                | D5                                                                                                                                                                                                                                             | e-Shot Mode                                                                                                                                                       |  |  |  |  |  |  |  |  |

|                | 0                                                                                                                                                                                                                                              | Normal mode; powered up and converting every 100 ms                                                                                                               |  |  |  |  |  |  |  |  |

|                | 1 One-shot mode                                                                                                                                                                                                                                |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| D6             | Reserved. Write 0 to this bit.                                                                                                                                                                                                                 |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Reserved       |                                                                                                                                                                                                                                                |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| D7<br>OS/SMBus |                                                                                                                                                                                                                                                | errupt Mode Only. Enable SMBus alert function mode. This bit can enable the ADT75 to support the SMBus alert function en the interrupt mode is selected (D1 = 1). |  |  |  |  |  |  |  |  |

| Alert          | D7                                                                                                                                                                                                                                             | OS/SMBus Alert Mode                                                                                                                                               |  |  |  |  |  |  |  |  |

| Mode           | 0                                                                                                                                                                                                                                              | Disable SMBus alert function. The OS/ALERT pin behaves as an OS pin when this bit status is selected.                                                             |  |  |  |  |  |  |  |  |

|                | 1 Enable SMBus alert function.                                                                                                                                                                                                                 |                                                                                                                                                                   |  |  |  |  |  |  |  |  |

## T<sub>HYST</sub> Setpoint Register

This 16-bit read/write register stores the temperature hysteresis limit for the two interrupt modes. The temperature limit is stored in twos complement format with the MSB being the temperature sign bit. When reading from this register the eight MSBs are read first and then the eight LSBs are read. The default setting has the  $T_{HYST}$  limit at 75°C. The control register settings are the default settings on power up.

MSB

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3               | D2               | D1               | D0               |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|------------------|------------------|------------------|------------------|

| 0   | 1   | 0   | 0   | 1   | 0   | 1  | 1  | 0  | 0  | 0  | 0  | N/A <sup>1</sup> | N/A <sup>1</sup> | N/A <sup>1</sup> | N/A <sup>1</sup> |

<sup>&</sup>lt;sup>1</sup> N/A = not applicable.

## Tos Setpoint Register

This 16-bit read/write register stores the overtemperature limit value for the two interrupt modes. The temperature limit is stored in two complement format with the MSB being the temperature sign bit. When reading from this register, the eight MSBs are read first and then the eight LSBs are read. The default setting has the  $T_{OS}$  limit at 80°C. The control register settings are the default settings on power up.

MSB LSB

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3               | D2               | D1               | D0               |

|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|------------------|------------------|------------------|------------------|

| 0   | 1   | 0   | 1   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | N/A <sup>1</sup> | N/A <sup>1</sup> | N/A <sup>1</sup> | N/A <sup>1</sup> |

$<sup>^{1}</sup>$  N/A = not applicable.

### **SERIAL INTERFACE**

Control of the ADT75 is carried out via the SMBus/I<sup>2</sup>C-compatible serial interface. The ADT75 is connected to this bus as a slave and is under the control of a master device.

Figure 13 shows a typical SMBus/I<sup>2</sup>C interface connection.

Figure 13. Typical SMBus/I<sup>2</sup>C Interface Connection

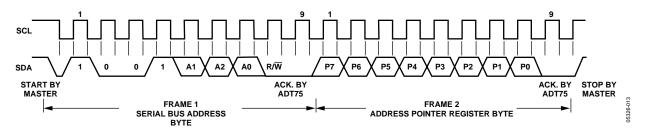

#### Serial Bus Address

Like all SMBus/I<sup>2</sup>C-compatible devices, the ADT75 has a 7-bit serial address. The four MSBs of this address for the ADT75 are set to 1001. Pin A2, Pin A1, and Pin A0 set the three LSBs. These pins can be configured two ways, low and high, to give eight different address options. Table 12 shows the different bus address options available. Recommended pull-up resistor value on the SDA and SCL lines is  $10 \text{ k}\Omega$ .

Table 12. SMBus/I<sup>2</sup>C Bus Address Options

| A6 | A5 | A4 | А3 | A2 | <b>A</b> 1 | A0 | Hex  |

|----|----|----|----|----|------------|----|------|

| 1  | 0  | 0  | 1  | 0  | 0          | 0  | 0x48 |

| 1  | 0  | 0  | 1  | 0  | 0          | 1  | 0x49 |

| 1  | 0  | 0  | 1  | 0  | 1          | 0  | 0x4A |

| 1  | 0  | 0  | 1  | 0  | 1          | 1  | 0x4B |

| 1  | 0  | 0  | 1  | 1  | 0          | 0  | 0x4C |

| 1  | 0  | 0  | 1  | 1  | 0          | 1  | 0x4D |

| 1  | 0  | 0  | 1  | 1  | 1          | 0  | 0x4E |

| 1  | 0  | 0  | 1  | 1  | 1          | 1  | 0x4F |

The ADT75 is designed with a SMBus/I<sup>2</sup>C timeout. The SMBus/I<sup>2</sup>C interface times out after 75 ms to 325 ms of no activity on the SDA line. After this timeout, the ADT75 resets the SDA line back to its idle state (SDA set to high impedance) and wait for the next start condition.

The serial bus protocol operates as follows:

- 1. The master initiates data transfer by establishing a start condition, defined as a high to low transition on the serial data line SDA, while the serial clock line SCL remains high. This indicates that an address/data stream is going to follow. All slave peripherals connected to the serial bus respond to the start condition and shift in the next eight bits, consisting of a 7-bit address (MSB first) plus a read/write (R/W) bit. The R/W bit determines whether data is written to, or read from, the slave device.

- 2. The peripheral with the address corresponding to the transmitted address responds by pulling the data line low during the low period before the ninth clock pulse, known as the acknowledge bit. All other devices on the bus now remain idle while the selected device waits for data to be read from or written to it. If the R/W bit is a zero then the master writes to the slave device. If the R/W bit is a one then the master reads from the slave device.

- 3. Data is sent over the serial bus in sequences of nine clock pulses, eight bits of data followed by an acknowledge bit from the receiver of data. Transitions on the data line must occur during the low period of the clock signal and remain stable during the high period, as a low to high transition when the clock is high can be interpreted as a stop signal.

- 4. When all data bytes have been read or written, stop conditions are established. In write mode, the master pulls the data line high during the 10<sup>th</sup> clock pulse to assert a stop condition. In read mode, the master device pulls the data line high during the low period before the ninth clock pulse. This is known as no acknowledge. The master takes the data line low during the low period before the 10<sup>th</sup> clock pulse, then high during the 10<sup>th</sup> clock pulse to assert a stop condition.

Any number of bytes of data can be transferred over the serial bus in one operation. However, it is not possible to mix read and write in one operation because the type of operation is determined at the beginning and cannot subsequently be changed without starting a new operation.

The I<sup>2</sup>C address set up by the three address pins is not latched by the device until after this address has been sent twice. On the eighth SCL cycle of the second valid communication, the serial bus address is latched in. This is the SCL cycle directly after the device has seen its own I<sup>2</sup>C serial bus address. Any subsequent changes on this pin has no effect on the I<sup>2</sup>C serial bus address.

### **WRITING DATA**

Depending on the register being written to, there are two different writes for the ADT75.

## Writing to the Address Pointer Register for a Subsequent Read

To read data from a particular register, the address pointer register must contain the address of that register. If it does not, the correct address must be written to the address pointer register by performing a single-byte write operation, as shown in Figure 14. The write operation consists of the serial bus address followed by the address pointer byte. No data is written to any of the data registers. A read operation is then performed to read the register.

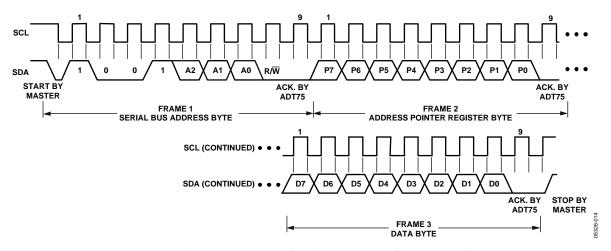

## Writing Data to a Register

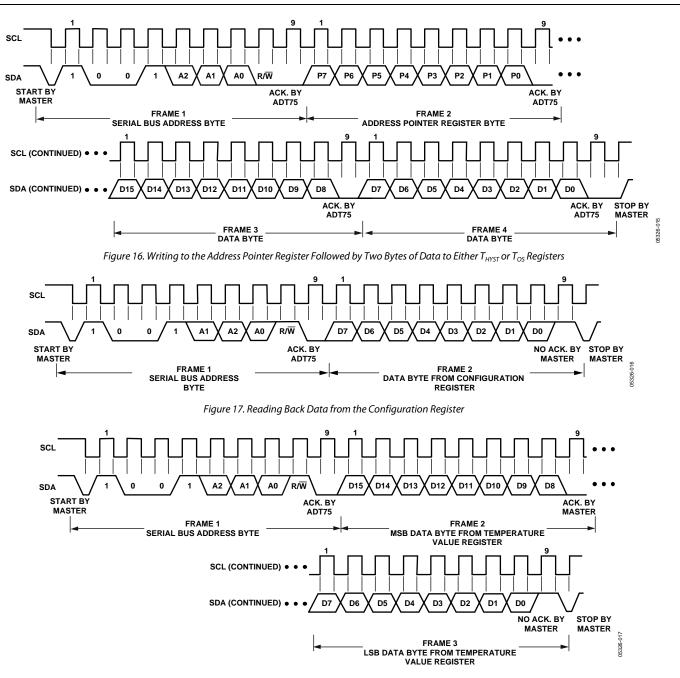

The configuration register is 8-bits wide so only one byte of data can be written to this register. Writing a single byte of data to the configuration register consists of the serial bus address, the data register address written to the address pointer register, followed by the data byte written to the selected data register. This is shown in Figure 15. The  $T_{\rm HYST}$  register and the  $T_{\rm OS}$  register are each 16-bits wide, so two data bytes can be written into these registers. Writing two bytes of data to either one of these registers consists of the serial bus address, the data register address written to the address pointer register, followed by the two data bytes written to the selected data register. This is shown in Figure 16. If more than the required number of data bytes is written to a register then the register ignores these extra data bytes. To write to a different register, another start or repeated start is required.

Figure 14. Writing to the Address Pointer Register to Select a Register for a Subsequent Read Operation

$Figure\ 15.\ Writing\ to\ the\ Address\ Pointer\ Register\ Followed\ by\ a\ Single\ Byte\ of\ Data\ to\ the\ Configuration\ Register$

Figure 18. Reading Back Data from the Temperature Value Register

### **READING DATA**

Reading data from the ADT75 is done in a one data byte operation for the configuration register and a two data byte operation for the temperature value register,  $T_{\rm HYST}$  register, and the  $T_{\rm OS}$  setpoint register. Reading back the contents of the configuration register is shown in Figure 17. Reading back the contents of the temperature value register is shown in Figure 18. Reading back from any register first requires a single-byte write operation to the address pointer register to set up the register address of the register that is going to be read from. To read from another register, execute another

write to the address pointer register to set up the relevant register address. Thus, block reads are not possible, that is, there is no I<sup>2</sup>C auto-increment. If the address pointer register has previously been set up with the address of the register that is going to receive a read command then there is no need to repeat a write operation to set up the register address again.

### OS/ALERT OUTPUT OVERTEMPERATURE MODES

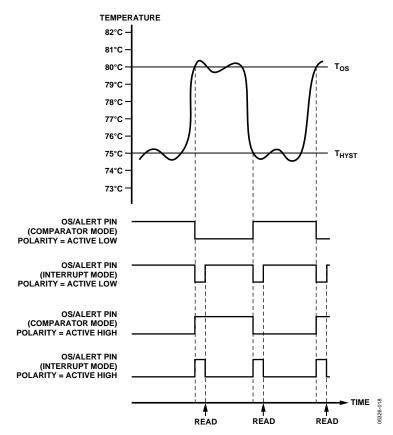

The ADT75 has two overtemperature modes, comparator mode and interrupt mode. The OS/ALERT pin defaults on power up as an OS pin; the comparator mode is the default power up overtemperature mode. The OS/ALERT output pin becomes active when the temperature measured exceeds the temperature limit stored in the  $T_{\rm OS}$  setpoint register. How this pin reacts after this event depends on the overtemperature mode selected.

## **Comparator Mode**

In the comparator mode, the OS/ALERT pin returns to its inactive status when the temperature measured drops below the limit stored in the  $T_{\rm HYST}$  setpoint register. Putting the ADT75 into shutdown mode does not reset the OS/ALERT state in comparator mode.

### Interrupt Mode

In the interrupt mode, the OS/ALERT pin goes inactive when any ADT75 register is read. The OS/ALERT pin can only return to active status if the temperature measured is below the limit stored in the  $T_{\rm HYST}$  setpoint register. Once the OS/ALERT pin is reset, it goes active again only when the temperature has gone above the  $T_{\rm OS}$  limit. The OS/ALERT pin can also be reset by a SMBus alert response address (ARA) when this pin has been selected as a SMBus alert pin. More information is given in the SMBUS Alert section.

Figure 19 illustrates the comparator and interrupt modes with both pin polarity settings. Placing the ADT75 into shutdown mode resets the OS/ALERT pin in the interrupt mode.

Figure 19. OS/ALERT Output Temperature Response Diagram

## **SMBus ALERT**

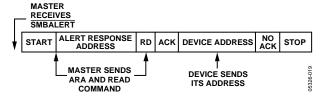

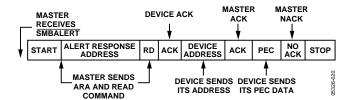

The OS/ALERT pin can behave as a SMBus alert pin when the SMBus alert function is enabled by setting Bit D7 in the configuration register. The interrupt mode must also be selected (Bit D1 in the configuration register). The OS/ALERT pin is an open-drain output and requires a pull-up to  $\rm V_{\rm DD}$ . Several SMBus alert outputs can be wire-AND'ed together, so that the common line goes low if one or more of the SMBus alert outputs goes low. The polarity of the OS/ALERT pin must be set for active low for a number of outputs to be wire-AND'ed together.

The OS/ALERT output can operate as a  $\overline{SMBALERT}$  function. Slave devices on the SMBus normally cannot signal to the master that they want to talk, but the  $\overline{SMBALERT}$  function allows them to do so.  $\overline{SMBALERT}$  is used in conjunction with the SMBus general call address.

One or more SMBus alert outputs can be connected to a common SMBALERT line connected to the master. When the SMBALERT line is pulled low by one of the devices, the following procedure occurs as shown in Figure 20.

Figure 20. ADT75 Responds to SMBALERT ARA

- 1. SMBALERT is pulled low.

- Master initiates a read operation and sends the SMBus alert response address (ARA = 0001 100). This reserved SMBus/ I<sup>2</sup>C address must not be used as a specific device address.

- 3. The device whose SMBus alert output is low responds to the SMBus alert response address and the master reads its device address. As the device address is seven bits long, the ADT75's LSB is free to be used as an indicator as to which temperature limit was exceeded. The LSB is high if the temperature is greater than or equal to T<sub>OS</sub>, and the LSB is low if the temperature is less than T<sub>HYST</sub>. The address of the device is now known and it can be interrogated in the usual way.

- 4. If more than one devices' SMBus alert output is low, the one with the lowest device address has priority, which is in accordance with normal SMBus specifications.

Once the ADT75 has responded to the SMBus alert response address, it resets its SMBus alert output. If the SMBALERT line remains low, the master sends the ARA again. It continues to do this until all devices whose SMBALERT outputs were low have responded.

Figure 21. ADT75 Responds to SMBALERT ARA with Packet Error Checking (PEC)

## APPLICATIONS INFORMATION

### THERMAL RESPONSE TIME

The time required for a temperature sensor to settle to a specified accuracy is a function of the thermal mass of the sensor and the thermal conductivity between the sensor and the object being sensed. Thermal mass is often considered equivalent to capacitance. Thermal conductivity is commonly specified using the symbol Q, and can be thought of as thermal resistance. It is commonly specified in units of degrees per watt of power transferred across the thermal joint. Thus, the time required for the ADT75 to settle to the desired accuracy is dependent on the package selected, the thermal contact established in that particular application, and the equivalent power of the heat source. In most applications, it is best to determine empirically the settling time.

#### **SELF-HEATING EFFECTS**

The temperature measurement accuracy of the ADT75 may be degraded in some applications due to self-heating. Errors can be introduced from the quiescent dissipation and power dissipated when converting. The magnitude of these temperature errors is dependent on the thermal conductivity of the ADT75 package, the mounting technique, and the effects of airflow. At 25°C, static dissipation in the ADT75 is typically 798.6  $\mu$ W operating at 3.3 V. In the 8-lead MSOP package mounted in free air, this accounts for a temperature increase due to self-heating of

$$\Delta T = P_{DISS} \times \theta_{IA} = 798.6 \ \mu W \times 205.9 \ C/W = 0.16 \ C$$

It is recommended that current dissipated through the device be kept to a minimum, because it has a proportional effect on the temperature error.

Using the power-down mode can reduce the current dissipated through the ADT75 subsequently reducing the self-heating effect. When the ADT75 is in power-down mode and operating at 25°C, static dissipation in the ADT75 is typically 78.6  $\mu W$  with  $V_{\rm DD}$  = 3.3 V and the power-up/conversion rate is 1 SPS (sample per second). In the 8-lead MSOP package mounted in free air, this accounts for a temperature increase due to self-heating of

$$\Delta T = P_{\text{DISS}} \times \theta_{JA} = 78.6 \ \mu\text{W} \times 205.9 \text{°C/W} = 0.016 \text{°C}$$

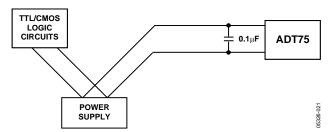

#### SUPPLY DECOUPLING

Decouple the ADT75 with a 0.1  $\mu F$  ceramic capacitor between  $V_{\rm DD}$  and GND. This is particularly important when the ADT75 is mounted remotely from the power supply. Precision analog products, such as the ADT75, require a well-filtered power source. Because the ADT75 operates from a single supply, it may seem convenient to tap into the digital logic power supply. However, the logic supply is often a switch mode design, which generates noise in the 20 kHz to 1 MHz range. In addition, fast logic gates can generate glitches hundreds of mV in amplitude due to wiring resistance and inductance.

If possible, power the ADT75 directly from the system power supply. This arrangement, shown in Figure 22, isolates the analog section from the logic switching transients. Even if a separate power supply trace is not available, generous supply bypassing reduces supply line induced errors. Local supply bypassing consisting of a 0.1  $\mu F$  ceramic capacitor is critical for the temperature accuracy specifications to be achieved. Place this decoupling capacitor as close as possible to the ADT75  $V_{\rm DD}$  pin.

Figure 22. Use Separate Traces to Reduce Power Supply Noise

## **TEMPERATURE MONITORING**

The ADT75 is ideal for monitoring the thermal environment within electronic equipment. For example, the surface-mounted package accurately reflects the exact thermal conditions that affect nearby integrated circuits.

The ADT75 measures and converts the temperature at the surface of its own semiconductor chip. When the ADT75 is used to measure the temperature of a nearby heat source, the thermal impedance between the heat source and the ADT75 must be considered. Often, a thermocouple or other temperature sensor is used to measure the temperature of the source, while the temperature is monitored by reading back from the ADT75 temperature value register.

Once the thermal impedance is determined, the temperature of the heat source can be inferred from the ADT75 output. As much as 60% of the heat transferred from the heat source to the thermal sensor on the ADT75 die is discharged via the copper tracks, the package pins, and the bond pads. Of the pins on the ADT75, the GND pin transfers most of the heat. Therefore, to measure the temperature of a heat source it is recommended that the thermal resistance between the ADT75 GND pin and the GND of the heat source is reduced as much as possible.

For example, use the ADT75's unique properties to monitor a high-power dissipation microprocessor. The ADT75 device, in a surface-mounted package, is mounted directly beneath the microprocessor's pin grid array (PGA) package. The ADT75 produces a linear temperature output while needing only two I/O pins and requiring no external characterization.

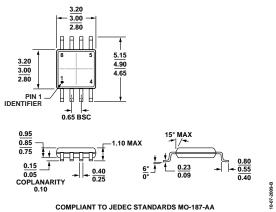

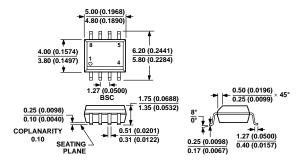

# **OUTLINE DIMENSIONS**

Figure 23. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MS-012-AA

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR