# $AD75019 - SPECIFICATIONS^{1}(T_{A} = +25^{\circ}C, V_{DD} \text{ and } V_{SS} = \pm 12 \text{ V}, V_{CC} = +5 \text{ V} \text{ unless otherwise noted})$

| AD75019                                                                                        | Symbol                              | Min            | Тур | Max            | Units  |

|------------------------------------------------------------------------------------------------|-------------------------------------|----------------|-----|----------------|--------|

| MULTIPLEXER                                                                                    |                                     |                |     |                |        |

| Input Signal Range                                                                             | V <sub>IN</sub>                     | $V_{SS} - 0.5$ |     | $V_{DD} + 0.5$ | V      |

| Switch ON Resistance, $V_{DD}$ and $V_{SS} = \pm 12$ V, $V_{SIGNAL} = \pm 12$ V                | R <sub>ON</sub>                     | 00             | 150 | 300            | Ω      |

| Switch ON Resistance, $V_{DD}$ and $V_{SS} = \pm 5 \text{ V}$ , $V_{SIGNAL} = \pm 5 \text{ V}$ | R <sub>ON</sub>                     |                | 300 | 500            | Ω      |

| Switch ON Resistance Matching <sup>2</sup> , $V_{SIGNAL} = \pm 12 V$                           | $\Delta R_{ON}$                     |                | 20  | 30             | Ω      |

| Leakage Current, $V_{SIGNAL} = \pm 10$ V                                                       | on                                  |                | 2   | 10             | nA     |

| Input/Output Capacitance                                                                       | C <sub>IN</sub>                     |                |     | 25             | pF     |

| Isolation Between Any Two Channels                                                             |                                     |                |     |                |        |

| $R_s = 600 \Omega$ , $R_L = 10 k\Omega$ , $V_{SIGNAL} = 2 V p-p$                               |                                     |                |     |                |        |

| $f_{SIGNAL} = 1 \text{ kHz}$                                                                   |                                     | 92             |     |                | dB     |

| $f_{SIGNAL} = 20 \text{ kHz}$                                                                  |                                     | 69             |     |                | dB     |

| $f_{SIGNAL} = 1 \text{ MHz}$                                                                   |                                     | 38             |     |                | dB     |

| Total Harmonic Distortion                                                                      |                                     |                |     |                |        |

| $R_s = 600 \Omega$ , $R_L = 10 k\Omega$ , $V_{SIGNAL} = 2 V p-p$                               |                                     |                |     | 0.01           | %      |

| Switch Frequency Response, -3 dB                                                               |                                     |                |     |                |        |

| $R_{s} = 600 \Omega, R_{L} = 10 k\Omega, V_{SIGNAL} = 2 V p-p$                                 |                                     | 20             |     |                | MHz    |

| Propagation Delay                                                                              |                                     |                | 4   | 8              | ns     |

| DIGITAL INPUTS (SIN, SCLK, PCLK)                                                               |                                     |                |     |                |        |

| Logic Levels (TTL Compatible)                                                                  |                                     |                |     |                |        |

| Input Voltage, Logic "1"                                                                       | V <sub>IH</sub>                     | 2.4            |     | 5.5            | V      |

| Input Voltage, Logic "0"                                                                       | V <sub>IL</sub>                     | 0              |     | 0.8            | V      |

| Input Current, $V_{IH} = 5.5 V$                                                                | I <sub>IH</sub>                     |                |     | $\pm 1$        | μA     |

| Input Current, $V_{IL} = 0.8 V$                                                                | I <sub>IL</sub>                     |                |     | $\pm 1$        | μA     |

| Input Capacitance                                                                              | C <sub>IN</sub>                     |                |     | 10             | pF     |

| DIGITAL OUTPUTS (SOUT)                                                                         |                                     |                |     |                |        |

| Logic Levels (TTL Compatible)                                                                  |                                     |                |     |                |        |

| Output Voltage, Logic "1"                                                                      | V <sub>OH</sub>                     | 2.8            |     |                | v      |

| Output Voltage, Logic "0"                                                                      | V <sub>OL</sub>                     | 2.0            |     | 0.4            | v      |

| Output Voltage, Logie $^{10}$<br>Output Current, $V_{OH} = 2.8 V$                              | I <sub>OH</sub>                     | 3.2            |     | 0.4            | mA     |

| Output Current, $V_{OL} = 0.4 V$                                                               | I <sub>OL</sub>                     | 3.2            |     |                | mA     |

|                                                                                                | LOL                                 | 5.2            |     |                | 1111 1 |

| POWER SUPPLY REQUIREMENTS                                                                      |                                     |                |     |                |        |

| Voltage Range, Total Analog                                                                    | $V_{DD} - V_{SS}$                   | 9.0            |     | 25.2           | V      |

| Voltage Range, Positive Analog                                                                 | V <sub>DD</sub> -V <sub>DGND</sub>  |                |     | 25.2           | V      |

| Voltage Range, Negative Analog                                                                 | V <sub>SS</sub> – V <sub>DGND</sub> | -20.7          | _   | 0              | V      |

| Voltage Range, Digital                                                                         | $V_{CC} - V_{DGND}$                 | 4.5            | 5   | 5.5            | V.     |

| Supply Current, SCLK = 5 MHz,                                                                  | $I_{DD}, I_{SS}$                    |                |     | $\pm 70$       | mA     |

| $V_{IL} = 0.8 \text{ V}, V_{IH} = 2.4 \text{ V}$                                               | I <sub>CC</sub>                     |                |     | 800            | μA     |

| Supply Current, Quiescent,                                                                     | I <sub>DD</sub> , I <sub>SS</sub>   |                | -   | ±400           | μA     |

| $V_{IL} = 0.8 \text{ V}, V_{IH} = 2.4 \text{ V}$                                               | I <sub>CC</sub>                     |                | _   | 100            | μA     |

NOTES <sup>1</sup>All minimum and maximum specifications are guaranteed, and specifications shown in **boldface** are tested on all production units at final electrical test. Results from those tests

are used to calculate outgoing quality levels. <sup>2</sup>Switch resistance matching is measured with zero volts at each analog input and refers to the difference between the maximum and minimum values. Specifications subject to change without notice.

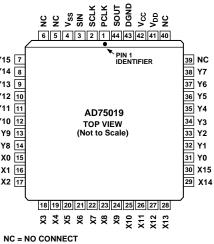

# **PIN FUNCTION DESCRIPTIONS**

| Pin | Name | Description                  | Pin | Name            | Description                       |        |                                                  |

|-----|------|------------------------------|-----|-----------------|-----------------------------------|--------|--------------------------------------------------|

| 1   | PCLK | Parallel Clock Input         | 23  | X8              | Analog Input (or Output)          |        | NC<br>V <sub>SS</sub><br>SIN<br>SCLK<br>SCLK     |

| 2   | SCLK | Serial Clock Input           | 24  | X9              | Analog Input (or Output)          |        | SCL SSIN SOL                                     |

| 3   | SIN  | Serial Data Input            | 25  | X10             | Analog Input (or Output)          |        | 6 5 4 3 2 1 44                                   |

| 4   | Vss  | Negative Analog Power Supply | 26  | X11             | Analog Input (or Output)          | ŕ      | •                                                |

| 5   | NC   | No Internal Connection       | 27  | X12             | Analog Input (or Output)          | Y15 7  |                                                  |

| 6   | NC   | No Internal Connection       | 28  | X13             | Analog Input (or Output)          | Y14 8  | IDE                                              |

| 7   | Y15  | Analog Output (or Input)     | 29  | X14             | Analog Output (or Input)          | Y13 9  |                                                  |

| 8   | Y14  | Analog Output (or Input)     | 30  | X15             | Analog Output (or Input)          |        |                                                  |

| 9   | Y13  | Analog Output (or Input)     | 31  | Y0              | Analog Output (or Input)          | Y12 10 |                                                  |

| 10  | Y12  | Analog Output (or Input)     | 32  | Y1              | Analog Output (or Input)          | Y11 11 | AD75019                                          |

| 11  | Y11  | Analog Output (or Input)     | 33  | Y2              | Analog Output (or Input)          | Y10 12 | TOP VIEW                                         |

| 12  | Y10  | Analog Output (or Input)     | 34  | Y3              | Analog Output (or Input)          | Y9 13  | (Not to Scale                                    |

| 13  | Y9   | Analog Output (or Input)     | 35  | Y4              | Analog Output (or Input)          | Y8 14  |                                                  |

| 14  | Y8   | Analog Output (or Input)     | 36  | Y5              | Analog Output (or Input)          | X0 15  |                                                  |

| 15  | X0   | Analog Input (or Output)     | 37  | Y6              | Analog Output (or Input)          | X1 16  |                                                  |

| 16  | X1   | Analog Input (or Output)     | 38  | Y7              | Analog Output (or Input)          | X2 17  |                                                  |

| 17  | X2   | Analog Input (or Output)     | 39  | NC              | No Internal Connection            |        |                                                  |

| 18  | X3   | Analog Input (or Output)     | 40  | NC              | No Internal Connection            | ,      | 18 19 20 21 22 23 24                             |

| 19  | X4   | Analog Input (or Output)     | 41  | VDD             | Positive Analog Power Supply      |        | 2 <del>2</del> 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 |

| 20  | X5   | Analog Input (or Output)     | 42  | V <sub>CC</sub> | Digital Power Supply              |        | * * * * * * *                                    |

| 21  | X6   | Analog Input (or Output)     | 43  | DGND            | Digital Ground                    | NC = N | IO CONNECT                                       |

| 22  | X7   | Analog Input (or Output)     | 44  | SOUT            | Serial Data Output: Positive True |        |                                                  |

### **PIN CONFIGURATION**

# AD75019

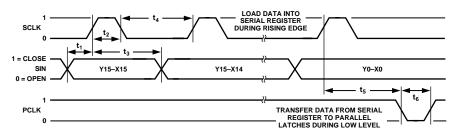

# **TIMING CHARACTERISTICS**<sup>1</sup> ( $T_A = T_{MIN}$ to $T_{MAX}$ , rated power supplies unless otherwise noted)

| Parameter                                     | Symbol         | Value | Units | Condition    |

|-----------------------------------------------|----------------|-------|-------|--------------|

| Data Setup Time                               | t <sub>1</sub> | 20    | ns    | min          |

| SCLK Pulsewidth                               | t <sub>2</sub> | 100   | ns    | min          |

| Data Hold Time                                | t <sub>3</sub> | 40    | ns    | min          |

| SCLK Pulse Separation                         | $t_4$          | 100   | ns    | min          |

| SCLK to PCLK Delay                            | t <sub>5</sub> | 65    | ns    | min          |

| SCLK to PCLK Delay and Release                | $(t_5 + t_6)$  | 5     | ms    | max          |

| PCLK Pulsewidth                               | t <sub>6</sub> | 65    | ns    | min          |

| Propagation Delay, PCLK to Switches On or Off | _              | 70    | ns    | max          |

| Data Load Time                                | _              | 52    | μs    | SCLK = 5 MHz |

| SCLK Frequency                                | _              | 20    | kHz   | min          |

| SCLK, PCLK Rise and Fall Times                | _              | 1     | μs    | max          |

#### NOTES

<sup>1</sup>Timing measurement reference level is 1.5 V.

Specifications subject to change without notice.

### TIMING DIAGRAM

# **OPERATION TRUTH TABLE**

| Control Lines |      |                   |                       |                                                                                                                                               |

|---------------|------|-------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| PCLK          | SCLK | SIN               | SOUT                  | Operation/Comment                                                                                                                             |

| 1             | 0    | Х                 | Х                     | No operation.                                                                                                                                 |

| 1             | 1    | Data <sub>i</sub> | Data <sub>i-256</sub> | The data on the SIN line is loaded into the serial register; data clocked into the serial register 256 clocks ago appears at the SOUT output. |

| 0             | Х    | Х                 | Х                     | Data in the serial shift register transfers into the parallel latches which control the switch array.                                         |

# APPLICATIONS INFORMATION

#### **Loading Data**

Data to control the switches is clocked serially into a 256-bit shift register and then transferred in parallel to 256 bits of memory. The rising edge of SCLK, the serial clock input, loads data into the shift register. The first bit loaded via SIN, the serial data input, controls the switch at the intersection of row Y15 and column X15. The next bits control the remaining columns (down to X0) of row Y15, and are followed by the bits for row Y14, and so on down to the data for the switch at the intersection of row Y0 and column X0. The shift register is dynamic, so there is a minimum clock rate, specified as 20 kHz.

After the shift register is filled with the new 256 bits of control data, PCLK is activated (pulsed low) to transfer the data to the parallel latches. Since the shift register is dynamic, there is a maximum time delay specified before the data is lost: PCLK must be activated and brought back high within 5 ms after filling the shift register. The switch control latches are static and will hold their data as long as power is applied.

To extend the number of switches in the array, you may cascade multiple AD75019s. The SOUT output is the end of the shift register, and may be directly connected to the SIN input of the next AD75019. REV. D

#### Power Supply Sequencing and Bypassing

All junction-isolated parts operating on multiple power supplies require proper attention to supply sequencing. Because BiMOS II is a junction-isolated process, parasitic diodes exist between  $V_{DD}$  and  $V_{CC}$ , and between  $V_{SS}$  and DGND. As a result,  $V_{DD}$  must always be greater than ( $V_{CC} - 0.5$  V), and  $V_{SS}$  must always be less than (DGND + 0.5 V).

If you can't ensure that system power supplies will sequence to meet these conditions, external Schottky (e.g., 1N5818) or silicon (e.g., 1N4001) diodes may be used. To protect the positive side, the anode would connect to  $V_{CC}$  (Pin 42) and the cathode to  $V_{DD}$  (Pin 41). For the negative side, connect the anode to  $V_{SS}$  (Pin 4) and the cathode to DGND (Pin 43).

Each of the three power supply pins [V<sub>DD</sub> (Pin 41), V<sub>CC</sub> (Pin 42) and V<sub>SS</sub> (Pin 4)] should be bypassed to DGND (Pin 43) through a 0.1  $\mu F$  ceramic capacitor located close to the package pins.

#### **Transistor Count**

AD75019 contains 5,472 transistors. This number may be used for calculating projected reliability.

# AD75019

# ABSOLUTE MAXIMUM RATINGS\*

|                                    | Min   | Max            | Units | Conditions            |

|------------------------------------|-------|----------------|-------|-----------------------|

| V <sub>DD</sub> to DGND            | -0.5  | +25.2          | V     |                       |

| V <sub>SS</sub> to DGND            | -25.2 | +0.5           | v     |                       |

| V <sub>CC</sub> to DGND            | -0.5  | +7.0           | v     |                       |

| V <sub>DD</sub> to V <sub>SS</sub> | -0.5  | +25.2          | v     |                       |

| V <sub>CC</sub> to V <sub>SS</sub> | -0.5  | +25.2          | v     |                       |

| Digital Inputs to DGND             | -0.3  | $V_{CC} + 0.5$ | v     |                       |

| Power Dissipation                  |       | 1.0            | w     | $T_A \le 75^{\circ}C$ |

| Operating Temperature Range        | 0     | +70            | °C    |                       |

| Storage Temperature                | -65   | +150           | °C    |                       |

| Lead Temperature                   |       | +300           | °C    | Soldering, 10 sec     |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# CAUTION \_

ESD (electrostatic discharge) sensitive device. The digital control inputs are Zener protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are removed.

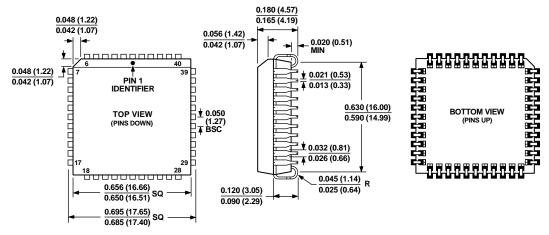

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-047-AC CONTROLLING DIMENSIONS ARE IN INCHES; MILLIMETER DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF INCH EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

> Figure 1. 44-Lead Plastic Leaded Chip Carrier [PLCC] (P-44) Dimensions shown in inches and (millimeters)

# **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                        | Package Option |

|--------------------|-------------------|--------------------------------------------|----------------|

| AD75019JPZ         | 0°C to 70°C       | 44-Lead Plastic Leaded Chip Carrier [PLCC] | P-44           |

| AD75019JPZ-REEL    | 0°C to 70°C       | 44-Lead Plastic Leaded Chip Carrier [PLCC] | P-44           |

<sup>1</sup> Z = RoHS Compliant Part.

# **REVISION HISTORY**

| 10/2018—Rev. C to Rev. D                     |

|----------------------------------------------|

| Changes to Temperature Range Parameter,      |

| AD75019—Specifications Table2                |

| Moved Outline Dimensions and Ordering Guide5 |

| Updated Outline Dimensions5                  |

| Changes to Ordering Guide5                   |

©2018 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D16744-0-10/18(D)

www.analog.com

Rev. D | Page 5 of 5