Pass through mode allows the STMIPID02 to be used as a standalone MIPI D-PHY physical layer device.

With this device a host with a standard 8-bit, 10-bit or 12-bit parallel input interface can be connected to camera modules with either a MIPI CSI-2 or a SMIA CCP2 low-voltage, fully differential bit-serial, low EMI interface.

There is an interrupt output for every MIPI CSI-2 short packet.

Power management is simplified by the presence of an integrated 1.2 V regulator to supply the MIPI D-PHY receiver and core logic.

The STMIPID02 is fully configurable via an I2C compatible slave control I/F.

DS12803 - Rev 1 page 2/50

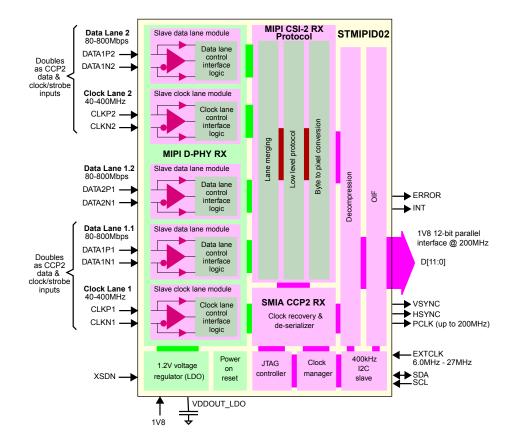

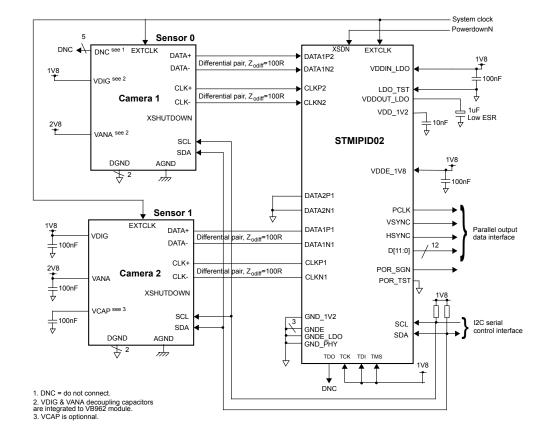

## 1 Block diagram

Figure 1. Block diagram

DS12803 - Rev 1 page 3/50

# 2 Application diagrams

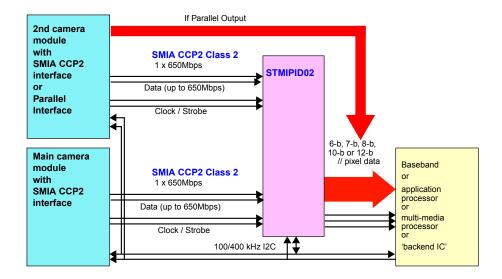

If Parallel Output 2nd camera module with MIPI CSI-2 1 x 800Mbps MIPI CSI-2 STMIPID02 interface or Data (80Mbps -> 800Mbps) parallel interface DDR Clock (40MHz -> 400MHz) 6-b, 7-b, 8-b, 10-b or 12-b MIPI CSI-2 2 x 800Mbps Main camera // pixel data Baseband module with Data2 (80Mbps -> 800Mbps) application MIPI CSI-2 processor interface Data1 (80Mbps -> 800Mbps) multi-media DDR Clock (40MHz -> 400MHz) processor or 100/400 kHz I2C 'backend IC'

Figure 2. MIPI CSI-2 application diagram

Figure 3. SMIA CCP2 application diagram

DS12803 - Rev 1 page 4/50

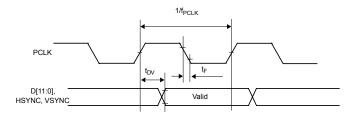

## 3 Output interface

The output interface is used to transfer image data from the STMIPID02 to the host.

#### **Features**

- CCIR601 compliant

- 12-bit data with pixel clock, HSYNC and VSYNC (external synchronization signals)

- Up to 200 MHz pixel clock, giving a data rate of 1.6 Gbit/s

- Programmable polarity of synchronization signals

- Tristate output control for multiple camera systems

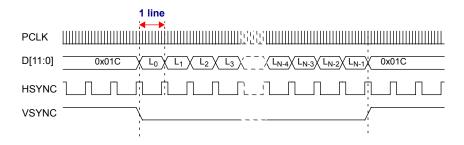

By default, VSYNC envelopes all lines of valid image data. HSYNC is active on all lines including vertical frame blanking period.

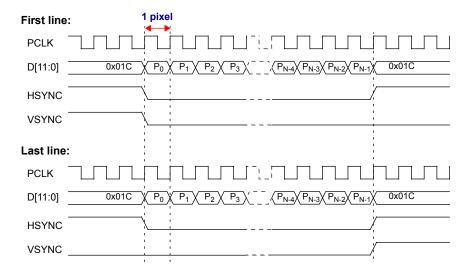

HSYNC and VSYNC output polarities are programmable. The description and the figures below assume the default polarity.

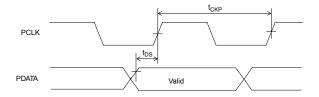

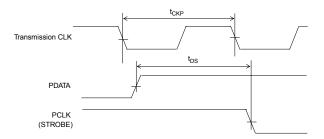

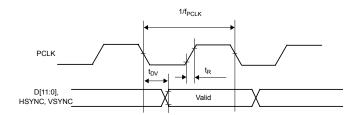

The host uses the rising edge of the PCLK to sample both the data and the synchronization lanes.

Since the output data bus is 12 bits wide, for an output stream of less than 12 bits per pixel, the data can be placed on lower or upper bits of the bus. This is controlled by the Mode\_Reg1[7] (address 0x14).

Table 1. Image format vs. number of bits on output interface

| Image format received      | Data type to be programmed in STMIPID02  | Number of bits on parallel output of STMIPID02 |

|----------------------------|------------------------------------------|------------------------------------------------|

| RAW6                       | RAW6                                     | 6 bits                                         |

| RAW7                       | RAW7                                     | 7 bits                                         |

| RAW8                       | RAW8                                     | 8bits                                          |

| RAW10                      | RAW10                                    | 10 bits                                        |

| RAW12                      | RAW12                                    | 12 bits                                        |

| RAW10 (as 10-6 compressed) | RAW6 (with decompression 6-10 enabled)   | 10 bits                                        |

| RAW10 ( as 10-7)           | RAW7 (with decompression 7-10 enabled)   | 10 bits                                        |

| RAW10 (as 10-8)            | RAW8 (with decompression 8-10 enabled)   | 10 bits                                        |

| RAW12 (as 12-10)           | RAW10 (with decompression 10-12 enabled) | 12 bits                                        |

| RAW12 (as 12-8)            | RAW8 (with decompression 8-12 enabled)   | 12 bits                                        |

| RAW12 (as 12-7)            | RAW8 (with decompression 7-12 enabled)   | 12 bits                                        |

| RAW12 (as 12-6)            | RAW8 (with decompression 6-12 enabled)   | 12 bits                                        |

| RGB565                     | RAW8                                     | 8 bits                                         |

| RGB888                     | RAW8                                     | 8 bits                                         |

| RGB444                     | RAW8                                     | 8 bits                                         |

| YUV420 8 bits              | RAW8                                     | 8 bits                                         |

| YUV422 8 bits              | RAW8                                     | 8 bits                                         |

| YUV420 10 bits             | RAW10                                    | 10 bits                                        |

DS12803 - Rev 1 page 5/50

Figure 4. 12-bit parallel data interface signals - frame level

Figure 5. 12-bit parallel data interface signals - line level

DS12803 - Rev 1 page 6/50

page 7/50

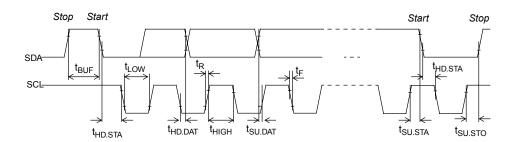

## 4 Control interface

The STMIPID02 is controlled through the 400 kHz I2C compatible slave command interface. The 8-bit device address is 0x28 for write operations and 0x29 for read operations. The register index is a 16-bit format and the register value is an 8-bit format. The external clock must be active for I2C slave operations.

#### Example

To write 0x15 in the register 0x02, the following sequence has to be applied:

S 0x28 A 0x00 A 0x02 A 0x15 A

To read the content of register 0x02:

**S** 0x28 **A** 0x00 **A** 0x02 **A P S** 0x29 **A** xx **N P**

Where **S** = START; **P** = STOP; **A** = ACK; **N** = NACK

Detailed control inteface timings are described in Section 11.5.2 I2C slave timing (SCL, SDA).

DS12803 - Rev 1

# 5 Application examples

SMIA CCP2 STMIPID02 3MP @ 15fps @ 10-b 10-b @ 65MHz 650Mbps, RAW10 PCLK = 65MHz SMIA CCP2 TX SMIA CCP2 RX Host Data (650Mbps) system Strobe MIPI CSI-2 800Mbps, RAW10 3MP @ 20fps @ 10-b STMIPID02 10-b @ 80MHz PCLK = 80MHz MIPI CSI-2 TX MIPI CSI-2 RX Host Data1 (800Mbps) system DDR Clock (400MHz) SMIA CCP2 STMIPID02 5MP @ 15fps @ 10-b 10-b @ 92.8MHz 650Mbps, 10b-7b Compressed PCLK = 92.8MHz SMIA CCP2 TX SMIA CCP2 RX 7 - 10 Decomp Host 10 - 7 Comp Data1 (650Mbps) system Strobe MIPI CSI-2 STMIPID02 5MP @ 15fps @ 10-b 10-b @ 96MHz 768Mbps, 10b-8b Compressed PCLK = 96MHz MIPI CSI-2 TX 8 - 10 Decomp Host MIPI CSI-2 RX 10 - 8 Comp Data1 (768Mbps) system DDR Clock (384MHz) MIPI CSI-2 1.44Gbps, RAW12 STMIPID02 8MP @ 12fps @ 12-b 12-b @ 120MHz PCLK = 120MHz MIPI CSI-2 TX Host CSI-2 RX Data2 (720Mbps) system Data1 (720Mbps) M DDR Clock (360MHz)

Figure 6. Application examples

# 6 Key technical specifications

**Table 2. Technical specifications**

| Technology                | ST 65 nm CMOS                                                    |

|---------------------------|------------------------------------------------------------------|

|                           | SMIA: RAW6, RAW7, RAW8, RAW10, and RAW12                         |

| Pixel format(s)           | SMIA: 8-10, 7-10, 6-10, 8-12, 7-12, 6-12 DPCM/PCM decompression  |

|                           | MIPI CSI-2: RAW6, RAW7, RAW8, RAW10, and RAW12 YUV, RGB, JPEG    |

|                           | MIPI CSI-2 interface (2x800 Mbps + 1x800 Mbps)                   |

| Input video interface(s)  | SMIA CCP2 Interface (1x208 Mbps Class 0 + 1x650 Mbps - Class 2)  |

| Output video interface(s) | 1V8, 200 MHz, 12-bit parallel interface + VSYNC, HSYNC, and PCLK |

| Control interface         | 100/400 kHz I2C                                                  |

| Clock input               | 6.0 MHz to 27 MHz                                                |

| Supply voltage            | Digital IO: 1.7 V - 1.9 V                                        |

| Power consumption         | TBC                                                              |

| Package type              | VFBGA 3x 3x1 mm, 49 ball, F7x7 pitch, 0.4 mm ball 0.25 mm        |

| Package size              | 3.0 mm x 3.0 mm x 1.0 mm (wlh)                                   |

| Device address            | 0x28                                                             |

# 7 Ball assignment and description

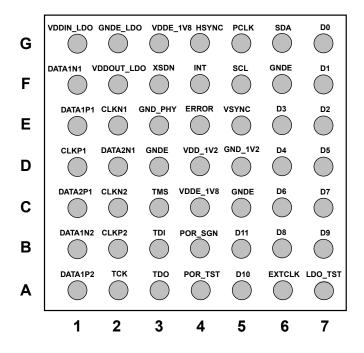

Figure 7. Ball assignment: bottom view (49 balls)

Note: The CSI-2 clock lanes must be in the middle of the two data lanes.

Note: The PCLK, HSYNC, VSYNC must be routed in the middle of the output data bus for skew management reasons.

Table 3. Ball description

| Ball name | Туре             | Description                                                                                 |  |  |  |  |  |  |  |  |

|-----------|------------------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

|           | Power supplies   |                                                                                             |  |  |  |  |  |  |  |  |

| VDDE_1V8  | Power            | 1V8 digital IO supply                                                                       |  |  |  |  |  |  |  |  |

| VDDIN_LDO | Power            | 1V8 voltage regulator supply                                                                |  |  |  |  |  |  |  |  |

| VDD_1V2   | Power            | 1V2 MIPI D-PHY and digital core supply                                                      |  |  |  |  |  |  |  |  |

| GNDE      | Ground           | Digital IO ground                                                                           |  |  |  |  |  |  |  |  |

| GNDE_LDO  | Ground           | Voltage regulator ground                                                                    |  |  |  |  |  |  |  |  |

| GND_PHY   | Ground           | D-PHY ground                                                                                |  |  |  |  |  |  |  |  |

| GND_1V2   | Ground           | Digital core ground                                                                         |  |  |  |  |  |  |  |  |

|           | System interface |                                                                                             |  |  |  |  |  |  |  |  |

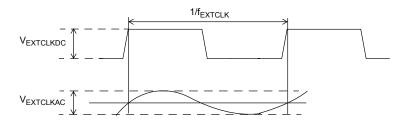

| EXTCLK    | Input            | System clock input (for I2C slave), 6.0 MHz - 27.0 MHz                                      |  |  |  |  |  |  |  |  |

| ERROR     | Output           | Error interrupt, indicates that an error (either D-PHY or protocol) has occurred            |  |  |  |  |  |  |  |  |

| INT       | Output           | MIPI CSI-2 short packet received interrupt, indicates that a short packet has been received |  |  |  |  |  |  |  |  |

DS12803 - Rev 1 page 10/50

| Ball name        | Туре                             | Description                                                                                                                                  |

|------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| XSDN             | Input                            | Chip shutdown                                                                                                                                |

|                  | Control interface                |                                                                                                                                              |

| SCL              | Input                            | Host I2C clock                                                                                                                               |

| SDA              | BiDir                            | Host I2C data                                                                                                                                |

|                  | Dual lane input data interface   |                                                                                                                                              |

| CLKP1, CLKN1     | Input                            | MIPI CSI-2 receiver 1 DDR clock input,<br>MIPI D-PHY physical layer, doubles as<br>CCP2 strobe/clock input in SMIA CCP2<br>Class 2 mode      |

| DATA1P1, DATA1N1 | Input                            | MIPI CSI-2 receiver 1 data lane 1, MIPI D-PHY physical layer, doubles as CCP2 data input in SMIA CCP2 Class 2 mode                           |

| DATA2P1, DATA2N1 | Input                            | MIPI CSI-2 receiver 1 data lane 2, MIPI<br>D-PHY physical layer                                                                              |

|                  | Single lane input data interface |                                                                                                                                              |

| CLKP2, CLKN2     | Input                            | MIPI CSI-2 receiver 2 DDR clock input,<br>MIPI D-PHY physical layer, doubles as<br>CCP2 strobe/clock input in SMIA CCP2<br>Class 2 mode      |

| DATA1P2, DATA1N2 | Input                            | MIPI CSI-2 receiver 2 data lane, MIPI D-<br>PHY physical layer, doubles as CCP2<br>data input in SMIA CCP2 Class 2 mode                      |

|                  | Output data interface            |                                                                                                                                              |

| D[11:0]          | Output                           | Parallel video 12-bit data output                                                                                                            |

| PCLK             | Output                           | Pixel clock: PCLK rising edge is used to sample D[11:0], HSYNC and VSYNC. PCLK polarity is programmable                                      |

| HSYNC            | Output                           | Horizontal synchronization: HSYNC is high during active video and low during the horizontal blanking periods. HSYNC polarity is programmable |

| VSYNC            | Output                           | Vertical synchronization: VSYNC is high during active video and low during the vertical blanking periods. VSYNC polarity is programmable     |

|                  | Power on reset (POR)             |                                                                                                                                              |

| POR_SGN          | BiDir                            | Power on reset signal                                                                                                                        |

| POR_TST          | Input                            | Power on reset test signal, should be set to ground for internal POR                                                                         |

|                  | Voltage regulator                |                                                                                                                                              |

| VDDOUT_LDO       | Power                            | LDO 1.2 V output                                                                                                                             |

|                  | Test interface (ST internal use) |                                                                                                                                              |

| LDO_TST          | Input                            | LDO regulator test mode                                                                                                                      |

| TDI              | Input                            | Test data input                                                                                                                              |

| TMS              | Input                            | Test mode                                                                                                                                    |

| TCK              | Input                            | Test clock                                                                                                                                   |

| TDO              | Output                           | Test data out                                                                                                                                |

# 8 Functional description

## 8.1 Power up sequence

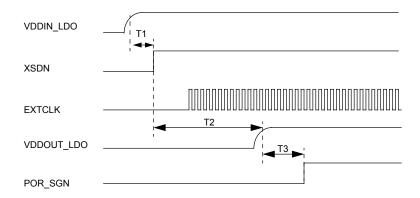

Please find below the timing of the power up sequence.

Figure 8. Power up sequence

Table 4. Power up sequence timing

| Symbol | Parameter                                                            | Min.                | Тур. | Max. | Unit |

|--------|----------------------------------------------------------------------|---------------------|------|------|------|

| T1     | Time between power up and LDO enable                                 | VDDIN_LDO<br>stable |      | +inf | S    |

| T2     | Time between<br>XSDN and CORE<br>power up (LDO out<br>rise to 1.2 V) |                     |      | 5    | ms   |

| Т3     | Time between<br>CORE power up to<br>1.2 V and reset<br>generation    |                     | 20   |      | μs   |

DS12803 - Rev 1 page 12/50

### 8.2 User modes

### 8.2.1 Standard modes

The output parallel interface outputs12 bits of data, HSYNC, VSYNC, and PCLK. It is recommended to enable the compensation macro (controlled by Mode\_Reg3[5], at address 0x36) for both Standard and Bypass modes.

#### CSI2/CSI2

- Main camera: CSI2 up to 1.6 Gbps (with limitation detailed in Section 8.3 CSI2 limitations)

- Second camera: CSI2 up to 800 Mbps

#### CSI2/CCP2

- Main camera: CSI2 up to 1.6 Gbps (with limitation detailed in Section 8.3 CSI2 limitations)

- Second camera: CCP2 up to 650 Mbps

#### CSI2/ITU-R601

- Main camera: CSI2 up to 1.6 Gbps (with limitation detailed in Section 8.3 CSI2 limitations)

- · Second camera: YUV directly connected to baseband parallel interface

### 8.2.2 Bypass modes

Bypass mode is used for any activities or applications where only PHY is needed, example, 8-bit data.

#### CSI2/CSI2

- Main camera: CSI2 up to 1.6 Gbps (with limitation detailed in Section 8.3 CSI2 limitations)

- Second camera: CSI2 up to 800 Mbps

#### **CSI2/ ITU-R601**

- Main camera: CSI2 up to 1.6 Gbps (with limitation detailed in Section 8.3 CSI2 limitations)

- Second camera: YUV directly connected to baseband parallel interface

### 8.3 CSI2 limitations

The bandwidth is limited to 800 Mbps in RAW6/RAW7 dual lane inputs. This is irrespective of the compression used or not

DS12803 - Rev 1 page 13/50

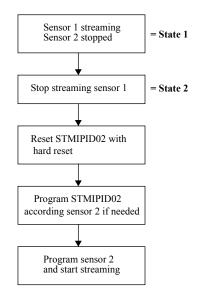

### 8.4 Sensor switching mechanism

The flow chart below explains the sensor switching mechanism. If one sensor is streaming and the other is not we are in **state1**. If both sensors are not streaming, we are in **state2**.

It is forbidden that both sensors stream simultaneously while switching. To switch sensors, it is obligatory to be in **state1** or **state2**.

Figure 9. Sensor switching mechanism

### 8.5 Error signal

Below is an accumulated status of all errors found in the chip.

- Status of all errors from all D-PHY's

- 2. Checksum and ECC failures of CSI reception

- 3. ccp\_shift\_sync, ccp\_false\_sync and ccp\_crc\_error of CCP reception

The individual status of an error can be checked on the respective I2C register bit. The status can be cleared by programming Mode\_reg2[6] register.

### 8.6 INT signal

This is a status showing reception of a short packet in the CSI stream. The user needs to clear the status by programming Clock\_control\_reg1[5] to observe the next short packet. If the user does not clear this bit then he may miss the transition on the INT ball when the next short packet is observed. The application of short packet interrupts is not envisioned yet.

DS12803 - Rev 1 page 14/50

# 9 Register description

# 9.1 Clock lane 1 registers

| Re       | gister Name       | Acce | ess              | Local<br>Address                                                     |                                                                                                 | Description                                                                                                                                                                    |                                                                                  |  |

|----------|-------------------|------|------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| clk_lane | _reg1             | R/W  |                  | 0x02                                                                 |                                                                                                 | General and CSI controls of clock lane1<br>(CLKP1,CLKN1)                                                                                                                       |                                                                                  |  |

| Bit No   | Bit Name          |      | Default<br>Value |                                                                      | Description                                                                                     |                                                                                                                                                                                |                                                                                  |  |

| 7        | ui_x4_clk_lane[5] |      | 0                |                                                                      | l                                                                                               | control (unused in CCP mode): Unit interval                                                                                                                                    |                                                                                  |  |

| 6        | ui_x4_clk_lane[4] |      |                  | time multiplied by four This signal indicates the bit period in unit |                                                                                                 |                                                                                                                                                                                |                                                                                  |  |

| 5        | ui_x4_clk_lane[3] |      |                  |                                                                      | 0.25 ns. If the unit interval is 3 ns, twelve (0x0C)                                            |                                                                                                                                                                                |                                                                                  |  |

| 4        | ui_x4_clk_lane[2] |      |                  |                                                                      | should be programmed. This value is used to<br>generate delays. Therefore, if the period is not |                                                                                                                                                                                |                                                                                  |  |

| 3        | ui_x4_clk_lane[1] |      |                  |                                                                      | multiple of 0.25 ns, the value should be round                                                  |                                                                                                                                                                                |                                                                                  |  |

| 2        | ui_x4_clk_lane[0] | l    |                  |                                                                      |                                                                                                 | down. For example, a 600 Mbps single lane linkuses a unit interval of 1.667 ns. Multiplying by four results in 6.667. In this case, a value of 6 (not 7) should be programmed. |                                                                                  |  |

| 1        | swap_pins_clk_la  | ne   | 0                |                                                                      | 0                                                                                               |                                                                                                                                                                                | Swap P and N pins 0= Swap disabled 1= Swap enabled (CLKP1 and CLKN1 are swapped) |  |

| 0        | Enable            |      | 0                |                                                                      | Enab                                                                                            | ole clock lane module (CLKP1 and CLKN1)  0= Disable clock lane 1  1= Enable clock lane 1                                                                                       |                                                                                  |  |

DS12803 - Rev 1 page 15/50

| Register Name |                               | Access |              | Loc<br>Addi |      | Description                                                                                                                                     |

|---------------|-------------------------------|--------|--------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|               | clk_lane_reg3                 | R/W    |              | 0x04        |      | CCP/CSI controls of the clock lane 1                                                                                                            |

| Bit No        | Bit Name                      |        | Defa<br>Valu |             | Desc | cription                                                                                                                                        |

| [7:5]         | Reserved                      |        | 000          |             | Rese | erved                                                                                                                                           |

| 4             | hs_rx_term_e_subLVDS_clk_lane |        |              |             | _    | n Speed termination enable for CCP mode used in CSI mode)  0= Disable HS termination  1= Enable HS termination, mandatory for CCP mode          |

| 3             | hs_rx_e_subLVDS_clk_lane      |        |              |             | _    | n Speed Receiver enable for CCP mode<br>used in CSI mode)<br>0= Disable HS receiver<br>1= Enable HS receiver, mandatory for<br>CCP mode         |

| 2             | hs_rx_wakeup_subLVDS_clk_lane |        | 0            |             | _    | n Speed Receiver wake-up enable for CCP e (unsused in CSI mode)  0= HS-receiver in low power mode 1= Enable HS receiver, mandatory for CCP mode |

| 1             | cntrl_mipi_subLVDS_clk        | _lane  | 0            |             | Sele | ct CSI or CCP mode<br>0= SMIA CCP<br>1= MIPI CSI                                                                                                |

| 0             | Reserved                      |        | 0            |             | Rese | erved                                                                                                                                           |

| Re        | egister Name       | Acc    | eess Local<br>Address |      |                                                                                                                                                   | Description                                                                |  |

|-----------|--------------------|--------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|

| clk_lar   | ne_wr_reg1         | RO     |                       | 0x01 |                                                                                                                                                   | Clock lane 1 status in CSI mode                                            |  |

| Bit<br>No | Bit Name           |        | Default D<br>Value    |      | Desc                                                                                                                                              | Description                                                                |  |

| [7:2]     | Reserved           |        | 000000                |      | Reserved                                                                                                                                          |                                                                            |  |

| 1         | ulp_active_not_cl  | k_lane | 0                     |      | CSI Ultra low-power state active 0= The clock lane is not in ULP state or prepare to leave ULP state 1= The clock lane has reached the ULP state. |                                                                            |  |

| 0         | stop_state_clk_lar | ne     | 0                     | 0    |                                                                                                                                                   | Lane in stop state signal indicates that the lane module is in STOP state. |  |

DS12803 - Rev 1 page 16/50

### 9.2 Data lane 1.1 controls

|           | Register Name       |                   | Access |                  | cal<br>ress | Description                                                                                    |  |

|-----------|---------------------|-------------------|--------|------------------|-------------|------------------------------------------------------------------------------------------------|--|

| data_la   | nne0_reg1           | R/W               |        | 0x05             |             | General controls of data lane1.1 (DATA1P1 and DATA1N1)                                         |  |

| Bit<br>No | Bit Name            | Name              |        | Default<br>Value |             | Description                                                                                    |  |

| [7:2]     | Reserved            |                   |        | 000000 Res       |             | Reserved                                                                                       |  |

| 1         | Swap_pins_data_lane | ins_data_lane     |        |                  |             | Swap P and N pins  0= Swap enabled (DATA1P1 and DATA1N1 are swapped)  1= Swap disabled         |  |

| 0         | Enable_data_lane    | nable_data_lane 0 |        |                  | Enal        | ble data lane 1.1 (DATA1P1 and DATA1N1)<br>0= Disable data lane 1.1<br>1= Enable data lane 1.1 |  |

| Re       | egister Name                       | Access        | Lo | ocal Address | Description                                                                                                                                            |

|----------|------------------------------------|---------------|----|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| data_lan | e0_reg2                            | R/W 0x06      |    | )6           | CCP/CSI controls of the data lane 1.1                                                                                                                  |

| Bit No   | Bit No Bit Name                    |               |    |              | Description                                                                                                                                            |

| [7:4]    | Reserved                           |               |    | 0000         | Reserved                                                                                                                                               |

| 3        | hs_rx_term_e_                      | subLVDS       |    | 0            | High Speed termination enable for CCP mode (unsused in CSI mode)  0= Disable HS termination  1= Enable HS termination, mandatory for CCP mode          |

| 2        | hs_rx_e_subL                       | VDS           |    | 0            | High Speed Receiver enable for CCP mode (unsused in CSI mode)  0= Disable HS receiver  1= Enable HS receiver, mandatory for CCP mode                   |

| 1        | hs_rx_wakeup_subLVDS_data_la<br>ne |               |    | 0            | High Speed Receiver wake-up enable for CCP mode (unsused in CSI mode)  0= HS-receiver in low power mode  1= Enable HS receiver, mandatory for CCP mode |

| 0        | cntrl_mipi_sub                     | LVDS_data_lan | ie | 0            | Select CSI or CCP mode<br>0= SMIA CCP<br>1= MIPI CSI                                                                                                   |

DS12803 - Rev 1 page 17/50

|          | Register Name Access   |             | S                | Local<br>Address |             | Description                                                                                                                                   |  |

|----------|------------------------|-------------|------------------|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| data_lan | e0_reg3                | RO          |                  | 0x07             |             | CSI controls of data lane 1.1                                                                                                                 |  |

| Bit No   | Bit No Bit Name        |             | Default<br>Value |                  | Description |                                                                                                                                               |  |

| [7:2]    | Reserved               |             | 000000           |                  | Rese        | Reserved                                                                                                                                      |  |

| 1        | ulp_active_not_data    | t_data_lane |                  |                  |             | Ultra low-power state active 0= The clock lane is not in ULP state or prepare to leave ULP state 1= The clock lane has reached the ULP state. |  |

| 0        | stop_state_data_lane 0 |             | 0                |                  | This        | Lane in stop state signal indicates that the lane module is in P state.                                                                       |  |

| Regi     | ster Name    | A  | ccess | Loc<br>Add       |                                                                                                                                                                | Description                                                                                                                                                                                                                           |  |  |  |

|----------|--------------|----|-------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| data_lan | e0_reg4      | RO |       | 0x0C             |                                                                                                                                                                | CSI protocol Error status registers                                                                                                                                                                                                   |  |  |  |

| Bit No   | Bit Name     |    |       | Default<br>Value |                                                                                                                                                                | cription                                                                                                                                                                                                                              |  |  |  |

| [7:6]    | Reserved     |    | 0     |                  | Rese                                                                                                                                                           | Reserved.                                                                                                                                                                                                                             |  |  |  |

| 5        | err_control  |    | 0     |                  |                                                                                                                                                                | Unexpected control sequence error This signal is asserted when an incorrect line state sequence is detected.                                                                                                                          |  |  |  |

| 4        | err_sync_esc |    | 0     |                  | If the<br>miss<br>this                                                                                                                                         | Escape synchronization error If the number of bits received during a low-power data transmission is not a multiple of eight when the transmission ends, this signal is asserted and remains high until the next change in line state. |  |  |  |

| 3        | err_esc      |    | 0     |                  | Error during escape command If an unrecognized escape entry command is received, this signal is asserted and remains high until the next change in line state. |                                                                                                                                                                                                                                       |  |  |  |

| 2        | err_eot_sync | hs | 0     | 0                |                                                                                                                                                                | Error during high-speed end of transmission (EoT)                                                                                                                                                                                     |  |  |  |

| 1        | err_sot_sync | hs | 0     |                  | Sync<br>(Sol                                                                                                                                                   | chronization error during high-speed start of transmission                                                                                                                                                                            |  |  |  |

| 0        | err_sot_hs   |    | 0     | Erro             |                                                                                                                                                                | r during high-speed start of transmission (SoT)                                                                                                                                                                                       |  |  |  |

DS12803 - Rev 1 page 18/50

### 9.3 Data lane 1.2 controls

| Re        | egister Name       | Access |        | Local<br>Address     |                                                                                            | Description                                                              |  |  |

|-----------|--------------------|--------|--------|----------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|--|

| data_la   | data_lane1_reg1 R/ |        | 0x09   |                      |                                                                                            | General controls of data lane1.2                                         |  |  |

| Bit<br>No | Bit Name           |        |        | Default Des<br>Value |                                                                                            | Description                                                              |  |  |

| [7:2]     | Reserved           |        | 000000 |                      | Reserved                                                                                   |                                                                          |  |  |

| 1         | Swap_pins_data     | _lane  | 0      |                      | 0= Sw                                                                                      | P and N pins<br>ap disabled<br>ap enabled (DATA2P1, DATA2N1 are swapped) |  |  |

| 0         | Enable_data_lan    | е      | 0      |                      | Enable data lane 1.2 (DATA1P1 and DATA1N1 0= Disable data lane 1.2 1= Enable data lane 1.2 |                                                                          |  |  |

| Reg<br>Nar | ister<br>ne          | Access               |                      | ocal<br>ddress | Description                                                                                                                                            |  |  |

|------------|----------------------|----------------------|----------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| data_lan   | e1_reg2              | R/W                  | 0x                   | 0A             | CCP/CSI controls of data lane 1.2                                                                                                                      |  |  |

| Bit No     | Bit Nam              | ie                   | Defa<br>ultVa<br>lue |                | Description                                                                                                                                            |  |  |

| [7:4]      | Reserved             | served 0000          |                      | 0000           | Reserved                                                                                                                                               |  |  |

| 3          | hs_rx_te<br>VDS      | rm_e_subI            | bL 0                 |                | High Speed termination enable for CCP mode (unsused in CSI mode)  0= Disable HS termination  1= Enable HS termination, mandatory for CCP mode          |  |  |

| 2          | hs_rx_e_             | e_e_subLVDS 0        |                      | 0              | High Speed Receiver enable for CCP mode (unsused in CSI mode) 0= Disable HS receiver 1= Enable HS receiver, mandatory for CCP mode                     |  |  |

| 1          | hs_rx_w<br>VDS_da    | akeup_sub<br>ta_lane | )L                   | 0              | High Speed Receiver wake-up enable for CCP mode (unsused in CSI mode)  0= HS-receiver in low power mode  1= Enable HS receiver, mandatory for CCP mode |  |  |

| 0          | cntrl_mi<br>S_data_l | pi_subLVI<br>ane     | D                    | 0              | Select CSI or CCP mode 0= SMIA CCP 1= MIPI CSI                                                                                                         |  |  |

DS12803 - Rev 1 page 19/50

|                 | Register Name Access |                  |        | Loc:<br>Addr |          | Description                                                                                                                               |

|-----------------|----------------------|------------------|--------|--------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| data_lan        | data_lane1_reg3 RO   |                  |        | 0x0B         |          | CSI status of the data lane 1.2                                                                                                           |

| Bit No Bit Name |                      | Default<br>Value |        | Desc         | cription |                                                                                                                                           |

| [7:2]           | Reserved             |                  | 000000 |              | Reserved |                                                                                                                                           |

| 1               | ulp_active_not_data  | data_lane        |        | 0            |          | a low-power state active 0= The clock lane is not in ULP state or prepare to leave ULP state 1= The clock lane has reached the ULP state. |

| 0               | stop_state_data_lane | е 0              |        | 0            |          | e in stop state<br>signal indicates that the lane module is in<br>P state.                                                                |

| Reg             | gister Name   | Access      |   | Loc<br>Add       |                                   | Description                                             |  |  |

|-----------------|---------------|-------------|---|------------------|-----------------------------------|---------------------------------------------------------|--|--|

| data_lane1_reg4 |               | RO          |   | 0x08             |                                   | CSI proocol error status registers of the data lane 1.2 |  |  |

| Bit No          | Bit Name      | Def         |   | Default<br>Value |                                   | ription                                                 |  |  |

| [7:6]           | Reserved      | 00          |   | )                |                                   | Reserved                                                |  |  |

| 5               | err_control   |             | 0 |                  | Unexpected control sequence error |                                                         |  |  |

| 4               | err_sync_esc  |             | 0 |                  | Escape synchronization error      |                                                         |  |  |

| 3               | err_esc       |             | 0 |                  | Error during escape command       |                                                         |  |  |

| 2               | err_eot_sync_ | eot_sync_hs |   | 0                |                                   | Error during high-speed end of transmission (EoT)       |  |  |

| 1               | err_sot_sync_ | hs 0        |   |                  | Sync                              | chronization error during high-speed SoT                |  |  |

| 0               | err_sot_hs    |             | 0 |                  | Erro                              | r during high-speed start of transmission (SoT)         |  |  |

DS12803 - Rev 1 page 20/50

# 9.4 Clock lane 2 registers

| Re        | egister Name                                          | Access |                  | Local<br>Address                                                            |      | Description                                                                                                                                   |  |  |

|-----------|-------------------------------------------------------|--------|------------------|-----------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| clk_laı   | ne_reg1_c2                                            | R/W    |                  | 0x31                                                                        |      | General and CSI controls of clock lane2                                                                                                       |  |  |

| Bit<br>No | Bit Name                                              |        | Default<br>Value |                                                                             | Desc | Description                                                                                                                                   |  |  |

| 7         | ui_x4_clk_lane[:                                      | 5]     | 0                | 0                                                                           |      | control (unused in CCP mode) :Unit interval time multi-                                                                                       |  |  |

| 6         | ui_x4_clk_lane[4] ui_x4_clk_lane[3] ui_x4_clk_lane[2] |        | 1 -              | plied by four  This signal indicates the bit period in units of 0.25 ns. If |      |                                                                                                                                               |  |  |

| 5         |                                                       |        |                  | the unit interval is 3 ns, twelve (0x0C) should be pro-                     |      |                                                                                                                                               |  |  |

| 4         |                                                       |        |                  |                                                                             | ı    | grammed. This value is used to generate delays. There-<br>fore, if the period is not a multiple of 0.25 ns, the value                         |  |  |

| 3         | ui_x4_clk_lane[                                       | 1]     |                  |                                                                             | ı    | should be rounded down. For example, a 600 Mbit/s sin-                                                                                        |  |  |

| 2         | ui_x4_clk_lane[(                                      | 0]     |                  |                                                                             |      | gle lane linkuses a unit interval of 1.667 ns. Multiplying by four results in 6.667. In this case, a value of 6 (not 7) should be programmed. |  |  |

| 1         | swap_pins_clk_l                                       | ane    | 0                |                                                                             |      | p P and N pins 0 = Swap enabled (CLKP2 and CLKN2 are swapped) 1= Swap disabled                                                                |  |  |

| 0         | Enable                                                |        | 0                |                                                                             | Enal | ole clock lane module (CLKP1 and CLKN1)  0= Disable clock lane 1  1= Enable clock lane 1                                                      |  |  |

DS12803 - Rev 1 page 21/50

| Re        | gister Name                       | Access      |                  | Local<br>ddress |                                                                                                                                                        | Description                                                                                                                                   |  |  |

|-----------|-----------------------------------|-------------|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| clk_lan   | e_reg3_c2                         | R/W         | 0x.              | 33              | C                                                                                                                                                      | CP/CSI controls of the clock lane 2                                                                                                           |  |  |

| Bit<br>No |                                   |             | Default<br>Value |                 | Description                                                                                                                                            |                                                                                                                                               |  |  |

| [7:5]     | Reserved                          |             |                  | 000             |                                                                                                                                                        | Reserved                                                                                                                                      |  |  |

| 4         | hs_rx_term_e_subLVDS_clk_la<br>ne |             |                  | 0               |                                                                                                                                                        | High Speed termination enable for CCP mode (unsused in CSI mode)  0= Disable HS termination  1= Enable HS termination, mandatory for CCP mode |  |  |

| 3         | hs_rx_e_subLVDS_clk_lane          |             |                  | 0               |                                                                                                                                                        | High Speed Receiver enable for CCP mode (unsused in CSI mode)  0= Disable HS receiver  1= Enable HS receiver, mandatory for CCP mode          |  |  |

| 2         | hs_rx_wakeup_subLVDS_clk_l ane    |             | 0                |                 | High Speed Receiver wake-up enable for CCP mode (unsused in CSI mode)  0= HS-receiver in low power mode  1= Enable HS receiver, mandatory for CCP mode |                                                                                                                                               |  |  |

| 1         | cntrl_mipi_subL                   | VDS_clk_lar | ne               | 0               |                                                                                                                                                        | Select CSI or CCP mode<br>0= SMIA CCP<br>1= MIPI CSI                                                                                          |  |  |

| 0         | Reserved                          |             |                  | 0               |                                                                                                                                                        | Reserved                                                                                                                                      |  |  |

|           | Register Name          | Acce | SS               | A | Local<br>Address | Description                                                                                                                                       |  |

|-----------|------------------------|------|------------------|---|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| clk_la    | clk_lane_wr_reg1_c2 RO |      |                  | 0 | x39              | CSI clock lane 2 status                                                                                                                           |  |

| Bit<br>No | Bit Name               |      | Default<br>Value |   | Description      |                                                                                                                                                   |  |

| [7:2]     | Reserved 000           |      | 000000           |   | Reserved         | d                                                                                                                                                 |  |

| 1         | ulp_active_not_clk_lar | ne   | 0                |   |                  | CSI Ultra low-power state active 0= The clock lane is not in ULP state or prepare to leave ULP state 1= The clock lane has reached the ULP state. |  |

| 0         | stop_state_clk_lane    |      | 0                |   |                  | CSI Lane in stop state This signal indicates that the lane module is in STOP state.                                                               |  |

DS12803 - Rev 1 page 22/50

## 9.5 Data lane 2 controls

|           | Register Name Access |    |   | Loc<br>Addr      |  | Description                                                                                |  |  |

|-----------|----------------------|----|---|------------------|--|--------------------------------------------------------------------------------------------|--|--|

| data_la   | data_lane3_reg1 R/W  |    |   | 0x34             |  | General controls of data lane 2 (DATA1P2 and DATA1N2)                                      |  |  |

| Bit<br>No | Bit Name             |    |   | Default<br>Value |  | Description                                                                                |  |  |

| [7:2]     | Reserved             | 00 |   | 000000           |  | Reserved                                                                                   |  |  |

| 1         | Swap_pins_data_lane  |    | 0 | 0                |  | p P and N pins<br>0= Swap disabled<br>1= Swap enabled (DATA1P2 and DATA1N2 are<br>swapped) |  |  |

| 0         | Enable_data_lane     | 0  |   | Е                |  | ole data lane 1.1 (DATA1P2 and DATA1N2)<br>0= Disable data lane 2<br>1= Enable data lane 2 |  |  |

| Re        | gister Name                        | Access       |      | Local<br>Address |  | Description                                                                                                                                            |  |  |

|-----------|------------------------------------|--------------|------|------------------|--|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| data_la   | ine3_reg2                          | R/W          | 0x35 | 35 (             |  | CCP/CSI controls of data lane 2                                                                                                                        |  |  |

| Bit<br>No |                                    |              | -    | Default<br>Value |  | Description                                                                                                                                            |  |  |

| [7:4]     | Reserved                           |              |      | 000              |  | Reserved                                                                                                                                               |  |  |

| 3         | hs_rx_term_e_subLVDS               |              |      |                  |  | High Speed termination enable for CCP mode (unsused in CSI mode)  0= Disable HS termination  1= Enable HS termination, mandatory for CCP mode          |  |  |

| 2         | hs_rx_e_subLVDS                    |              |      | 0                |  | High Speed Receiver enable for CCP mode (unsused in CSI mode)  0= Disable HS receiver  1= Enable HS receiver, mandatory for CCP mode                   |  |  |

| 1         | hs_rx_wakeup_subLVDS_data_<br>lane |              | a_ 0 | 0                |  | High Speed Receiver wake-up enable for CCP mode (unsused in CSI mode)  0= HS-receiver in low power mode  1= Enable HS receiver, mandatory for CCP mode |  |  |

| 0         | cntrl_mipi_subI                    | .VDS_data_la | ne 0 |                  |  | Select CSI or CCP mode<br>0= SMIA CCP<br>1= MIPI CSI                                                                                                   |  |  |

DS12803 - Rev 1 page 23/50

|           | Register Name Access   |                           |                           |    | Local<br>Address | Description                                                                                                                                           |  |

|-----------|------------------------|---------------------------|---------------------------|----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| data_la   | data_lane3_reg3 RC     |                           |                           | 0x | кЗА              | CSI status of data lane 2                                                                                                                             |  |

| Bit<br>No |                        |                           | Default Descripe<br>Value |    | Descript         | tion                                                                                                                                                  |  |

| [7:2]     | :2] Reserved           |                           | 000000                    |    | Reserved         |                                                                                                                                                       |  |

| 1         | ulp_active_not_data_la | not_data_lane 0(u in 0 mo |                           | d  |                  | CSI Ultra low-power state active  0 = The clock lane is not in ULP state or prepare to leave ULP state  1 = The clock lane has reached the ULP state. |  |

| 0         | stop_state_data_lane   | 0                         |                           |    |                  | CSI Lane in stop state This signal indicates that the lane module is in STOP state.                                                                   |  |

| I         | Register Name   | Acces | s               | Lo<br>Add   |                                                     | Description                                                                                                                                                                                                                                                                                                                           |  |  |

|-----------|-----------------|-------|-----------------|-------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| data_lar  | ne3_reg4        | RO    |                 | 0x3E        | 3                                                   | CSI protocoleError status registers of data lane 2                                                                                                                                                                                                                                                                                    |  |  |

| Bit<br>No |                 |       | Defaul<br>Value | t           | Description                                         |                                                                                                                                                                                                                                                                                                                                       |  |  |

| [7:6]     | Reserved        |       | 0               |             | Reser                                               | ved                                                                                                                                                                                                                                                                                                                                   |  |  |

| 5         | err_control     | 0     |                 | 0           |                                                     | Unexpected control sequence error This signal is asserted when an incorrect line state sequence is detected. For example, if a turn-around request or escape mode request is immediately followed by a stop state instead of the required bridge state, this signal is asserted and remains high until the next change in line state. |  |  |

| 4         | err_sync_esc    | 0     |                 | I<br>t<br>s |                                                     | Escape synchronization error If the number of bits received during a low-power data transmission is not a multiple of eight when the transmission ends, this signal is asserted and remains high until the next change in line state.                                                                                                 |  |  |

| 3         | err_esc         | 0     |                 | 0           |                                                     | Error during escape command If an unrecognized escape entry command is received, this signal is asserted and remains high until the next change in line state.                                                                                                                                                                        |  |  |

| 2         | err_eot_sync_hs |       | 0               |             | Error during high-speed end of transmission (EoT)   |                                                                                                                                                                                                                                                                                                                                       |  |  |

| 1         | err_sot_sync_hs |       | 0               |             | Synchronization error during high-speed SoT         |                                                                                                                                                                                                                                                                                                                                       |  |  |

| 0         | err_sot_hs      |       | 0               |             | Error during high-speed start of transmission (SoT) |                                                                                                                                                                                                                                                                                                                                       |  |  |

DS12803 - Rev 1 page 24/50

# 9.6 CCP RX and error flag registers

| Regist   | er Name  | Access | Local<br>Address | Description                                                                                                                                                                                                                                                                                |  |  |  |

|----------|----------|--------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| ccp_rx_i | reg1     | R/W    | 0x0D             | CCP Data clock/data strobe mode selection and Error signal control                                                                                                                                                                                                                         |  |  |  |

| Bit No   | Bit Name |        | Default<br>Value | Description                                                                                                                                                                                                                                                                                |  |  |  |

| 7        | Delay[4] |        | 0                | Error Signals (pulses) generated are valid for short                                                                                                                                                                                                                                       |  |  |  |

| 6        | Delay[3] |        |                  | duration (4 input DDR clocks).  To be able to capture this in I2C registers working on                                                                                                                                                                                                     |  |  |  |

| 5        | Delay[2] |        |                  | host clock, these Error pulses need to stretched (dura-                                                                                                                                                                                                                                    |  |  |  |

| 4        | Delay[1] |        |                  | tion of pulses need to be increased). This pulse stretching is programmable.                                                                                                                                                                                                               |  |  |  |

| 3        | Delay[0] |        |                  | Delay value is multiplied by 16 for single lane & by 8 for dual lane. For example: If original pulse width is 4 clocks and Register Value is 3 specifies for dual lane system. The resultant Pulse captured will be 4 (original clocks) + 3 (programmed value) * 8 (dual lane) = 28 clocks |  |  |  |

| 2        | Reserved |        | 0                | Reserved                                                                                                                                                                                                                                                                                   |  |  |  |

| 1        | Reserved |        | 0                | Reserved                                                                                                                                                                                                                                                                                   |  |  |  |

| 0        | DS_MODI  | 3      | 0                | Selects between CCP Data-Strobe mode and Data-Clock mode for the main camera (unuse in CSI)  DC_MODE=0 -> Data clock mode  DS_MODE= 1 -> Data strobe mode                                                                                                                                  |  |  |  |

| 1        | Register Access<br>Name |                    | Local<br>Address   |      | Description                                                          |                                        |  |  |

|----------|-------------------------|--------------------|--------------------|------|----------------------------------------------------------------------|----------------------------------------|--|--|

| ccp_rx_i | reg2                    | R/W                |                    | 0x0E |                                                                      | CCP controls                           |  |  |

| Bit No   |                         |                    | Default D<br>Value |      | Description                                                          |                                        |  |  |

| 7        | Reserved                | 0                  |                    | 0 R  |                                                                      | Reserved                               |  |  |

| 6        | Clr_glue_s              | sync_error 0       |                    |      | Clear                                                                | sync error in CCP path                 |  |  |

| 5        | pix_width               | _ccp_rx[3]         | 0                  |      | Pixel width input in CCP mode (unused in CSI). It should             |                                        |  |  |

| 4        | pix_width               | _ccp_rx[2]         |                    |      | be selected between the allowed pixel widths: 6, 7, 8, 10 or 12-bit. |                                        |  |  |

| 3        | pix_width               | _ccp_rx[1]         |                    |      | Value of this register-slice is binary equivalents of 6, 7,          |                                        |  |  |

| 2        | pix_width               | ix_width_ccp_rx[0] |                    |      |                                                                      | 8, 10 or 12, other values are invalid. |  |  |

| 1        | clr_ccp_sh              | ift_sync           | 0                  |      | Clear                                                                | CCP shift sync flag                    |  |  |

| 0        | clr_ccp_cr              | _crc_error 0       |                    |      | Clear CCP CRC error                                                  |                                        |  |  |

DS12803 - Rev 1 page 25/50

| Reg      | Register Name Access |                    |      | Local<br>Address |                  | Description                              |  |

|----------|----------------------|--------------------|------|------------------|------------------|------------------------------------------|--|

| ccp_rx_r | reg3 RO              |                    | 0x0F |                  |                  | CCP channel and error flags              |  |

| Bit No   | Bit Name             | e Default<br>Value |      |                  |                  |                                          |  |

| 7        | Glue_logic_          | sync_error         | 0 In |                  | Inc              | orrect data length error flag            |  |

| [3-6]    | ccp_channe           | 1[0-3]             | 00   | 00               | Cha              | annel ID extracted from input CCP stream |  |

| 2        | ccp_shift_sy         | ync                | 0    |                  | CC               | P shift sync error flag                  |  |

| 1        | ccp_false_s          | ccp_false_sync 0   |      |                  | CC               | CCP false sync error flag                |  |

| 0        | ccp_crc_error 0      |                    |      | СС               | P CRC error flag |                                          |  |

| Re                 | egister Name | Access | Access Local Add |   |      | Description                                                                                     |  |

|--------------------|--------------|--------|------------------|---|------|-------------------------------------------------------------------------------------------------|--|

| ccp_rx_reg1_c2 R/W |              | R/W    | 0x38             |   |      | Data clock / data strobe selection for the second camera (CLKP2,CLKN2,DATA1P2,DATA1N2)          |  |

| Bit No             | Bit Name     |        | Default<br>Value |   | Desc | cription                                                                                        |  |

| [7:1]              | Reserved     |        | 0000000          |   | Rese | erved                                                                                           |  |