MB95F394H/F396K/F398H/F394K/F396H/F398K

# CMOS F<sup>2</sup>MC-8FX MB95390H Series 8-bit Microcontrollers

MB95390H is a series of general-purpose, single-chip microcontrollers. In addition to a compact instruction set, the microcontrollers of this series contain a variety of peripheral resources.

# Features

# F<sup>2</sup>MC-8FX CPU core

Instruction set optimized for controllers

- Multiplication and division instructions

- 16-bit arithmetic operations

- Bit test branch instructions

- Bit manipulation instructions, etc.

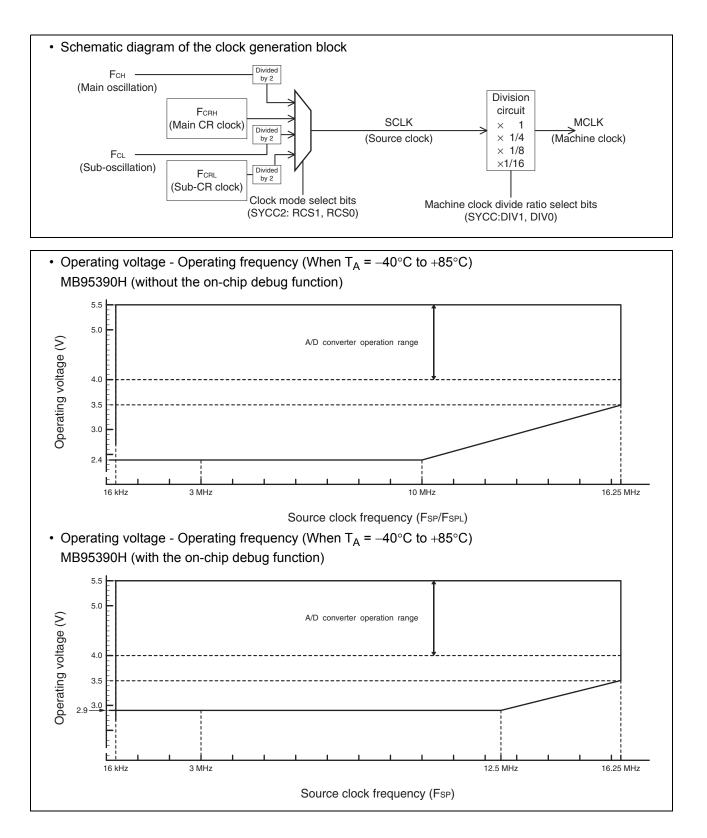

### Clock

Selectable main clock source

Main OSC clock (up to 16.25 MHz, maximum machine clock frequency: 8.125 MHz)

External clock (up to 32.5 MHz, maximum machine clock frequency: 16.25 MHz)

Main CR clock (1/8/10/12.5 MHz  $\pm 2\%$  or  $\pm 2.5\%^*$ , maximum machine clock frequency: 12.5 MHz)

:The main CR clock oscillation accuracy of a product in LQFP package (FPT-48P-M49 or FPT-52P-M02) is  $\pm 2\%$  and that of a product in QFN package (LCC-48P-M11) is  $\pm 2.5\%$ .

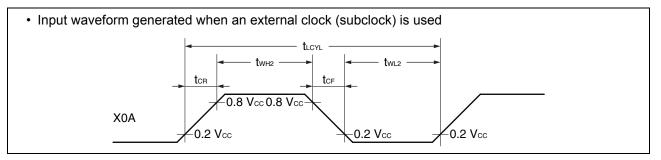

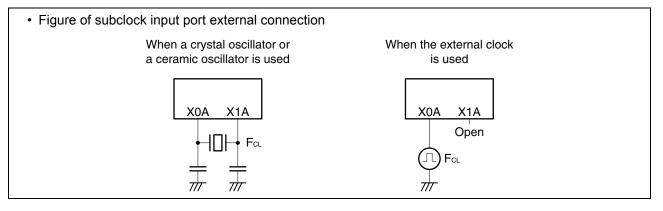

#### Selectable subclock source

Sub-OSC clock (32.768 kHz)

External clock (32.768 kHz)

Sub-CR clock (Typ: 100 kHz, Min: 50 kHz, Max: 200 kHz)

#### Timer

- 8/16-bit composite timer × 2 channels

- 8/16-bit PPG × 3 channels

- 16-bit PPG × 1 channel (can work independently or together with the multi-pulse generator)

- 16-bit reload timer × 1 channel (can work independently or together with the multi-pulse generator)

- Time-base timer × 1 channel

- Watch prescaler × 1 channel

# UART/SIO × 1 channel

- Full duplex double buffer

- Capable of clock-asynchronous (UART) serial data transfer and clock-synchronous (SIO) serial data transfer

### $I^2C \times 1$ channel

Built-in wake-up function

# Multi-pulse generator (MPG) (for DC motor control) $\times$ 1 channel

- 16-bit reload timer × 1 channel

- 16-bit PPG timer × 1 channel

- Waveform sequencer (including a 16-bit timer equipped with a buffer and a compare clear function)

### LIN-UART

- Full duplex double buffer

- Capable of clock-synchronous serial data transfer and clock-asynchronous serial data transfer

### External interrupt × 8 channels

- Interrupt by edge detection (rising edge, falling edge, and both edges can be selected)

- Can be used to wake up the device from different low power consumption (standby) modes

### 8/10-bit A/D converter × 12 channels

8-bit and 10-bit resolution can be chosen.

### Low power consumption (standby) modes

- Stop mode

- Sleep mode

- Watch mode

- Time-base timer mode

### I/O port

- MB95F394H/F396H/F398H (maximum no. of I/O ports: 44)

- General-purpose I/O ports (N-ch open drain).....: 3

- General-purpose I/O ports (CMOS I/O).....: 41

- MB95F394K/F396K/F398K (maximum no. of I/O ports: 45)

- General-purpose I/O ports (N-ch open drain).....: 4 General-purpose I/O ports (CMOS I/O).....: 41

٠

# **On-chip debug**

- 1-wire serial control

- Serial writing supported (asynchronous mode)

# Hardware/software watchdog timer

- Built-in hardware watchdog timer

- Built-in software watchdog timer

# Low-voltage detection reset circuit

Built-in low-voltage detector

## **Clock supervisor counter**

Built-in clock supervisor counter function

## Programmable port input voltage level

CMOS input level / hysteresis input level

### **Dual operation Flash memory**

The erase/write operation and the read operation can be executed in different banks (upper bank/lower bank) simultaneously.

## Flash memory security function

Protects the content of the Flash memory

# Contents

| Product Line-up                         | 4  |

|-----------------------------------------|----|

| Packages and Corresponding Products     | 6  |

| Differences Among Products and Notes on |    |

| Product Selection                       | 7  |

| Pin Assignment                          | 8  |

| Pin Functions                           | 11 |

| I/O Circuit Type                        | 15 |

| Notes On Device Handling                | 18 |

| Pin Connection                          | 18 |

| Power supply pins                       | 18 |

| Block Diagram                           | 20 |

| CPU Core                                | 21 |

| Interrupt Source Table                  | 28 |

| Electrical Characteristics              | 29 |

| Absolute Maximum Ratings                | 29 |

| Recommended Operating Conditions        | 31 |

| DC Characteristics                      | 32 |

| AC Characteristics                      | 35 |

| Clock Timing                            | 35 |

| -                                       |    |

| 4  | Source Clock/Machine Clock               |    |

|----|------------------------------------------|----|

| 6  | External Reset                           |    |

|    | Power-on Reset                           | 40 |

| 7  | Peripheral Input Timing                  | 41 |

| 8  | LIN-UART Timing                          |    |

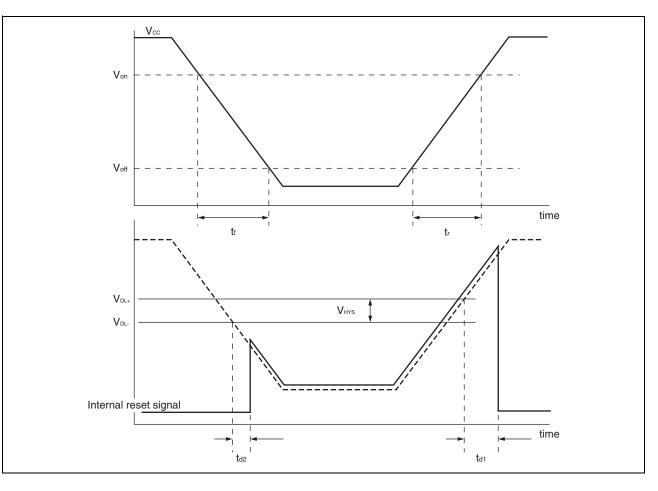

| 11 | Low-voltage Detection                    |    |

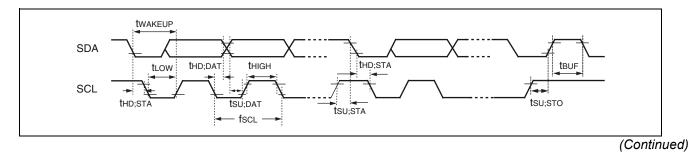

| 15 | I2C Timing                               |    |

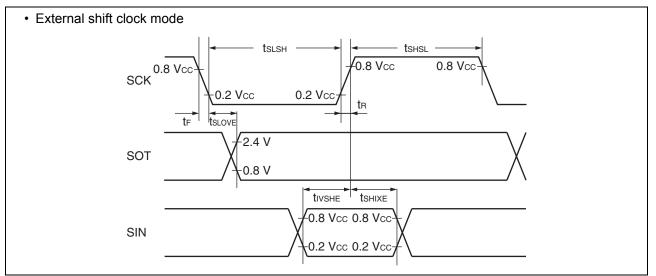

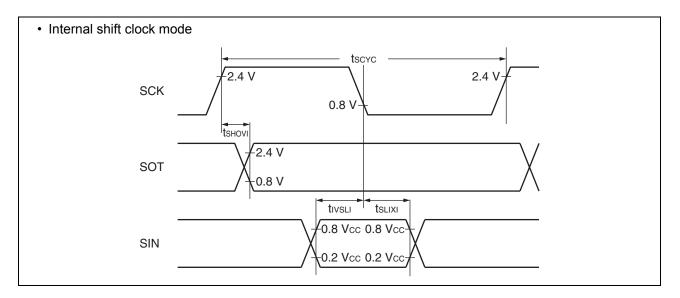

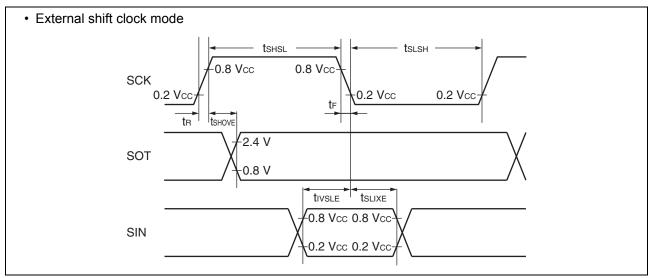

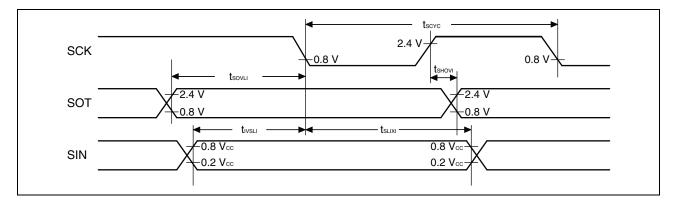

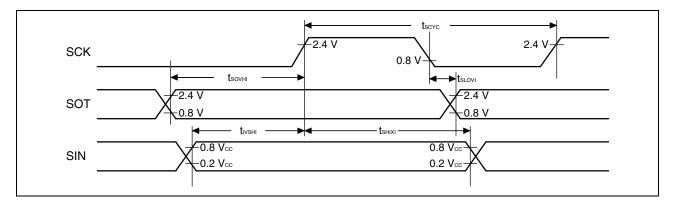

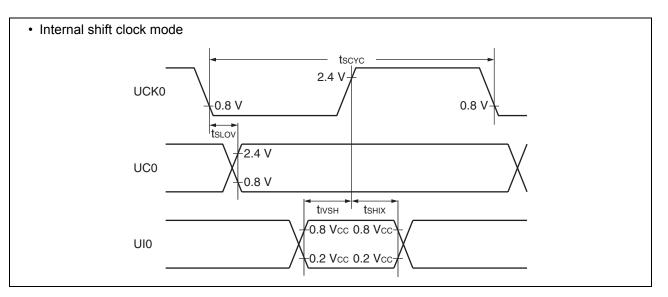

| 18 | UART/SIO, Serial I/O Timing              |    |

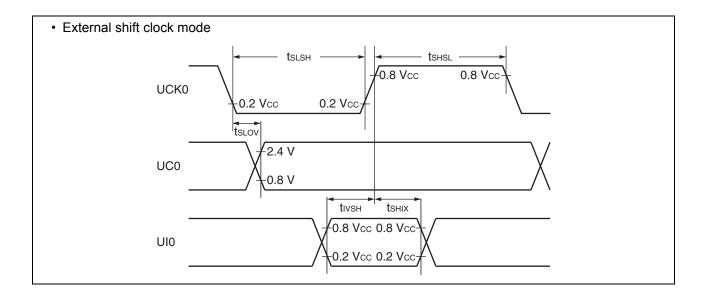

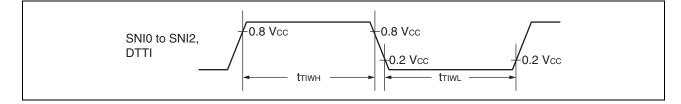

| 18 | MPG Input Timing                         |    |

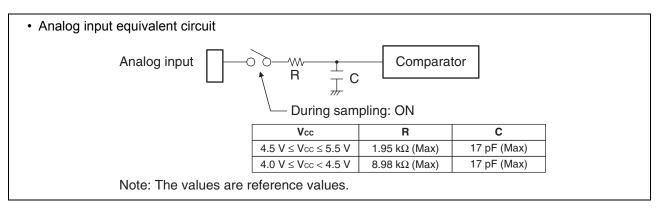

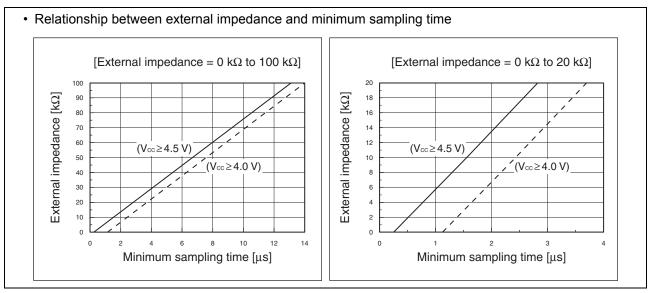

| 18 | A/D Converter                            |    |

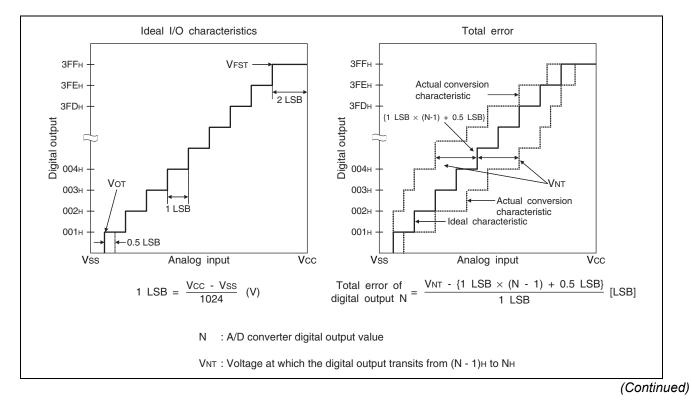

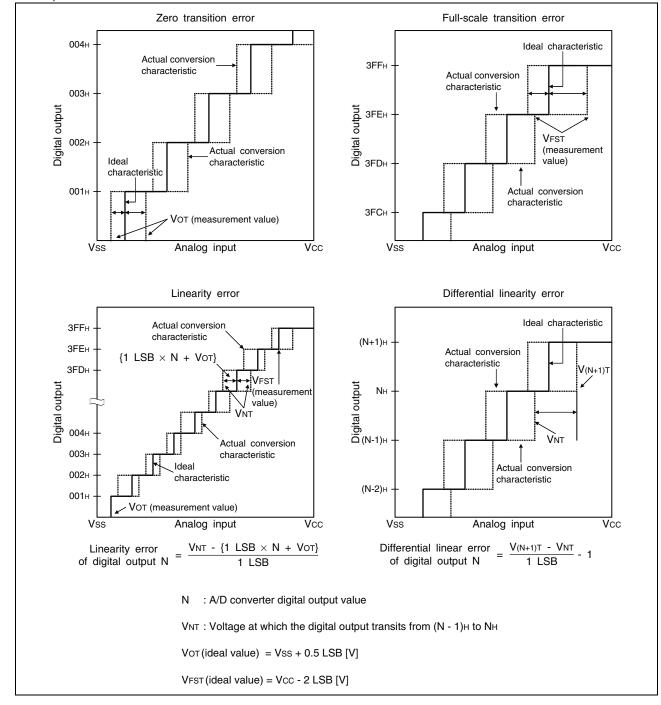

| 20 | A/D Converter Electrical Characteristics |    |

| 21 | Notes on Using the A/D Converter         |    |

| 28 | Definitions of A/D Converter Terms       |    |

| 29 | Flash Memory Write/Erase Characteristics |    |

| 29 | Sample Characteristics                   | 60 |

| 31 | Mask Options                             | 66 |

| 32 | Ordering Information                     |    |

| 35 | Package Dimension                        |    |

| 35 | Major Changes                            |    |

|    |                                          |    |

# 1. Product Line-up

| Part number                         |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |                       |                                                                            |                     |            |  |  |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------|----------------------------------------------------------------------------|---------------------|------------|--|--|--|

|                                     | MB95F394H                                                                                                                                                                                                                                                                                                                                                                                                                         | MB95F396H                                                          | MB95F398H             | MB95F394K                                                                  | MB95F396K           | MB95F398K  |  |  |  |

| Parameter                           |                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |                       |                                                                            |                     |            |  |  |  |

| Туре                                |                                                                                                                                                                                                                                                                                                                                                                                                                                   | •                                                                  | Flash mem             | ory product                                                                | •                   | •          |  |  |  |

| Clock supervisor<br>counter         | It supervises the m                                                                                                                                                                                                                                                                                                                                                                                                               | supervises the main clock oscillation.                             |                       |                                                                            |                     |            |  |  |  |

| Program ROM<br>capacity             | 20 Kbyte                                                                                                                                                                                                                                                                                                                                                                                                                          | 36 Kbyte                                                           | 60 Kbyte              | 20 Kbyte                                                                   | 36 Kbyte            | 60 Kbyte   |  |  |  |

| RAM capacity                        | 496 bytes                                                                                                                                                                                                                                                                                                                                                                                                                         | 1008 bytes                                                         | 2032 bytes            | 496 bytes                                                                  | 1008 bytes          | 2032 bytes |  |  |  |

| Low-voltage<br>detection reset      |                                                                                                                                                                                                                                                                                                                                                                                                                                   | No                                                                 |                       |                                                                            | Yes                 |            |  |  |  |

| Reset input                         |                                                                                                                                                                                                                                                                                                                                                                                                                                   | Dedicated                                                          |                       | Sel                                                                        | ected through softw | /are       |  |  |  |

| CPU functions                       | <ul> <li>Number of basic instructions</li> <li>Instruction bit length</li> <li>Instruction length</li> <li>Data bit length</li> <li>Minimum instruction execution time</li> <li>Interrupt processing time</li> <li>136</li> <li>136</li> <li>136</li> <li>140 3 bytes</li> <li>1, 8 and 16 bits</li> <li>61.5 ns (with machine clock frequency = 16.25 MHz)</li> <li>0.6 μs (with machine clock frequency = 16.25 MHz)</li> </ul> |                                                                    |                       |                                                                            |                     |            |  |  |  |

| General-purpose<br>I/O              | <ul> <li>I/O ports (Max)</li> <li>CMOS I/O</li> <li>N-ch open drain</li> </ul>                                                                                                                                                                                                                                                                                                                                                    | : 44<br>: 41<br>: 3                                                |                       | <ul><li>I/O ports (Max)</li><li>CMOS I/O</li><li>N-ch open drain</li></ul> | : 45<br>: 41<br>: 4 |            |  |  |  |

| Time-base timer                     | Interval time: 0.256                                                                                                                                                                                                                                                                                                                                                                                                              | 3 ms to 8.3 s (with e                                              | external clock freque | ency = 4 MHz)                                                              |                     |            |  |  |  |

| Hardware/software<br>watchdog timer |                                                                                                                                                                                                                                                                                                                                                                                                                                   | n cycle<br>ation clock at 10 Mł<br>ck can be used as tł            |                       | he hardware watch                                                          | dog timer.          |            |  |  |  |

| Wild register                       | It can be used to re                                                                                                                                                                                                                                                                                                                                                                                                              | eplace three bytes o                                               | of data.              |                                                                            |                     |            |  |  |  |

| LIN-UART                            | <ul> <li>Clock-synchronomy</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                             | communication spe<br>ous serial data trans<br>o can be used as a l | fer and clock-asynd   | chronous serial data                                                       |                     | 1.         |  |  |  |

| 8/10-bit A/D                        | 12 channels                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |                       |                                                                            |                     |            |  |  |  |

| converter                           | 8-bit resolution and                                                                                                                                                                                                                                                                                                                                                                                                              | 10-bit resolution ca                                               | an be chosen.         |                                                                            |                     |            |  |  |  |

|                                     | 2 channels                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                    |                       |                                                                            |                     |            |  |  |  |

| 8/16-bit<br>composite timer         | <ul> <li>The timer can be configured as an "8-bit timer × 2 channels" or a "16-bit timer × 1 channel".</li> <li>It has the following functions: timer function, PWC function, PWM function and input capture function.</li> <li>Count clock: it can be selected from internal clocks (seven types) and external clocks.</li> <li>It can output square wave.</li> </ul>                                                            |                                                                    |                       |                                                                            |                     |            |  |  |  |

| External<br>interrupt               | <ul> <li>8 channels</li> <li>Interrupt by edge detection (The rising edge, falling edge, or both edges can be selected.)</li> <li>It can be used to wake up the device from different standby modes.</li> </ul>                                                                                                                                                                                                                   |                                                                    |                       |                                                                            |                     |            |  |  |  |

| On-chip debug                       | <ul><li>1-wire serial con</li><li>It supports serial</li></ul>                                                                                                                                                                                                                                                                                                                                                                    | trol<br>I writing. (asynchror                                      | nous mode)            |                                                                            |                     |            |  |  |  |

| Part number                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |                                           |                                           |                    |                     |  |  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------|-------------------------------------------|--------------------|---------------------|--|--|

|                                                    | MB95F394H                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MB95F396H           | MB95F398H                                 | MB95F394K                                 | MB95F396K          | MB95F398K           |  |  |

| Parameter                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |                                           |                                           |                    |                     |  |  |

| UART/SIO                                           | <ul> <li>1 channel</li> <li>Data transfer with UART/SIO is enabled.</li> <li>It has a full duplex double buffer, variable data length (5/6/7/8 bits), a built-in baud rate generator and an error detection function.</li> <li>It uses the NRZ type transfer format.</li> <li>LSB-first data transfer and MSB-first data transfer are available to use.</li> <li>Clock-asynchronous (UART) serial data transfer and clock-synchronous (SIO) serial data transfer is enabled.</li> </ul> |                     |                                           |                                           |                    |                     |  |  |

| l <sup>2</sup> C                                   | <ul> <li>It has the follow<br/>wake-up functior</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                              |                     | error function, arbit                     | tration function, tran                    |                    | detection function, |  |  |

| 8/16-bit PPG                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     | as two 8-bit PPG ch<br>selected from eigh | nannels or a single f<br>t clock sources. | 16-bit PPG channel |                     |  |  |

| 16-bit PPG                                         | <ul> <li>PWM mode and one-shot mode are available to use.</li> <li>The counter operating clock can be selected from eight clock sources.</li> <li>It supports external trigger start.</li> <li>It can work independently or together with the multi-pulse generator.</li> </ul>                                                                                                                                                                                                         |                     |                                           |                                           |                    |                     |  |  |

| 16-bit reload timer                                | <ul> <li>Two clock modes and two counter operating modes are available to use.</li> <li>It can output square waveform.</li> <li>Count clock: it can be selected from internal clocks (seven types) and external clocks.</li> <li>Two counter operating modes: reload mode and one-shot mode</li> <li>It can work independently or together with the multi-pulse generator.</li> </ul>                                                                                                   |                     |                                           |                                           |                    |                     |  |  |

| Multi-pulse<br>generator (for DC<br>motor control) | <ul> <li>16-bit PPG timer: 1 channel</li> <li>16-bit reload timer operations: toggle output, one-shot output</li> <li>Event counter: 1 channel</li> <li>Waveform sequencer (including a 16-bit timer equipped with a buffer and a compare clear function)</li> </ul>                                                                                                                                                                                                                    |                     |                                           |                                           |                    |                     |  |  |

| Watch prescaler                                    | Eight different time                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | intervals can be se | elected.                                  |                                           |                    |                     |  |  |

| Flash memory                                       | <ul> <li>It supports automatic programming, Embedded Algorithm, and write/erase/erase-suspend/erase-resume commands.</li> <li>It has a flag indicating the completion of the operation of Embedded Algorithm.</li> <li>Number of write/erase cycles: 100000</li> <li>Data retention time: 20 years</li> <li>Flash security feature for protecting the content of the Flash memory</li> </ul>                                                                                            |                     |                                           |                                           |                    |                     |  |  |

| Standby mode                                       | Sleep mode, stop r                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | node, watch mode,   | time-base timer me                        | ode                                       |                    |                     |  |  |

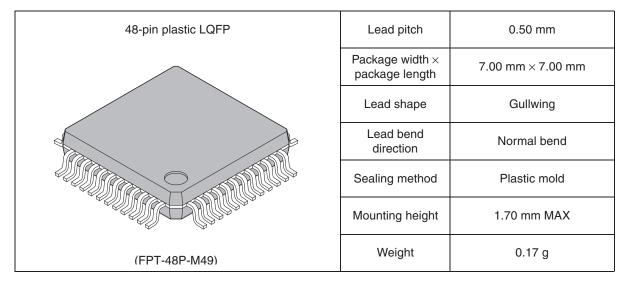

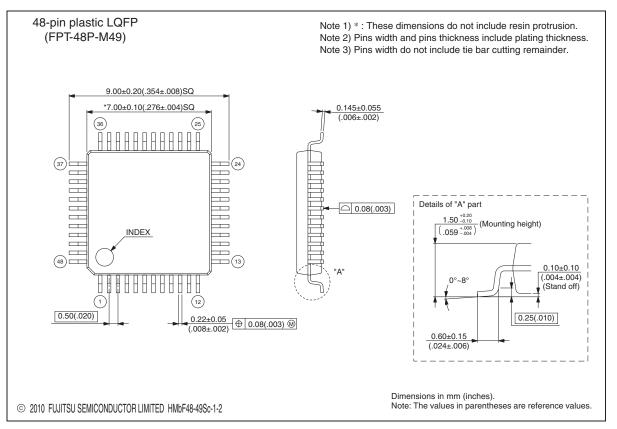

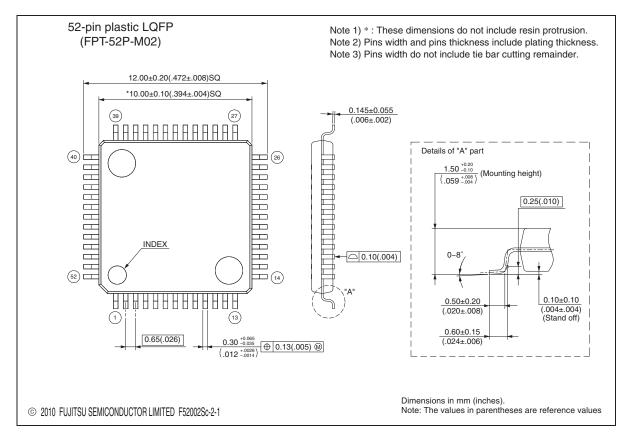

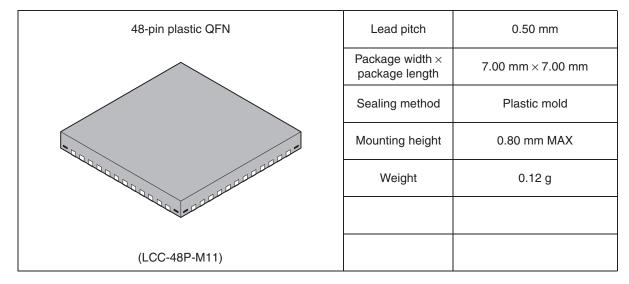

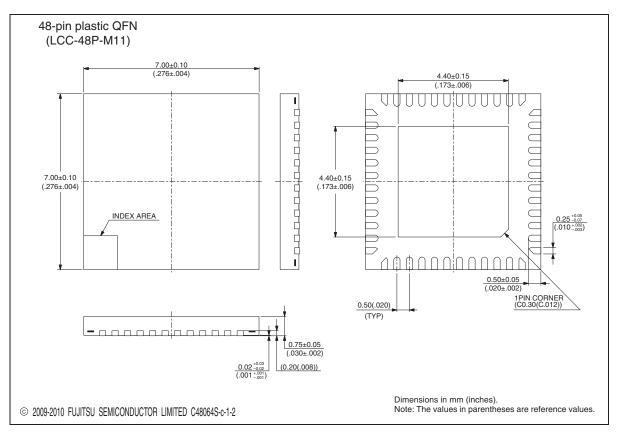

| Package                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     | FPT-52                                    | 3P-M49<br>2P-M02<br>8P-M11                |                    |                     |  |  |

# 2. Packages and Corresponding Products

| Part number<br>Package | MB95F394H | MB95F396H | MB95F398H | MB95F394K | MB95F396K | MB95F398K |

|------------------------|-----------|-----------|-----------|-----------|-----------|-----------|

| FPT-48P-M49            | 0         | 0         | 0         | 0         | 0         | 0         |

| FPT-52P-M02            | 0         | 0         | 0         | 0         | 0         | 0         |

| LCC-48P-M11            | 0         | 0         | 0         | 0         | 0         | 0         |

O: Available

# 3. Differences Among Products and Notes on Product Selection

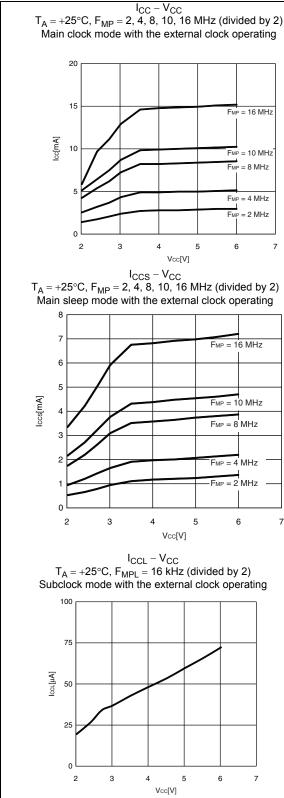

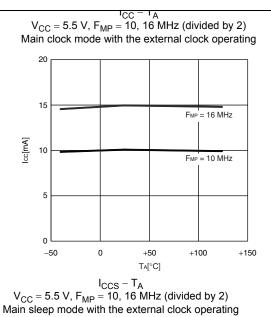

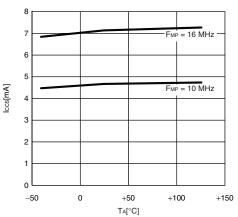

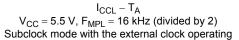

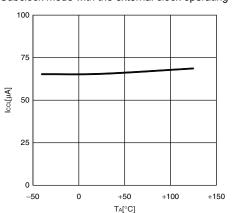

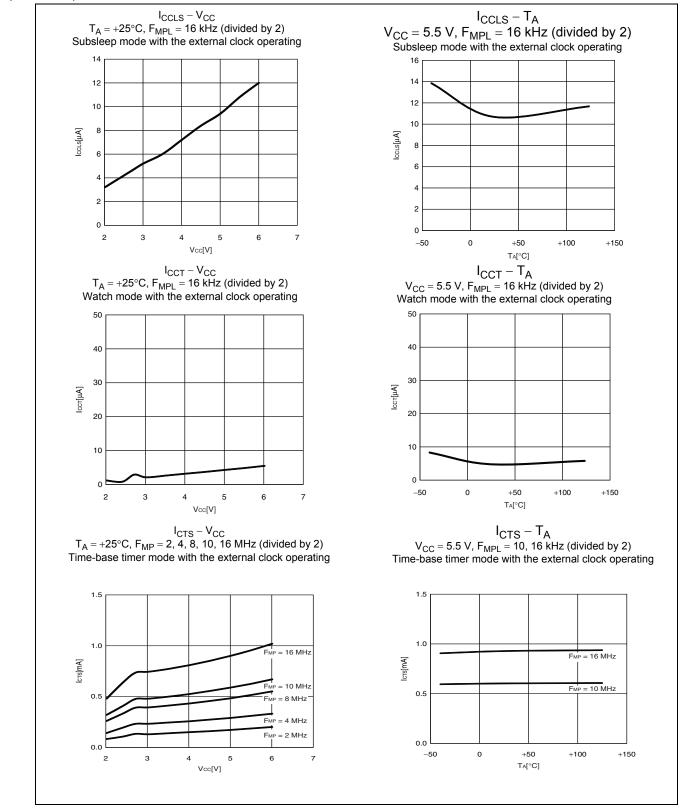

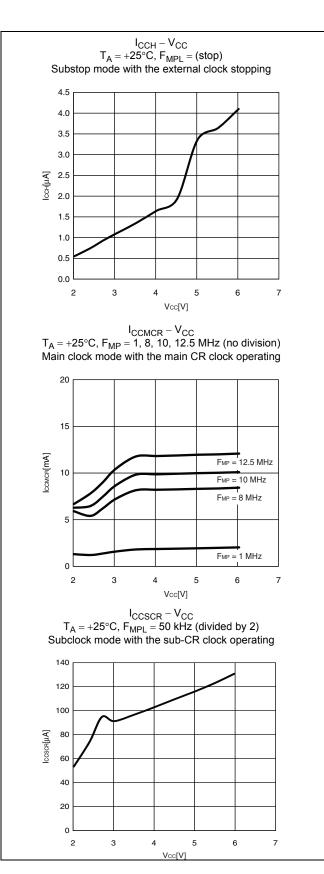

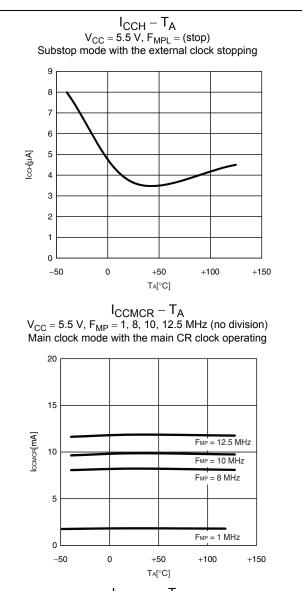

#### Current consumption

When using the on-chip debug function, take account of the current consumption of flash erase/write. For details of current consumption, see "Electrical Characteristics".

#### Package

For details of information on each package, see "Packages and Corresponding Products" and "Package Dimension".

#### Operating voltage

The operating voltage varies, depending on whether the on-chip debug function is used or not. For details of the operating voltage, see "Electrical Characteristics".

#### On-chip debug function

The on-chip debug function requires that  $V_{CC}$ ,  $V_{SS}$  and one serial wire be connected to an evaluation tool. For details of the connection method, refer to "CHAPTER 29 EXAMPLE OF SERIAL PROGRAMMING CONNECTION" in the hardware manual of the MB95390H Series.

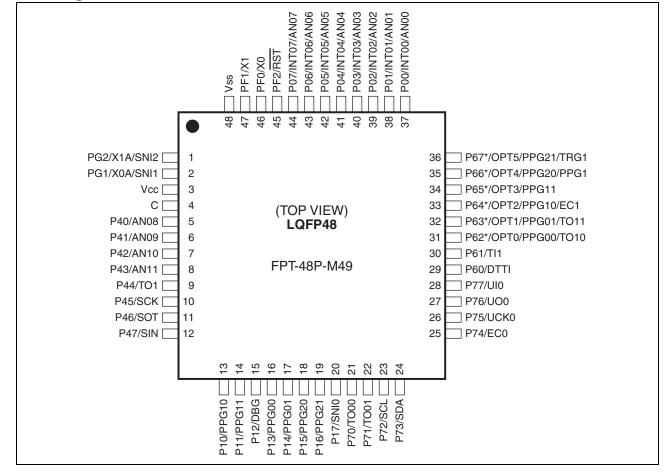

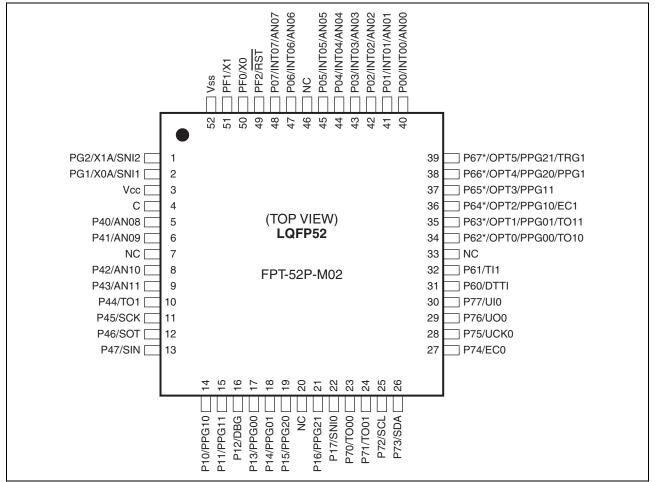

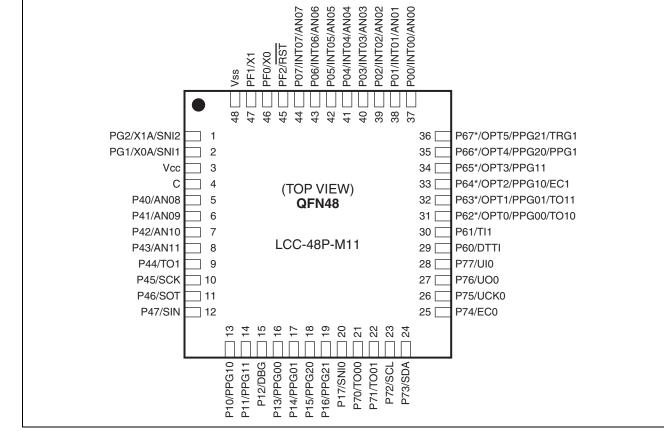

# 4. Pin Assignment

\*: High-current pin (8 mA/12 mA)

\*: High-current pin (8 mA/12 mA)

\*: High-current pin (8 mA/12 mA)

# 5. Pin Functions

| Pin no.              |                     |                      | Pin l/O         |                               |                                                                                     |

|----------------------|---------------------|----------------------|-----------------|-------------------------------|-------------------------------------------------------------------------------------|

| LQFP48* <sup>1</sup> | QFN48* <sup>2</sup> | LQFP52* <sup>3</sup> | name            | circuit<br>type* <sup>4</sup> | Function                                                                            |

|                      |                     |                      | PG2             |                               | General-purpose I/O port                                                            |

| 1                    | 1                   | 1                    | X1A             | с                             | Subclock I/O oscillation pin                                                        |

|                      | I                   |                      | SNI2            |                               | Trigger input pin for the position detection function of the MPG waveform sequencer |

|                      |                     |                      | PG1             |                               | General-purpose I/O port                                                            |

| 2                    | 2                   | 2                    | X0A             | с                             | Subclock input oscillation pin                                                      |

| _                    | -                   | _                    | SNI1            |                               | Trigger input pin for the position detection function of the MPG waveform sequencer |

| 3                    | 3                   | 3                    | V <sub>CC</sub> | —                             | Power supply pin                                                                    |

| 4                    | 4                   | 4                    | С               | —                             | Capacitor connection pin                                                            |

| 5                    | 5                   | 5                    | P40             | к                             | General-purpose I/O port                                                            |

| 5                    | 5                   | 5                    | AN08            | n.                            | A/D converter analog input pin                                                      |

| 6                    | 6                   | 6                    | P41             | к                             | General-purpose I/O port                                                            |

| 0                    | 0                   | 0                    | AN09            |                               | A/D converter analog input pin                                                      |

| —                    | —                   | 7                    | NC              | —                             | It is an internally connected pin. Always leave it unconnected.                     |

| 7                    | 7                   | 8                    | P42             | к                             | General-purpose I/O port                                                            |

| 1                    | 1                   | 0                    | AN10            |                               | A/D converter analog input pin                                                      |

| 8                    | 8                   | 9                    | P43             | к                             | General-purpose I/O port                                                            |

| 0                    | 0                   | 9                    | AN11            | Γ.                            | A/D converter analog input pin                                                      |

| 9                    | 9                   | 10                   | P44             | G                             | General-purpose I/O port                                                            |

| 3                    | 3                   | 10                   | TO1             | 0                             | 16-bit reload timer ch. 0 output pin                                                |

| 10                   | 10                  | 11                   | P45             | G                             | General-purpose I/O port                                                            |

| 10                   | 10                  |                      | SCK             | 0                             | LIN-UART clock I/O pin                                                              |

| 11                   | 11                  | 12                   | P46             | G                             | General-purpose I/O port                                                            |

|                      | 11                  | 12                   | SOT             | 0                             | LIN-UART data output pin                                                            |

| 12                   | 12                  | 13                   | P47             | J                             | General-purpose I/O port                                                            |

| 12                   | 12                  | 10                   | SIN             | 0                             | LIN-UART data input pin                                                             |

| 13                   | 13                  | 14                   | P10             | G                             | General-purpose I/O port                                                            |

| 15                   | 15                  | 14                   | PPG10           | 0                             | 8/16-bit PPG ch. 1 output pin                                                       |

| 14                   | 14                  | 15                   | P11 G           |                               | General-purpose I/O port                                                            |

| 14                   | 17                  | 10                   | PPG11           |                               | 8/16-bit PPG ch. 1 output pin                                                       |

| 15                   | 15                  | 16                   | P12             | н                             | General-purpose I/O port                                                            |

|                      | 10                  | 10                   | DBG             |                               | DBG input pin                                                                       |

| 16                   | 16                  | 17                   | P13             | G                             | General-purpose I/O port                                                            |

| 10                   |                     | 17                   | PPG00           |                               | 8/16-bit PPG ch. 0 output pin                                                       |

|                      | Pin no.             |                      | Pin I/O |                               | -                                                                                   |

|----------------------|---------------------|----------------------|---------|-------------------------------|-------------------------------------------------------------------------------------|

| LQFP48* <sup>1</sup> | QFN48* <sup>2</sup> | LQFP52* <sup>3</sup> | name    | circuit<br>type* <sup>4</sup> | Function                                                                            |

| 17                   | 17                  | 18                   | P14     | G                             | General-purpose I/O port                                                            |

| 17                   | 17                  | 10                   | PPG01   | U                             | 8/16-bit PPG ch. 0 output pin                                                       |

| 18                   | 18                  | 19                   | P15     | G                             | General-purpose I/O port                                                            |

| 10                   | 10                  | 15                   | PPG20   | U                             | 8/16-bit PPG ch. 2 output pin                                                       |

| —                    | _                   | 20                   | NC      | _                             | It is an internally connected pin. Always leave it unconnected.                     |

| 19                   | 19                  | 21                   | P16     | G                             | General-purpose I/O port                                                            |

| 15                   | 19                  | 21                   | PPG21   | U                             | 8/16-bit PPG ch. 2 output pin                                                       |

|                      |                     |                      | P17     |                               | General-purpose I/O port                                                            |

| 20                   | 20                  | 22                   | SNI0    | G                             | Trigger input pin for the position detection function of the MPG waveform sequencer |

| 21                   | 21                  | 23                   | P70     | G                             | General-purpose I/O port                                                            |

| 21                   | 21                  | 25                   | TO00    | 9                             | 8/16-bit composite timer ch. 0 output pin                                           |

| 22                   | 22                  | 24                   | P71     | G                             | General-purpose I/O port                                                            |

| 22                   | 22                  | 24                   | TO01    | 9                             | 8/16-bit composite timer ch. 0 output pin                                           |

| 23                   | 23                  | 25                   | P72     | - 1                           | General-purpose I/O port                                                            |

| 23                   | 23                  | 25                   | SCL     |                               | I <sup>2</sup> C clock I/O pin                                                      |

| 24                   | 24                  | 26                   | P73     |                               | General-purpose I/O port                                                            |

| 24                   | 24                  | 20                   | SDA     | I                             | I <sup>2</sup> C data I/O pin                                                       |

| 25                   | 25                  | 27                   | P74     | G                             | General-purpose I/O port                                                            |

| 25                   | 25                  | 21                   | EC0     | 0                             | 8/16-bit composite timer ch. 0 clock input pin                                      |

| 26                   | 26                  | 28                   | P75     | G                             | General-purpose I/O port                                                            |

| 20                   | 20                  | 20                   | UCK0    | U                             | UART/SIO ch. 0 clock I/O pin                                                        |

| 27                   | 27                  | 29                   | P76     | G                             | General-purpose I/O port                                                            |

| 21                   | 21                  | 25                   | UO0     | 0                             | UART/SIO ch. 0 data output pin                                                      |

| 28                   | 28                  | 30                   | P77     | J                             | General-purpose I/O port                                                            |

| 20                   | 20                  | 50                   | UIO     | 0                             | UART/SIO ch. 0 data input pin                                                       |

| 29                   | 29                  | 31                   | P60     | G                             | General-purpose I/O port                                                            |

| 25                   | 25                  | 01                   | DTTI    | 0                             | MPG waveform sequencer input pin                                                    |

| 30                   | 30                  | 32                   | P61     | G                             | General-purpose I/O port                                                            |

| 50                   | 50                  | 52                   | TI1 G   |                               | 16-bit reload timer ch. 0 input pin                                                 |

| —                    | _                   | 33                   | NC      | —                             | It is an internally connected pin. Always leave it unconnected.                     |

|                      |                     |                      | P62     |                               | General-purpose I/O port<br>High-current pin                                        |

| 31                   | 31                  | 34                   | OPT0    | D                             | MPG waveform sequencer output pin                                                   |

|                      |                     |                      | PPG00   |                               | 8/16-bit PPG ch. 0 output pin                                                       |

|                      |                     |                      | TO10    |                               | 8/16-bit composite timer ch. 1 output pin                                           |

|                      | Pin no.             |                      |       | I/O<br>circuit     | E. w. et a v                                   |

|----------------------|---------------------|----------------------|-------|--------------------|------------------------------------------------|

| LQFP48* <sup>1</sup> | QFN48* <sup>2</sup> | LQFP52* <sup>3</sup> | name  | type* <sup>4</sup> | Function                                       |

|                      |                     |                      | P63   |                    | General-purpose I/O port<br>High-current pin   |

| 32                   | 32                  | 35                   | OPT1  | D                  | MPG waveform sequencer output pin              |

|                      |                     |                      | PPG01 |                    | 8/16-bit PPG ch. 0 output pin                  |

|                      |                     |                      | TO11  |                    | 8/16-bit composite timer ch. 1 output pin      |

|                      |                     |                      | P64   |                    | General-purpose I/O port<br>High-current pin   |

| 33                   | 33                  | 36                   | OPT2  | D                  | MPG waveform sequencer output pin              |

|                      |                     |                      | PPG10 |                    | 8/16-bit PPG ch. 1 output pin                  |

|                      |                     |                      | EC1   |                    | 8/16-bit composite timer ch. 1 clock input pin |

|                      |                     |                      | P65   |                    | General-purpose I/O port<br>High-current pin   |

| 34                   | 34                  | 37                   | OPT3  | D                  | MPG waveform sequencer output pin              |

|                      |                     |                      | PPG11 |                    | 8/16-bit PPG ch. 1 output pin                  |

|                      |                     |                      | P66   |                    | General-purpose I/O port<br>High-current pin   |

| 35                   | 35                  | 38                   | OPT4  | D                  | MPG waveform sequencer output pin              |

|                      |                     |                      | PPG20 |                    | 8/16-bit PPG ch. 2 output pin                  |

|                      |                     |                      | PPG1  |                    | 16-bit PPG ch. 1 output pin                    |

|                      |                     |                      | P67   |                    | General-purpose I/O port<br>High-current pin   |

| 36                   | 36                  | 39                   | OPT5  | D                  | MPG waveform sequencer output pin              |

|                      |                     |                      | PPG21 |                    | 8/16-bit PPG ch. 2 output pin                  |

|                      |                     |                      | TRG1  |                    | 16-bit PPG ch. 1 trigger input pin             |

|                      |                     |                      | P00   |                    | General-purpose I/O port                       |

| 37                   | 37                  | 40                   | INT00 | E                  | External interrupt input pin                   |

|                      |                     |                      | AN00  |                    | A/D converter analog input pin                 |

|                      |                     |                      | P01   |                    | General-purpose I/O port                       |

| 38                   | 38                  | 41                   | INT01 | E                  | External interrupt input pin                   |

|                      |                     |                      | AN01  |                    | A/D converter analog input pin                 |

|                      |                     |                      | P02   |                    | General-purpose I/O port                       |

| 39                   | 39                  | 42                   | INT02 | E                  | External interrupt input pin                   |

|                      |                     |                      | AN02  |                    | A/D converter analog input pin                 |

|                      |                     |                      | P03   |                    | General-purpose I/O port                       |

| 40                   | 40                  | 43                   | INT03 | E                  | External interrupt input pin                   |

|                      |                     |                      | AN03  |                    | A/D converter analog input pin                 |

|                      | Pin no.             |                      |                 | I/O<br>circuit     |                                                                 |

|----------------------|---------------------|----------------------|-----------------|--------------------|-----------------------------------------------------------------|

| LQFP48* <sup>1</sup> | QFN48* <sup>2</sup> | LQFP52* <sup>3</sup> | name            | type <sup>*4</sup> | Function                                                        |

|                      |                     |                      | P04             |                    | General-purpose I/O port                                        |

| 41                   | 41                  | 44                   | INT04           | E                  | External interrupt input pin                                    |

|                      |                     |                      | AN04            |                    | A/D converter analog input pin                                  |

|                      |                     |                      | P05             |                    | General-purpose I/O port                                        |

| 42                   | 42                  | 45                   | INT05           | E                  | External interrupt input pin                                    |

|                      |                     |                      | AN05            |                    | A/D converter analog input pin                                  |

| —                    | —                   | 46                   | NC              | —                  | It is an internally connected pin. Always leave it unconnected. |

|                      | 43                  | 47                   | P06             |                    | General-purpose I/O port                                        |

| 43                   |                     |                      | INT06           | E                  | External interrupt input pin                                    |

|                      |                     |                      | AN06            |                    | A/D converter analog input pin                                  |

|                      | 44                  | 48                   | P07             |                    | General-purpose I/O port                                        |

| 44                   |                     |                      | 48 INT07        | E                  | External interrupt input pin                                    |

|                      |                     |                      | AN07            |                    | A/D converter analog input pin                                  |

|                      |                     |                      | PF2             |                    | General-purpose I/O port                                        |

| 45                   | 45                  | 49                   | RST             | A                  | Reset pin<br>Dedicated reset pin in MB95F394H/F396H/F398H       |

| 46                   | 46                  | 50                   | PF0             | в                  | General-purpose I/O port                                        |

| 40                   | 40                  | 50                   | X0              |                    | Main clock I/O oscillation pin                                  |

| 47                   | 47                  | 51                   | PF1             | в                  | General-purpose I/O port                                        |

| 47                   | 47                  | 51                   | X1              |                    | Main clock I/O oscillation pin                                  |

| 48                   | 48                  | 52                   | V <sub>SS</sub> | —                  | Power supply pin (GND)                                          |

\*1: Package code: FPT-48P-M49

\*2: Package code: LCC-48P-M11

\*3: Package code: FPT-52P-M02

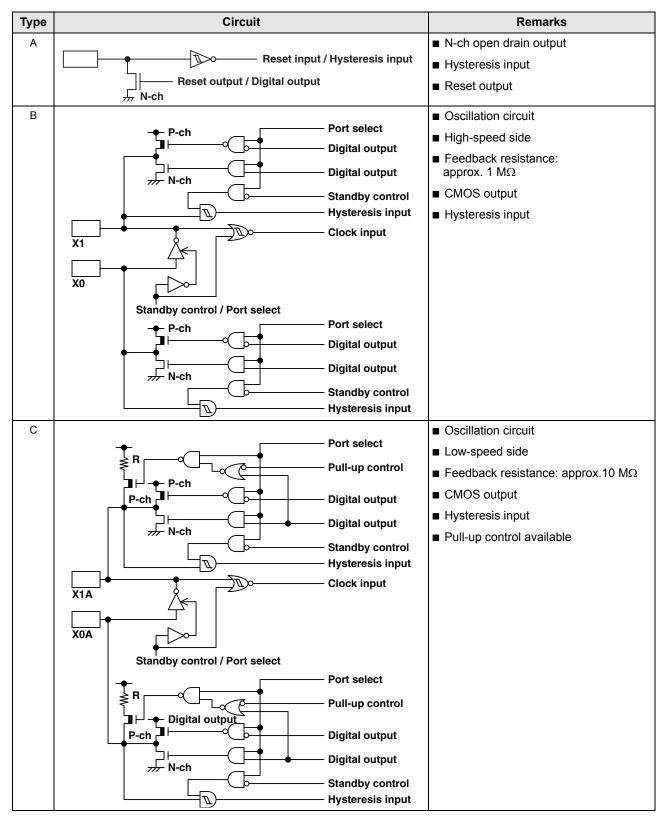

\*4: For the I/O circuit types, see "I/O Circuit Type".

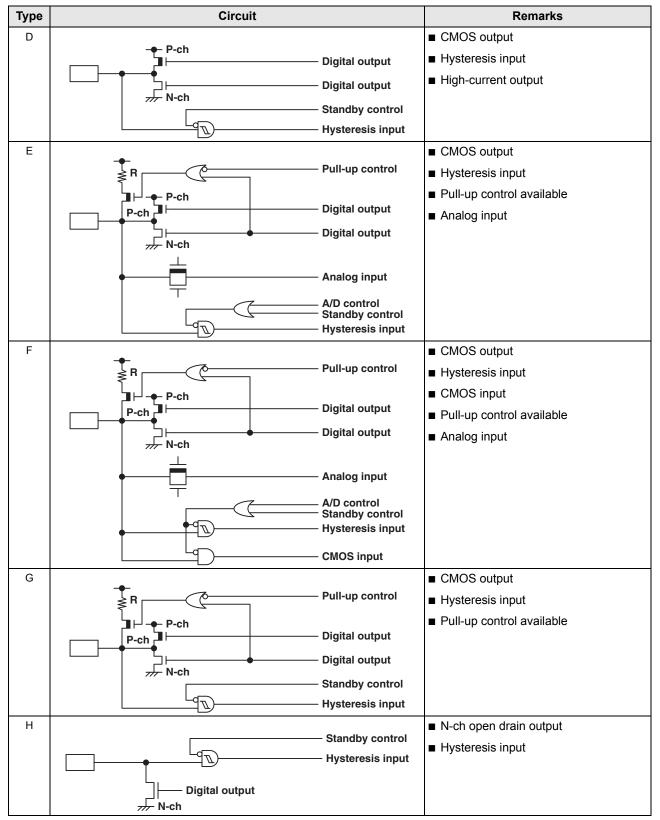

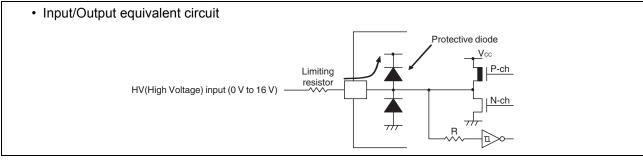

# 6. I/O Circuit Type

#### (Continued) Туре Circuit Remarks I N-ch open drain output Hysteresis input **Digital output** "FN-ch CMOS input Standby control Hysteresis input Π **CMOS** input CMOS output J Pull-up control Hysteresis input CMOS input P-ch **Digital output** P-ch Pull-up control available **Digital output** ୷ N-ch Standby control Hysteresis input $\square$ **CMOS** input κ Hysteresis input Pull-up control CMOS output Pull-up control available P-ch **Digital output** P-ch Analog input **Digital output** ୷ N-ch Standby control Δ Hysteresis input Analog input

# 7. Notes On Device Handling

#### Preventing latch-ups

When using the device, ensure that the voltage applied does not exceed the maximum voltage rating.

In a CMOS IC, if a voltage higher than  $V_{CC}$  or a voltage lower than  $V_{SS}$  is applied to an input/output pin that is neither a medium-withstand voltage pin nor a high-withstand voltage pin, or if a voltage out of the rating range of power supply voltage mentioned in "14.1 Absolute Maximum Ratings" of "Electrical Characteristics" is applied to the  $V_{CC}$  pin or the  $V_{SS}$  pin, a latch-up may occur.

When a latch-up occurs, power supply current increases significantly, which may cause a component to be thermally destroyed.

- Stabilizing supply voltage

- Supply voltage must be stabilized.

A malfunction may occur when power supply voltage fluctuates rapidly even though the fluctuation is within the guaranteed operating range of the  $V_{CC}$  power supply voltage.

As a rule of voltage stabilization, suppress voltage fluctuation so that the fluctuation in  $V_{CC}$  ripple (p-p value) at the commercial frequency (50 Hz/60 Hz) does not exceed 10% of the standard  $V_{CC}$  value, and the transient fluctuation rate does not exceed 0.1 V/ms at a momentary fluctuation such as switching the power supply.

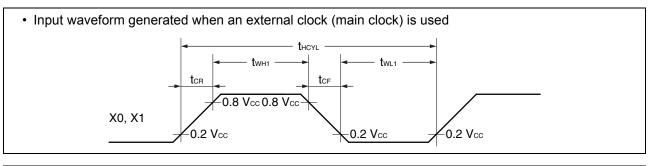

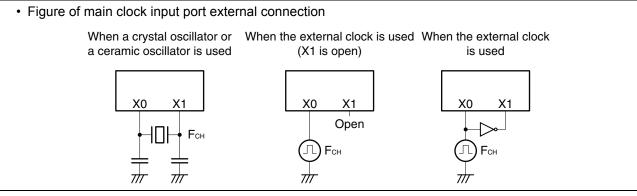

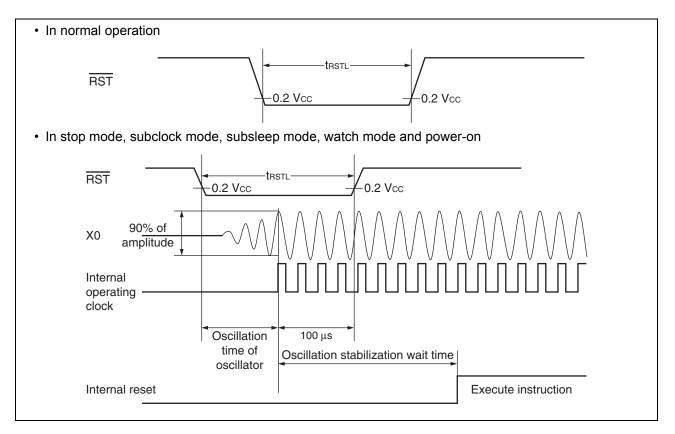

Notes on using the external clock

When an external clock is used, oscillation stabilization wait time is required for power-on reset, wake-up from subclock mode or stop mode.

# 8. Pin Connection

#### Treatment of unused pins

If an unused input pin is left unconnected, a component may be permanently damaged due to malfunctions or latch-ups. Always pull up or pull down an unused input pin through a resistor of at least  $2 k\Omega$ . Set an unused input/output pin to the output state and leave it unconnected, or set it to the input state and treat it the same as an unused input pin. If there is an unused output pin, leave it unconnected.

### 9. Power supply pins

To reduce unnecessary electro-magnetic emission, prevent malfunctions of strobe signals due to an increase in the ground level, and conform to the total output current standard, always connect the  $V_{CC}$  pin and the  $V_{SS}$  pin to the power supply and ground outside the device. In addition, connect the current supply source to the  $V_{CC}$  pin and the  $V_{SS}$  pin with low impedance.

It is also advisable to connect a ceramic capacitor of approximately 0.1  $\mu$ F as a bypass capacitor between the V<sub>CC</sub> pin and the V<sub>SS</sub> pin at a location close to this device.

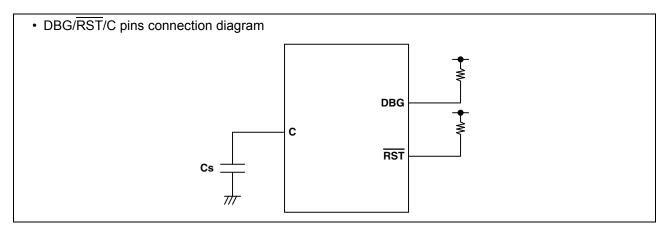

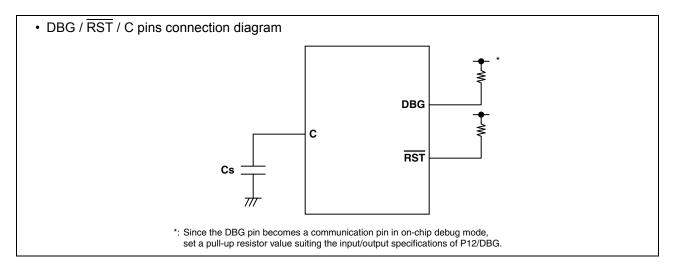

#### DBG pin

Connect the DBG pin directly to an external pull-up resistor.

To prevent the device from unintentionally entering the debug mode due to noise, minimize the distance between the DBG pin and the  $V_{CC}$  or  $V_{SS}$  pin when designing the layout of the printed circuit board.

The DBG pin should not stay at "L" level after power-on until the reset output is released.

■ RST pin

Connect the RST pin directly to an external pull-up resistor.

To prevent the device from unintentionally entering the reset mode due to noise, minimize the distance between the  $\overline{RST}$  pin and the V<sub>CC</sub> or V<sub>SS</sub> pin when designing the layout of the printed circuit board.

The RST/PF2 pin functions as the reset input/output pin after power-on. In addition, the reset output of the RST/PF2 pin can be enabled by the RSTOE bit in the SYSC register, and the reset input function and the general purpose I/O function can be selected by the RSTEN bit in the SYSC register.

#### C pin

Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. The bypass capacitor for the  $V_{CC}$  pin must have a capacitance larger than  $C_S$ . For the connection to a smoothing capacitor  $C_S$ , see the diagram below. To prevent the device from unintentionally entering a mode to which the device is not set to transit due to noise, minimize the distance between the C pin and  $C_S$  and the distance between  $C_S$  and the V<sub>SS</sub> pin when designing the layout of a printed circuit board.

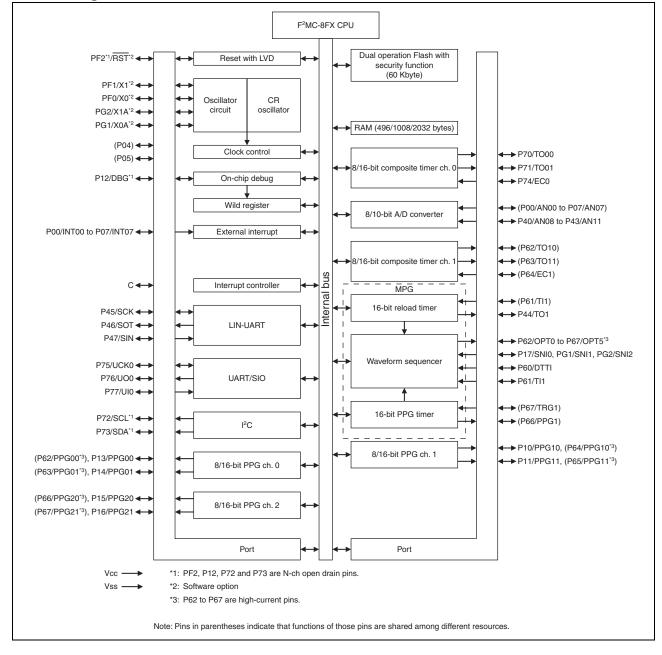

# 10. Block Diagram

# 11. CPU Core

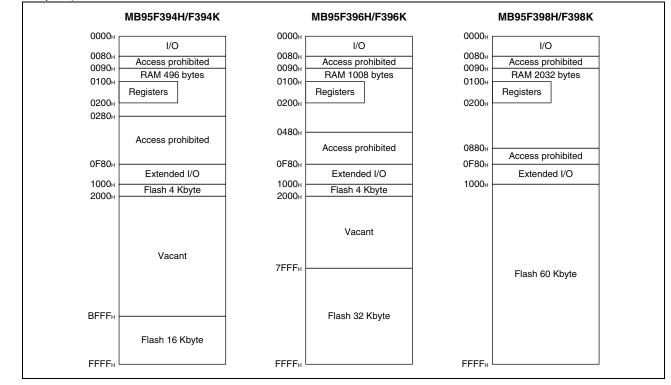

#### Memory Space

The memory space of the MB95390H Series is 64 Kbyte in size, and consists of an I/O area, a data area, and a program area. The memory space includes areas intended for specific purposes such as general-purpose registers and a vector table. The memory maps of the MB95390H Series are shown below.

#### Memory Maps

# 12. I/O Map

| Address                                      | Register abbreviation | Register name                                        | R/W | Initial value         |

|----------------------------------------------|-----------------------|------------------------------------------------------|-----|-----------------------|

| 0000 <sub>H</sub>                            | PDR0                  | Port 0 data register                                 | R/W | 00000000 <sub>B</sub> |

| 0001 <sub>H</sub>                            | DDR0                  | Port 0 direction register                            | R/W | 00000000 <sub>B</sub> |

| 0002 <sub>H</sub>                            | PDR1                  | Port 1 data register                                 | R/W | 00000000 <sub>B</sub> |

| 0003 <sub>H</sub>                            | DDR1                  | Port 1 direction register                            | R/W | 00000000 <sub>B</sub> |

| 0004 <sub>H</sub>                            | —                     | (Disabled)                                           | —   | _                     |

| 0005 <sub>H</sub>                            | WATR                  | Oscillation stabilization wait time setting register | R/W | 11111111 <sub>B</sub> |

| 0006 <sub>H</sub>                            | —                     | (Disabled)                                           | _   | _                     |

| 0007 <sub>H</sub>                            | SYCC                  | System clock control register                        | R/W | 0000X011 <sub>B</sub> |

| 0008 <sub>H</sub>                            | STBC                  | Standby control register                             | R/W | 00000XXX <sub>B</sub> |

| 0009 <sub>H</sub>                            | RSRR                  | Reset source register                                | R/W | XXXXXXXXB             |

| 000A <sub>H</sub>                            | TBTC                  | Time-base timer control register                     | R/W | 00000000 <sub>B</sub> |

| 000B <sub>H</sub>                            | WPCR                  | Watch prescaler control register                     | R/W | 00000000 <sub>B</sub> |

| 000C <sub>H</sub>                            | WDTC                  | Watchdog timer control register                      | R/W | 00XX0000 <sub>B</sub> |

| 000D <sub>H</sub>                            | SYCC2                 | System clock control register 2                      | R/W | XX100011 <sub>B</sub> |

| 000E <sub>H</sub><br>to<br>0011 <sub>H</sub> | _                     | (Disabled)                                           | _   | _                     |

| 0012 <sub>H</sub>                            | PDR4                  | Port 4 data register                                 | R/W | 00000000 <sub>B</sub> |

| 0013 <sub>H</sub>                            | PDR4                  | Port 4 direction register                            | R/W | 00000000 <sub>B</sub> |

| 0014 <sub>H</sub> ,<br>0015 <sub>H</sub>     | _                     | (Disabled)                                           | _   | _                     |

| 0016 <sub>H</sub>                            | PDR6                  | Port 6 data register                                 | R/W | 00000000 <sub>B</sub> |

| 0017 <sub>H</sub>                            | DDR6                  | Port 6 direction register                            | R/W | 00000000 <sub>B</sub> |

| 0018 <sub>H</sub>                            | DDR7                  | Port 7 data register                                 | R/W | 00000000 <sub>B</sub> |

| 0019 <sub>H</sub>                            | DDR7                  | Port 7 direction register                            | R/W | 00000000 <sub>B</sub> |

| 001A <sub>H</sub><br>to<br>0027 <sub>H</sub> | _                     | (Disabled)                                           | _   | _                     |

| 0028 <sub>H</sub>                            | PDRF                  | Port F data register                                 | R/W | 00000000 <sub>B</sub> |

| 0029 <sub>H</sub>                            | DDRF                  | Port F direction register                            | R/W | 00000000 <sub>B</sub> |

| 002A <sub>H</sub>                            | PDRG                  | Port G data register                                 | R/W | 00000000 <sub>B</sub> |

| 002B <sub>H</sub>                            | DDRG                  | Port G direction register                            | R/W | 00000000 <sub>B</sub> |

| 002C <sub>H</sub>                            | PUL0                  | Port 0 pull-up register                              | R/W | 00000000 <sub>B</sub> |

| 002D <sub>H</sub>                            | PUL1                  | Port 1 pull-up register                              | R/W | 00000000 <sub>B</sub> |

| 002E <sub>H</sub> ,<br>002F <sub>H</sub>     | _                     | (Disabled)                                           | _   | _                     |

| 0030 <sub>H</sub>                            | PUL4                  | Port 4 pull-up register                              | R/W | 00000000 <sub>B</sub> |

| 0031 <sub>H</sub>                            | PUL6                  | Port 6 pull-up register                              | R/W | 00000000 <sub>B</sub> |

| 0032 <sub>H</sub>                            | PUL7                  | Port 7 pull-up register                              | R/W | 00000000 <sub>B</sub> |

| 0033 <sub>H</sub> ,<br>0034 <sub>H</sub>     | —                     | (Disabled)                                           | _   | _                     |

| 0035 <sub>H</sub>                            | PULG                  | Port G pull-up register                              | R/W | 00000000 <sub>B</sub> |

| Address                                      | Register abbreviation | Register name                                           | R/W | Initial value         |

|----------------------------------------------|-----------------------|---------------------------------------------------------|-----|-----------------------|

| 0036 <sub>H</sub>                            | T01CR1                | 8/16-bit composite timer 01 status control register 1   | R/W | 00000000 <sub>B</sub> |

| 0037 <sub>H</sub>                            | T00CR1                | 8/16-bit composite timer 00 status control register 1   | R/W | 00000000 <sub>B</sub> |

| 0038 <sub>H</sub>                            | T11CR1                | 8/16-bit composite timer 11 status control register 1   | R/W | 00000000 <sub>B</sub> |

| 0039 <sub>H</sub>                            | T10CR1                | 8/16-bit composite timer 10 status control register 1   | R/W | 00000000 <sub>B</sub> |

| 003A <sub>H</sub>                            | PC01                  | 8/16-bit PPG timer 01 control register                  | R/W | 00000000 <sub>B</sub> |

| 003B <sub>H</sub>                            | PC00                  | 8/16-bit PPG timer 00 control register                  | R/W | 00000000 <sub>B</sub> |

| 003C <sub>H</sub>                            | PC11                  | 8/16-bit PPG timer 11 control register                  | R/W | 00000000 <sub>B</sub> |

| 003D <sub>H</sub>                            | PC10                  | 8/16-bit PPG timer 10 control register                  | R/W | 00000000 <sub>B</sub> |

| 003E <sub>H</sub>                            | PC21                  | 8/16-bit PPG timer 21 control register                  | R/W | 00000000 <sub>B</sub> |

| 003F <sub>H</sub>                            | PC20                  | 8/16-bit PPG timer 20 control register                  | R/W | 00000000 <sub>B</sub> |

| 0040 <sub>H</sub>                            | TMCSRH1               | 16-bit reload timer control status register upper       | R/W | 00000000 <sub>B</sub> |

| 0041 <sub>H</sub>                            | TMCSRL1               | 16-bit reload timer control status register lower       | R/W | 00000000 <sub>B</sub> |

| 0042 <sub>H</sub> ,<br>0043 <sub>H</sub>     | _                     | (Disabled)                                              | _   | _                     |

| 0044 <sub>H</sub>                            | PCNTH1                | 16-bit PPG status control register upper                | R/W | 00000000 <sub>B</sub> |

| 0045 <sub>H</sub>                            | PCNTL1                | 16-bit PPG status control register lower                | R/W | 00000000 <sub>B</sub> |

| 0046 <sub>H</sub> ,<br>0047 <sub>H</sub>     | _                     | (Disabled)                                              | _   | -                     |

| 0048 <sub>H</sub>                            | EIC00                 | External interrupt circuit control register ch. 0/ch. 1 | R/W | 00000000 <sub>B</sub> |

| 0049 <sub>H</sub>                            | EIC10                 | External interrupt circuit control register ch. 2/ch. 3 | R/W | 00000000 <sub>B</sub> |

| 004A <sub>H</sub>                            | EIC20                 | External interrupt circuit control register ch. 4/ch. 5 | R/W | 00000000 <sub>B</sub> |

| 004B <sub>H</sub>                            | EIC30                 | External interrupt circuit control register ch. 6/ch. 7 | R/W | 00000000 <sub>B</sub> |

| 004C <sub>H</sub><br>to<br>004F <sub>H</sub> | _                     | (Disabled)                                              | _   | _                     |

| 0050 <sub>H</sub>                            | SCR                   | LIN-UART serial control register                        | R/W | 00000000 <sub>B</sub> |

| 0051 <sub>H</sub>                            | SMR                   | LIN-UART serial mode register                           | R/W | 00000000 <sub>B</sub> |

| 0052 <sub>H</sub>                            | SSR                   | LIN-UART serial status register                         | R/W | 00001000 <sub>B</sub> |

| 0053 <sub>H</sub>                            | RDR/TDR               | LIN-UART receive/transmit data register                 | R/W | 00000000 <sub>B</sub> |

| 0054 <sub>H</sub>                            | ESCR                  | LIN-UART extended status control register               | R/W | 00000100 <sub>B</sub> |

| 0055 <sub>H</sub>                            | ECCR                  | LIN-UART extended communication control register        | R/W | 000000XX <sub>B</sub> |

| 0056 <sub>H</sub>                            | SMC10                 | UART/SIO serial mode control register 1                 | R/W | 00000000 <sub>B</sub> |

| 0057 <sub>H</sub>                            | SMC20                 | UART/SIO serial mode control register 2                 | R/W | 00100000 <sub>B</sub> |

| 0058 <sub>H</sub>                            | SSR0                  | UART/SIO serial status and data register                | R/W | 00000001 <sub>B</sub> |

| 0059 <sub>H</sub>                            | TDR0                  | UART/SIO serial output data register                    | R/W | 00000000 <sub>B</sub> |

| 005A <sub>H</sub>                            | RDR0                  | UART/SIO serial input data register                     | R   | 00000000 <sub>B</sub> |

| 005B <sub>H</sub><br>to<br>005F <sub>H</sub> | _                     | (Disabled)                                              | _   | _                     |

| Address           | Register abbreviation | Register name                                                               | R/W | Initial value         |

|-------------------|-----------------------|-----------------------------------------------------------------------------|-----|-----------------------|

| 0060 <sub>H</sub> | IBCR00                | I <sup>2</sup> C bus control register 0                                     | R/W | 00000000 <sub>B</sub> |

| 0061 <sub>H</sub> | IBCR10                | I <sup>2</sup> C bus control register 1                                     | R/W | 00000000 <sub>B</sub> |

| 0062 <sub>H</sub> | IBCR0                 | I <sup>2</sup> C bus status register                                        | R/W | 00000000 <sub>B</sub> |

| 0063 <sub>H</sub> | IDDR0                 | I <sup>2</sup> C data register                                              | R/W | 00000000 <sub>B</sub> |

| 0064 <sub>H</sub> | IAAR0                 | I <sup>2</sup> C address register                                           | R/W | 00000000 <sub>B</sub> |

| 0065 <sub>H</sub> | ICCR0                 | I <sup>2</sup> C clock control register                                     | R/W | 00000000 <sub>B</sub> |

| 0066 <sub>H</sub> | OPCUR                 | Output control register (upper)                                             | R/W | 00000000 <sub>B</sub> |

| 0067 <sub>H</sub> | OPCLR                 | Output control register (lower)                                             | R/W | 00000000 <sub>B</sub> |

| 0068 <sub>H</sub> | IPCUR                 | Input control register (upper)                                              | R/W | 00000000 <sub>B</sub> |

| 0069 <sub>H</sub> | IPCLR                 | Input control register (lower)                                              | R/W | 00000000 <sub>B</sub> |

| 006A <sub>H</sub> | NCCR                  | Noise cancellation control register                                         | R/W | 00000000 <sub>B</sub> |

| 006B <sub>H</sub> | TCSR                  | Timer control status register                                               | R/W | 00000000 <sub>B</sub> |

| 006C <sub>H</sub> | ADC1                  | 8/10-bit A/D converter control register 1                                   | R/W | 00000000 <sub>B</sub> |

| 006D <sub>H</sub> | ADC2                  | 8/10-bit A/D converter control register 2                                   | R/W | 00000000 <sub>B</sub> |

| 006E <sub>H</sub> | ADDH                  | 8/10-bit A/D converter data register (upper)                                | R/W | 00000000 <sub>B</sub> |

| 006F <sub>H</sub> | ADDL                  | 8/10-bit A/D converter data register (lower)                                | R/W | 00000000 <sub>B</sub> |

| 0070 <sub>H</sub> | —                     | (Disabled)                                                                  | —   | —                     |

| 0071 <sub>H</sub> | FSR2                  | Flash memory status register 2                                              | R/W | 00000000 <sub>B</sub> |

| 0072 <sub>H</sub> | FSR                   | Flash memory status register                                                | R/W | 000X0000 <sub>B</sub> |

| 0073 <sub>H</sub> | SWRE0                 | Flash memory sector write control register 0                                | R/W | 00000000 <sub>B</sub> |

| 0074 <sub>H</sub> | FSR3                  | Flash memory status register 3                                              | R   | 00000000 <sub>B</sub> |

| 0075 <sub>H</sub> | —                     | (Disabled)                                                                  | —   |                       |

| 0076 <sub>H</sub> | WREN                  | Wild register address compare enable register                               | R/W | 00000000 <sub>B</sub> |

| 0077 <sub>H</sub> | WROR                  | Wild register data test setting register                                    | R/W | 00000000 <sub>B</sub> |

| 0078 <sub>H</sub> | _                     | Mirror of register bank pointer (RP) and mirror of direct bank pointer (DP) | _   | —                     |

| 0079 <sub>H</sub> | ILR0                  | Interrupt level setting register 0                                          | R/W | 11111111 <sub>B</sub> |

| 007A <sub>H</sub> | ILR1                  | Interrupt level setting register 1                                          | R/W | 11111111 <sub>B</sub> |

| 007B <sub>H</sub> | ILR2                  | Interrupt level setting register 2                                          | R/W | 11111111 <sub>B</sub> |

| 007C <sub>H</sub> | ILR3                  | Interrupt level setting register 3                                          | R/W | 11111111 <sub>B</sub> |

| 007D <sub>H</sub> | ILR4                  | Interrupt level setting register 4                                          | R/W | 11111111 <sub>B</sub> |

| 007E <sub>H</sub> | ILR5                  | Interrupt level setting register 5                                          |     | 11111111 <sub>B</sub> |

| 007F <sub>H</sub> | _                     | (Disabled)                                                                  | —   | _                     |