| N  | ABSOLUTE MAXIMUM RATINGS                                 |

|----|----------------------------------------------------------|

| 1  | Supply Voltage Range (VCC, VCCA, VCCQA,                  |

| 9  | VCCQB, VCCQC)0.3V to +4.0V                               |

| 3  | Voltage Range at CIN, IN_SEL, DM, DF, PLL_BP,            |

| EX | DA, DB, DC, QA_CTRL1, QA_CTRL2,                          |

|    | QB_CTRL, QC_CTRL, RES[6:0]0.3V to (VCC + 0.3V)           |

| P  | Voltage Range at DIN, DIN (VCC - 2.35V) to (VCC - 0.35V) |

|    | Voltage Range at QA[4:0], QA[4:0], QB[2:0],              |

|    | QB[2:0], QC, QC when LVDS Output0.3V to (VCC + 0.3V)     |

|    | Current into QA[4:0], QA[4:0], QB[2:0], QB[2:0],         |

|    | QC, QC when LVPECL Output56mA                            |

| Voltage Range at XIN                                | 0.3V to +1.2V         |

|-----------------------------------------------------|-----------------------|

| Voltage Range at XOUT                               | -0.3V to (VCC - 0.6V) |

| Continuous Power Dissipation ( $TA = +70^{\circ}$ ) | C)                    |

| 48-Pin TQFN (derate 40mW/°C above +                 | 70°C)3200mW           |

| Operating Junction Temperature Range                | 55°C to +150°C        |

| Storage Temperature Range                           | 65°C to +160°C        |

| Lead Temperature (soldering, 10s)                   | +300°C                |

| Soldering Temperature (reflow)                      | +260°C                |

|                                                     |                       |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VCC = +3.0V to +3.6V, TA = -40°C to +85°C. Typical values are at VCC = +3.3V, TA = +25°C, unless otherwise noted. Signal applied to CIN or DIN/DIN only when selected as the reference clock.) (Note 1)

| PARAMETER                                       | SYMBOL        | CONDITIONS                            | MIN                    | TYP                    | MAX          | UNITS             |

|-------------------------------------------------|---------------|---------------------------------------|------------------------|------------------------|--------------|-------------------|

| Supply Current with PLL                         | laa           | Configured with LVPECL outputs        |                        | 150                    | 200          | то Л              |

| Enabled (Note 2)                                | Icc           | Configured with LVDS outputs          |                        | 270                    | 360          | mA mA             |

| Supply Current with PLL                         |               | Configured with LVPECL outputs        |                        | 100                    |              | A                 |

| Bypassed (Note 2)                               |               | Configured with LVDS outputs          |                        | 220                    |              | mA                |

| LVCMOS/LVTTL CONTROL INF<br>QC_CTRL)            | PUTS (IN_SEL  | ., DM, DF, DA, DB, DC, PLL_BP, QA_CTR | L1, QA_C7              | RL2, QB                | _CTRL,       |                   |

| Input High Voltage                              | VIH           |                                       | 2.0                    |                        |              | V                 |

| Input Low Voltage                               | VIL           |                                       |                        |                        | 0.8          | V                 |

| Input High Current                              | lін           | V <sub>IN</sub> = V <sub>CC</sub>     |                        |                        | 80           | μΑ                |

| Input Low Current                               | IIL           | V <sub>IN</sub> = 0V                  | -80                    |                        |              | μΑ                |

| LVCMOS/LVTTL CLOCK INPUT                        | (CIN)         |                                       |                        |                        |              |                   |

| Reference Clock Input<br>Frequency              | fREF          |                                       | 15                     |                        | 160          | MHz               |

| Input Amplitude Range                           |               | Internally AC-coupled (Note 3)        | 1.2                    |                        | 3.6          | V <sub>P-P</sub>  |

| Input High Current                              | lін           | VIN = VCC                             |                        |                        | 80           | μΑ                |

| Input Low Current                               | lıL           | V <sub>IN</sub> = 0V                  | -80                    |                        |              | μA                |

| Reference Clock Input Duty-<br>Cycle Distortion |               |                                       | 40                     |                        | 60           | %                 |

| Input Capacitance                               |               |                                       |                        | 1.5                    |              | pF                |

| DIFFERENTIAL CLOCK INPUT                        | (DIN, DIN) (N | ote 4)                                | •                      |                        |              |                   |

| Differential Input Frequency                    | fREF          |                                       | 15                     |                        | 350          | MHz               |

| Input Bias Voltage                              | Vсмі          |                                       | V <sub>C</sub> C - 1.8 | V <sub>C</sub> C - 1.3 |              | V                 |

| Input Differential Voltage Swing                |               |                                       | 150                    |                        | 1800         | mV <sub>P-P</sub> |

| Single-Ended Voltage Range                      |               |                                       | VCC - 2.0              |                        | VCC -<br>0.7 | V                 |

| Input Differential Impedance                    |               |                                       | 80                     | 100                    | 120          | Ω                 |

| Differential Input Capacitance                  |               |                                       |                        | 1.5                    |              | pF                |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(VCC = +3.0V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}.$  Typical values are at  $VCC = +3.3V, T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Signal applied to CIN or DIN/ $\overline{\text{DIN}}$  only when selected as the reference clock.) (Note 1)

| PARAMETER                                                                   | SYMBOL              | CO                                     | NDITIONS              | MIN                     | TYP                    | MAX                    | UNITS            |

|-----------------------------------------------------------------------------|---------------------|----------------------------------------|-----------------------|-------------------------|------------------------|------------------------|------------------|

| LVDS OUTPUTS (QA[4:0], QA[4                                                 | :0], QB[2:0],       | $\overline{QB[2:0]},QC,\overline{QC})$ | (Note 5)              |                         |                        |                        |                  |

| Output High Voltage                                                         | Voh                 |                                        |                       |                         |                        | 1.475                  | V                |

| Output Low Voltage                                                          | VoL                 |                                        |                       | 0.925                   |                        |                        | V                |

| Differential Output Voltage                                                 | IV <sub>OD</sub> I  |                                        |                       | 250                     |                        | 400                    | mV               |

| Change in Magnitude of Differential Output for Complementary States         | ΔIV <sub>OD</sub> I |                                        |                       |                         |                        | 25                     | mV               |

| Output Offset Voltage                                                       | Vos                 |                                        |                       | 1.125                   | -                      | 1.3                    | V                |

| Change in Magnitude of<br>Output Offset Voltage for<br>Complementary States | ΔIVOSI              |                                        |                       |                         |                        | 25                     | mV               |

| Differential Output Impedance                                               |                     |                                        |                       | 80                      | 100                    | 140                    | Ω                |

| Output Current                                                              |                     | Short together                         |                       |                         | 3                      |                        | mA               |

| Output Current                                                              |                     | Short to ground                        |                       |                         | 6                      |                        | IIIA             |

| Output Current When Disabled                                                |                     | $VQ_{-} = V\overline{Q_{-}} = 0V t$    | o VCC                 |                         | 10                     |                        | μΑ               |

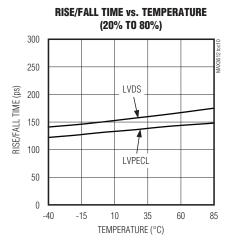

| Output Rise/Fall Time                                                       |                     | 20% to 80%                             |                       |                         | 160                    | 240                    | ps               |

| Output Duty-Cycle Distortion                                                |                     | PLL enabled                            |                       | 48                      | 50                     | 52                     | %                |

| Output Duty-Cycle Distortion                                                |                     | PLL bypassed (N                        | ote 6)                |                         | 50                     |                        | /0               |

| LVPECL OUTPUTS (QA[4:0], QA                                                 | A[4:0], QB[2:       | 0], QB[2:0], QC, Q                     | C) (Note 7)           |                         |                        |                        |                  |

| Output High Voltage                                                         | Voн                 |                                        |                       | V <sub>CC</sub> - 1.13  | V <sub>CC</sub> - 0.98 | V <sub>CC</sub> - 0.83 | V                |

| Output Low Voltage                                                          | VoL                 |                                        |                       | V <sub>C</sub> C - 1.85 | V <sub>CC</sub> -      | VCC -<br>1.55          | V                |

| Output-Voltage Swing (Single-Ended)                                         |                     |                                        |                       | 0.5                     | 0.7                    | 0.9                    | V <sub>P-P</sub> |

| Output Current When Disabled                                                |                     | $V_O = 0V$ to $V_{CC}$                 |                       |                         | 10                     |                        | μΑ               |

| Output Rise/Fall Time                                                       |                     | 20% to 80%, diffe                      | erential load = 100Ω  |                         | 140                    | 240                    | ps               |

| 0 + + D + 0 + D' + i'                                                       |                     | PLL enabled                            |                       | 48                      | 50                     | 52                     | 0/               |

| Output Duty-Cycle Distortion                                                |                     | PLL bypassed (N                        | ote 6)                |                         | 50                     |                        | %                |

| PLL SPECIFICATIONS                                                          | '                   |                                        |                       |                         |                        |                        |                  |

| VCO Frequency Range                                                         | fvco                |                                        |                       |                         | 625                    |                        | MHz              |

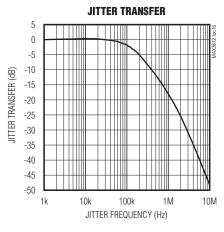

| PLL Jitter Transfer Bandwidth                                               |                     |                                        |                       |                         | 130                    |                        | kHz              |

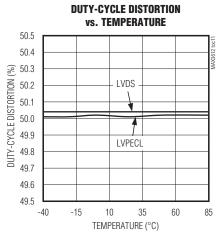

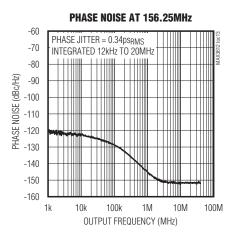

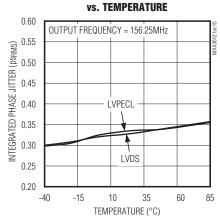

|                                                                             |                     | 25MHz crystal                          | 12kHz to 20MHz        |                         | 0.34                   | 1.0                    |                  |

| Integrated Phase Jitter at                                                  | D.                  | input                                  | 1.875MHz to 20MHz     |                         | 0.14                   |                        | 1                |

| 156.25MHz Output                                                            |                     | 25MHz LVCMOS<br>(Note 8)               | or differential input |                         | 0.34                   |                        | psRMS            |

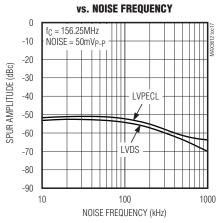

| Supply-Noise Induced Phase<br>Spur                                          |                     | (Note 9)                               |                       |                         | -56                    |                        | dBc              |

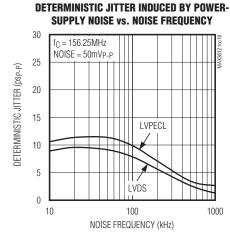

| Determinisitic Jitter Induced by Power-Supply Noise                         |                     | (Note 9)                               |                       |                         | 6                      |                        | psp-p            |

#### **♥** ELECTRICAL CHARACTERISTICS (continued)

$(VCC = +3.0V \text{ to } +3.6V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}.$  Typical values are at  $VCC = +3.3V, T_A = +25^{\circ}\text{C}$ , unless otherwise noted. Signal applied to CIN or DIN/\overline{DIN} only when selected as the reference clock.) (Note 1)

| PARAMETER                         | SYMBOL | CONDITIONS       | MIN TYP MAX | UNITS      |

|-----------------------------------|--------|------------------|-------------|------------|

| Nonharmonic and Subharmonic Spurs |        | (Note 10)        | -70         | dBc        |

|                                   |        | fOFFSET = 1kHz   | -115        |            |

|                                   |        | fOFFSET = 10kHz  | -116        | -ID - /    |

| SSB Phase Noise at 312.5MHz       |        | foffset = 100kHz | -122        | dBc/<br>Hz |

|                                   |        | fOFFSET = 1MHz   | -139        | ] ''2      |

|                                   |        | foffset ≥ 10MHz  | -149        |            |

|                                   |        | fOFFSET = 1kHz   | -122        | dBc/       |

|                                   |        | foffset = 10kHz  | -123        |            |

| SSB Phase Noise at 156.25MHz      |        | foffset = 100kHz | -129        |            |

|                                   |        | foffset = 1MHz   | -145        | 1 112      |

|                                   |        | foffset ≥ 10MHz  | -152        |            |

|                                   |        | fOFFSET = 1kHz   | -123        |            |

|                                   |        | foffset = 10kHz  | -124        | dBc/       |

| SSB Phase Noise at 125MHz         |        | foffset = 100kHz | -130        |            |

|                                   |        | foffset = 1MHz   | -147        | ] ' ' ' '  |

|                                   |        | fOFFSET ≥ 10MHz  | -153        |            |

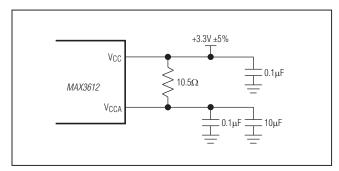

- **Note 1:** A series resistor of up to  $10.5\Omega$  is allowed between VCC and VCCA for filtering supply noise when system power-supply tolerance is VCC =  $3.3V \pm 5\%$ . See Figure 2.

- Note 2: Measured with all outputs enabled and unloaded.

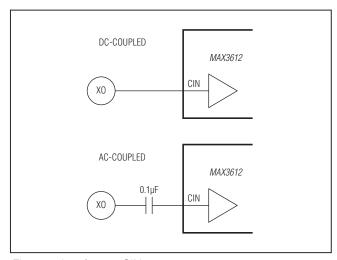

- Note 3: CIN can be AC- or DC-coupled. See Figure 7. Input high voltage must be ≤ V<sub>CC</sub> to +0.3V.

- Note 4: DIN can be AC- or DC-coupled. See Figure 9.

- **Note 5:** Measured with  $100\Omega$  differential load.

- Note 6: Measured with crystal input, or with 50% duty cycle LVCMOS, or differential input.

- **Note 7:** Measured with output termination of  $50\Omega$  to  $V_{CC}$  2V or Thevenin equivalent.

- **Note 8:** Measured using LVCMOS/LVTTL input with slew rate ≥ 1.0V/ns, or differential input with slew rate ≥ 0.5V/ns.

- **Note 9:** Measured at 156.25MHz output with 200kHz, 50mVp-p sinusoidal signal on the supply using the crystal input and the power-supply filter shown in Figure 2. See the *Typical Operating Characteristics* for other supply noise frequencies. Deterministic jitter is calculated from the measured power-supply-induced spurs. For more information, refer to Application Note 4461: *HFAN-04.5.5*: Characterizing Power-Supply Noise Rejection in PLL Clock Synthesizers.

- **Note 10:** Measured with all outputs enabled and all three banks at different frequencies.

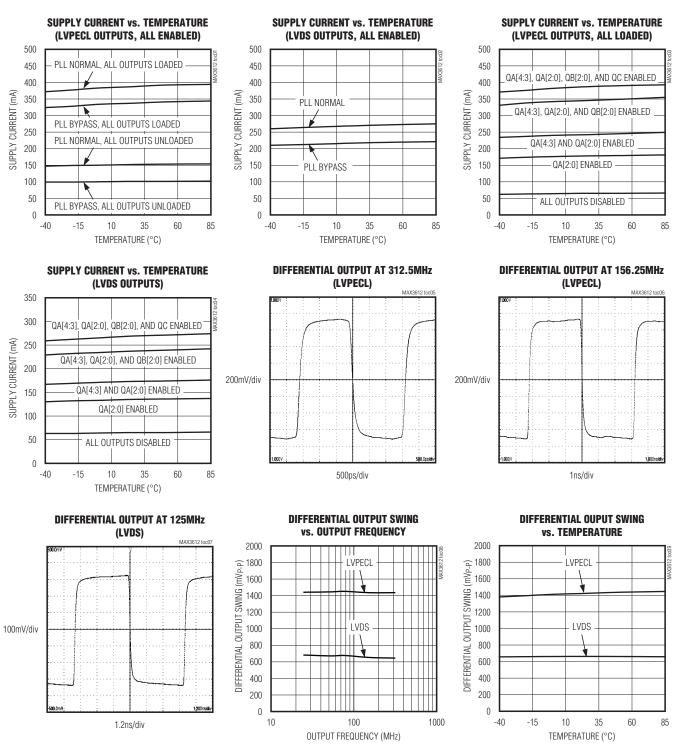

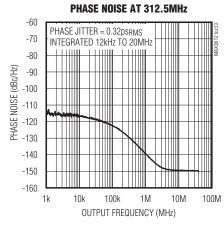

### **Typical Operating Characteristics**

$(V_{CC} = 3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

#### Typical Operating Characteristics (continued)

(VCC = 3.3V, TA = +25°C, unless otherwise noted.)

SPURS INDUCED BY POWER-SUPPLY NOISE

**INTEGRATED PHASE JITTER (12kHz TO 20MHz)**

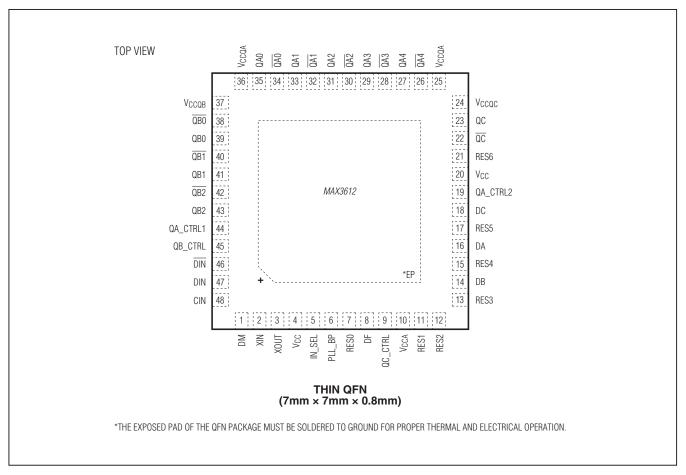

### \_Pin Description

| PIN    | NAME     | FUNCTION                                                                                                                                                                       |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | DM       | LVCMOS/LVTTL Input. Control for input divider M. See Table 3.                                                                                                                  |

| 2      | XIN      | Crystal Oscillator Input                                                                                                                                                       |

| 3      | XOUT     | Crystal Oscillator Output                                                                                                                                                      |

| 4, 20  | Vcc      | Positive Power Supply. Connect to +3.3V.                                                                                                                                       |

| 5      | IN_SEL   | LVCMOS/LVTTL Input. Three-level control for input mux. See Table 1.                                                                                                            |

| 6      | PLL_BP   | LVCMOS/LVTTL Input. Three-level control for PLL bypass mode. See Table 2.                                                                                                      |

| 7      | RES0     | Reserved. Connect to GND for normal operation.                                                                                                                                 |

| 8      | DF       | LVCMOS/LVTTL Input. Control for feedback divider F. See Table 4.                                                                                                               |

| 9      | QC_CTRL  | LVCMOS/LVTTL Input. Three-level control input for C-bank output interface. See Table 8.                                                                                        |

| 10     | VCCA     | Power Supply for Internal Voltage-Controlled Oscillators (VCOs). See Figure 3.                                                                                                 |

| 11     | RES1     | Reserved. Connect to GND for normal operation.                                                                                                                                 |

| 12     | RES2     | Reserved. Connect to V <sub>CC</sub> for normal operation.                                                                                                                     |

| 13     | RES3     | Reserved. Connect to GND for normal operation.                                                                                                                                 |

| 14     | DB       | LVCMOS/LVTTL Input. Three-level controls for output divider B. See Table 5.                                                                                                    |

| 15     | RES4     | Reserved. Connect to GND for normal operation.                                                                                                                                 |

| 16     | DA       | LVCMOS/LVTTL Input. Three-level controls for output divider A. See Table 5.                                                                                                    |

| 17     | RES5     | Reserved. Connect to GND for normal operation.                                                                                                                                 |

| 18     | DC       | LVCMOS/LVTTL Input. Three-level controls for output divider C. See Table 5.                                                                                                    |

| 19     | QA_CTRL2 | LVCMOS/LVTTL Input. Three-level control for QA[4:3] output interface. See Table 6.                                                                                             |

| 21     | RES6     | Reserved. Connect to GND for normal operation.                                                                                                                                 |

| 22, 23 | QC, QC   | C-Bank Differential Output. Configured as LVPECL, LVDS, or high-Z with the QC_CTRL pin.                                                                                        |

| 24     | Vccqc    | Power Supply for C-Bank Differential Output. Connect to +3.3V.                                                                                                                 |

| 25, 36 | VCCQA    | Power Supply for A-Bank Differential Outputs. Connect to +3.3V.                                                                                                                |

| 26, 27 | QA4, QA4 | A-Bank Differential Output. Configured as LVPECL, LVDS, or high-Z with the QA_CTRL2 pin.                                                                                       |

| 28, 29 | QA3, QA3 | A-Bank Differential Output. Configured as LVPECL, LVDS, or high-Z with the QA_CTRL2 pin.                                                                                       |

| 30, 31 | QA2, QA2 | A-Bank Differential Output. Configured as LVPECL, LVDS, or high-Z with the QA_CTRL1 pin.                                                                                       |

| 32, 33 | QA1, QA1 | A-Bank Differential Output. Configured as LVPECL, LVDS, or high-Z with the QA_CTRL1 pin.                                                                                       |

| 34, 35 | QAO, QAO | A-Bank Differential Output. Configured as LVPECL, LVDS, or high-Z with the QA_CTRL1 pin.                                                                                       |

| 37     | VCCQB    | Power Supply for B-Bank Differential Outputs. Connect to +3.3V.                                                                                                                |

| 38, 39 | QB0, QB0 | B-Bank Differential Output. Configured as LVPECL, LVDS, or high-Z with the QB_CTRL pin.                                                                                        |

| 40, 41 | QB1, QB1 | B-Bank Differential Output. Configured as LVPECL, LVDS, or high-Z with the QB_CTRL pin.                                                                                        |

| 42, 43 | QB2, QB2 | B-Bank Differential Output. Configured as LVPECL, LVDS, or high-Z with the QB_CTRL pin.                                                                                        |

| 44     | QA_CTRL1 | LVCMOS/LVTTL Input. Three-level control for QA[2:0] output interface. See Table 6.                                                                                             |

| 45     | QB_CTRL  | LVCMOS/LVTTL Input. Three-level control for B-bank output interface. See Table 7.                                                                                              |

| 46, 47 | DIN, DIN | Differential Clock Input. Operates up to 350MHz. This input can accept DC-coupled LVPECL signals, and is internally biased to accept AC-coupled LVDS, CML, and LVPECL signals. |

| 48     | CIN      | LVCMOS Clock Input. Operates up to 160MHz.                                                                                                                                     |

| _      | EP       | Exposed Pad. Connect to supply ground for proper electrical and thermal performance.                                                                                           |

#### **Detailed Description**

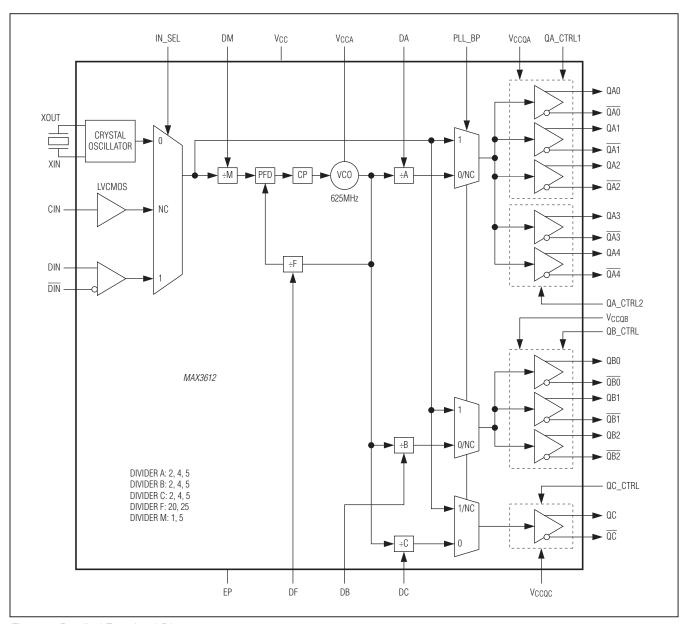

The MAX3612 is a low-jitter clock generator optimized for Ethernet applications. It consists of a selectable reference clock (on-chip crystal oscillator, LVCMOS input, or differential input), PLL with on-chip VCO, pin-programmable dividers and muxes, and three banks of clock outputs. See Figure 1. The output banks include nine pin-programmable LVDS/LVPECL output buffers.

The frequency and output interface of each output bank can be individually programmed. A PLL bypass mode is also available for system testing or clock distribution.

#### **Crystal Oscillator**

The on-chip crystal oscillator provides the low-frequency reference clock for the PLL. This oscillator requires an external crystal connected between XIN and XOUT. See the *Crystal Selection and Layout* section for more

Figure 1. Detailed Functional Diagram

information. The XIN and XOUT pins can be left open if not used.

#### **LVCMOS Clock Input**

An LVCMOS-compatible clock source can be connected to CIN to serve as the PLL reference clock. The input is internally biased to allow AC- or DC-coupling (see the *Applications Information* section). It is designed to operate from 15MHz to 160MHz. No signal should be applied to CIN if not used.

#### **Differential Clock Input**

A differential clock source can be connected to DIN to serve as the PLL reference clock. This input operates from 15MHz to 350MHz and contains an internal  $100\Omega$  differential termination. This input can accept DC-coupled LVPECL signals, and is internally biased to accept AC-coupled LVDS, CML, and LVPECL signals (see the *Applications Information* section). No signal should be applied to DIN if not used.

#### Phase-Locked Loop (PLL)

The PLL takes the signal from the crystal oscillator, LVCMOS clock input, or differential clock input and synthesizes a low-jitter, high-frequency clock. The PLL contains a phase-frequency detector (PFD), a charge pump (CP), and a low-phase noise VCO. The VCO output is connected to the PFD input through a feedback divider. The PFD compares the reference frequency to the divided-down VCO output and generates a control signal that keeps the VCO locked to the reference clock. The high-frequency VCO output clock is sent to the output dividers. To minimize noise-induced jitter, the VCO supply (VCCA) is isolated from the core logic and output buffer supplies.

#### **Dividers and Muxes**

The dividers and muxes are set with three-level control inputs. Divider settings and routing information are given in Tables 1 to 9.

#### Table 1. PLL Input

| IN_SEL | INPUT                                                                   |

|--------|-------------------------------------------------------------------------|

| 0      | Crystal Input. XO circuit is disabled when not selected.                |

| 1      | Differential Input. No signal should be applied to DIN if not selected. |

| NC     | LVCMOS Input. No signal should be applied to CIN if not selected.       |

#### Table 2. PLL Bypass

| PLL_BP | PLL OPERATION                                                                                                                                                                            |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0      | PLL Enabled for Normal Operation. All outputs from the A-, B-, and C-banks are derived from the VCO.                                                                                     |

| 1      | PLL Bypassed. Selected input passes directly to the outputs. The VCO is disabled to minimize power consumption and intermodulation spurs. Used for system testing or clock distribution. |

| NC     | The outputs from A-bank and B-bank are derived from the VCO, but the C-bank output is directly driven from the input signal for purposes of daisy chaining.                              |

#### Table 3. Input Divider M

| DM | M DIVIDER RATIO |

|----|-----------------|

| 0  | ÷1              |

| 1  | ÷5              |

| NC | Not allowed     |

**Note:** When the on-chip XO is selected (IN\_SEL = 0), the setting DM = 0 is required.

#### Table 4. PLL Feedback Divider F

| DF | F DIVIDER RATIO |

|----|-----------------|

| 0  | ÷25             |

| 1  | ÷20             |

| NC | Not allowed     |

| DA/DB/DC | A, B, C DIVIDER RATIO |

|----------|-----------------------|

| 0        | ÷4                    |

| 1        | ÷5                    |

| NC       | ÷2                    |

#### Table 6. A-Bank Output Interface

| QA_CTRL1 | QA[2:0] OUTPUT                     |

|----------|------------------------------------|

| 0        | QA[2:0] = LVDS                     |

| 1        | QA[2:0] = LVPECL                   |

| NC       | QA[2:0] disabled to high impedance |

| QA_CTRL2 | QA[4:3] OUTPUT                     |

| 0        | QA[4:3] = LVDS                     |

| 1        | QA[4:3] = LVPECL                   |

| NC       | QA[4:3] disabled to high impedance |

#### Table 7. B-Bank Output Interface

| QB_CTRL | QB[2:0] OUTPUT                     |

|---------|------------------------------------|

| 0       | QB[2:0] = LVDS                     |

| 1       | QB[2:0] = LVPECL                   |

| NC      | QB[2:0] disabled to high impedance |

#### Table 8. C-Bank Output Interface

| QC_CTRL | QC OUTPUT                     |

|---------|-------------------------------|

| 0       | QC = LVDS                     |

| 1       | QC = LVPECL                   |

| NC      | QC disabled to high impedance |

#### LVDS/LVPECL Clock Outputs

The differential clock outputs (QA[4:0], QB[2:0], QC) operate up to 350MHz and have a pin-programmable LVDS/LVPECL output interface. See Tables 6 to 8. When configured as LVDS, the buffers are designed to drive transmission lines with a  $100\Omega$  differential termination. When configured as LVPECL, the buffers are designed to drive transmission lines terminated with  $50\Omega$  to VCC - 2V. Unused output banks can be disabled to high impedance and unused outputs can be left open.

#### **Internal Reset**

During power-on, a power-on reset (POR) signal is generated to synchronize all dividers. A reset signal is also generated if any control pin is changed. Outputs within a bank are phase aligned, but outputs bank-to-bank may not be phase aligned.

#### Applications Information

#### **Output Frequency Configuration**

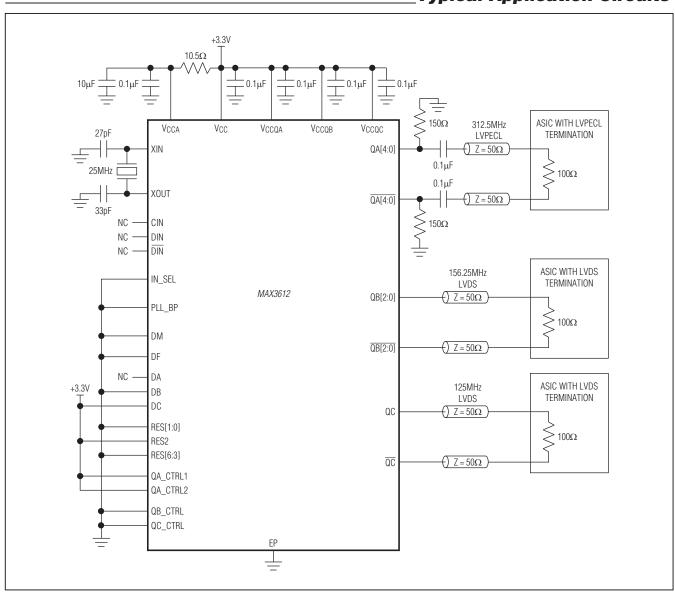

Table 9 provides the divider ratios for typical configurations.

#### **Power-Supply Filtering**

The MAX3612 is a mixed analog/digital IC. The PLL contains analog circuitry susceptible to random noise. To take full advantage of on-board filtering and noise attenuation, in addition to excellent on-chip power-supply rejection, this part provides a separate power-supply pin, VCCA, for the VCO circuitry. Figure 2 illustrates the recommended power-supply filter network for VCCA. The purpose of this design technique is to ensure clean input power supply to the VCO circuitry and to improve

#### **Table 9. Divider Configurations**

| INPUT<br>FREQUENCY<br>(MHz) | INPUT<br>DIVIDER<br>M | FEEDBACK<br>DIVIDER<br>F | VCO FREQUENCY<br>(MHz) | OUTPUT<br>DIVIDERS<br>A, B, C | OUTPUT<br>FREQUENCY<br>(MHz) |

|-----------------------------|-----------------------|--------------------------|------------------------|-------------------------------|------------------------------|

| 25                          | . 4                   | ÷25                      |                        | . 0                           | 312.5                        |

| 31.25                       | ÷1                    | ÷20                      | 625                    | ÷2                            | 312.5                        |

| 125                         | ÷5                    | ÷25                      | 025                    | ÷4                            | 156.25                       |

| 156.25                      | ,÷5                   | ÷20                      |                        | ÷5                            | 125                          |

the overall immunity to power-supply noise. This network requires that the power supply is +3.3V ±5%. Decoupling capacitors should be used on all other supply pins for best performance. All supply connections should be driven from the same source.

#### **Ground Connection**

The 48-pin TQFN package features an exposed pad (EP), which provides a low resistance thermal path for heat removal from the IC and also the electrical ground. For proper operation, the EP must be connected to the circuit board ground plane with multiple vias.

Figure 2. Power-Supply Filter

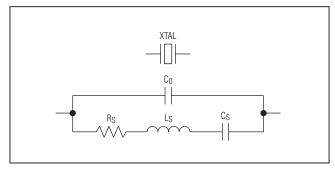

#### **Crystal Selection and Layout**

The MAX3612 features an integrated on-chip crystal oscillator to minimize system implementation cost.

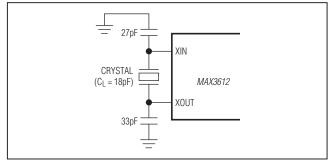

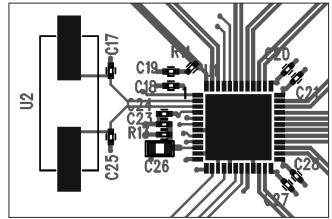

The crystal oscillator is designed to drive a fundamental mode, AT-cut crystal resonator. See Table 10 for recommended crystal specifications. See Figure 3 for the crystal equivalent circuit and Figure 4 for the recommended external capacitor connections. The crystal, trace, and two external capacitors should be placed on the board as close as possible to the XIN and XOUT pins to reduce crosstalk of active signals into the oscillator.

The total load capacitance for the crystal is a combination of external and on-chip capacitance. The layout shown in Figure 5 gives approximately 1.7pF of trace plus footprint capacitance per side of the crystal. Note the ground plane is removed under the crystal to minimize capacitance. There is approximately 2.5pF of on-chip capacitance between XIN and XOUT. With an external 27pF capacitor connected to XIN and a 33pF external capacitor connected to XOUT, the total load capacitance for the crystal is approximately 18pF. The XIN and XOUT pins can be left open if not used.

**Table 10. Crystal Selection Parameters**

| PARAMETER                          | SYMBOL         | MIN | TYP | MAX | UNITS |

|------------------------------------|----------------|-----|-----|-----|-------|

| Crystal Oscillation Frequency      | fosc           |     | 25  |     | MHz   |

| Shunt Capacitance                  | C <sub>0</sub> |     | 2.0 | 7.0 | pF    |

| Load Capacitance                   | CL             |     | 18  |     | pF    |

| Equivalent Series Resistance (ESR) | Rs             |     | 10  | 50  | Ω     |

| Maximum Crystal Drive Level        |                |     |     | 200 | μW    |

Figure 3. Crystal Equivalent Circuit

Figure 4. Crystal, Capacitor Connections

# **MAX3612**

### Low-Jitter Clock Generator with Nine LVDS/LVPECL Outputs

Figure 5. Crystal Layout

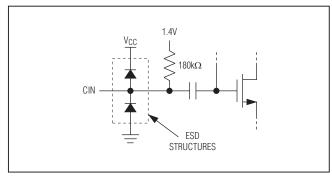

Figure 6. Equivalent CIN Circuit

Figure 7. Interface to CIN

#### **Interfacing with LVCMOS Input**

The equivalent LVCMOS input circuit for CIN is given in Figure 6. This input is internally biased to allow AC- or DC-coupling, and has  $180 k\Omega$  input impedance. See Figure 7 for the interface circuit. No signal should be applied to CIN if not used.

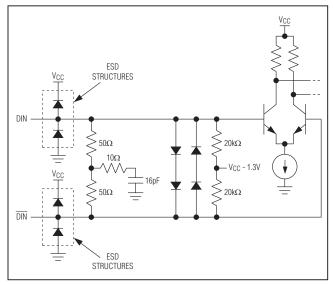

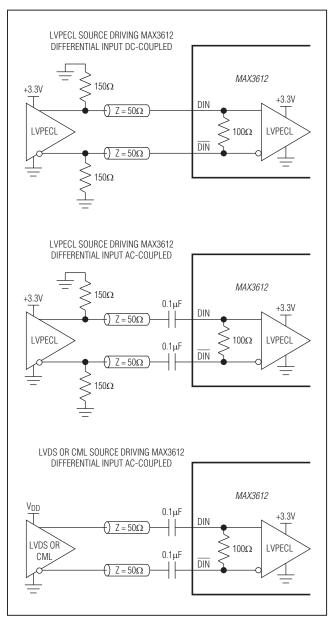

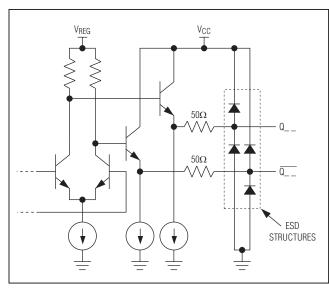

#### **Interfacing with Differential Input**

The equivalent input circuit for DIN is given in Figure 8. This input operates up to 350MHz and contains an internal  $100\Omega$  differential termination as well as a  $35\Omega$  common-mode termination. The common-mode termination ensures good signal integrity when connected to a source with large common-mode signals. The input can accept DC-coupled LVPECL signals, and is internally biased to accept AC-coupled LVDS, CML, and LVPECL signals (Figure 9). No signal should be applied to DIN if not used.

Figure 8. Equivalent DIN Circuit

Figure 9. Interfacing to DIN

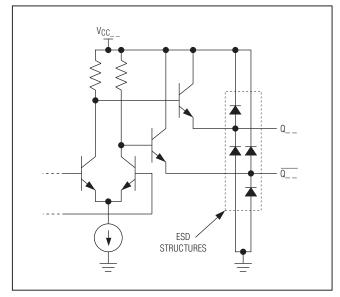

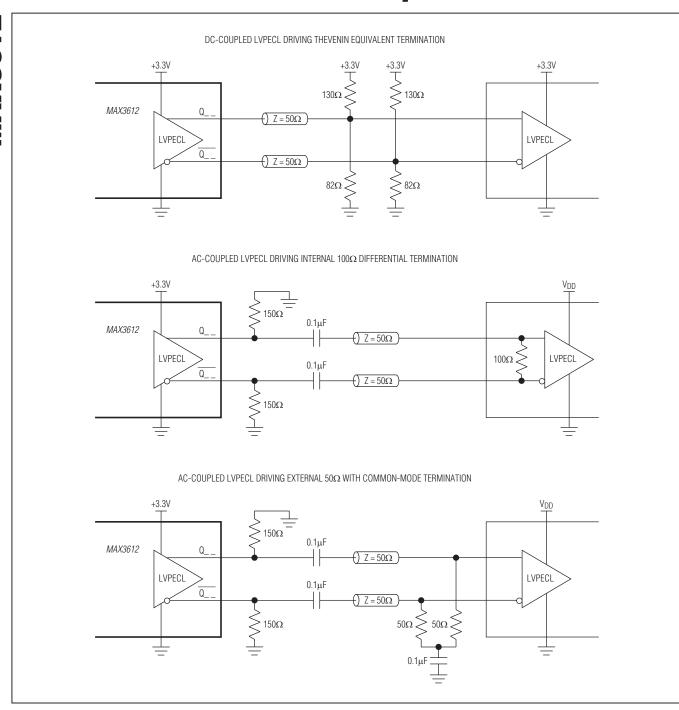

#### **Interfacing with LVPECL Outputs**

The equivalent LVPECL output circuit is given in Figure 10. These outputs are designed to drive a pair of  $50\Omega$  transmission lines terminated with  $50\Omega$  to  $V_{TT} = V_{CC}$  - 2V. If a separate termination voltage (V<sub>TT</sub>) is not available, other terminations methods can be used such as those shown in Figure 11. For more information on LVPECL terminations and how to interface with other logic families, refer to Application Note 291: HFAN-01.0: Introduction to LVDS, PECL, and CML.

Figure 10. Equivalent LVPECL Output Circuit

Figure 11. Interface to LVPECL Outputs

Figure 12. Equivalent LVDS Output Circuit

Figure 13. Interface to LVDS Outputs

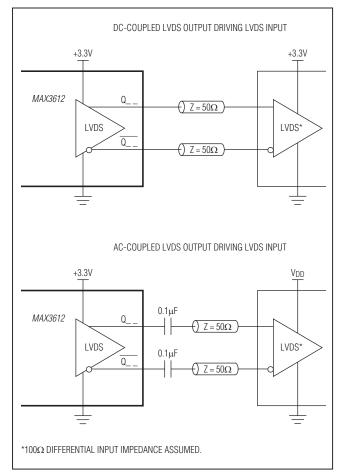

#### **Interfacing with LVDS Outputs**

The equivalent LVDS output circuit is given in Figure 12. These outputs provide  $100\Omega$  differential output impedance designed to drive a  $100\Omega$  differential transmission line terminated with a  $100\Omega$  differential load. Example interface circuits are shown in Figure 13. For more information on LVDS terminations and how to interface with other logic families, refer to Application Note 291: *HFAN-01.0: Introduction to LVDS, PECL, and CML*.

#### **Layout Considerations**

The inputs and outputs are the most critical paths for the MAX3612; great care should be taken to minimize discontinuities on the transmission lines. Here are some suggestions for maximizing the performance of the MAX3612:

- An uninterrupted ground plane should be positioned beneath the clock outputs. The ground plane under the crystal should be removed to minimize capacitance.

- Supply decoupling capacitors should be placed close to the supply pins, preferably on the same side of the board as the MAX3612.

- Take care to isolate input traces from the MAX3612 outputs.

- The crystal, trace, and two external capacitors should be placed on the board as close as possible to the XIN and XOUT pins to reduce crosstalk of active signals into the oscillator.

- Maintain  $100\Omega$  differential (or  $50\Omega$  single-ended) transmission line impedance into and out of the part.

- Provide space between differential output pairs to reduce crosstalk, especially if the outputs are operating at different frequencies.

- Use multilayer boards with an uninterrupted ground plane to minimize EMI and crosstalk.

Refer to the MAX3612 evaluation kit for more information.

\_Chip Information

PROCESS: BICMOS

#### **Pin Configuration**

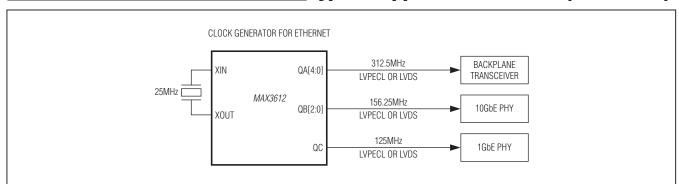

#### **Typical Application Circuits**

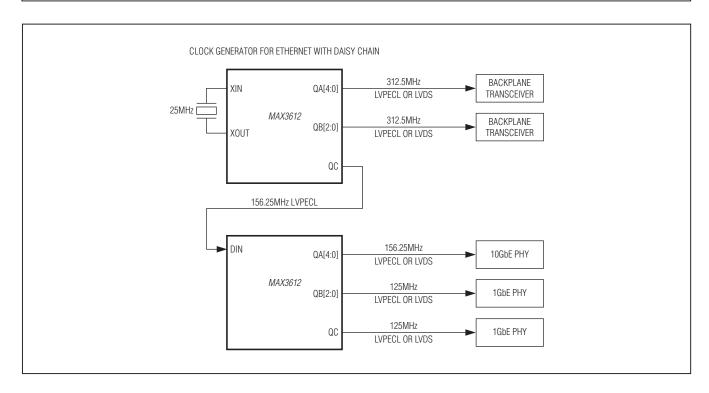

#### **Typical Application Circuits (continued)**

#### **Package Information**

For the latest package outline information and land patterns, go to **http://www.microsemi.com.** Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 48 TQFN-EP   | T4877+4      | <u>21-0144</u> | <u>90-0130</u>   |

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PAGES<br>CHANGED |

|--------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0                  | 11/09         | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                |

| 1                  | 6/10          | Added the lead and soldering temperatures to the <i>Absolute Maximum Ratings</i> section; changed the descriptions in the <i>Pin Description</i> table for RES2 (connect to VCC) and RES6 (connect to GND); replaced Figure 5 with customer board layout; revised the RES pin connections to match the <i>Pin Description</i> descriptions in the <i>Typical Application Circuits</i> ; updated the package code and added the land pattern no. to the <i>Package Information</i> table | 2, 7, 12, 17, 18 |

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo CA 92656 USA Within the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136 Fax: +1 (949) 215-4996 Microsemi Corporation (NASDAQ: MSCC) offers a comprehensive portfolio of semiconductor solutions for: aerospace, defense and security; enterprise and communications; and industrial and alternative energy markets. Products include high-performance, high-reliability analog and RF devices, mixed signal and RF integrated circuits, customizable SoCs, FPGAs, and complete subsystems. Microsemi is headquartered in Aliso Viejo, Calif. Learn more at **www.microsemi.com**.

© 2012 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.