## **Electrical Characteristics**

(Test conditions unless otherwise specified:  $T_A = 25$ °C;  $V_{IN} = 450$ V)

| Sym                | Parameter                                    | Min  | Тур   | Max  | Units | Conditions                                            |

|--------------------|----------------------------------------------|------|-------|------|-------|-------------------------------------------------------|

| V <sub>OUT</sub>   | Output voltage                               | 18.0 | -     | 24   | V     | I <sub>OUT</sub> = 0                                  |

|                    | V <sub>out</sub> over temperature            | 17.7 | -     | 24.3 | V     | I <sub>OUT</sub> = 0, T <sub>A</sub> = -40°C to +85°C |

| I <sub>out</sub>   | Output current limiting                      | 2.0  | 3.0   | 4.0  | mA    |                                                       |

| V <sub>IN</sub>    | Operating input voltage range                | 35   | -     | 450  | V     |                                                       |

| I <sub>INQ</sub>   | Input quiescent current                      | -    | -     | 500  | μA    | V <sub>IN</sub> = 400V, I <sub>OUT</sub> = 0          |

| V                  | Output turn off voltage                      | 12.6 | 13.25 | 13.9 | V     |                                                       |

| V <sub>OFF</sub>   | V <sub>OFF</sub> over temperature            | 12.3 | 13.25 | 14.2 | V     | T <sub>A</sub> = -40°C to +85°C                       |

| \/                 | Output reset voltage                         | 6.3  | 7.0   | 7.7  | V     |                                                       |

| V <sub>RESET</sub> | V <sub>RESET</sub> over temperature          | 6.0  | 7.0   | 8.0  | V     | T <sub>A</sub> = -40°C to +85°C                       |

| I <sub>OFF</sub>   | V <sub>IN</sub> off-state leakage current    | -    | -     | 75   | μA    | V <sub>IN</sub> = 400V                                |

| V <sub>AUX</sub>   | External voltage applied to V <sub>OUT</sub> | -    | -     | 22   | V     |                                                       |

| I <sub>AUX</sub>   | Input current applied to V <sub>OUT</sub>    | -    | -     | 500  | μA    | V <sub>AUX</sub> = 22V                                |

# **Block Diagram**

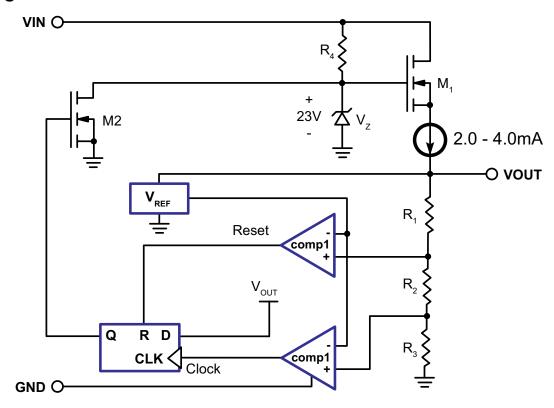

#### **Block Diagram Detailed Description**

The Supertex LR745 is a high voltage, switch-mode power supply start-up circuit which has 3 terminals: VIN, GND, and VOUT. An input voltage range of 35 - 450VDC can be applied directly at the input VIN pin. The output voltage,  $V_{\text{OUT}}$  is monitored by the 2 comparators, COMP1 and COMP2. An internal reference,  $V_{\text{REF}}$  and resistor divider  $R_1$ ,  $R_2$ , and  $R_3$  set the nominal  $V_{\text{OUT}}$  trip points of 7.0V for COMP1 and 13.25V for COMP2.

When a voltage is applied on VIN,  $V_{\text{OUT}}$  will start to ramp up from 0V. When  $V_{OUT}$  is less than 7.0V, the output of COMP1 will be at a logic high state, keeping the D flip flop in a reset state. The output of the D flip flop, Q, will be at logic low keeping transistor M<sub>2</sub> off. The data input for the D flip flop, D, is internally connected to a logic high. As V<sub>OUT</sub> becomes greater than 7.0V, COMP1 will change to a logic low state.  $V_{\text{\tiny OUT}}$  will continue to increase, and the constant current source of typically 3.0mA output will charge an external storage capacitor. As  $V_{OUT}$  reaches above 13.25V, the output of COMP2 will then switch from a logic high to a logic low state. The D flip flop's output does not change state since its clock input is designed to trigger only on a rising edge, logic low to logic high transition. When there is no load connected to the output, the output voltage will continue to increase until it reaches 21.5V, which is the zener voltage minus the threshold voltage of transistor M₁. The zener voltage is typically 23V, and the threshold voltage of M<sub>4</sub> is typically 1.5V. The zener diode is biased by resistor R<sub>4</sub>.

$V_{\text{OUT}}$  will start to decrease when it is connected to an external load greater than the internal constant current source, which is the case when the PWM IC starts up. When  $V_{\text{OUT}}$  falls below 13.25V, the output of COMP2 will switch from a logic low to a logic high. The output of COMP2 will clock in a logic 1 into the D flip flop, causing the D flip flop's output, Q, to switch from a logic low to a logic high. Transistor  $M_2$  will then be turned on pulling the gate of transistor  $M_1$  to ground, thereby turning transistor  $M_1$  off. Transistor  $M_2$  will remain off as long as  $V_{\text{OUT}}$  is greater than 7.0V. Once  $V_{\text{OUT}}$  decreases below 7.0V, COMP1 will reset the D flip flop, thereby turning transistor  $M_2$  off and transistor  $M_3$  back on.

## **Typical Application**

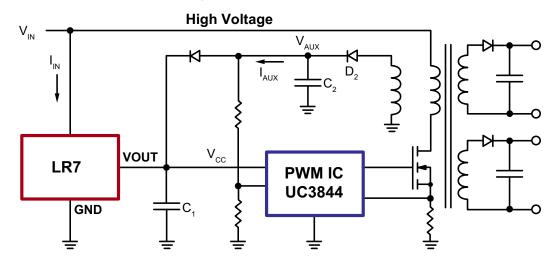

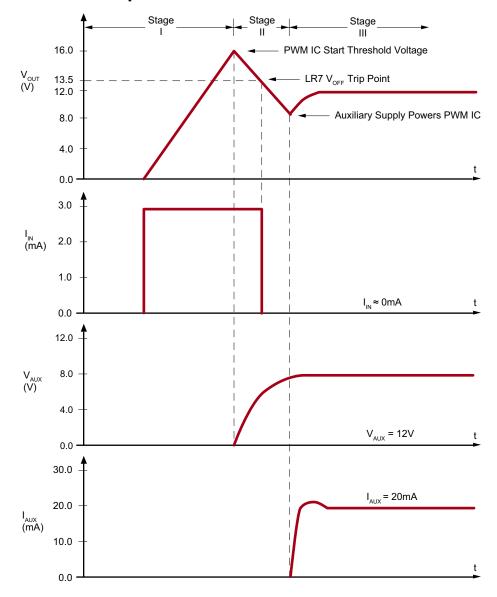

Figure 1 shows a simplified typical configuration of a switch-mode power supply, SMPS, using the Supertex LR745 in the start-up circuit.

The LR745's VOUT terminal is connected to the VCC line of a PWM IC, Unitrode part #UC3844. An auxiliary winding

on the transformer is used to generate a  $V_{\rm CC}$  voltage to power the PWM IC after start-up. The LR745 is used to supply power for the PWM IC only during start-up. After start-up, the LR745 turns off and the auxiliary winding is used to supply power for the PWM IC. Figure 2 shows the typical current and voltage waveforms at various stages from power up to operation powered by the auxiliary winding.

#### Stage I

Once a voltage is applied on VIN, the LR745 will start to charge the  $V_{\rm CC}$  capacitor,  $C_{\rm 1}$ . The  $V_{\rm CC}$  voltage will start to increase at a rate limited by the internal current limiter of 3.0mA. The PWM IC is in its start-up condition and will typically draw 0.5mA from the  $V_{\rm CC}$  line. The  $V_{\rm CC}$  voltage will continue to increase until it reaches the PWM IC's start threshold voltage of typically 16V.

#### Stage II

Once  $V_{\rm CC}$  reaches 16V, the PWM IC is in its operating condition and will draw typically 20mA, depending on the operating frequency and size of the switching MOSFET. The output of the LR745,  $V_{\rm OUT}$ , is internally current limited to 3.0mA. The remaining 17mA will be supplied by  $C_1$  causing the  $V_{\rm CC}$  voltage decrease. When  $V_{\rm CC}$  decreases to 13.25V, the LR745 will turn off its output, thereby reducing its input current from 3.0mA to 10s of microamperes. At this point, all 20mA will be supplied by  $C_1$ . The PWM IC can now operate to a minimum  $V_{\rm CC}$  voltage of typically 10V.

Once the switching MOSFET starts operating, the energy in the primary winding is transferred to the secondary outputs and the auxiliary winding, thereby building up  $V_{\text{AUX}}$ . It is necessary to size the  $V_{\text{CC}}$  storage capacitor,  $C_{\text{1}}$ , such that  $V_{\text{AUX}}$  increases to a voltage greater than 10V before  $V_{\text{CC}}$  decreases to 10V. This allows  $V_{\text{AUX}}$  to supply the required operating current for the PWM IC.

If for some reason the auxiliary voltage does not reach 10V,  $V_{\rm CC}$  will continue to decrease. Once  $V_{\rm CC}$  goes below 10V, the PWM IC will return to its start-up condition. The PWM IC will now only draw 0.5mA.  $V_{\rm CC}$  will continue to decrease but at a much slower rate. Once  $V_{\rm CC}$  decreases below 7.0V, the LR745 will turn the output,  $V_{\rm OUT}$  back on.  $V_{\rm OUT}$  will start charging  $C_{\rm 1}$  as described in Stage I.

#### Stage III

At this stage the LR745's output is turned off and the PWM IC is operating from the  $V_{AUX}$  supply. The auxiliary voltage,  $V_{AUX}$ , can be designed to vary anywhere between the minimum operating  $V_{CC}$  voltage of the PWM IC (10V) to the maximum auxiliary voltage rating of the LR745 (22V).

Figure 1: Simplified SMPS Using LR745

Figure 1: LR745 Start-up Waveforms

## **Design Considerations**

### I. Calculating the value for C,

Sizing the  $V_{\rm CC}$  capacitor,  $C_1$ , is an important factor. Making  $C_1$  too large will cause the SMPS to power up too slowly. However, if too small,  $C_1$  will not allow the SMPS to power up due to insufficient charge in the capacitor to power the IC and MOSFET until the auxiliary supply is available. The value of  $C_1$  can be approximated by the following equation:

$$C_{1} = \frac{\left[\frac{1}{f}\right] \cdot N \cdot I}{V_{START} - V_{MIN}}$$

where,

f = switching frequency

N = number of clock cycles required to charge  $V_{\text{AUX}}$  to  $V_{\text{MIN}}$  value

I = PWM operating current

V<sub>START</sub> = PWM IC start threshold rating

$V_{MIN}$  = PWM IC minimum  $V_{CC}$  operating voltage

Consider for example, a PWM IC with a switching frequency of 100KHz, operating current of 20mA, start threshold of 16V, and a minimum operating voltage of 10V. If 100 clock cycles are required to charge the auxiliary voltage to 10V, the minimum value of C<sub>1</sub> is calculated as follows:

$$C_{1} = \frac{\left[\frac{1}{100kHz}\right] \cdot 100 \cdot 20mA}{16V - 10V}$$

$$C_1 = 3.3 \mu F$$

#### II. SMPS with wide minimum to maximum load

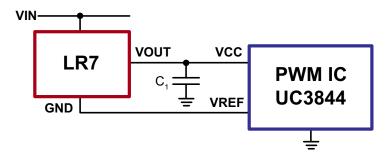

An important point is that the LR745's output voltage,  $V_{\text{OUT}}$  must discharge to below the nominal  $V_{\text{OFF}}$  trip point of 13.25V in order for its output to turn off. If the SMPS requires a wide minimum to maximum output load variation, it will be difficult to guarantee that  $V_{\text{CC}}$  will fall below 13.25V under minimum load conditions. Consider an SMPS that is required to power small as well as large loads and is also required to power up quickly. Such a SMPS may power up too fast with a small load, not allowing the  $V_{\text{CC}}$  voltage to fall below 13.25V. For such conditions, the circuit in Figure 3 is recommended.

In Figure 3, the VREF pin of the UC3844 is used to bias the ground pin of the LR745. The VREF pin on the UC3844 is a 5.0V reference, which stays at 0V until the  $\rm V_{CC}$  voltage reaches the start threshold voltage. Once  $\rm V_{CC}$  reaches the start threshold voltage,  $\rm V_{REF}$  will switch digitally from 0V to 5.0V. During start-up, the LR745 will be on, and  $\rm V_{CC}$  will start to increase up to 16V. Once  $\rm V_{CC}$  reaches16V, the UC3844 will start to operate and  $\rm V_{REF}$  will increase from 0V to 5.0V. The LR745 will see an effective  $\rm V_{OUT}$  voltage of 11V (16V minus 5.0V) because the ground of the LR745 is now at 5.0V. The LR745 will immediately turn off its output,  $\rm V_{OUT}$ , without having to wait for the  $\rm V_{CC}$  voltage to decrease. The  $\rm V_{REF}$  switching from 0 to 5.0V during start is a common feature in most PWM ICs.

## Figure 3: Using V<sub>REF</sub> for the LR745 Ground Voltage

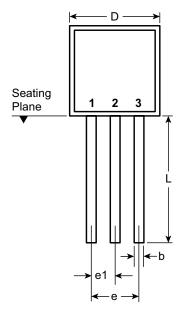

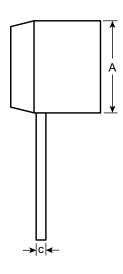

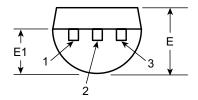

# 3-Lead TO-92 Package Outline (N3)

**Front View**

**Side View**

**Bottom View**

| Symbol              |     | Α    | b                 | С                 | D    | E    | E1   | е    | e1   | L     |

|---------------------|-----|------|-------------------|-------------------|------|------|------|------|------|-------|

| Dimensions (inches) | MIN | .170 | .014 <sup>†</sup> | .014 <sup>†</sup> | .175 | .125 | .080 | .095 | .045 | .500  |

|                     | NOM | -    | -                 | -                 | -    | -    | -    | -    | -    | -     |

|                     | MAX | .210 | .022 <sup>†</sup> | .022 <sup>†</sup> | .205 | .165 | .105 | .105 | .055 | .610* |

JEDEC Registration TO-92.

Drawings not to scale.

Supertex Doc.#: DSPD-3TO92N3, Version E041009.

<sup>\*</sup> This dimension is not specified in the JEDEC drawing.

<sup>†</sup> This dimension differs from the JEDEC drawing.

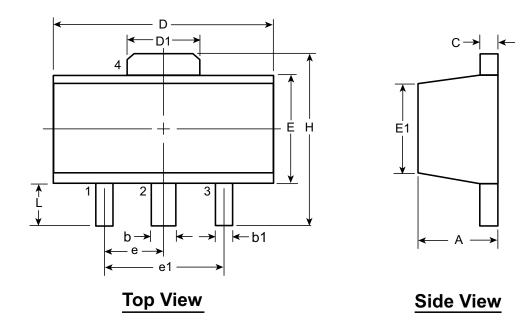

# 3-Lead TO-243AA (SOT-89) Package Outline (N8)

| Symbol          |     | Α    | b    | b1   | С    | D    | D1   | Е    | E1                | е           | e1          | Н    | L                 |

|-----------------|-----|------|------|------|------|------|------|------|-------------------|-------------|-------------|------|-------------------|

| Dimensions (mm) | MIN | 1.40 | 0.44 | 0.36 | 0.35 | 4.40 | 1.62 | 2.29 | 2.00 <sup>†</sup> | 1.50<br>BSC | 3.00<br>BSC | 3.94 | 0.73 <sup>†</sup> |

|                 | NOM | -    | -    | -    | -    | -    | -    | -    | -                 |             |             | -    | -                 |

|                 | MAX | 1.60 | 0.56 | 0.48 | 0.44 | 4.60 | 1.83 | 2.60 | 2.29              |             |             | 4.25 | 1.20              |

JEDEC Registration TO-243, Variation AA, Issue C, July 1986.

† This dimension differs from the JEDEC drawing

Drawings not to scale.

Supertex Doc. #: DSPD-3TO243AAN8, Version F111010.

(The package drawings in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="http://www.supertex.com/packaging.html">http://www.supertex.com/packaging.html</a>.)

**Supertex inc.** does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives an adequate "product liability indemnification insurance agreement." **Supertex inc.** does not assume responsibility for use of devices described, and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications refer to the **Supertex inc.** (website: http://www.supertex.com)

©2013 **Supertex inc.** All rights reserved. Unauthorized use or reproduction is prohibited.