## Allowable Operating Ranges at Ta = 25°C

| Parameter              | Symbol           | Conditions           | Ratings              | Unit |

|------------------------|------------------|----------------------|----------------------|------|

| Supply voltage range   | V <sub>CC</sub>  |                      | 4.5 to 6.7           | V    |

|                        | V <sub>M</sub>   |                      | 20 to 42             | V    |

| Input current range    | I <sub>REG</sub> | V <sub>REG</sub> pin | 1 to 5               | mA   |

| FG pin applied voltage | V <sub>FG</sub>  |                      | 0 to V <sub>CC</sub> | V    |

| FG pin output current  | I <sub>FG</sub>  |                      | 0 to 10              | mA   |

## Electrical Characteristics at Ta = 25 °C, $V_{CC} = 5V$ , $V_{M} = 30V$

| Parameter                        | Symbol                  | Conditions                                     | Ratings |            |                      | Unit  |

|----------------------------------|-------------------------|------------------------------------------------|---------|------------|----------------------|-------|

| Farameter                        | Symbol                  | Conditions                                     | min     | min typ ma |                      | Offic |

| Supply current                   | Icc                     |                                                | 10      | 14         | 18                   | mA    |

| Output Block                     |                         |                                                |         |            |                      |       |

| Output saturation voltage        | V <sub>O</sub> sat1(L)  | $I_O = 1.0A$ , $V_O(sink)$                     |         | 1.1        | 1.4                  | V     |

|                                  | V <sub>O</sub> sat1(H)  | I <sub>O</sub> = 1.0A, V <sub>O</sub> (source) |         | 0.9        | 1.3                  | V     |

|                                  | V <sub>O</sub> sat1     | $I_O = 1.0A$ , $V_O(sink) + V_O(source)$       |         | 2.0        | 2.6                  | V     |

|                                  | V <sub>O</sub> sat2(L)  | $I_O = 2.0A$ , $V_O(sink)$                     |         | 1.4        | 1.8                  | V     |

|                                  | V <sub>O</sub> sat2(H)  | I <sub>O</sub> = 2.0A, V <sub>O</sub> (source) |         | 1.2        | 1.7                  | V     |

|                                  | V <sub>O</sub> sat2     | $I_O = 2.0A$ , $V_O(sink) + V_O(source)$       |         | 2.6        | 3.4                  | V     |

| Output leak current              | I <sub>O</sub> Leak(L)  |                                                |         |            | 100                  | μΑ    |

|                                  | I <sub>O</sub> Leak(H)  |                                                | -100    |            |                      | μΑ    |

| Upper side diode forward voltage | V <sub>FH</sub> 1       | I <sub>O</sub> = 1.0A                          |         | 1.2        | 1.6                  | V     |

|                                  | V <sub>FH</sub> 2       | I <sub>O</sub> = 2.0A                          |         | 2.1        | 2.6                  | V     |

| Hall Amplifier                   | •                       |                                                |         |            |                      | •     |

| Input bias current               | I <sub>HB</sub>         |                                                | -4      | -1         |                      | μА    |

| Common-mode input voltage range  | VICM                    |                                                | 1.5     |            | V <sub>CC</sub> -1.5 | ٧     |

| Hall input sensitivity           | VHIN                    |                                                | 60      |            |                      | mVp-p |

| Hysteresis width                 | ΔV <sub>IN</sub> (HA)   |                                                | 23      | 32         | 39                   | mV    |

| Input voltage (low to high)      | V <sub>SLH</sub>        |                                                | 6       | 16         | 25                   | mV    |

| Input voltage (high to low)      | VSHL                    |                                                | -25     | -16        | -6                   | mV    |

| FG Pin (speed pulse output)      | •                       |                                                |         |            |                      | I.    |

| Output low-level voltage         | V <sub>FGL</sub>        | I <sub>FG</sub> = 5mA                          |         |            | 0.5                  | V     |

| Pull-up resistor value           | R <sub>FG</sub>         |                                                | 7.5     | 10         | 12.5                 | kΩ    |

| Current Limiter                  | 1                       |                                                |         |            |                      | I     |

| Limiter                          | V <sub>RF</sub>         |                                                | 0.45    | 0.50       | 0.55                 | V     |

| Thermal Shutdown                 |                         |                                                |         | '          |                      |       |

| Thermal shutdown operating       | TSD                     | Design target Value (junction temperature)     | 150     | 180        |                      | °C    |

| temperature                      |                         |                                                |         |            |                      |       |

| Hysteresis width                 | ΔTSD                    | Design target Value (junction temperature)     |         | 40         |                      | °C    |

| Low-Voltage Protection           | 1                       |                                                | I I     | 1          |                      | ı     |

| Operating voltage                | V <sub>LVSD</sub>       |                                                | 3.5     | 3.8        | 4.1                  | V     |

| Non-operating voltage            | V <sub>LVSD</sub> (OFF) |                                                |         | 4.3        | 4.5                  | V     |

| Hysteresis width                 | ∆VLVSD                  |                                                | 0.4     | 0.5        | 0.6                  | V     |

| PWM Oscillator                   | 1                       | <u></u>                                        | 1       | 1          |                      | 1     |

| Output high-level voltage        | V <sub>OH</sub> (OSC)   |                                                | 2.95    | 3.10       | 3.25                 | V     |

| Output low-level voltage         | V <sub>OL</sub> (OSC)   |                                                | 1.38    | 1.45       | 1.59                 | V     |

| Amplitude                        | Vosc                    |                                                | 1.50    | 1.65       | 1.71                 | Vp-p  |

| Oscillator frequency             | fosc                    | C = 2200pF                                     | 19.6    | 23.0       | 27.6                 | kHz   |

| Charge current                   | I <sub>CHG</sub>        |                                                | -110    | -94        | -83                  | μΑ    |

| Discharge resistance             | R <sub>DCHG</sub>       |                                                | 1.6     | 2.1        | 2.6                  | kΩ    |

| V <sub>REG</sub> Pin             |                         |                                                |         |            |                      |       |

| Pin voltage                      | V <sub>REG</sub>        | I <sub>REG</sub> = 1.5mA                       | 6.6     | 7.0        | 7.2                  | V     |

Continued on next page.

## LB1975

### Continued from preceding page.

| Development                    | Comple el              | Conditions            |                      | Ratings |      |      |  |  |

|--------------------------------|------------------------|-----------------------|----------------------|---------|------|------|--|--|

| Parameter                      | Symbol                 | Conditions            | min                  | typ     | max  | Unit |  |  |

| V <sub>CTL</sub> Pin           |                        |                       |                      |         |      |      |  |  |

| Input voltage                  | V <sub>CTL</sub> 1     | Output duty 0%        | 1.1                  | 1.4     | 1.7  | V    |  |  |

|                                | V <sub>CTL</sub> 2     | Output duty 100%      | 3.2                  | 3.5     | 3.8  | V    |  |  |

| Input bias current             | I <sub>B</sub> 1(CTL)  | V <sub>CTL</sub> = 0V | -82                  |         |      | μА   |  |  |

|                                | I <sub>B</sub> 2(CTL)  | V <sub>CTL</sub> = 5V |                      |         | 92   | μА   |  |  |

| V <sub>CTL</sub> Amplifier     |                        |                       |                      |         |      |      |  |  |

| Reference voltage              | VCREF                  |                       | 2.23                 | 2.35    | 2.46 | V    |  |  |

| Output voltage                 | V <sub>COUT</sub> 1    | V <sub>CTL</sub> = 0V | 3.90                 | 4.20    | 4.40 | V    |  |  |

|                                | V <sub>COUT</sub> 2    | V <sub>CTL</sub> = 5V | 0.60                 | 0.80    | 1.10 | ٧    |  |  |

| Start/Stop Pin                 |                        |                       |                      |         |      |      |  |  |

| High-level input voltage range | V <sub>IH</sub> (S/S)  |                       | V <sub>CC</sub> -1.5 |         | Vcc  | V    |  |  |

| Low-level input voltage range  | V <sub>IL</sub> (S/S)  |                       | 0                    |         | 1.5  | >    |  |  |

| Input open voltage             | V <sub>IO</sub> (S/S)  |                       | V <sub>CC</sub> -0.5 |         | VCC  | >    |  |  |

| Hysteresis width               | ΔV <sub>IN</sub> (S/S) |                       | 0.35                 | 0.50    | 0.65 | >    |  |  |

| High-level input current       | I <sub>IH</sub> (S/S)  | $V(S/S) = V_{CC}$     | -10                  | 0       | +10  | μА   |  |  |

| Low-level input current        | I <sub>IL</sub> (S/S)  | V(S/S) = 0V           | -280                 | -210    |      | μА   |  |  |

| Forward/Reverse Pin            |                        |                       |                      |         |      |      |  |  |

| High-level input voltage range | V <sub>IH</sub> (F/R)  |                       | V <sub>CC</sub> -1.5 |         | Vcc  | V    |  |  |

| Low-level input voltage range  | V <sub>IL</sub> (F/R)  |                       | 0                    |         | 1.5  | V    |  |  |

| Input open voltage             | V <sub>IO</sub> (F/R)  |                       | V <sub>CC</sub> -0.5 |         | Vcc  | V    |  |  |

| Hysteresis width               | ΔV <sub>IN</sub> (F/R) |                       | 0.35                 | 0.50    | 0.65 | V    |  |  |

| High-level input current       | I <sub>IH</sub> (F/R)  | $V(F/R) = V_{CC}$     | -10                  | 0       | +10  | μА   |  |  |

| Low-level input current        | I <sub>IL</sub> (F/R)  | V(F/R) = 0V           | -280                 | -210    |      | μА   |  |  |

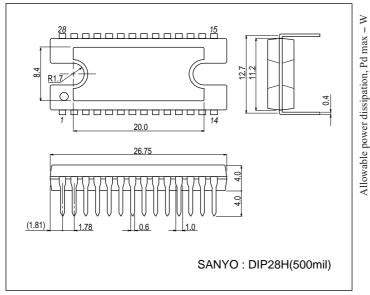

# **Package Dimensions**

unit : mm (typ) 3147C

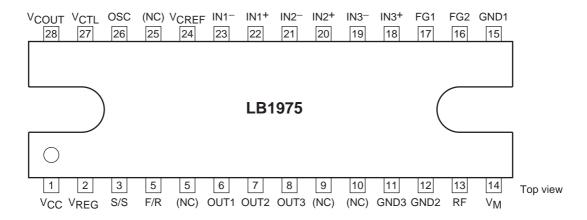

## **Pin Assignment**

### **Truth Table**

|   | Input |     |     | Forward/reverse control | Output        | FG o | utput |             |

|---|-------|-----|-----|-------------------------|---------------|------|-------|-------------|

|   | IN1   | IN2 | IN3 | F/R                     | Source → Sink | FG1  | FG2   |             |

| 1 | н ь   |     | Н   | L                       | OUT2 → OUT1   |      | L     |             |

| ı | П     | L   | П   | Н                       | OUT1 → OUT2   | L    | L     |             |

| 2 | Н     |     |     | L                       | OUT3 → OUT1   |      | н     |             |

| 2 | П     | L   | _   | Н                       | OUT1 → OUT3   | L    | п<br> |             |

| 3 | Ι     | н   |     | L                       | OUT3 → OUT2   |      | L     |             |

| 3 |       |     |     | П                       | П             | L    | Н     | OUT2 → OUT3 |

| 4 |       | Н   |     | L                       | OUT1 → OUT2   | Н    | Н     |             |

| 4 | L     | П   | L   | Н                       | OUT2 → OUT1   | Н    |       |             |

| 5 |       |     | Н   | L                       | OUT1 → OUT3   |      |       |             |

| o | L     | Н   | П   | Н                       | OUT3 → OUT1   | Н    | L     |             |

| 6 |       |     | L   | L                       | OUT2 → OUT3   |      | н     |             |

| 0 |       | L   | Н   | Н                       | OUT3 → OUT2   | Н    | П     |             |

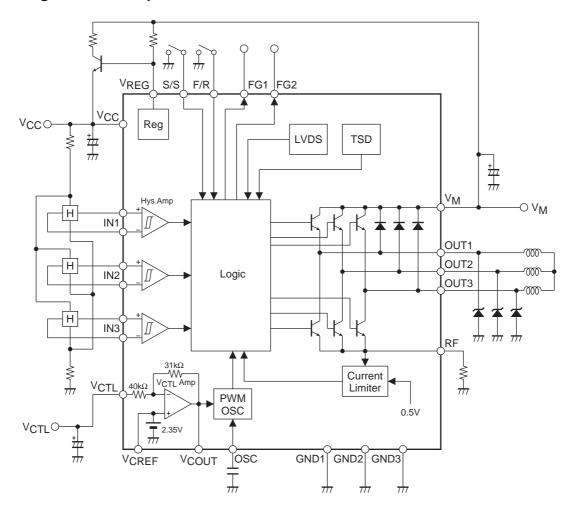

## **Block Diagram and Peripheral Circuit**

## **Pin Functions**

| Pin No. | Pin name        | Pin voltage             | Function                                                                                                                                                              | Equivalent circuit |

|---------|-----------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 1       | V <sub>CC</sub> | 4.5V to 6.7V            | Power supply for blocks other than the output block.                                                                                                                  |                    |

| 2       | VREG            | 0.0V to 7.3V            | Shunt regulator output pin (7V).                                                                                                                                      | 2                  |

| 3       | S/S             | 0.0V to V <sub>CC</sub> | Start/stop control pin.  Low: start  High or Open: stop  Typical threshold voltage for  V <sub>CC</sub> = 5V:  approx. 2.8V (low to high)  approx. 2.3V (high to low) | Vcc \$20kΩ 3.8kΩ 3 |

Continued on next page.

### Continued from preceding page.

| Pin No.                          | Pin name                                     | Pin voltage                       | Function                                                                                                                                                                  | Equivalent circuit                                |

|----------------------------------|----------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| 4                                | F/R                                          | 0.0V to V <sub>CC</sub>           | Forward/reverse pin. Low: forward High or Open: reverse  Typical threshold voltage for V <sub>CC</sub> = 5V: approx. 2.8V (low to high) approx. 2.3V (high to low)        | VCC<br>\$20kΩ<br>3.8kΩ<br>4                       |

| 6<br>7<br>8                      | OUT1<br>OUT2<br>OUT3                         |                                   | Output pin 1. Output pin 2. Output pin 3.                                                                                                                                 | V <sub>CC</sub> (14)                              |

| 13                               | RF                                           | 0.0V to V <sub>CC</sub>           | Output current detect pin.  Connect resistor Rf between this pin and ground. Output current is limited to value set with V <sub>RF</sub> /Rf. (Current limiter operation) | 0.5V 8 8 120ΩΩ                                    |

| 14                               | ٧ <sub>M</sub>                               |                                   | Output block power supply.                                                                                                                                                |                                                   |

| 11                               | GND3                                         |                                   | Output block ground.                                                                                                                                                      |                                                   |

| 15<br>12                         | GND1<br>GND2                                 |                                   | Ground for blocks other than the output block.                                                                                                                            |                                                   |

| 17                               | FG1                                          | 0.0V to V <sub>CC</sub>           | Speed pulse output pin 1 with built-in pull-up resistor.                                                                                                                  | V <sub>CC</sub> \$10kΩ 16(17)                     |

| 16                               | FG2                                          | 0.0V to V <sub>CC</sub>           | Speed pulse output pin 2 with built-in pull-up resistor.                                                                                                                  |                                                   |

| 22<br>23<br>20<br>21<br>18<br>19 | IN1+<br>IN1-<br>IN2+<br>IN2-<br>IN3+<br>IN3- | 1.5V to<br>V <sub>CC</sub> – 1.5V | Hall input pin. IN+ > IN-: High input IN+ < IN-: Low input                                                                                                                | V <sub>CC</sub> (18) (300Ω (21) (22) (23)         |

| 26                               | OSC                                          | 1.0V to V <sub>CC</sub>           | This pin sets the PWM oscillation frequency. Connect a capacitor between this pin and ground.                                                                             | VCC<br>2V 94μΑ<br>200Ω<br>W<br>2.1kΩ §<br>777 777 |

Continued on next page.

## LB1975

### Continued from preceding page.

| Pin No. | Pin name | Pin voltage                       | Function                                                                                                                                                 | Equivalent circuit                                                          |

|---------|----------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

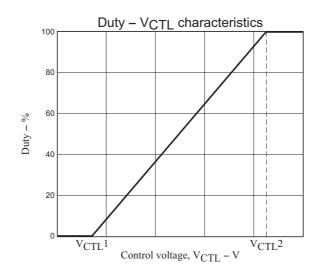

| 27      | VCTL     | 0.0V to 6.7V                      | Output duty cycle control pin.  • VCTL ≤ VCTL1  Duty cycle 0%  • VCTL1 < VCTL < VCTL2  Duty cycle is controlled by VCTL  • VCTL ≥ VCTL2  Duty cycle 100% | 31kΩ<br>W VCC  40kΩ 2.35V  77                                               |

| 24      | VCREF    | 0.0V to<br>V <sub>CC</sub> – 2.0V | V <sub>CTL</sub> amplifier internal reference voltage pin (2.35V).                                                                                       | V <sub>CC</sub> 100μA 200Ω 23.5kΩ 23.777 777 777 777 777 777 777 777 777 77 |

| 28      | VCOUT    | 0.7V to<br>V <sub>CC</sub> – 0.7V | V <sub>CTL</sub> amplifier output pin.                                                                                                                   | V <sub>CC</sub> 28 31kΩ W 200Ω W 200Ω W 777 777 777 777 777 777 777 777 777 |

### **IC Description**

#### 1. Direct PWM Drive

The LB1975 employs the direct PWM drive principle. Motor rotation speed is controlled by varying the output duty cycle according to an analog voltage input (V<sub>CTL</sub>). This eliminates the need to alter the motor power supply voltage. Compared to previous ICs using the PAM principle (such as the Sanyo LB1690), this allows simplification of the power supply circuitry. The V<sub>CTL</sub> input can be directly supplied by a microcontroller, motor speed can, therefore, be controlled directly from the microcontroller.

For PWM, the source-side output transistors are switched on and off so that the ON duty tracks the V<sub>CTL</sub> input. The output duty cycle can be controlled over the range of 0% to 100% by the V<sub>CTL</sub> input.

#### 2. PWM Frequency

The PWM oscillator frequency fpwm [Hz] is set by the capacitance C [pF] connected between the OSC pin and GND. The following equation applies:

$f_{PWM} \approx 1 / (1.97 \times C) \times 10^8$

Because output transistor on/off switching is subject to a delay, setting the PWM frequency to a very high value will cause the delay to become noticeable. The PWM frequency therefore should normally be kept below 40kHz (typ.), which is achieved with a capacitance C of 1300pF or higher. For reference, the source-side output transistor switching delay time is about  $2\mu s$  for ON and about  $4\mu s$  for OFF.

#### 3. Output Diodes

Because the PWM switching operation is carried out by the source-side output transistors, Schottky barrier diodes must be connected between the OUT pins and GND (OUT1 to OUT3). Use diodes with an average forward current rating in the range of 1.0 to 2.0A, in accordance with the motor type and current limiting requirements.

If no Schottky barrier diodes are connected externally, or if Schottky barrier diodes with high forward voltage  $(V_F)$  are used, the internal parasitic diode between OUT and GND becomes active. When this happens, the output logic circuit may malfunction, resulting in feed-through current in the output which can destroy the output transistors. To prevent this possibility, Schottky barrier diodes must be used and dimensioned properly.

The larger the  $V_F$  of the externally connected Schottky barrier diodes, or the hotter the IC is, the more likely are the parasitic diodes between OUT and GND to become active and the more likely is malfunction to occur. The  $V_F$  of the Schottky barrier diodes must be determined so that output malfunction does not occur also when the IC becomes hot. If malfunction occurs, choose a Schottky barrier diode with lower  $V_F$ .

#### 4. Protection circuits

#### 4-1. Low voltage protection circuit

When the  $V_{CC}$  voltage falls below a stipulated level ( $V_{LVSD}$ ), the low voltage protection circuit cuts off the source-side output transistors to prevent  $V_{CC}$  related malfunction.

#### 4-2. Thermal shutdown circuit (overheat protection circuit)

When the junction temperature rises above a stipulated value (TSD), the thermal shutdown circuit cuts off the sourceside output transistors to prevent IC damage due to overheating. Design the application heat characteristics so that the protection circuit will not be triggered under normal circumstances.

#### 4-3. Current limiter

The current limiter cuts off the source-side output transistors when the output current reaches a preset value (limiter value). This interrupts the source current and thereby limits the output current peak value. By connecting the resistance Rf between the RF pin and ground, the output current can be detected as a voltage. When the RF pin voltage reaches 0.5V (typ.), the current limiter is activated. It performs on/off control of the source-side output transistors, thereby limiting the output current to the value determined by 0.5/Rf.

#### 5. Hall Input Circuit

The Hall input circuit is a differential amplifier with a hysteresis of 32mV (typ.). The operation DC level must be within the common-mode input voltage range (1.5V to  $V_{CC}-1.5V$ ). To prevent noise and other adverse influences, the input level should be at least 3 times the hysteresis (120 to 16mVp-p). If noise at the Hall input is a problem, a noise-canceling capacitor (about  $0.01\mu\text{F}$ ) should be connected across the Hall input IN<sup>+</sup> and IN<sup>-</sup> pins.

#### 6. FG Output Circuit

The Hall input signal at IN1, IN2, and IN3 is combined and subject to waveform shaping before being output. The signal at FG1 has the same frequency as the FG1 Hall input, and the signal at FG2 has a frequency that is three times higher.

#### LB1975

#### 7. Start/Stop Control Circuit

The start/stop control circuit turns the source-side output transistors OFF (motor stop) when a High signal is input at the S/S pin or when the pin is Open. When a Low signal is input at the S/S pin, the source-side output transistors are turned ON, and the normal operation state is established (motor start).

#### 8. Forward/Reverse Switching

The LB1975 is designed under the assumption that forward/reverse switching is not carried out while the motor is running. If switching is carried out while the motor is running, reverse torque braking occurs, leading to a high current flow. If the current limiter is triggered, the source-side output transistors are switched off, and the sink-side output transistors go into the short brake condition. However, because the current limiter of this IC cannot control the current flowing in the sink-side output transistors, these may be destroyed by the short brake current. Therefore F/R switching while the motor is running is permissible only if the output current (I<sub>O</sub>) is limited to a maximum of 2.5A using the motor coil resistance or other suitable means.

F/R switching should be carried out only while a High signal is input to the S/S pin or the pin is Open (stop condition), or while the VCTL pin conforms to the following condition:  $V_{CTL} \le V_{CTL} 1$  (duty cycle 0%). In any other condition, F/R switching will result in feed-through current. The F/R pin should therefore be fixed to Low (forward) or High or Open (reverse) during use.

#### 9. VCC, VM Power Supplies

When the power supply voltage (VCC, VM) rises very quickly when a power is first applied, a feed-through current may occur at the output. If the current remains below about 0.2A to 0.3A, it does not pose a problem, but such a possibility should still be prevented by slowing down the voltage rise at power-on. Especially if the F/R pin is set to High or Open (reverse), a quick rise in VCC is likely to cause feed-through current. This should be prevented by ensuring that  $\Delta V_{CC}$  /  $\Delta t = 0.2V/\mu s$  or less. Feed-through current can also be prevented by first switching on V<sub>CC</sub> and then V<sub>M</sub> during power-on.

The sequence at power-down should be as follows. Provide a stop input to the S/S pin or a duty ratio 0% input to the VCTL pin. When the motor has come to a full stop, switch off  $V_M$  and then VCC. If power is switched off while the motor is still rotating or a current is flowing in the motor coil (including motor restraint or inertia rotation), a counter electromotive current or kickback current may flow on the  $V_M$  side, depending on the motor type and power-off procedure. If this current cannot be absorbed by the  $V_M$  power supply or a capacitor,  $V_M$  voltage may rise and exceed the absolute maximum  $V_M$  rating for the IC. Ensure that this does not happen through proper design of the  $V_M$  power supply or through use of a capacitor.

Because the LB1975 incorporates a shunt regulator, it can be used on a single power supply. In this case, supply  $V_{CC}$  (6.3V typ.) to the  $V_{REG}$  pin via an external NPN transistor and resistor. When not using the regulator, leave the  $V_{REG}$  pin open.

#### 10. Power Supply Stabilizing Capacitors

If the  $V_{CC}$  line fluctuates drastically, the low-voltage protection circuit may be activated by mistake, or other malfunctions may occur. The  $V_{CC}$  line must therefore be stabilized by connecting a capacitor of at least several  $\mu F$  between  $V_{CC}$  and GND. Because a large switching current flows in the  $V_M$  line, wiring inductance and other factors can lead to  $V_M$  voltage fluctuations. As the GND line also fluctuates, the  $V_M$  line must be stabilized by connecting a capacitor of at least several  $\mu F$  between VM and GND, to prevent exceeding  $V_M$  max or other problems. Especially when long wiring runs ( $V_M$ ,  $V_{CC}$ , GND) are used, sufficient capacitance should be provided to ensure power supply stability.

#### 11. VCREF Pin, VCOUT Pin

These pins are always used in the Open condition. If chattering occurs in the PWM switching output, connect a capacitor (about  $0.1\mu\text{F}$ ) between V<sub>CREF</sub> and ground or between V<sub>COUT</sub> and GND.

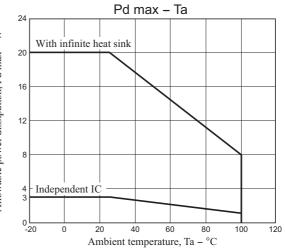

### 12. IC Heat Dissipation Fins

A heat sink may be mounted to the heat dissipation fins of this IC, but it may not be connected to GND. The sink should be electrically open.

#### 13. Sample calculation for internal power dissipation (approximate)

The calculation assumes the following parameters:

$V_{CC} = 5V$

$V_{\mathbf{M}} = 30V$

Source-side output transistor ON duty cycle 80% (PWM control)

Output current  $I_O = 1A$  (RF pin average current)

(1) ICC power dissipation P1

$$P1 = V_{CC} \times I_{CC} = 5V \times 14mA = 0.07W$$

(2) Output drive current power dissipation P2

$$P2 = V_M \times 11mA = 30V \times 11mA = 0.33W$$

(3) Source-side output transistor power dissipation P3

$$P3 = V_O(\text{source}) \times I_O \times \text{Duty}(\text{on}) = 0.9V \times 1A \times 0.8 = 0.72W$$

(4) Sink-side output transistor power dissipation P4

$$P4 = V_O(sink) \times I_O = 1.1V \times 1A = 1.10W$$

(5) Total internal power dissipation P

$$P = P1 + P2 + P3 + P4 = 2.22W$$

#### 14. IC temperature Rise Measurement

Because the chip temperature of the IC cannot be measured directly, measurement according to one of the following procedures should always be carried out.

#### 14-1. Thermocouple measurement

A thermocouple element is mounted to the IC heat dissipation fin. This measurement method is easy to implement, but it will be subject to measurement errors if the temperature is not stable.

#### 14-2. Measurement using internal diode characteristics of IC

This is the recommended measurement method. It makes use of the parasitic diode incorporated in the IC between FG1 and GND. Set FG1 to High and measure the voltage  $V_F$  of the parasitic diode to calculate the temperature. (Sanyo data: for  $I_F = -1$ mA,  $V_F$  temperature characteristics are about -2mV/ $^{\circ}$ C)

#### 15. NC Pins

Because NC pins are electrically open, they may be used for wiring purpose etc.

- SANYO Semiconductor Co.,Ltd. assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO Semiconductor Co.,Ltd. products described or contained herein.

- SANYO Semiconductor Co.,Ltd. strives to supply high-quality high-reliability products, however, any and all semiconductor products fail or malfunction with some probability. It is possible that these probabilistic failures or malfunction could give rise to accidents or events that could endanger human lives, trouble that could give rise to smoke or fire, or accidents that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO Semiconductor Co.,Ltd. products described or contained herein are controlled under any of applicable local export control laws and regulations, such products may require the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written consent of SANYO Semiconductor Co.,Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO Semiconductor Co.,Ltd. product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production.

- Upon using the technical information or products described herein, neither warranty nor license shall be granted with regard to intellectual property rights or any other rights of SANYO Semiconductor Co.,Ltd. or any third party. SANYO Semiconductor Co.,Ltd. shall not be liable for any claim or suits with regard to a third party's intellectual property rights which has resulted from the use of the technical information and products mentioned above.

This catalog provides information as of December, 2008. Specifications and information herein are subject to change without notice.