#### **Table of Contents**

# **Table of Contents**

| 1                                                                                                                    | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                              |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 2                                                                                                                    | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                              |

| <b>3</b><br>3.1<br>3.2<br>3.3                                                                                        | Pin Configuration         Pin Assignment         Pin Definitions and Functions         Voltage and Current Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7<br>7                                                         |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.3.1<br>4.3.2                                                                      | General Product Characteristics         Absolute Maximum Ratings         Functional Range         Thermal Resistance         PCB set up         Thermal Impedance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9<br>11<br>12<br>12                                            |

| <b>5</b><br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.3.2<br>5.4<br>5.5                                                        | Power Stage         Output ON-state Resistance         Turn ON/OFF Characteristics with Resistive Load         Inductive Load         Output Clamping         Maximum Load Inductance         Inverse Current Capability         Electrical Characteristics Power Stage                                                                                                                                                                                                                                                                                                                                                                                                            | 15<br>16<br>16<br>16<br>17<br>19                               |

| <b>6</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.5.1<br>6.5.2<br>6.6                                                 | Protection Functions<br>Loss of Ground Protection<br>Undervoltage Protection<br>Overvoltage Protection<br>Reverse Polarity Protection<br>Overload Protection<br>Current Limitation<br>Temperature Limitation in the Power DMOS<br>Electrical Characteristics for the Protection Functions                                                                                                                                                                                                                                                                                                                                                                                          | 21<br>22<br>22<br>23<br>23<br>23<br>25                         |

| <b>7</b><br>7.1<br>7.2<br>7.3.1<br>7.3.2<br>7.3.3<br>7.3.3.1<br>7.3.3.2<br>7.3.3.3<br>7.3.4<br>7.3.5<br>7.3.6<br>7.4 | $\begin{array}{c} \textbf{Diagnostic Functions} \\ \text{IS Pin} \\ \text{SENSE Signal in Different Operating Modes} \\ \text{SENSE Signal in the Nominal Current Range} \\ \text{SENSE Signal Variation as a Function of Temperature and Load Current} \\ \text{SENSE Signal Timing} \\ \text{SENSE Signal in Open Load} \\ \text{Open Load in ON Diagnostic} \\ \text{Open Load in OFF Diagnostic} \\ \text{Open Load Diagnostic Timing} \\ \text{SENSE Signal with OUT in Short Circuit to } V_{\text{S}} \\ \text{SENSE Signal in Case of Overload} \\ \text{SENSE Signal in Case of Inverse Current} \\ \text{Electrical Characteristics Diagnostic Function} \\ \end{array}$ | 26<br>27<br>28<br>29<br>30<br>30<br>30<br>31<br>31<br>32<br>32 |

| <b>8</b><br>8.1<br>8.2                                                                                               | Input Pins Input Circuitry DEN / DSEL Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 36                                                             |

#### **Table of Contents**

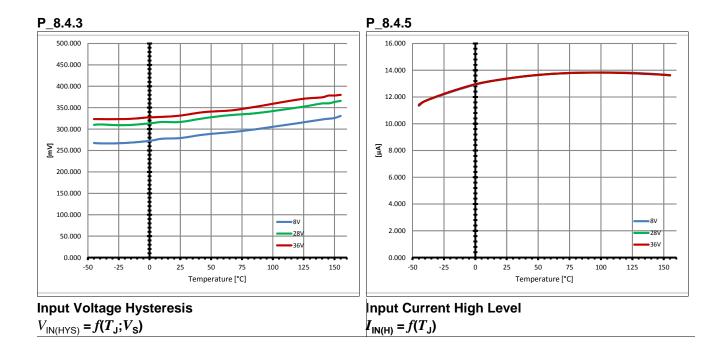

| 8.3<br>8.4                                  | Input Pin Voltage       36         Electrical Characteristics       37                                                           |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| <b>9</b><br>9.1<br>9.2<br>9.3<br>9.4<br>9.5 | Characterization Results38General Product Characteristics38Power Stage39Protection Functions47Diagnostic Mechanism42Input Pins43 |

| <b>10</b><br>10.1                           | Application Information       44         Further Application Information       45                                                |

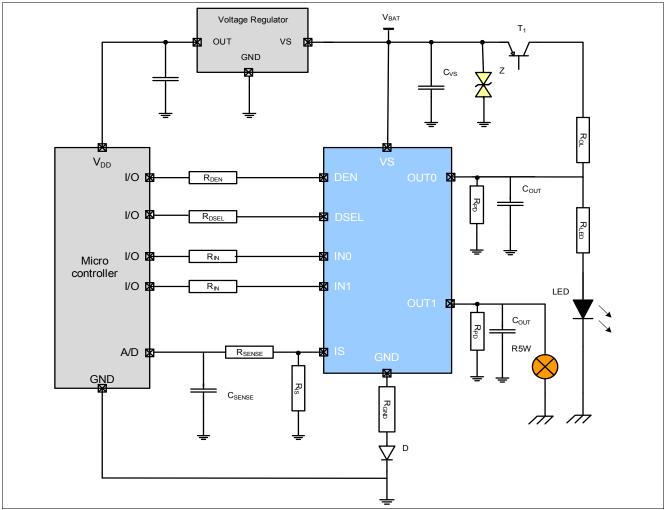

| 11                                          | Package Outlines                                                                                                                 |

| 12                                          | Revision History                                                                                                                 |

# **Smart High-Side Power Switch**

#### **BTT6100-2EKA**

#### Application

- · Suitable for resistive, inductive and capacitive loads

- Replaces electromechanical relays, fuses and discrete circuits

- · Most suitable for loads with high inrush current, such as lamps

- Suitable for 24V Trucks and Transportation System

#### **Basic Features**

- Dual channel device

- Very low stand-by current

- 3.3 V and 5 V compatible logic inputs

- Electrostatic discharge protection (ESD)

- Optimized electromagnetic compatibility

- Logic ground independent from load ground

- Very low power DMOS leakage current in OFF state

- Green product (RoHS compliant)

- AEC qualified

#### Description

The BTT6100-2EKA is a 100 m $\Omega$  dual channel Smart High-Side Power Switch, embedded in a PG-DSO-14-40 EP, Exposed Pad package, providing protective functions and diagnosis. The power transistor is built by an N-channel vertical power MOSFET with charge pump. The device is integrated in Smart6 HV technology. It is specially designed to drive lamps up to 1x P21W 24V or 1x R10W 12V, as well as LEDs in the harsh automotive environment.

#### Table 1 Product Summary

| Parameter                                                 | Symbol               | Value    |

|-----------------------------------------------------------|----------------------|----------|

| Operating voltage range                                   | V <sub>S(OP)</sub>   | 5 V 36 V |

| Maximum supply voltage                                    | V <sub>S(LD)</sub>   | 65 V     |

| Maximum ON state resistance at $T_J$ = 150 °C per channel | R <sub>DS(ON)</sub>  | 200 mΩ   |

| Nominal load current (one channel active)                 | I <sub>L(NOM)1</sub> | 2.6 A    |

| Nominal load current (all channels active)                | I <sub>L(NOM)2</sub> | 2.2 A    |

| Typical current sense ratio                               | k <sub>ILIS</sub>    | 600      |

| Туре         | Package         | Marking      |

|--------------|-----------------|--------------|

| BTT6100-2EKA | PG-DSO-14-40 EP | BTT6100-2EKA |

PG-DSO-14-40 EP

Overview

#### Table 1 Product Summary (cont'd)

| Parameter                                                | Symbol              | Value  |

|----------------------------------------------------------|---------------------|--------|

| Minimum current limitation                               | I <sub>L5(SC)</sub> | 20 A   |

| Maximum standby current with load at $T_{\rm J}$ = 25 °C | I <sub>S(OFF)</sub> | 500 nA |

#### **Diagnostic Functions**

- Proportional load current sense multiplexed for the 2 channels

- · Open load detection in ON and OFF

- Short circuit to battery and ground indication

- · Overtemperature switch off detection

- Stable diagnostic signal during short circuit

- Enhanced k<sub>ILIS</sub> dependency with temperature and load current

#### **Protection Functions**

- Stable behavior during undervoltage

- · Reverse polarity protection with external components

- Secure load turn-off during logic ground disconnection with external components

- Overtemperature protection with latch

- Overvoltage protection with external components

- Enhanced short circuit operation

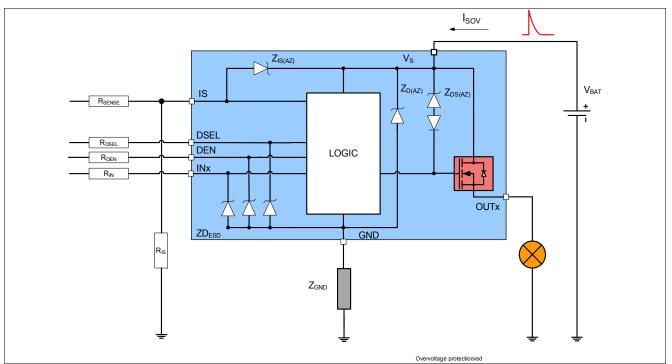

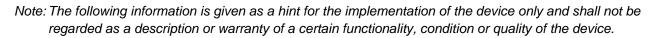

**Block Diagram**

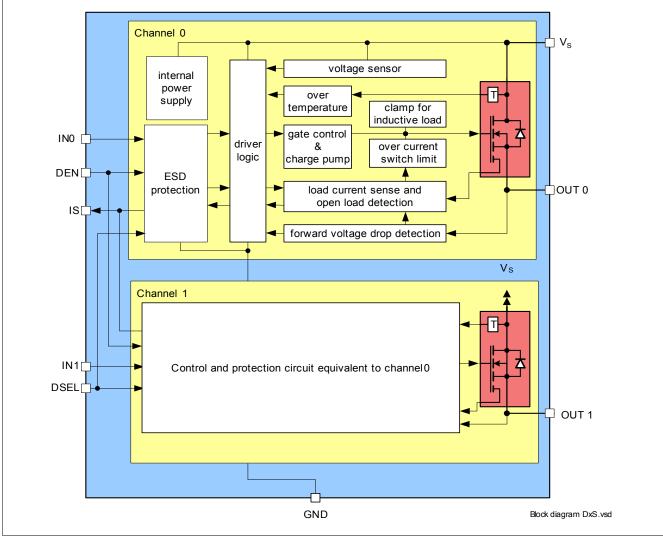

# 2 Block Diagram

Figure 1 Block Diagram for the BTT6100-2EKA

**Pin Configuration**

# 3 Pin Configuration

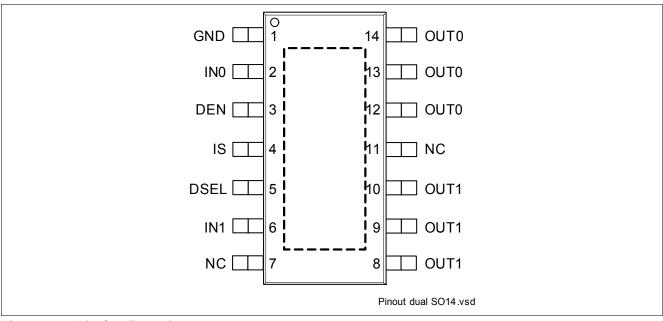

# 3.1 Pin Assignment

#### Figure 2 Pin Configuration

#### 3.2 Pin Definitions and Functions

| Symbol | Function                                                                        |

|--------|---------------------------------------------------------------------------------|

| GND    | GrouND; Ground connection                                                       |

| IN0    | INput channel 0; Input signal for channel 0 activation                          |

| DEN    | Diagnostic ENable; Digital signal to enable/disable the diagnosis of the device |

| IS     | Sense; Sense current of the selected channel                                    |

| DSEL   | Diagnostic SELection; Digital signal to select the channel to be diagnosed      |

| IN1    | INput channel 1; Input signal for channel 1 activation                          |

| NC     | Not Connected; No internal connection to the chip                               |

| OUT1   | <b>OUTput 1;</b> Protected high side power output channel 1 <sup>1)</sup>       |

| OUT0   | <b>OUTput 0</b> ; Protected high side power output channel 0 <sup>1)</sup>      |

| Vs     | Voltage Supply; Battery voltage                                                 |

|        | GND<br>IN0<br>DEN<br>IS<br>DSEL<br>IN1<br>NC<br>OUT1                            |

1) All output pins of a given channel must be connected together on the PCB. All pins of an output are internally connected together. PCB traces have to be designed to withstand the maximum current which can flow.

**Pin Configuration**

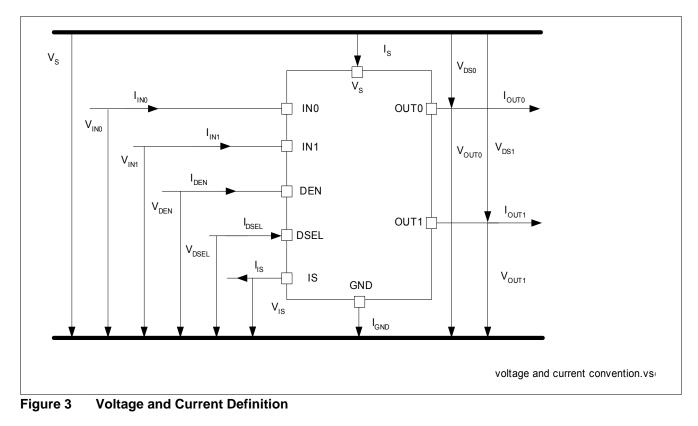

# 3.3 Voltage and Current Definition

Figure 3 shows all terms used in this data sheet, with associated convention for positive values.

# 4 General Product Characteristics

# 4.1 Absolute Maximum Ratings

# Table 2 Absolute Maximum Ratings <sup>1)</sup>

$T_{\rm J}$  = -40°C to 150°C; (unless otherwise specified)

| Parameter                                   | Symbol               | Values    |          |                  | Unit        | Note /                                                                                                                                                                                                                                                                                                         | Number   |

|---------------------------------------------|----------------------|-----------|----------|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                             |                      | Min.      | Тур.     | Max.             |             | Test Condition                                                                                                                                                                                                                                                                                                 |          |

| Supply Voltages                             |                      |           | <u>.</u> |                  |             |                                                                                                                                                                                                                                                                                                                |          |

| Supply voltage                              | Vs                   | -0.3      | -        | 48               | V           | -                                                                                                                                                                                                                                                                                                              | P_4.1.1  |

| Reverse polarity voltage                    | -V <sub>S(REV)</sub> | 0         | -        | 28               | V           | t < 2  min<br>$T_{A} = 25 \text{ °C}$<br>$R_{L} \ge 25 \Omega$<br>$Z_{GND}$ = Diode +27 $\Omega$                                                                                                                                                                                                               | P_4.1.2  |

| Supply voltage for short circuit protection | V <sub>BAT(SC)</sub> | 0         | -        | 36               | V           | $\begin{split} R_{\text{Supply}} &= 10 \text{ m}\Omega\\ L_{\text{Supply}} &= 5 \mu\text{H}\\ R_{\text{ECU}} &= 20 m\Omega\\ R_{\text{Cable}} &= 16 m\Omega/\text{m}\\ L_{\text{Cable}} &= 1 \mu\text{H/m},\\ l &= 0  \text{ or } 5 \text{m}\\ \text{See Chapter 6 and}\\ \hline \text{Figure 28} \end{split}$ | P_4.1.3  |

| Supply voltage for Load dump protection     | $V_{\rm S(LD)}$      | -         | -        | 65               | V           | $^{2)}R_{1} = 2 \Omega$<br>$R_{L} = 25 \Omega$                                                                                                                                                                                                                                                                 | P_4.1.12 |

| Short Circuit Capability                    |                      |           |          |                  |             |                                                                                                                                                                                                                                                                                                                |          |

| Permanent short circuit<br>IN pin toggles   | n <sub>RSC1</sub>    | -         | -        | 100              | k<br>cycles | 3)                                                                                                                                                                                                                                                                                                             | P_4.1.4  |

| Input Pins                                  |                      |           |          |                  |             |                                                                                                                                                                                                                                                                                                                |          |

| Voltage at INPUT pins                       | $V_{IN}$             | -0.3<br>— | -        | 6<br>7           | V           | –<br><i>t</i> < 2 min                                                                                                                                                                                                                                                                                          | P_4.1.13 |

| Current through INPUT pins                  | I <sub>IN</sub>      | -2        | -        | 2                | mA          | -                                                                                                                                                                                                                                                                                                              | P_4.1.14 |

| Voltage at DEN pin                          | $V_{DEN}$            | -0.3<br>— | -        | 6<br>7           | V           | -<br><i>t</i> < 2 min                                                                                                                                                                                                                                                                                          | P_4.1.15 |

| Current through DEN pin                     | $I_{DEN}$            | -2        | _        | 2                | mA          | -                                                                                                                                                                                                                                                                                                              | P_4.1.16 |

| Voltage at DSEL pin                         | $V_{DSEL}$           | -0.3<br>— | -        | 6<br>7           | V           | –<br><i>t</i> < 2 min                                                                                                                                                                                                                                                                                          | P_4.1.17 |

| Current through DSEL pin                    | IDSEL                | -2        | _        | 2                | mA          | -                                                                                                                                                                                                                                                                                                              | P_4.1.18 |

| Sense Pin                                   |                      |           |          |                  |             |                                                                                                                                                                                                                                                                                                                |          |

| Voltage at IS pin                           | $V_{IS}$             | -0.3      | -        | $V_{S}$          | V           | -                                                                                                                                                                                                                                                                                                              | P_4.1.19 |

| Current through IS pin                      | I <sub>IS</sub>      | -25       | _        | 50               | mA          | -                                                                                                                                                                                                                                                                                                              | P_4.1.20 |

| Power Stage                                 | 1                    | 1         | 1        | 1                | 1           | 1                                                                                                                                                                                                                                                                                                              | 1        |

| Load current                                | <i>I</i> _           | -         | _        | $I_{\rm L(LIM)}$ | А           | -                                                                                                                                                                                                                                                                                                              | P_4.1.21 |

#### Table 2 Absolute Maximum Ratings (cont'd)<sup>1)</sup>

$T_{\rm J}$  = -40°C to 150°C; (unless otherwise specified)

| Parameter                                                    | Symbol           | Values      |      |          | Unit | Note /                                                                              | Number   |

|--------------------------------------------------------------|------------------|-------------|------|----------|------|-------------------------------------------------------------------------------------|----------|

|                                                              |                  | Min.        | Тур. | Max.     |      | Test Condition                                                                      |          |

| Power dissipation (DC)                                       | P <sub>TOT</sub> | -           | -    | 1.8      | W    | <i>T</i> <sub>A</sub> = 85 °C<br><i>T</i> <sub>J</sub> < 150 °C                     | P_4.1.22 |

| Maximum energy dissipation<br>Single pulse (one channel)     | E <sub>AS</sub>  | -           | -    | 36       | mJ   | $I_{L(0)} = 1.5 \text{ A}$<br>$T_{J(0)} = 150 \text{ °C}$<br>$V_{S} = 28 \text{ V}$ | P_4.1.23 |

| Voltage at power transistor                                  | $V_{\rm DS}$     | -           | -    | 65       | V    | -                                                                                   | P_4.1.26 |

| Currents                                                     |                  |             |      | <b>I</b> | P    | 1                                                                                   |          |

| Current through ground pin                                   | I <sub>GND</sub> | -20<br>-150 | -    | 20<br>20 | mA   | -<br><i>t</i> < 2 min                                                               | P_4.1.27 |

| Temperatures                                                 | 4                |             |      |          | P    |                                                                                     | H        |

| Junction temperature                                         | TJ               | -40         | -    | 150      | °C   | -                                                                                   | P_4.1.28 |

| Storage temperature                                          | T <sub>STG</sub> | -55         | _    | 150      | °C   | -                                                                                   | P_4.1.30 |

| ESD Susceptibility                                           |                  | #           |      | -        |      | -                                                                                   | !        |

| ESD susceptibility (all pins)                                | $V_{ESD}$        | -2          | -    | 2        | kV   | <sup>4)</sup> HBM                                                                   | P_4.1.31 |

| ESD susceptibility OUT Pin vs. GND and $V_{\rm S}$ connected | $V_{ESD}$        | -4          | -    | 4        | kV   | <sup>4)</sup> HBM                                                                   | P_4.1.32 |

| ESD susceptibility                                           | $V_{ESD}$        | -500        | -    | 500      | V    | <sup>5)</sup> CDM                                                                   | P_4.1.33 |

| ESD susceptibility pin (corner pins)                         | $V_{ESD}$        | -750        | -    | 750      | V    | <sup>5)</sup> CDM                                                                   | P_4.1.34 |

1) Not subject to production test. Specified by design.

2)  $V_{\rm S(LD)}$  is setup without the DUT connected to the generator per ISO 7637-1.

3) Threshold limit for short circuit failures: 100 ppm. Please refer to the legal disclaimer for short-circuit capability at the end of this document.

4) ESD susceptibility HBM according to ANSI/ESDA/JEDEC JS-001.

5) "CDM" ESDA STM5.3.1 or ANSI/ESD 5.5.3.1

#### Notes

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

# 4.2 Functional Range

| Parameter                                             | Symbol               | Values |      |      | Unit | Note /                                                                                                                                                                          | Number   |

|-------------------------------------------------------|----------------------|--------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                       |                      | Min.   | Тур. | Max. |      | Test Condition                                                                                                                                                                  |          |

| Nominal operating voltage                             | $V_{\rm NOM}$        | 8      | 28   | 36   | V    | -                                                                                                                                                                               | P_4.2.1  |

| Extended operating voltage                            | V <sub>S(OP)</sub>   | 5      | -    | 48   | V    | <sup>2)</sup> $V_{\rm IN}$ = 4.5 V<br>$R_{\rm L}$ = 25 $\Omega$<br>$V_{\rm DS}$ < 0.5 V                                                                                         | P_4.2.2  |

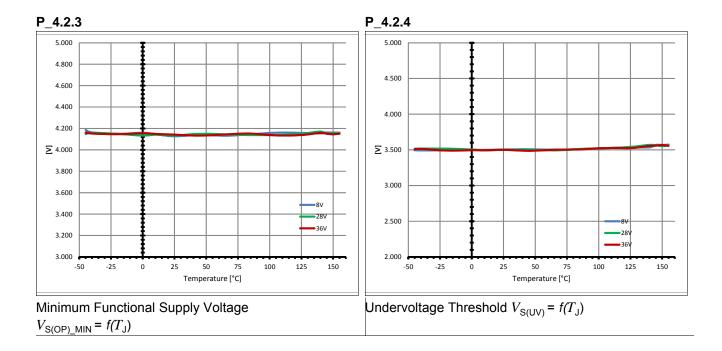

| Minimum functional supply<br>voltage                  | $V_{\rm S(OP)\_MIN}$ | 3.8    | 4.3  | 5    | V    | <sup>1)</sup> $V_{\rm IN}$ = 4.5 V<br>$R_{\rm L}$ = 25 Ω<br>From $I_{\rm OUT}$ = 0 A<br>to<br>$V_{\rm DS}$ < 0.5 V;<br>see Figure 15                                            | P_4.2.3  |

| Undervoltage shutdown                                 | V <sub>S(UV)</sub>   | 3      | 3.5  | 4.1  | V    | <sup>1)</sup> $V_{\rm IN} = 4.5 V$<br>$V_{\rm DEN} = 0 V$<br>$R_{\rm L} = 25 \Omega$<br>From $V_{\rm DS} < 1 V$ ;<br>to $I_{\rm OUT} = 0 A$<br>See Chapter 9.1<br>and Figure 15 | P_4.2.4  |

| Undervoltage shutdown<br>hysteresis                   | $V_{\rm S(UV)\_HYS}$ | -      | 850  | -    | mV   | 2)                                                                                                                                                                              | P_4.2.13 |

| Operating current<br>One channel active               | I <sub>GND_1</sub>   | -      | 2    | 4    | mA   | $V_{\rm IN} = 5.5 V$ $V_{\rm DEN} = 5.5 V$ Device in $R_{\rm DS(ON)}$ $V_{\rm S} = 36 V$ See Chapter 9.1                                                                        | P_4.2.5  |

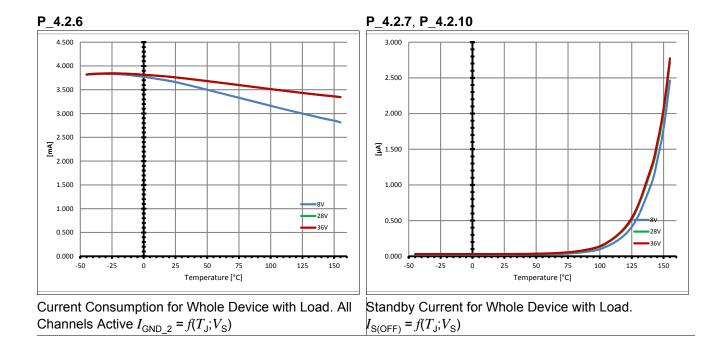

| Operating current<br>All channels active              | I <sub>GND_4</sub>   | -      | 4    | 6    | mA   | $V_{\rm IN} = 5.5 V$ $V_{\rm DEN} = 5.5 V$ Device in $R_{\rm DS(ON)}$ $V_{\rm S} = 36 V$ See Chapter 9.1                                                                        | P_4.2.6  |

| Standby current for whole device with load (ambiente) | I <sub>S(OFF)</sub>  | -      | 0.1  | 0.5  | μA   | <sup>1)</sup> $V_{\rm S}$ = 36 V<br>$V_{\rm OUT}$ = 0 V<br>$V_{\rm IN}$ floating<br>$V_{\rm DEN}$ floating<br>$T_{\rm J} \le$ 85 °C                                             | P_4.2.7  |

# Table 3Functional Range $T_J = -40^{\circ}$ C to $150^{\circ}$ C; (unless otherwise specified)

#### Table 3Functional Range $(cont'd)T_J = -40^{\circ}C$ to $150^{\circ}C$ ; (unless otherwise specified)

| Parameter                                                     | Symbol                  |      | Value | S    | Unit | Note /<br>Test Condition                                                                                                   | Number   |

|---------------------------------------------------------------|-------------------------|------|-------|------|------|----------------------------------------------------------------------------------------------------------------------------|----------|

|                                                               |                         | Min. | Тур.  | Max. |      |                                                                                                                            |          |

| Maximum standby current for whole device with load            | I <sub>S(OFF)_150</sub> | -    | _     | 10   | μΑ   | $V_{\rm S}$ = 36 V<br>$V_{\rm OUT}$ = 0 V<br>$V_{\rm IN}$ floating<br>$V_{\rm DEN}$ floating<br>$T_{\rm J}$ = 150 °C       | P_4.2.10 |

| Standby current for whole device with load, diagnostic active | I <sub>S(OFF_DEN)</sub> | -    | 0.6   | -    | mA   | ${}^{2)} V_{\rm S} = 36 \text{ V}$ $V_{\rm OUT} = 0 \text{ V}$ $V_{\rm IN} \text{ floating}$ $V_{\rm DEN} = 5.5 \text{ V}$ | P_4.2.8  |

1) Test at  $T_{\rm J}$  = -40°C only

2) Not subject to production test. Specified by design.

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 4.3 Thermal Resistance

#### Table 4Thermal Resistance

| Parameter                                  | Symbol            |      | Values |      |     | Note /                | Number  |

|--------------------------------------------|-------------------|------|--------|------|-----|-----------------------|---------|

|                                            |                   | Min. | Тур.   | Max. |     | <b>Test Condition</b> |         |

| Junction to soldering point                | R <sub>thJS</sub> | -    | 5      | -    | K/W | 1)                    | P_4.3.1 |

| Junction to ambient<br>All channels active | R <sub>thJA</sub> | -    | 32     | -    | K/W | 1)2)                  | P_4.3.2 |

1) Not subject to production test. Specified by design.

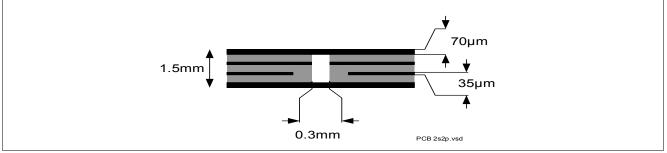

2) Specified R<sub>thja</sub> value is according to JEDEC JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The product (chip + package) was simulated on a 76.4 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70µm Cu, 2 x 35 µm Cu). Where applicable, a thermal via array under the exposed pad contacts the first inner copper layer. Please refer to Figure 4.

#### 4.3.1 PCB set up

Figure 4 2s2p PCB Cross Section

#### **General Product Characteristics**

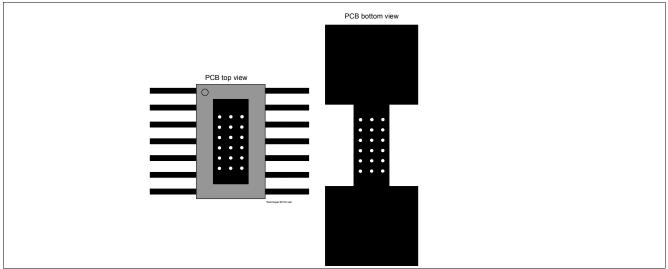

Figure 5 PC Board Top and Bottom View for Thermal Simulation with 600 mm<sup>2</sup> Cooling Area

# 4.3.2 Thermal Impedance

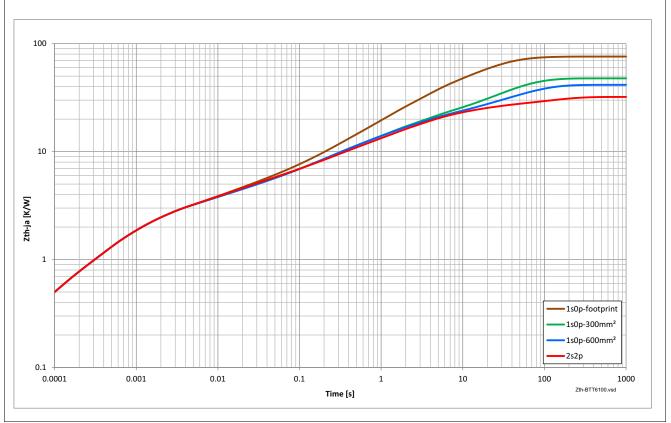

Figure 6 Typical Thermal Impedance. 2s2p PCB set up according Figure 5

#### **General Product Characteristics**

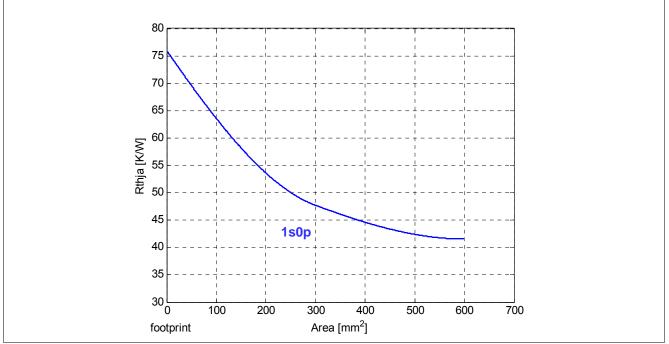

Figure 7 Typical Thermal Resistance. PCB set-up 1s0p

The power stages are built using an N-channel vertical power MOSFET (DMOS) with charge pump.

# 5.1 Output ON-state Resistance

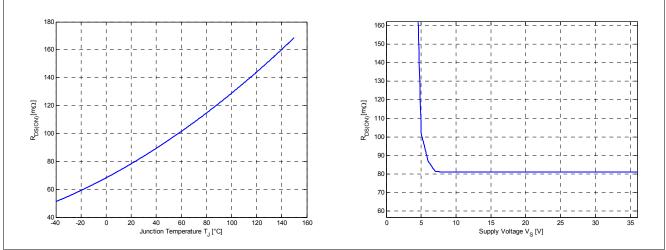

The ON-state resistance  $R_{\text{DS(ON)}}$  depends on the supply voltage as well as the junction temperature  $T_{\text{J}}$ . Figure 8 shows the dependencies in terms of temperature and supply voltage for the typical ON-state resistance. The behavior in reverse polarity is described in Chapter 6.4.

Figure 8 Typical ON-state Resistance

A high signal at the input pin (see **Chapter 8**) causes the power DMOS to switch ON with a dedicated slope, which is optimized in terms of EMC emission.

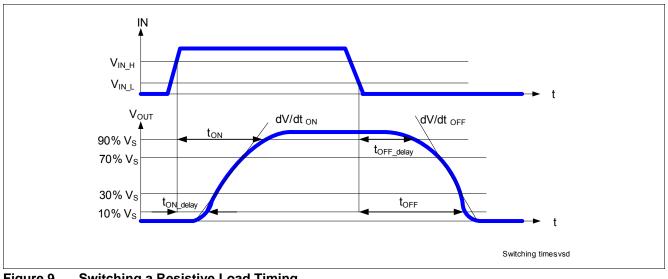

# 5.2 Turn ON/OFF Characteristics with Resistive Load

Figure 9 shows the typical timing when switching a resistive load.

Figure 9 Switching a Resistive Load Timing

#### 5.3 Inductive Load

# 5.3.1 Output Clamping

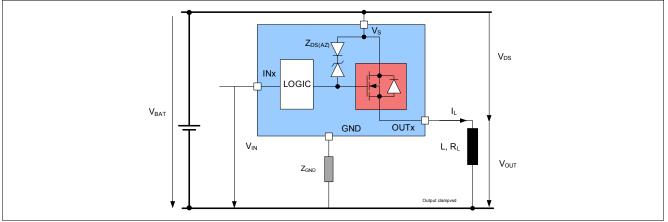

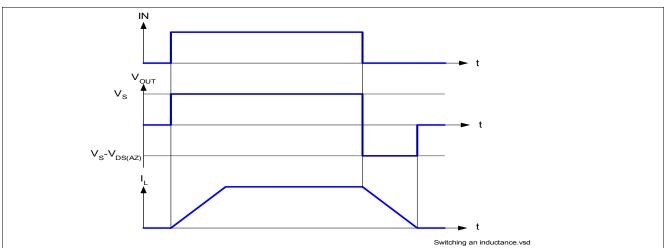

When switching OFF inductive loads with high side switches, the voltage  $V_{\text{OUT}}$  drops below ground potential, because the inductance intends to continue driving the current. To prevent the destruction of the device by avalanche due to high voltages, there is a voltage clamp mechanism  $Z_{\text{DS(AZ)}}$  implemented that limits negative output voltage to a certain level ( $V_{\text{S}}$  -  $V_{\text{DS(AZ)}}$ ). Please refer to Figure 10 and Figure 11 for details. Nevertheless, the maximum allowed load inductance is limited.

Figure 10 Output Clamp

Figure 11 Switching an Inductive Load Timing

# 5.3.2 Maximum Load Inductance

During demagnetization of inductive loads, energy has to be dissipated in the BTT6100-2EKA. This energy can be calculated with following equation:

$$E = V_{\text{DS}(\text{AZ})} \times \frac{L}{R_{\text{L}}} \times \left[\frac{V_{\text{S}} - V_{\text{DS}(\text{AZ})}}{R_{\text{L}}} \times \ln\left(1 - \frac{R_{\text{L}} \times I_{\text{L}}}{V_{\text{S}} - V_{\text{DS}(\text{AZ})}}\right) + I_{\text{L}}\right]$$

(1)

Data Sheet PROFET™+ 24V

Following equation simplifies under the assumption of  $R_{L} = 0 \Omega$ .

$$E = \frac{1}{2} \times L \times I^2 \times \left(1 - \frac{V_{\rm S}}{V_{\rm S} - V_{\rm DS(AZ)}}\right)$$

(2)

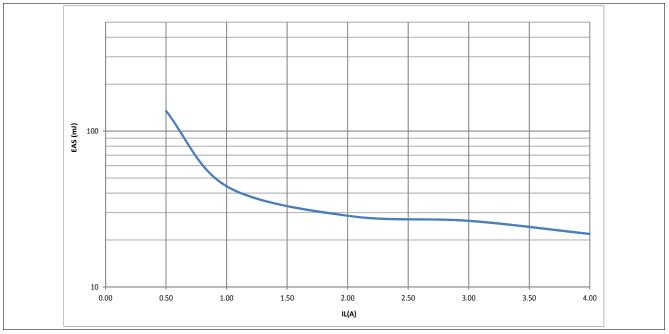

The energy, which is converted into heat, is limited by the thermal design of the component. See **Figure 12** for the maximum allowed energy dissipation as a function of the load current.

Figure 12 Maximum Energy Dissipation Single Pulse,  $T_{J\_START}$  = 150 °C;  $V_S$  = 28V

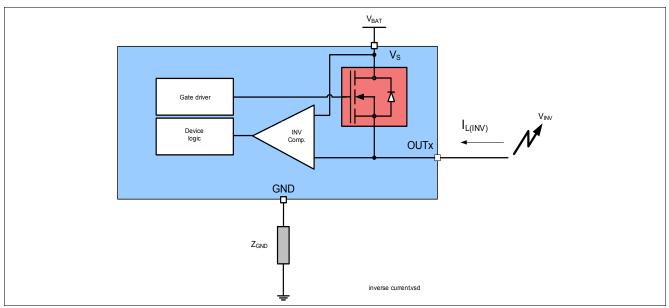

# 5.4 Inverse Current Capability

In case of inverse current, meaning a voltage  $V_{\rm INV}$  at the OUTput higher than the supply voltage  $V_{\rm S}$ , a current  $I_{\rm INV}$  will flow from output to  $V_{\rm S}$  pin via the body diode of the power transistor (please refer to Figure 13). The output stage follows the state of the IN pin, except if the IN pin goes from OFF to ON during inverse. In that particular case, the output stage is kept OFF until the inverse current disappears. Nevertheless, the current  $I_{\rm INV}$  should not be higher than  $I_{\rm L(INV)}$ . If the channel is OFF, the diagnostic will detect an open load at OFF. If the affected channel is ON, the diagnostic will detect open load at ON (the overtemperature signal is inhibited). At the appearance of  $V_{\rm INV}$ , a parasitic diagnostic can be observed. After, the diagnosis is valid and reflects the output state. At  $V_{\rm INV}$  vanishing, the diagnosis is valid and reflects the output state. At vanishing, the diagnosis is valid and reflects the output state are available.

#### **Power Stage**

Figure 13 Inverse Current Circuitry

# 5.5 Electrical Characteristics Power Stage

#### Table 5 Electrical Characteristics: Power Stage

$V_{\rm S}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to 150°C (unless otherwise specified).

Typical values are given at  $V_{\rm S}$  = 28 V,  $T_{\rm J}$  = 25 °C

| Parameter                                                                                    | Symbol                  | Values |      |      | Unit | Note /                                                                                                 | Number   |

|----------------------------------------------------------------------------------------------|-------------------------|--------|------|------|------|--------------------------------------------------------------------------------------------------------|----------|

|                                                                                              |                         | Min.   | Тур. | Max. |      | Test Condition                                                                                         |          |

| ON-state resistance per<br>channel                                                           | R <sub>DS(ON)_150</sub> | 150    | 180  | 200  | mΩ   | $I_{L} = I_{L4} = 2 \text{ A}$<br>$V_{IN} = 4.5 \text{ V}$<br>$T_{J} = 150 \text{ °C}$<br>See Figure 8 | P_5.5.1  |

| ON-state resistance per<br>channel                                                           | R <sub>DS(ON)_25</sub>  | -      | 100  | -    | mΩ   | <sup>1)</sup> <i>T</i> <sub>J</sub> = 25 °C                                                            | P_5.5.21 |

| Nominal load current<br>One channel active                                                   | $I_{\rm L(NOM)1}$       | -      | 2.6  | -    | A    | <sup>1)</sup> $T_{\rm A}$ = 85 °C<br>$T_{\rm J}$ < 150 °C                                              | P_5.5.2  |

| Nominal load current<br>All channels active                                                  | I <sub>L(NOM)2</sub>    | -      | 2.2  | -    | A    |                                                                                                        | P_5.5.3  |

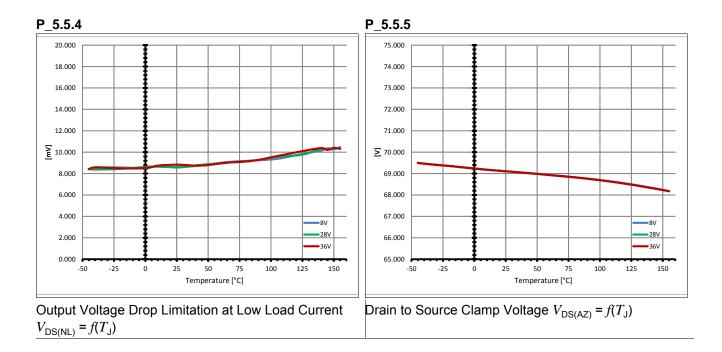

| Output voltage drop limitation at small load currents                                        | $V_{\rm DS(NL)}$        | -      | 10   | 22   | mV   | $I_{\rm L} = I_{\rm L0} = 50 \text{ mA}$<br>See <b>Chapter 9.3</b>                                     | P_5.5.4  |

| Drain to source clamping<br>voltage<br>$V_{\text{DS(AZ)}} = [V_{\text{S}} - V_{\text{OUT}}]$ | V <sub>DS(AZ)</sub>     | 65     | 70   | 75   | V    | $I_{\rm DS}$ = 20 mA<br>See Figure 11<br>See Chapter 9.1                                               | P_5.5.5  |

| Output leakage current per channel $T_{\rm J} \le 85 \ ^{\circ}{\rm C}$                      | I <sub>L(OFF)</sub>     | -      | 0.1  | 0.5  | μA   | $^{2)} V_{\rm IN}$ floating $V_{\rm OUT}$ = 0 V $T_{\rm J} \le 85^{\circ}{\rm C}$                      | P_5.5.6  |

| Dutput leakage current per channel $T_{\rm J}$ = 150 °C                                      | I <sub>L(OFF)_150</sub> | -      | 1    | 5    | μA   | $V_{\rm IN}$ floating<br>$V_{\rm OUT}$ = 0 V<br>$T_{\rm J}$ = 150 °C                                   | P_5.5.8  |

| nverse current capability                                                                    | I <sub>L(INV)</sub>     | -      | 2.2  | -    | A    | <sup>1)</sup> $V_{\rm S} < V_{\rm OUTX}$<br>See Figure 13                                              | P_5.5.9  |

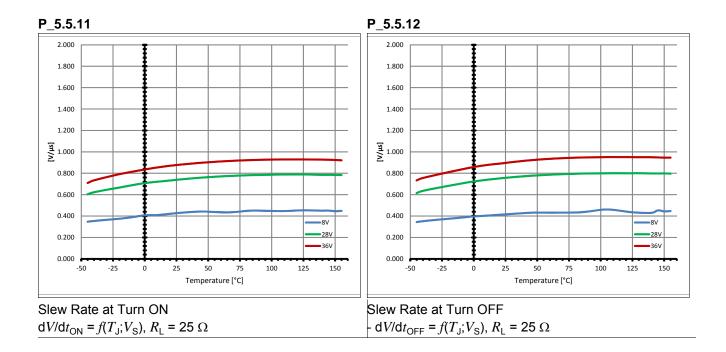

| Slew rate 30% to 70% $V_{\rm S}$                                                             | dV/dt <sub>ON</sub>     | 0.3    | 0.8  | 1.3  | V/µs | $R_{\rm L}$ = 25 $\Omega$<br>$V_{\rm S}$ = 28 V                                                        | P_5.5.11 |

| Slew rate 70% to 30% $V_{\rm S}$                                                             | -dV/dt <sub>OFF</sub>   | 0.3    | 0.8  | 1.3  | V/µs | See Figure 9<br>See Chapter 9.1                                                                        | P_5.5.12 |

| Slew rate matching<br>dV/dt <sub>ON</sub> - dV/dt <sub>OFF</sub>                             | ∆dV/dt                  | -0.15  | 0    | 0.15 | V/µs | _                                                                                                      | P_5.5.13 |

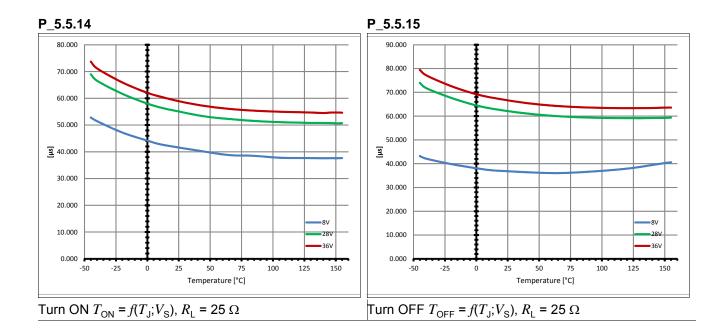

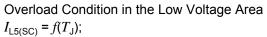

| Furn-ON time to $V_{OUT}$ = 90% $V_{S}$                                                      | t <sub>ON</sub>         | 20     | 70   | 150  | μs   |                                                                                                        | P_5.5.14 |

| Furn-OFF time to $V_{OUT}$ = 10% $V_{S}$                                                     | t <sub>OFF</sub>        | 20     | 70   | 150  | μs   |                                                                                                        | P_5.5.15 |

| Furn-ON / OFF matching                                                                       | $\Delta t_{\rm SW}$     | -50    | 0    | 50   | μs   |                                                                                                        | P_5.5.16 |

| Furn-ON time to $V_{OUT}$ = 10% $V_{S}$                                                      | t <sub>ON_delay</sub>   | -      | 35   | 70   | μs   |                                                                                                        | P_5.5.17 |

| Furn-OFF time to $V_{OUT}$ = 90% $V_{S}$                                                     | t <sub>OFF_delay</sub>  | -      | 35   | 70   | μs   |                                                                                                        | P_5.5.18 |

#### Table 5 Electrical Characteristics: Power Stage (cont'd)

$V_{\rm S}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to 150°C (unless otherwise specified). Typical values are given at  $V_{\rm S}$  = 28 V,  $T_{\rm J}$  = 25 °C

| Parameter         | Symbol           |      | Values |      | Unit | Note /                                                                                                       | Number   |

|-------------------|------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------------------|----------|

|                   |                  | Min. | Тур.   | Max. |      | Test Condition                                                                                               |          |

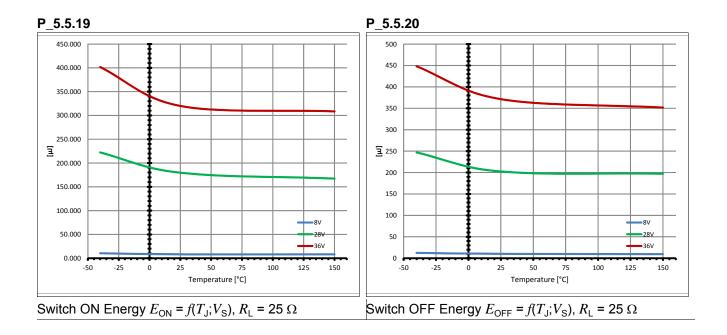

| Switch ON energy  | E <sub>ON</sub>  | _    | 320    | -    | μJ   | <sup>1)</sup> $R_{\rm L}$ = 25 Ω<br>$V_{\rm OUT}$ = 90% $V_{\rm S}$<br>$V_{\rm S}$ = 36 V<br>See Chapter 9.1 | P_5.5.19 |

| Switch OFF energy | E <sub>OFF</sub> | -    | 371    | -    | μJ   | <sup>1)</sup> $R_{\rm L}$ = 25 Ω<br>$V_{\rm OUT}$ = 10% $V_{\rm S}$<br>$V_{\rm S}$ = 36 V<br>See Chapter 9.1 | P_5.5.20 |

1) Not subject to production test, specified by design.

2) Test at  $T_{\rm J}$  = -40°C only

# 6 Protection Functions

The device provides integrated protection functions. These functions are designed to prevent the destruction of the IC from fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are designed for neither continuous nor repetitive operation.

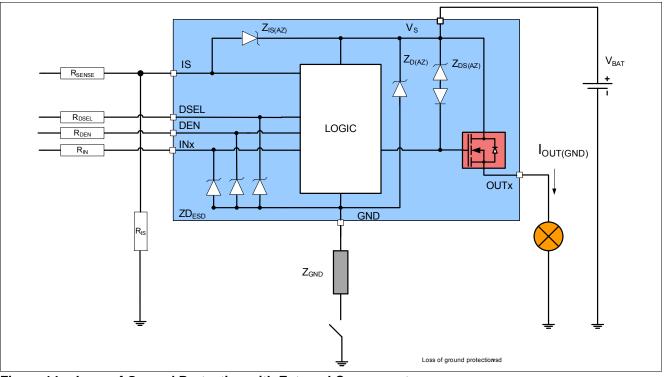

#### 6.1 Loss of Ground Protection

In case of loss of the module ground and the load remains connected to ground, the device protects itself by automatically turning OFF (when it was previously ON) or remains OFF, regardless of the voltage applied on IN pins.

In case of loss of device ground, it's recommended to use input resistors between the microcontroller and the BTT6100-2EKA to ensure switching OFF of channels.

In case of loss of module or device ground, a current ( $I_{OUT(GND)}$ ) can flow out of the DMOS. Figure 14 sketches the situation.

$Z_{\rm GND}$  is recommended to be a resistor in series to a diode .

Figure 14 Loss of Ground Protection with External Components

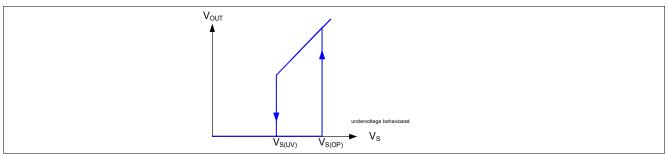

#### 6.2 Undervoltage Protection

Between  $V_{S(UV)}$  and  $V_{S(OP)}$ , the undervoltage mechanism is triggered.  $V_{S(OP)}$  represents the minimum voltage where the switching ON and OFF can takes place.  $V_{S(UV)}$  represents the minimum voltage the switch can hold ON. If the supply voltage is below the undervoltage mechanism  $V_{S(UV)}$ , the device is OFF (turns OFF). As soon as the supply voltage is above the undervoltage mechanism  $V_{S(OP)}$ , then the device can be switched ON. When the switch is ON, protection functions are operational. Nevertheless, the diagnosis is not guaranteed until  $V_S$  is in the  $V_{NOM}$  range. Figure 15 sketches the undervoltage mechanism.

#### **Protection Functions**

Figure 15 Undervoltage Behavior

#### 6.3 Overvoltage Protection

There is an integrated clamp mechanism for overvoltage protection  $(Z_{D(AZ)})$ . To guarantee this mechanism operates properly in the application, the current in the Zener diode has to be limited by a ground resistor. Figure 16 shows a typical application to withstand overvoltage issues. In case of supply voltage higher than  $V_{S(AZ)}$ , the power transistor switches ON and in addition the voltage across the logic section is clamped. As a result, the internal ground potential rises to  $V_{\rm S}$  -  $V_{S(AZ)}$ . Due to the ESD Zener diodes, the potential at pin INx, DSEL, and DEN rises almost to that potential, depending on the impedance of the connected circuitry. In the case the device was ON, prior to overvoltage, the BTT6100-2EKA remains ON. In the case the BTT6100-2EKA was OFF, prior to overvoltage, the power transistor can be activated. In the case the supply voltage is in above  $V_{\rm BAT(SC)}$  and below  $V_{\rm DS(AZ)}$ , the output transistor is still operational and follows the input. If at least one channel is in the ON state, parameters are no longer guaranteed and lifetime is reduced compared to the nominal supply voltage range. This especially impacts the short circuit robustness, as well as the maximum energy  $E_{\rm AS}$  capability.  $Z_{\rm GND}$  is recommended to be a resistor in series to a diode.

Figure 16 Overvoltage Protection with External Components

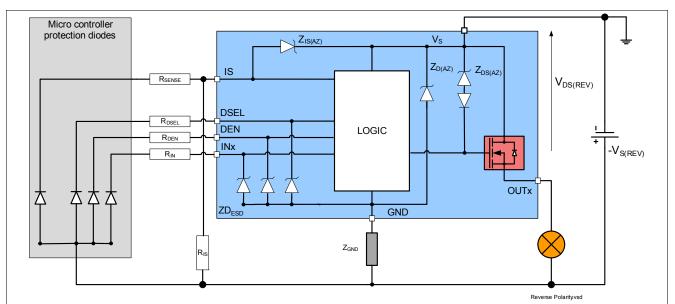

#### 6.4 Reverse Polarity Protection

In case of reverse polarity, the intrinsic body diodes of the power DMOS causes power dissipation. The current in this intrinsic body diode is limited by the load itself. Additionally, the current into the ground path and the logic pins

Data Sheet PROFET™+ 24V

#### **Protection Functions**

has to be limited to the maximum current described in **Chapter 4.1** with an external resistor. **Figure 17** shows a typical application.  $R_{\text{GND}}$  resistor is used to limit the current in the Zener protection of the device. Resistors  $R_{\text{DSEL}}$ ,  $R_{\text{DEN}}$ , and  $R_{\text{IN}}$  are used to limit the current in the logic of the device and in the ESD protection stage.  $R_{\text{SENSE}}$  is used to limit the current in the logic of the device and in the ESD protection stage.  $R_{\text{DEN}} = R_{\text{DSEL}} = R_{\text{IN}} = R_{\text{SENSE}} = 10 \text{ k}\Omega$ .  $Z_{\text{GND}}$  is recommended to be a resistor in series to a diode.

During reverse polarity, no protection functions are available.

Figure 17 Reverse Polarity Protection with External Components

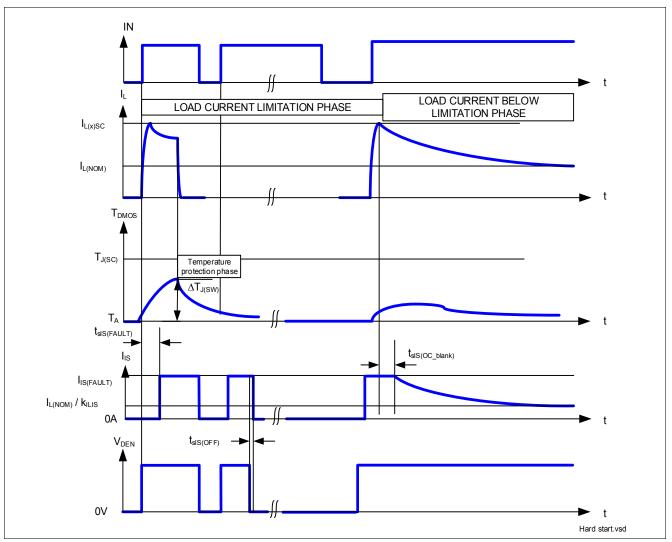

#### 6.5 Overload Protection

In case of overload, such as high inrush of cold lamp filament, or short circuit to ground, the BTT6100-2EKA offers several protection mechanisms.

#### 6.5.1 Current Limitation

At first step, the instantaneous power in the switch is maintained at a safe value by limiting the current to the maximum current allowed in the switch  $I_{L(SC)}$ . During this time, the DMOS temperature is increasing, which affects the current flowing in the DMOS.

# 6.5.2 Temperature Limitation in the Power DMOS

Each channel incorporates both an absolute  $(T_{J(SC)})$  and a dynamic  $(T_{J(SW)})$  temperature sensor. Activation of either sensor will cause an overheated channel to switch OFF to prevent destruction. Any protective switch OFF latches the output until the temperature has reached an acceptable value. **Figure 18** gives a sketch of the situation.

No retry strategy is implemented such that when the DMOS temperature has cooled down enough, the switch is switched ON again. Only the IN pin signal toggling can re-activate the power stage (latch behavior).

**Protection Functions**

#### Figure 18 Overload Protection

Note: For better understanding, the time scale is not linear. The real timing of this drawing is application dependent and cannot be described.

**Protection Functions**

#### 6.6 **Electrical Characteristics for the Protection Functions**

#### Table 6 **Electrical Characteristics: Protection**

$V_{\rm S}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to 150°C (unless otherwise specified). Typical values are given at  $V_{\rm S}$  = 28 V,  $T_{\rm J}$  = 25 °C

| Parameter                                          | Symbol                 | Values |                   |            | Unit | Note /                                                                            | Number   |

|----------------------------------------------------|------------------------|--------|-------------------|------------|------|-----------------------------------------------------------------------------------|----------|

|                                                    |                        | Min.   | Тур.              | Max.       |      | Test Condition                                                                    |          |

| Loss of Ground                                     |                        |        | - !               | - <b>P</b> |      | -                                                                                 |          |

| Output leakage current while GND disconnected      | I <sub>OUT(GND)</sub>  | -      | 0.1               | -          | mA   | <sup>1)2)</sup> $V_{\rm S}$ = 28 V<br>See Figure 14                               | P_6.6.1  |

| Reverse Polarity                                   |                        |        |                   | L.         |      |                                                                                   |          |

| Drain source diode voltage during reverse polarity | $V_{\rm DS(REV)}$      | 200    | 650               | 700        | mV   | <sup>3)</sup> $I_{L} = -2 \text{ A}$<br>$T_{J} = 150 \text{ °C}$<br>See Figure 17 | P_6.6.2  |

| Overvoltage                                        |                        |        | 1                 |            |      |                                                                                   |          |

| Overvoltage protection                             | $V_{\rm S(AZ)}$        | 65     | 70                | 75         | V    | I <sub>SOV</sub> = 5 mA<br>See Figure 16                                          | P_6.6.3  |

| Overload Condition                                 | 1                      | I      |                   | -          | 1    |                                                                                   |          |

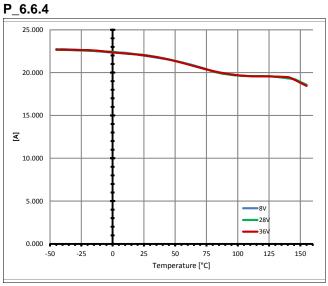

| Load current limitation                            | I <sub>L5(SC)</sub>    | 20     | 25                | 30         | A    | $^{(4)}V_{DS}$ = 5 V<br>See Figure 18 and<br>Chapter 9.3                          | P_6.6.4  |

| Dynamic temperature increase while switching       | $\Delta T_{\rm J(SW)}$ | -      | 80                | -          | К    | <sup>5)</sup> See Figure 18                                                       | P_6.6.8  |

| Thermal shutdown<br>temperature                    | $T_{\rm J(SC)}$        | 150    | 170 <sup>5)</sup> | 200 5)     | °C   | <sup>3)</sup> See Figure 18                                                       | P_6.6.10 |

| Thermal shutdown hysteresis                        | $\Delta T_{\rm J(SC)}$ | _      | 30                | _          | К    | 2)                                                                                | P_6.6.11 |

1) All pins are disconnected except  $V_{\rm S}$  and OUT.

2) Not Subject to production test, specified by design

3) Test at  $T_J$  = +150°C only

4) Test at  $T_{\rm J}$  = -40°C only

5) Functional test only

# 7 Diagnostic Functions

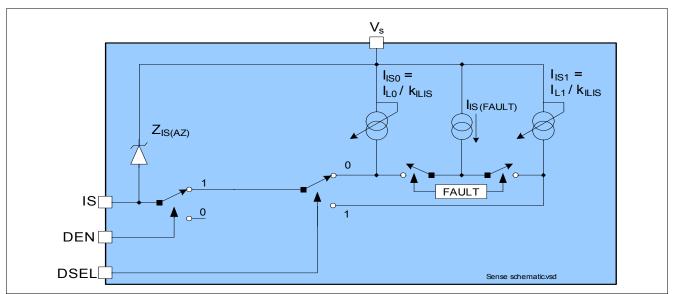

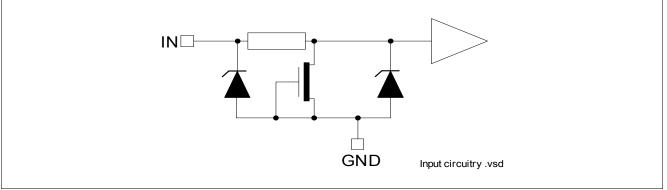

For diagnosis purpose, the BTT6100-2EKA provides a combination of digital and analog signals at pin IS. These signals are called SENSE. In case the diagnostic is disabled via DEN, pin IS becomes high impedance. In case DEN is activated, the sense current of the channel X is enabled/disabled via associated pin DSEL. **Table 7** gives the truth table.

| Table 7 | Diagnostic Truth Table |

|---------|------------------------|

|         | Blaghoodo madri rabio  |

| DEN | DSEL       | IS                                |

|-----|------------|-----------------------------------|

| 0   | don't care | Z                                 |

| 1   | 0          | Sense output 0 I <sub>IS(0)</sub> |

| 1   | 1          | Sense output 1 I <sub>IS(1)</sub> |

#### 7.1 IS Pin

The BTT6100-2EKA provides a sense signal called  $I_{IS}$  at pin IS. As long as no "hard" failure mode occurs (short circuit to GND / current limitation / overtemperature / excessive dynamic temperature increase or open load at OFF) a proportional signal to the load current (ratio  $k_{ILIS} = I_L / I_{IS}$ ) is provided. The complete IS pin and diagnostic mechanism is described on **Figure 19**. The accuracy of the sense current depends on temperature and load current. The sense pin multiplexes the currents  $I_{IS(0)}$  and  $I_{IS(1)}$  via the pin DSEL. Thanks to this multiplexing, the matching between  $k_{ILISCHANNEL0}$  and  $k_{ILISCHANNEL1}$  is optimized. Due to the ESD protection, in connection to  $V_S$ , it is not recommended to share the IS pin with other devices if these devices are using another battery feed. The consequence is that the unsupplied device would be fed via the IS pin of the supplied device.

Figure 19 Diagnostic Block Diagram

# 7.2 SENSE Signal in Different Operating Modes

Table 8 gives a quick reference for the state of the IS pin during device operation.

| Operation Mode                             | Input level Channel X | DEN <sup>1)</sup> | Output Level                           | <b>Diagnostic Output</b>                               |

|--------------------------------------------|-----------------------|-------------------|----------------------------------------|--------------------------------------------------------|

| Normal operation                           | OFF                   | Н                 | Z                                      | Z                                                      |

| Short circuit to GND                       |                       |                   | ~ GND                                  | Z                                                      |

| Overtemperature                            |                       |                   | Z                                      | Z                                                      |

| Short circuit to $V_{\rm S}$               |                       |                   | Vs                                     | I <sub>IS(FAULT)</sub>                                 |

| Open Load                                  |                       |                   | $< V_{OL(OFF)}$<br>> $V_{OL(OFF)}^{2}$ | Z                                                      |

|                                            |                       |                   | * VOL(OFF)                             | I <sub>IS(FAULT)</sub>                                 |

| Inverse current                            |                       |                   | $\sim V_{\rm INV}$                     | I <sub>IS(FAULT)</sub>                                 |

| Normal operation                           | ON                    |                   | ~ V <sub>S</sub>                       | $I_{\rm IS} = I_{\rm L} / k_{\rm ILIS}$                |

| Current limitation                         |                       |                   | < V <sub>S</sub>                       | I <sub>IS(FAULT)</sub>                                 |

| Short circuit to GND                       |                       |                   | ~ GND                                  | I <sub>IS(FAULT)</sub>                                 |

| Overtemperature <sub>TJ(SW)</sub><br>event |                       |                   | Z                                      | I <sub>IS(FAULT)</sub>                                 |

| Short circuit to V <sub>S</sub>            |                       |                   | Vs                                     | $I_{\rm IS} < I_{\rm L} / k_{\rm ILIS}$                |

| Open Load                                  |                       |                   | $\sim V_{\rm S}^{3)}$                  | $I_{\rm IS} < I_{\rm IS(OL)}$                          |

| Inverse current                            |                       |                   | $\sim V_{\rm INV}$                     | $I_{\rm IS} < I_{\rm IS(OL)}^{4)}$                     |

| Underload                                  |                       |                   | $\sim {V_{\rm S}}^{5)}$                | $I_{\rm IS(OL)} < I_{\rm IS} < I_{\rm L}/k_{\rm ILIS}$ |

| Don't care                                 | Don't care            | L                 | Don't care                             | Z                                                      |

#### Table 8 Sense Signal, Function of Operation Mode

1) The table doesn't indicate but it is assumed that the appropriate channel is selected via the DSEL pins.

2) Stable with additional pull-up resistor.

3) The output current has to be smaller than  $I_{L(OL)}$ .

4) After maximum  $t_{INV}$ .

5) The output current has to be higher than  $I_{L(OL)}$ .

# 7.3 SENSE Signal in the Nominal Current Range

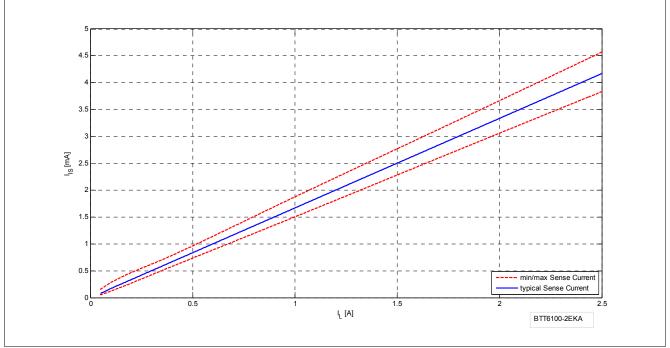

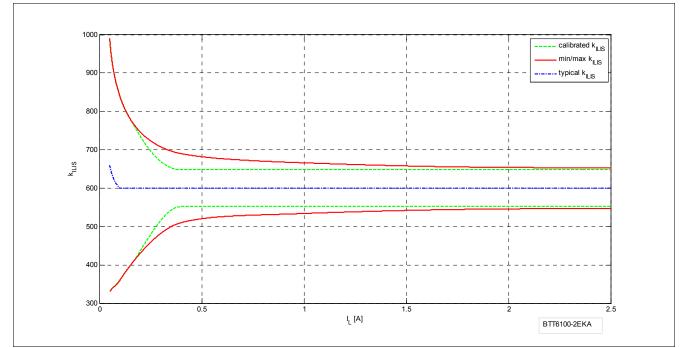

**Figure 20** and **Figure 21** show the current sense as a function of the load current in the power DMOS. Usually, a pull-down resistor  $R_{IS}$  is connected to the current sense IS pin. This resistor has to be higher than 560  $\Omega$  to limit the power losses in the sense circuitry. A typical value is 1.2 k $\Omega$ . The blue curve represents the ideal sense current, assuming an ideal  $k_{ILIS}$  factor value. The red curves shows the accuracy the device provides across full temperature range at a defined current.

#### **Diagnostic Functions**

Figure 20 Current Sense for Nominal Load

# 7.3.1 SENSE Signal Variation as a Function of Temperature and Load Current

In some applications a better accuracy is required at smaller currents. To achieve this accuracy requirement, a calibration on the application is possible. To avoid multiple calibration points at different load and temperature conditions, the BTT6100-2EKA allows limited derating of the  $k_{ILIS}$  value, at a given point ( $I_{L3}$ ;  $T_J$  = +25 °C). This derating is described by the parameter  $\Delta k_{ILIS}$ . Figure 21 shows the behavior of the sense current, assuming one calibration point at nominal load at +25 °C.

The blue line indicates the ideal  $k_{\rm ILIS}$  ratio.

The green lines indicate the derating on the parameter across temperature and voltage, assuming one calibration point at nominal temperature and nominal battery voltage.

The red lines indicate the  $k_{\rm ILIS}$  accuracy without calibration.

# infineon

# BTT6100-2EKA

#### **Diagnostic Functions**

Figure 21 Improved Current Sense Accuracy with One Calibration Point at 0.4A

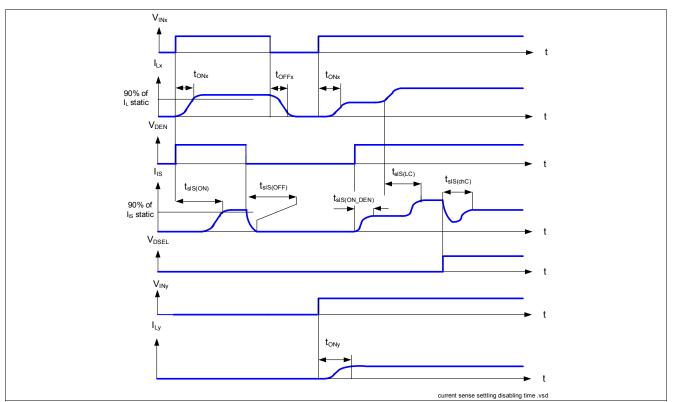

# 7.3.2 SENSE Signal Timing

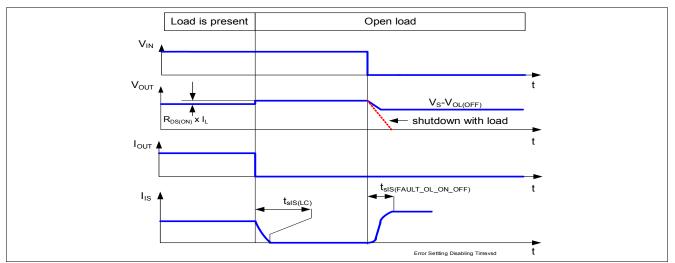

Figure 22 shows the timing during settling and disabling of the SENSE.

Figure 22 Current Sense Settling / Disabling Timing

# 7.3.3 SENSE Signal in Open Load

# 7.3.3.1 Open Load in ON Diagnostic

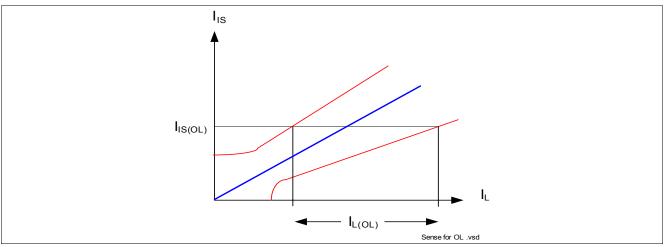

If the channel is ON, a leakage current can still flow through an open load, for example due to humidity. The parameter  $I_{L(OL)}$  gives the threshold of recognition for this leakage current. If the current  $I_L$  flowing out the power DMOS is below this value, the device recognizes a failure, if the DEN (and DSEL) is selected. In that case, the SENSE current is below  $I_{IS(OL)}$ . Otherwise, the minimum SENSE current is given above parameter  $I_{IS(OL)}$ . Figure 23 shows the SENSE current behavior in this area. The red curve shows a typical product curve. The blue curve shows the ideal current sense.

Figure 23 Current Sense Ratio for Low Currents

# 7.3.3.2 Open Load in OFF Diagnostic

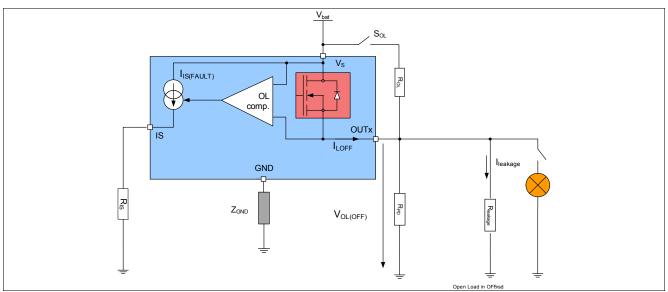

For open load diagnosis in OFF-state, an external output pull-up resistor ( $R_{OL}$ ) is recommended. For the calculation of pull-up resistor value, the leakage currents and the open load threshold voltage  $V_{OL(OFF)}$  have to be taken into account. Figure 24 gives a sketch of the situation.  $I_{leakage}$  defines the leakage current in the complete system, including  $I_{L(OFF)}$  (see Chapter 5.5) and external leakages, e.g, due to humidity, corrosion, etc... in the application.

To reduce the stand-by current of the system, an open load resistor switch  $S_{OL}$  is recommended. If the channel x is OFF, the output is no longer pulled down by the load and  $V_{OUT}$  voltage rises to nearly  $V_S$ . This is recognized by the device as an open load. The voltage threshold is given by  $V_{OL(OFF)}$ . In that case, the SENSE signal is switched to the  $I_{IS(FAULT)}$ .

An additional  $R_{PD}$  resistor can be used to pull  $V_{OUT}$  to 0V. Otherwise, the OUT pin is floating. This resistor can be used as well for short circuit to battery detection, see **Chapter 7.3.4**.

#### **Diagnostic Functions**

Figure 24 Open Load Detection in OFF Electrical Equivalent Circuit

# 7.3.3.3 Open Load Diagnostic Timing

**Figure 25** shows the timing during either Open Load in ON or OFF condition when the DEN pin is HIGH. Please note that a delay  $t_{sIS(FAULT_OL_OFF)}$  has to be respected after the falling edge of the input, when applying an open load in OFF diagnosis request, otherwise the diagnosis can be wrong.

Figure 25 Sense Signal in Open Load Timing

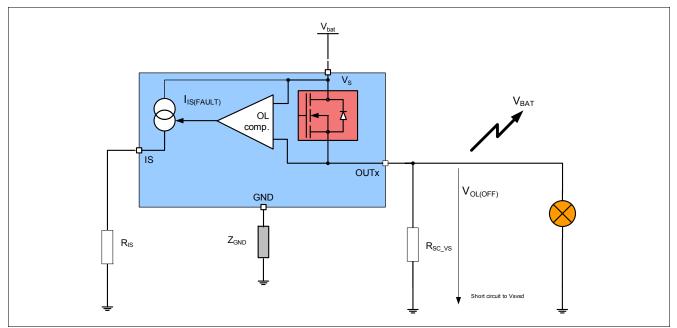

# 7.3.4 SENSE Signal with OUT in Short Circuit to V<sub>S</sub>

In case of a short circuit between the OUTput-pin and the  $V_{\rm S}$  pin, all or portion (depending on the short circuit impedance) of the load current will flow through the short circuit. As a result, a lower current compared to the normal operation will flow through the DMOS of the BTT6100-2EKA, which can be recognized at the current sense signal. The open load at OFF detection circuitry can also be used to distinguish a short circuit to  $V_{\rm S}$ . In that case, an external resistor to ground  $R_{\rm SC \ VS}$  is required. Figure 26 gives a sketch of the situation.

#### **Diagnostic Functions**

Figure 26 Short Circuit to Battery Detection in OFF Electrical Equivalent Circuit

# 7.3.5 SENSE Signal in Case of Overload

An overload condition is defined by a current flowing out of the DMOS reaching the current limitation and / or the absolute dynamic temperature swing  $T_{J(SW)}$  is reached, and / or the junction temperature reaches the thermal shutdown temperature  $T_{J(SC)}$ . Please refer to **Chapter 6.5** for details.

In that case, the SENSE signal given is by  $I_{\rm IS(FAULT)}$  when the diagnostic is selected.

The device has a thermal latch behavior, such that when the overtemperature or the exceed dynamic temperature condition has disappeared, the DMOS is reactivated only when the IN is toggled LOW to HIGH. If the DEN pin is activated, and DSEL pin is selected to the correct channel, the SENSE follows the output stage. If no reset of the latch occurs, the device remains in the latching phase and  $I_{IS(FAULT)}$  at the IS pin, eventhough the DMOS is OFF.

# 7.3.6 SENSE Signal in Case of Inverse Current

In the case of inverse current, the sense signal of the affected channel will indicate open load in OFF state and indicate open load in ON state. The unaffected channels indicate normal behavior as long as the  $I_{INV}$  current is not exceeding the maximum value specified in **Chapter 5.4**.

# 7.4 Electrical Characteristics Diagnostic Function

#### Table 9 Electrical Characteristics: Diagnostics

$V_{\rm S}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to 150°C (unless otherwise specified).

Typical values are given at  $V_{\rm S}$  = 28 V,  $T_{\rm J}$  = 25 °C

| Parameter                                               | Symbol                                      | Values  |          |         | Unit    |                                                                                                                                        | Number   |

|---------------------------------------------------------|---------------------------------------------|---------|----------|---------|---------|----------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                         |                                             | Min.    | Тур.     | Max.    |         | Test Condition                                                                                                                         |          |

| Load Condition Threshold f                              | or Diagnosti                                | )       | <b>i</b> | ł       |         |                                                                                                                                        | 1        |

| Open load detection threshold in OFF state              | V <sub>S</sub> - V <sub>OL(OFF)</sub>       | 4       | -        | 6       | V       | <sup>1)</sup> $V_{\rm IN} = 0 V$<br>$V_{\rm DEN} = 4.5 V$<br>See Figure 25                                                             | P_7.5.1  |

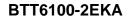

| Open load detection<br>threshold in ON state            | I <sub>L(OL)</sub>                          | 5       | _        | 25      | mA      | $V_{\rm IN} = V_{\rm DEN} = 4.5 \text{ V}$<br>$I_{\rm IS(OL)} = 22.5 \mu \text{A}$<br>See Figure 23<br>See Chapter 9.4                 | P_7.5.2  |

| Sense Pin                                               |                                             |         |          |         |         |                                                                                                                                        |          |

| IS pin leakage current when sense is disabled           | I <sub>IS_(DIS)</sub>                       | -       | 0.02     | 1       | μA      | <sup>1)</sup> $V_{\rm IN} = 4.5 V$<br>$V_{\rm DEN} = 0 V$<br>$I_{\rm L} = I_{\rm L4} = 2 A$                                            | P_7.5.4  |

| Sense signal saturation voltage                         | V <sub>S</sub> - V <sub>IS</sub><br>(range) | 1       | -        | 3.5     | V       | $V_{\rm IN} = 0 V$<br>$V_{\rm OUT} = V_{\rm S} > 10 V$<br>$V_{\rm DEN} = 4.5 V$<br>$I_{\rm IS} = 6 \text{ mA}$<br>See Chapter 9.4      | P_7.5.6  |

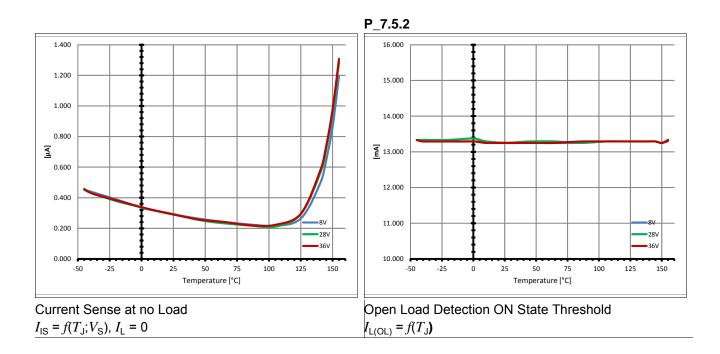

| Sense signal maximum current in fault condition         | I <sub>IS(FAULT)</sub>                      | 6       | 15       | 35      | mA      | $V_{\rm IS} = V_{\rm IN} = V_{\rm DSEL} = 0 V$ $V_{\rm OUT} = V_{\rm S} > 10 V$ $V_{\rm DEN} = 4.5 V$ See Figure 19<br>See Chapter 9.4 | P_7.5.7  |

| Sense pin maximum voltage                               | $V_{\rm IS(AZ)}$                            | 65      | 70       | 75      | V       | I <sub>IS</sub> = 5 mA<br>See <b>Figure 19</b>                                                                                         | P_7.5.3  |

| Current Sense Ratio Signal                              | in the Nomin                                | al Area | , Stable | Load Cu | rrent C | ondition                                                                                                                               | 1        |

| Current sense ratio<br>$I_{L0} = 50 \text{ mA}$         | k <sub>ILIS0</sub>                          | -50%    | 660      | +50%    |         | V <sub>IN</sub> = 4.5 V<br>V <sub>DEN</sub> = 4.5 V                                                                                    | P_7.5.8  |

| Current sense ratio $I_{L1} = 0.1 \text{ A}$            | k <sub>ILIS1</sub>                          | -40%    | 600      | +40%    |         | See Figure 20<br>T <sub>J</sub> = -40 °C; 150 °C                                                                                       | P_7.5.9  |

| Current sense ratio $I_{L2} = 0.4 \text{ A}$            | k <sub>ILIS2</sub>                          | -15%    | 600      | +15%    |         |                                                                                                                                        | P_7.5.10 |

| Current sense ratio $I_{L3} = 1 \text{ A}$              | k <sub>ILIS3</sub>                          | -11%    | 600      | +11%    |         |                                                                                                                                        | P_7.5.11 |

| Current sense ratio $I_{L4} = 2 \text{ A}$              | k <sub>ILIS4</sub>                          | -9%     | 600      | +9%     |         |                                                                                                                                        | P_7.5.12 |

| k <sub>ILIS</sub> derating with current and temperature | $\Delta k_{\rm ILIS}$                       | -8      | 0        | +8      | %       | <sup>2)</sup> $k_{ILIS3}$ versus $k_{ILIS2}$<br>See <b>Figure 21</b>                                                                   | P_7.5.17 |

| Diagnostic Timing in Norma                              | I Condition                                 |         |          |         | I       |                                                                                                                                        |          |

#### Table 9 Electrical Characteristics: Diagnostics (cont'd)

$V_{\rm S}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to 150°C (unless otherwise specified). Typical values are given at  $V_{\rm S}$  = 28 V,  $T_{\rm J}$  = 25 °C

| Parameter                                                                                                      | Symbol                                | Values L |      |      | Unit | Note /                                                                                                                                                                                                      | Number   |  |

|----------------------------------------------------------------------------------------------------------------|---------------------------------------|----------|------|------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|                                                                                                                |                                       | Min.     | Тур. | Max. |      | Test Condition                                                                                                                                                                                              |          |  |

| Current sense settling time to $k_{\rm ILIS}$ function stable after positive input slope on both INput and DEN | t <sub>sis(on)</sub>                  | -        | -    | 150  | μs   | <sup>2)</sup> $V_{\text{DEN}} = V_{\text{IN}} = 0$ to<br>4.5 V<br>$V_{\text{S}} = 28$ V<br>$R_{\text{IS}} = 1.2$ kΩ<br>$C_{\text{SENSE}} < 100$ pF<br>$I_{\text{L}} = I_{\text{L3}} = 1$ A<br>See Figure 22 | P_7.5.18 |  |

| Current sense settling time<br>with load current stable and<br>transition of the DEN                           | t <sub>sis(on_den)</sub>              | -        | -    | 10   | μs   | <sup>1)</sup> $V_{IN}$ = 4.5 V<br>$V_{DEN}$ = 0 to 4.5 V<br>$R_{IS}$ = 1.2 kΩ<br>$C_{SENSE}$ < 100 pF<br>$I_{L}$ = $I_{L3}$ = 1 A<br>See Figure 22                                                          | P_7.5.19 |  |

| Current sense settling time to $I_{\rm IS}$ stable after positive input slope on current load                  | t <sub>sIS(LC)</sub>                  | -        | -    | 15   | μs   | <sup>1)</sup> $V_{IN} = 4.5 V$<br>$V_{DEN} = 4.5 V$<br>$R_{IS} = 1.2 k\Omega$<br>$C_{SENSE} < 100 pF$<br>$I_L = I_{L2} = 0.4 A to I_L =$<br>$I_{L3} = 1 A$<br>See Figure 22                                 | P_7.5.20 |  |

| Diagnostic Timing in Open I                                                                                    | Load Conditi                          | on       |      |      |      |                                                                                                                                                                                                             |          |  |

| Current sense settling time to $I_{\rm IS}$ stable for open load detection in OFF state                        | t <sub>SIS(FAULT_OL_</sub><br>OFF)    | -        | -    | 50   | μs   | <sup>1)</sup> $V_{IN} = 0V$<br>$V_{DEN} = 0$ to 4.5 V<br>$R_{IS} = 1.2$ kΩ<br>$C_{SENSE} < 100$ pF<br>$V_{OUT} = V_S = 28$ V                                                                                | P_7.5.22 |  |

| Current sense settling time to $I_{\rm IS}$ stable for open load detection in ON-OFF transition                | t <sub>sIS(FAULT_OL_</sub><br>ON_OFF) | -        | 150  | -    | μs   | <sup>2)</sup> $V_{IN}$ = 4.5 to 0V<br>$V_{DEN}$ = 4.5 V<br>$R_{IS}$ = 1.2 kΩ<br>$C_{SENSE}$ < 100 pF<br>$V_{OUT}$ = $V_{S}$ = 28 V<br>See Figure 25                                                         | P_7.5.23 |  |

| Diagnostic Timing in Overlo                                                                                    | ad Condition                          | า        |      |      |      |                                                                                                                                                                                                             | T        |  |

| Current sense settling time to $I_{\rm IS}$ stable for overload detection                                      | <sup>f</sup> siS(FAULT)               | -        | -    | 150  | μs   | <sup>1) 3) 4)</sup> $V_{\rm IN} = V_{\rm DEN} = 0$ to<br>4.5 V<br>$R_{\rm IS} = 1.2 \text{ k}\Omega$<br>$C_{\rm SENSE} < 100 \text{ pF}$<br>$V_{\rm DS} = 5 \text{ V}$<br>See Figure 18                     | P_7.5.24 |  |

| Current sense over current<br>blanking time                                                                    | t <sub>slS(OC_blank)</sub>            |          | 350  | -    | μs   | <sup>2)</sup> $V_{IN} = V_{DEN} = 4.5 V$<br>$R_{IS} = 1.2 kΩ$<br>$C_{SENSE} < 100 pF$<br>$V_{DS} = 5 V to 0 V$<br>See Figure 18                                                                             | P_7.5.32 |  |

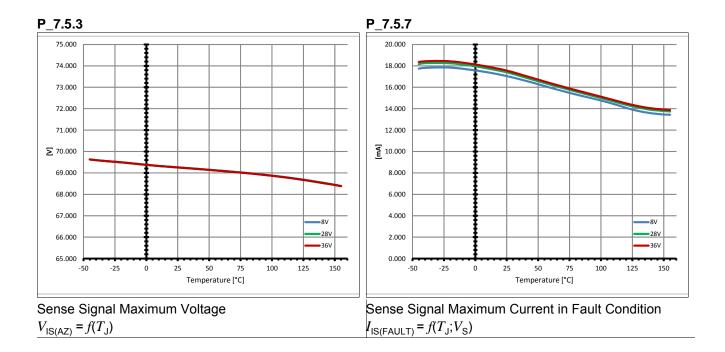

#### Table 9 Electrical Characteristics: Diagnostics (cont'd)