## **TABLE OF CONTENTS**

| Features                                                            |

|---------------------------------------------------------------------|

| Applications                                                        |

| General Description                                                 |

| Functional Block Diagram                                            |

| Revision History                                                    |

| Specifications                                                      |

| Absolute Maximum Ratings 5                                          |

| Thermal Resistance5                                                 |

| ESD Caution5                                                        |

| Pin Configuration and Function Descriptions                         |

| Typical Performance Characteristics                                 |

| Theory of Operation14                                               |

| Amplifier14                                                         |

| High Power Supply Rejection (PSR) and Common-Mode Rejection (CMR)14 |

| 1/f Noise Correction14                                              |

| REVISION HISTORY                                                    |

| 2/08—Rev. SpA to Rev. B                                             |

| Changes to Features Section                                         |

| Changes to Amplifier Section and Figure 43 14                       |

| Changes to Current Source Section                                   |

| Changes to Current Excitation Section, Output Filtering             |

| Section, Clock Feedthrough Section, and Figure 45 16                |

| Changes to Figure 46                                                |

| Current Source                               | . 15 |

|----------------------------------------------|------|

| Applications Information                     | . 16 |

| Typical Connections                          | . 16 |

| Current Excitation                           | . 16 |

| Enable/Disable Function                      | . 16 |

| Output Filtering                             | . 16 |

| Clock Feedthrough                            | . 16 |

| Maximizing Performance Through Proper Layout | . 17 |

| Power Supply Bypassing                       | . 17 |

| Dual-Supply Operation                        | . 17 |

| Pressure Sensor Bridge Application           | . 18 |

| Temperature Sensor Application               | . 19 |

| ADC/Microcontroller                          | . 19 |

| Outline Dimensions                           | . 20 |

| Ordaring Guida                               | 20   |

8/07—Revision SpA

7/07—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{\text{CC}}$  = 2.6 V to 5.0 V,  $T_{\text{A}}$  = 25°C,  $C_{\text{FILTER}}$  = 6.8 nF, output antialiasing capacitor = 68 nF,  $R_{\text{SET}}$  = 3 k $\Omega$ , common-mode input = 0.6 V, unless otherwise noted.

Table 1.

| Parameter                                                                          | Test Conditions                                                                               | Min                   | Тур      | Max                     | Unit   |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------|----------|-------------------------|--------|

| COMMON-MODE REJECTION RATIO (CMRR)                                                 | Input voltage ( $V_{INP} - V_{INN}$ )<br>range of 0.2 V to $V_{CC} - 1.7$ V                   |                       |          |                         |        |

| CMRR DC                                                                            |                                                                                               | 110                   | 120      |                         | dB     |

| NOISE                                                                              |                                                                                               |                       |          |                         |        |

| Amplifier and VREF                                                                 | Input referred, f = 0.1 Hz to 10 Hz                                                           |                       | 0.75     |                         | μV р-р |

| VOLTAGE OFFSET                                                                     |                                                                                               |                       |          |                         |        |

| Output Offset                                                                      | Reference is internal and set to 900 mV nominal                                               | 865                   | 900      | 935                     | mV     |

| Output Offset TC                                                                   | $-40$ °C < $T_A$ < $+85$ °C                                                                   | -300                  | ±50      | +300                    | μV/°C  |

| PSR                                                                                |                                                                                               |                       | 120      |                         | dB     |

| INPUT CURRENT                                                                      |                                                                                               |                       |          |                         |        |

| Input Bias Current                                                                 |                                                                                               | -1000                 | ±100     | +1000                   | pА     |

| Input Offset Current                                                               |                                                                                               | -2000                 | ±200     | +2000                   | pА     |

| DYNAMIC RESPONSE                                                                   |                                                                                               |                       |          |                         |        |

| Small Signal Bandwidth –3 dB                                                       | With external filter capacitors,  C_FILTER = 6.8 nF and output antialiasing capacitor = 68 nF |                       | 0.25     |                         | kHz    |

| GAIN                                                                               |                                                                                               |                       |          |                         |        |

| Gain                                                                               |                                                                                               |                       | 50       |                         | V/V    |

| Gain Error                                                                         |                                                                                               | -1.0                  | ±0.5     | +1.0                    | %      |

| Gain Nonlinearity                                                                  |                                                                                               |                       | ±0.0075  |                         | %      |

| Gain Drift                                                                         | $-40$ °C < $T_A$ < $+85$ °C                                                                   | -25                   | ±15      | +25                     | ppm/°C |

| INPUT                                                                              |                                                                                               |                       |          |                         |        |

| Differential Input Impedance                                                       |                                                                                               |                       | 50  1    |                         | MΩ  pF |

| Input Voltage Range                                                                |                                                                                               | 0.2                   |          | Vcc – 1.7               | V      |

| OUTPUT                                                                             |                                                                                               |                       |          |                         |        |

| Output Voltage Range                                                               | $V_{OUT} = Gain \times (V_{INP} - V_{INN}) + Output Offset$                                   | 0.075                 |          | $V_{\text{CC}} - 0.075$ | V      |

| Output Series Resistance                                                           |                                                                                               |                       | 10 ± 20% |                         | kΩ     |

| CURRENT EXCITATION                                                                 |                                                                                               |                       |          |                         |        |

| Excitation Current Range                                                           | Excitation current = $0.9 \text{ V/R}_{\text{SET}}$                                           | 300                   |          | 1300                    | μΑ     |

| Excitation Current Accuracy                                                        |                                                                                               | -1.0                  |          | +1.0                    | %      |

| Excitation Current Drift                                                           | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}$                                    | -250                  | ±50      | +250                    | ppm/°C |

| External Resistor for Setting<br>Excitation Current (R <sub>SET</sub> )            |                                                                                               | 692                   |          | 3000                    | Ω      |

| Excitation Current Power Supply Rejection                                          |                                                                                               | -2.0                  | +0.2     | +2.0                    | μA/V   |

| Excitation Current Pin Voltage                                                     |                                                                                               | 0                     |          | $V_{CC} - 1.0$          | V      |

| <b>Excitation Current Output Resistance</b>                                        |                                                                                               |                       | 100      |                         | ΜΩ     |

| Required Capacitor from Ground to<br>Excitation Current Pin (C <sub>BRIDGE</sub> ) |                                                                                               |                       | 0.1      |                         | μF     |

| ENABLE                                                                             |                                                                                               |                       |          |                         |        |

| ENBL High Level                                                                    | V <sub>cc</sub> < 2.9 V                                                                       | V <sub>CC</sub> – 0.5 |          | $V_{CC}$                | V      |

|                                                                                    | Vcc > 2.9 V                                                                                   | 2.4                   |          | $V_{CC}$                | V      |

| ENBL Low Level                                                                     |                                                                                               | GND                   |          | 0.8                     | V      |

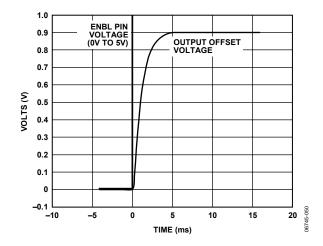

| Start-Up Time for ENBL                                                             |                                                                                               |                       | 5.0      |                         | ms     |

| Parameter                   | Test Conditions | Min | Тур                            | Max                                 | Unit |

|-----------------------------|-----------------|-----|--------------------------------|-------------------------------------|------|

| POWER SUPPLY                |                 |     |                                |                                     |      |

| Operating Range             |                 | 2.6 |                                | 5.5                                 | V    |

| Quiescent Current           |                 |     | 1.2 + 2×<br>excitation current | $1.8 + 2 \times$ excitation current | mA   |

| Shutdown Current            |                 |     | 0.5                            | 10                                  | μΑ   |

| TEMPERATURE RANGE           |                 |     |                                |                                     |      |

| For Operational Performance |                 | -40 |                                | +85                                 | °C   |

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                               | Rating               |

|-----------------------------------------|----------------------|

| Supply Voltage                          | 6 V                  |

| Input Voltage                           | +V <sub>SUPPLY</sub> |

| Differential Input Voltage <sup>1</sup> | ±V <sub>SUPPLY</sub> |

| Output Short-Circuit Duration to GND    | Indefinite           |

| Storage Temperature Range               | −65°C to +150°C      |

| Operating Temperature Range             | -40°C to +85°C       |

| Junction Temperature Range              | −65°C to +150°C      |

| Lead Temperature (Soldering, 10 sec)    | 300°C                |

$<sup>^{\</sup>rm 1}$  Differential input voltage is limited to  $\pm 5.0$  V, the supply voltage, or whichever is less.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

Table 3.

| Package Type            | θја  | <b>Ө</b> зс | Unit |

|-------------------------|------|-------------|------|

| 16-Lead LFCSP (0.55 mm) | 42.5 | 7.7         | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

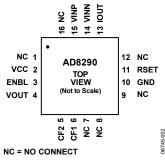

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                                                                                            |

|---------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | NC       | Tie to Ground <sup>1</sup> or Pin 16.                                                                                                                                  |

| 2       | VCC      | Positive Power Supply Voltage.                                                                                                                                         |

| 3       | ENBL     | Logic 1 enables the part, and Logic 0 disables the part.                                                                                                               |

| 4       | VOUT     | Open End of Internal 10 k $\Omega$ Resistor. Tie one end of external antialiasing filter capacitor (6.8 nF) to this pin, and tie the other end to ground. <sup>1</sup> |

| 5       | CF2      | Tie one end of the CFILTER (68 nF) that is in parallel with the internal gain resistor to this pin.                                                                    |

| 6       | CF1      | Tie the other end of the CFILTER (68 nF) that is in parallel with the internal gain resistor to this pin.                                                              |

| 7       | NC       | Tie to Ground. <sup>1</sup>                                                                                                                                            |

| 8       | NC       | Tie to Ground. <sup>1</sup>                                                                                                                                            |

| 9       | NC       | Tie to Ground. <sup>1</sup>                                                                                                                                            |

| 10      | GND      | Ground <sup>1</sup> or Negative Power Supply Voltage.                                                                                                                  |

| 11      | RSET     | Tie one end of Resistor R <sub>SET</sub> to this pin to set the excitation current and tie the other end of Resistor R <sub>SET</sub> to Pin 10.                       |

| 12      | NC       | Tie to Ground. <sup>1</sup>                                                                                                                                            |

| 13      | IOUT     | Excitation Current Output. Tie one end of C <sub>BRIDGE</sub> (0.1 μF) to this pin and tie the other end of C <sub>BRIDGE</sub> to ground. <sup>1</sup>                |

| 14      | VINN     | Negative Input Terminal.                                                                                                                                               |

| 15      | VINP     | Positive Input Terminal.                                                                                                                                               |

| 16      | NC       | Tie to Ground <sup>1</sup> or Pin 1.                                                                                                                                   |

| 17/Pad  | NC       | Pad should be floating and not tied to any potential.                                                                                                                  |

<sup>&</sup>lt;sup>1</sup> During dual-supply operation, ground becomes the negative power supply voltage.

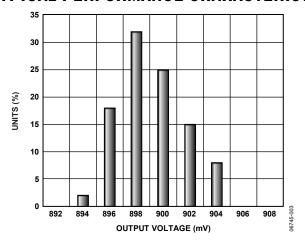

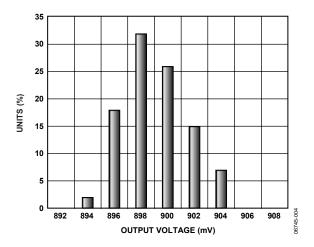

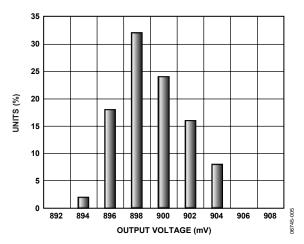

## TYPICAL PERFORMANCE CHARACTERISTICS

Figure 3. Output Offset Voltage at 2.6 V Supply

Figure 4. Output Offset Voltage at 3.6 V Supply

Figure 5. Output Offset Voltage at 5.0 V Supply

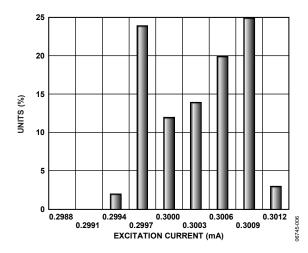

Figure 6. Excitation Output Current for 3 k $\Omega$  R<sub>SET</sub> at 2.6 V Supply

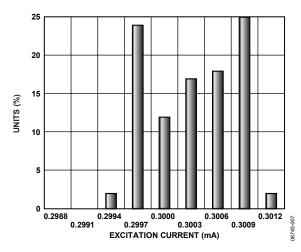

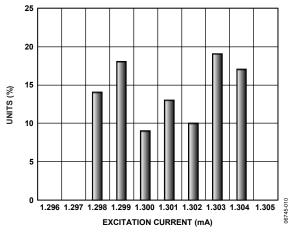

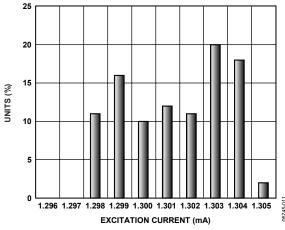

Figure 7. Excitation Output Current for 3 k $\Omega$  R<sub>SET</sub> at 3.6 V Supply

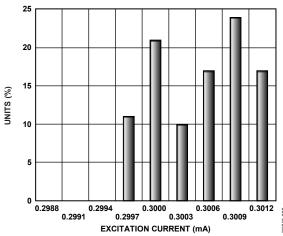

Figure 8. Excitation Output Current for 3  $k\Omega$  R<sub>SET</sub> at 5.0 V Supply

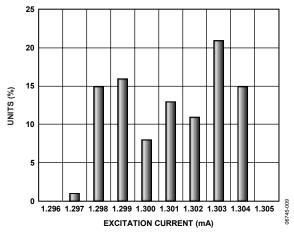

Figure 9. Output Excitation Current for 692  $\Omega$  R<sub>SET</sub> at 2.6 V Supply

Figure 10. Output Excitation Current for 692  $\Omega$  R<sub>SET</sub> at 3.6 V Supply

Figure 11. Output Excitation Current for 692  $\Omega$  R<sub>SET</sub> at 5.0 V Supply

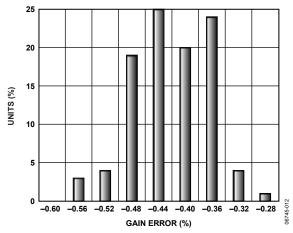

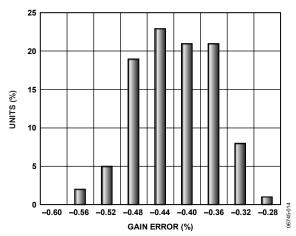

Figure 12. Percent Gain Error at 2.6 V Supply

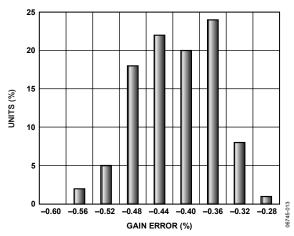

Figure 13. Percent Gain Error at 3.6 V Supply

Figure 14. Percent Gain Error at 5.0 V Supply

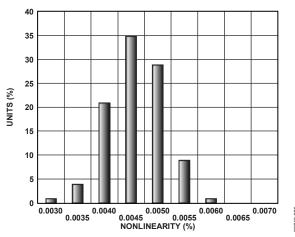

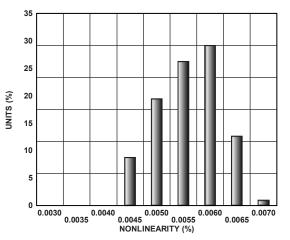

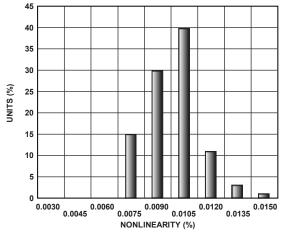

Figure 15. Percent Nonlinearity at 2.6 V Supply

Figure 16. Percent Nonlinearity at 3.6 V Supply

Figure 17. Percent Nonlinearity at 5.0 V Supply

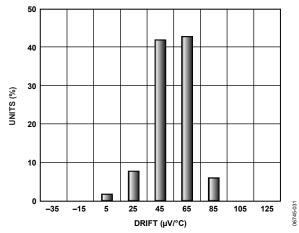

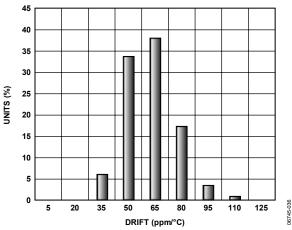

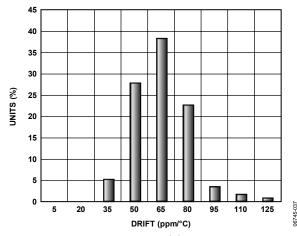

Figure 18. Output Offset Voltage Drift from −40°C to +85°C at 2.6 V Supply

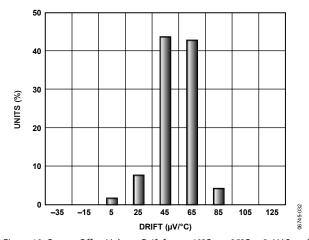

Figure 19. Output Offset Voltage Drift from  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  at 3.6 V Supply

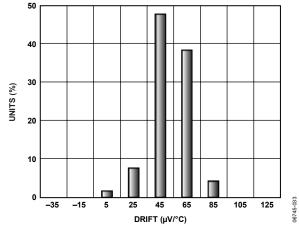

Figure 20. Output Offset Voltage Drift from  $-40^{\circ}$ C to  $+85^{\circ}$ C at 5.0 V Supply

Figure 21. Excitation Current Drift from  $-40^{\circ}$ C to  $+85^{\circ}$ C at 2.6 V Supply,  $R_{SET} = 3 \text{ k}\Omega$

Figure 22. Excitation Current Drift from  $-40^{\circ}$ C to  $+85^{\circ}$ C at 3.6 V Supply,  $R_{SET}=3~k\Omega$

Figure 23. Excitation Current Drift from  $-40^{\circ}$ C to  $+85^{\circ}$ C at 5.0 V Supply,  $R_{SET}=3$  k $\Omega$

Figure 24. Excitation Current Drift from  $-40^{\circ}$ C to  $+85^{\circ}$ C at 2.6 V Supply,  $R_{SET} = 692 \Omega$

Figure 25. Excitation Current Drift from  $-40^{\circ}$ C to  $+85^{\circ}$ C at 3.6 V Supply,  $R_{SET} = 692 \Omega$

Figure 26. Excitation Current Drift from  $-40^{\circ}$ C to  $+85^{\circ}$ C at 5.0 V Supply,  $R_{SET}=692~\Omega$

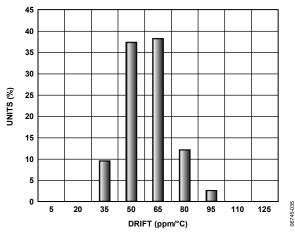

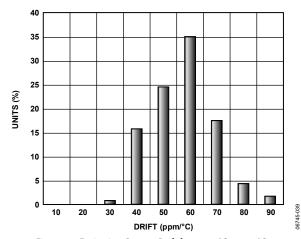

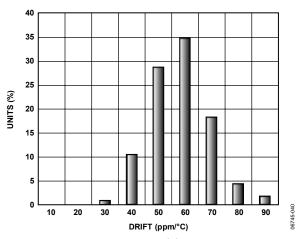

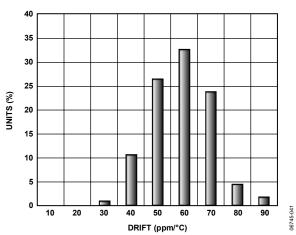

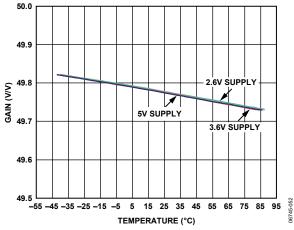

Figure 27. Gain Drift from  $-40^{\circ}$ C to  $+85^{\circ}$ C at 2.6 V Supply

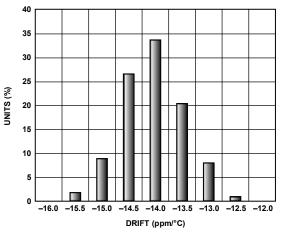

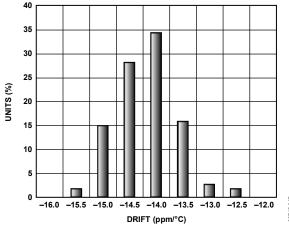

Figure 28. Gain Drift from −40°C to +85°C at 3.6 V Supply

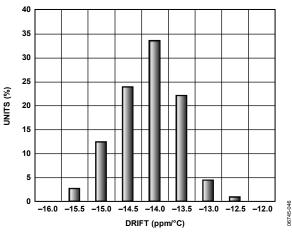

Figure 29. Gain Drift from −40°C to +85°C at 5.0 V Supply

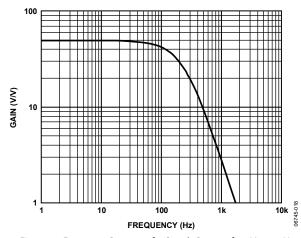

Figure 30. Frequency Response for Supply Range of 2.6 V to 5.0 V (External C<sub>FILTER</sub> = 6.8 nF, Antialiasing Capacitor = 68 nF)

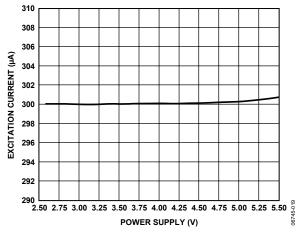

Figure 31. Low Excitation Current vs. Power Supply

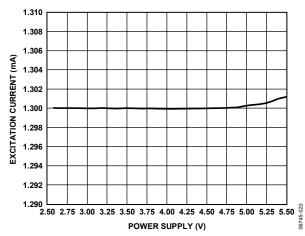

Figure 32. High Excitation Current vs. Power Supply

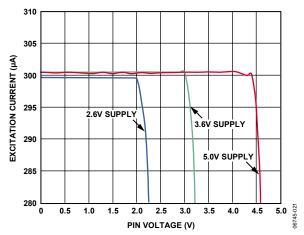

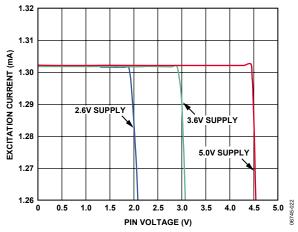

Figure 33. Low Excitation Current vs. Excitation Current Pin Voltage

Figure 34. High Excitation Current vs. Excitation Current Pin Voltage

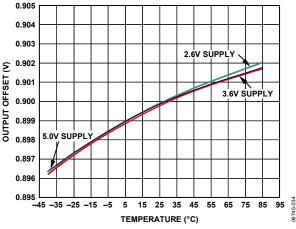

Figure 35. Output Offset Voltage vs. Temperature

Figure 36. Gain vs. Temperature

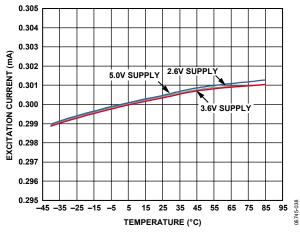

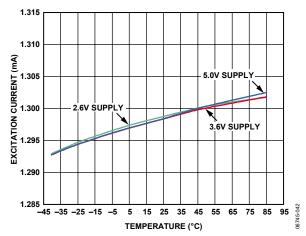

Figure 37. Excitation Current vs. Temperature,  $R_{SET} = 3 \text{ k}\Omega$

Figure 38. Excitation Current vs. Temperature,  $R_{SET} = 692 \Omega$

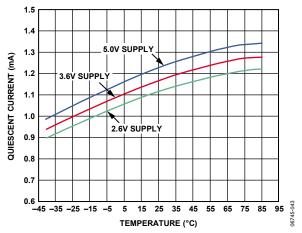

$\textit{Figure 39. Quiescent Current vs. Temperature (Excludes 2 \times Excitation Current)}$

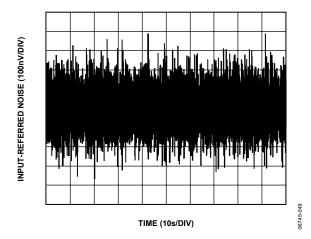

Figure 40. 0.01 Hz to 10 Hz Input-Referred Noise

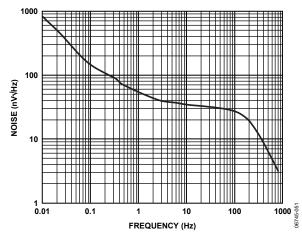

Figure 41. Input-Referred Noise vs. Frequency

Figure 42. ENBL Pin Voltage for 5.0 V Supply vs. Output Offset Voltage Start-Up Time

# THEORY OF OPERATION AMPLIFIER

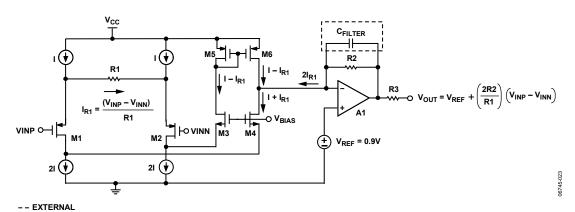

The amplifier of the AD8290 is a precision current-mode correction instrumentation amplifier. It is internally set to a fixed gain of 50. The current-mode correction topology results in excellent accuracy.

Figure 43 shows a simplified diagram illustrating the basic operation of the instrumentation amplifier within the AD8290 (without correction). The circuit consists of a voltage-to-current amplifier (M1 to M6), followed by a current-to-voltage amplifier (R2 and A1). Application of a differential input voltage forces a current through R1, resulting in a conversion of the input voltage to a signal current. Transistors M3 to M6 transfer twice the signal current to the inverting input of the op amp, A1. A1 and R2 form a current-to-voltage converter to produce a rail-to-rail output voltage, V<sub>OUT</sub>.

Op Amp A1 is a high precision auto-zero amplifier. This amplifier preserves the performance of the autocorrecting, current-mode amplifier topology while offering the user a true voltage-in, voltage-out instrumentation amplifier. Offset errors are corrected internally.

An internal 0.9 V reference voltage is applied to the noninverting input of A1 to set the output offset level. External Capacitor  $C_{\text{FILTER}}$  is used to filter out correction noise.

# HIGH POWER SUPPLY REJECTION (PSR) AND COMMON-MODE REJECTION (CMR)

PSR and CMR indicate the amount that the offset voltage of an amplifier changes when its common-mode input voltage or power supply voltage changes. The autocorrection architecture of the AD8290 continuously corrects for offset errors, including those induced by changes in input or supply voltage, resulting in exceptional rejection performance. The continuous autocorrection provides great CMR and PSR performances over the entire operating temperature range ( $-40^{\circ}$ C to  $+85^{\circ}$ C).

### 1/f NOISE CORRECTION

Flicker noise, also known as 1/f noise, is noise inherent in the physics of semiconductor devices and decreases 10 dB per decade. The 1/f corner frequency of an amplifier is the frequency at which the flicker noise is equal to the broadband noise of the amplifier. At lower frequencies, flicker noise dominates causing large errors in low frequency or dc applications.

Flicker noise appears as a slowly varying offset error that is reduced by the autocorrection topology of the AD8290, allowing the AD8290 to have lower noise near dc than standard low noise instrumentation amplifiers.

Figure 43. Simplified Schematic of the Instrumentation Amplifier Within the AD8290

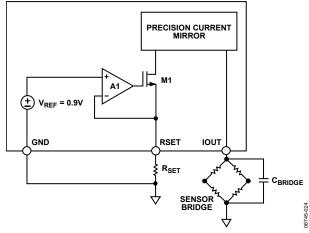

### **CURRENT SOURCE**

The AD8290 generates an excitation current that is programmable with an external resistor,  $R_{\text{SET}}$ , as shown in Figure 44. A1 and M1 are configured to produce 0.9 V across  $R_{\text{SET}}$ , which is based on an internal 0.9 V reference and creates a current equal to 0.9 V/R\_{\text{SET}} internal to the AD8290. This current is passed to a precision current mirror and a replica of the current is sourced from the IOUT pin. This current can be used for the excitation of a sensor bridge.  $C_{\text{BRIDGE}}$  is used to filter noise from the current excitation circuit.

Figure 44. Current Excitation

# APPLICATIONS INFORMATION TYPICAL CONNECTIONS

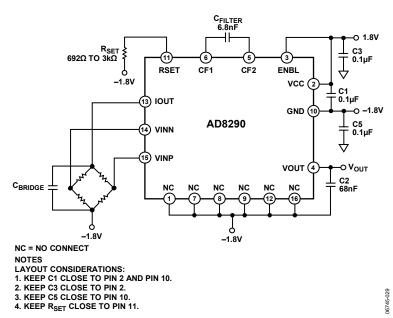

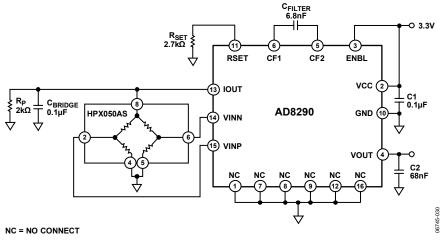

Figure 45 shows the typical connections for single-supply operation when used with a sensor bridge.

#### **CURRENT EXCITATION**

In Figure 45,  $R_{\text{SET}}$  is used to set the excitation current sourced at the IOUT pin. The formula for the excitation current  $I_{\text{OUT}}$  is

$I_{OUT} = (900/R_{SET}) \text{ mA}$

where  $R_{SET}$  is the resistor between Pin 10 (GND) and Pin 11 (RSET).

The AD8290 is internally set by the factory to provide the current excitation described by the previous formula (within the tolerance range listed in Table 1). The range of  $R_{\text{SET}}$  is 692  $\Omega$  to 3 k $\Omega$ , resulting in a corresponding  $I_{\text{OUT}}$  of 1300  $\mu A$  to 300  $\mu A$ , respectively.

### **ENABLE/DISABLE FUNCTION**

Pin 3 (ENBL) provides the enabling/disabling function of the AD8290 to conserve power when the device is not needed. A Logic 1 turns the part on and allows it to operate normally. A Logic 0 disables the output and excitation current and reduces the quiescent current to less than 10  $\mu$ A.

The turn-on time upon switching Pin 3 high is dominated by the output filters. When the device is disabled, the output becomes high impedance, enabling the muxing application of multiple AD8290 instrumentation amplifiers.

### **OUTPUT FILTERING**

Filter Capacitor  $C_{\text{FILTER}}$  is required to limit the amount of switching noise present at the output. The recommended bandwidth of the filter created by  $C_{\text{FILTER}}$  and an internal  $100~\text{k}\Omega$  is 235 Hz. Select  $C_{\text{FILTER}}$  based on

$C_{FILTER} = 1/(235 \times 2 \times \pi \times 100 \text{ k}\Omega) = 6.8 \text{ nF}$

For bandwidths greater than 10 Hz, an additional single-pole RC filter of 235 Hz is required on the output, which is also recommended when driving an ADC requiring an antialiasing filter. Internal to the AD8290 is a series 10 k $\Omega$  resistor at the output (R3 in Figure 43) and using an external 68 nF capacitor to ground produces an RC filter of 235 Hz on the output as well. These two filters produce an overall bandwidth of approximately 160 Hz for the output signal.

In addition, when driving low impedances, the internal series  $10 \text{ k}\Omega$  resistor creates a voltage divider at the output. If it is necessary to access the output of the internal amplifier prior to the  $10 \text{ k}\Omega$  resistor, it is available at the CF2 pin.

For applications with low bandwidths (<10 Hz), only the first filter capacitor (C<sub>FILTER</sub>) is required. In this case, the high frequency noise from the auto-zero amplifier (output amplifier) is not filtered before the following stage.

### **CLOCK FEEDTHROUGH**

The AD8290 uses two synchronized clocks to perform autocorrection. The input voltage-to-current amplifiers are corrected at 60 kHz.

Trace amounts of these clock frequencies can be observed at the output. The amount of feedthrough is dependent upon the gain because the autocorrection noise has an input- and output-referred term. The correction feedthrough is also dependent upon the values of the external capacitors, C2 and CFILTER.

NOTES

LAYOUT CONSIDERATIONS:

1. KEEP C1 CLOSE TO PIN 2 AND PIN 10. 2. KEEP R<sub>SET</sub> CLOSE TO PIN 11.

> Figure 45. Typical Single-Supply Connections Rev. B | Page 16 of 20

# MAXIMIZING PERFORMANCE THROUGH PROPER LAYOUT

To achieve the maximum performance of the AD8290, care should be taken in the circuit board layout. The PCB surface must remain clean and free of moisture to avoid leakage currents between adjacent traces. Surface coating of the circuit board reduces surface moisture and provides a humidity barrier, reducing parasitic resistance on the board.

$R_{\text{SET}}$  should be placed close to RSET (Pin 11) and GND (Pin 10). The paddle on the bottom of the package should not be connected to any potential and should be floating.

For high impedance sources, the PCB traces from the AD8290 inputs should be kept to a minimum to reduce input bias current errors.

### POWER SUPPLY BYPASSING

The AD8290 uses internally generated clock signals to perform autocorrection. As a result, proper bypassing is necessary to achieve optimum performance. Inadequate or improper bypassing of the supply lines can lead to excessive noise and offset voltage. A 0.1  $\mu F$  surface-mount capacitor should be connected between Pin 2 (VCC) and Pin 10 (GND) when operating with a single supply and should be located as close as possible to those two pins.

### **DUAL-SUPPLY OPERATION**

The AD8290 can be configured to operate in dual-supply mode. An example of such a circuit is shown in Figure 46, where the AD8290 is powered by  $\pm 1.8$  V supplies. When operating with dual supplies, pins that are normally referenced to ground in the single-supply mode, now need to be referenced to the negative supply. These pins include the following: Pin 1, Pin 7, Pin 8, Pin 9, Pin 10, Pin 12, and Pin 16. External components, such as  $R_{SET}$ , the sensing bridge, and the antialiasing filter capacitor at the output, should also be referenced to the negative supply. Additionally, two bypass capacitors should be added beyond what is necessary for single-supply operation: one between the negative supply and ground, and the other between the positive and negative supplies.

When operating in dual-supply mode, the specifications change and become relative to the negative supply. The input voltage range minimum shifts from 0.2 V to 0.2 V above the negative supply (in this example: -1.6 V), the output voltage range shifts from a minimum of 0.075 V to 0.075 V above the negative supply (in this example: -1.725 V), and the excitation current pin voltage minimum shifts from 0 V to -1.8 V in this example. The maximum specifications of these three parameters are specified relative to  $V_{\rm CC}$  in Table 1 and do not change.

For other specifications, both the minimum and maximum specifications change. The output offset shifts from a minimum of +865 mV and maximum of +935 mV to a minimum of -935 mV and a maximum of -865 mV in the example. In addition, the logic levels for the ENBL operation should be adjusted accordingly.

Figure 46. Typical Dual-Supply Connections

### PRESSURE SENSOR BRIDGE APPLICATION

Given its excitation current range, the AD8290 provides a good match with pressure sensor circuits. Two such sensors are the Fujikura FGN-615PGSR and the Honeywell HPX050AS. Figure 47 shows the AD8290 paired with the Honeywell bridge and the appropriate connections. In this example, a resistor,  $R_{\text{P}}$ , is added to the circuit to ensure that the maximum output voltage of the AD8290 is not exceeded. Depending on the sensors specifications,  $R_{\text{P}}$  may not be necessary.

The specifications for the bridge are show in Table 5 and the chosen conditions for the AD8290 are listed in Table 6.

Given these specifications, calculations should be made to ensure that the AD8290 is operating within its required ranges. The combination of the excitation current and  $R_{\text{P}}$  must be chosen to ensure that the conditions stay within the minimum and maximum specifications of the AD8290. For this example, because the specifications of the HPX050AS are for a bridge excitation voltage of 3.0 V, care must be taken to scale the resulting voltage calculations to the actual bridge voltage. The required calculations are shown in Table 7.

Figure 47. HPX050AS Pressure Sensor Application

Table 5. HPX050AS Specifications

| Bridge Imp | oedance (Ω) | Rated Of | fset (mV) | Rated Outpo | ut Span (mV) |                           |

|------------|-------------|----------|-----------|-------------|--------------|---------------------------|

| Minimum    | Maximum     | Minimum  | Maximum   | Minimum     | Maximum      | Bridge Excite Voltage (V) |

| 4000       | 6000        | -30      | +30       | 0           | 80           | 3.0                       |

Table 6. Typical AD8290 Conditions for Pressure Sensor Circuit

| AD8290 Vcc (V)   | Excitation Current (μA) | Parallel Resistor R <sub>P</sub> (Ω) |

|------------------|-------------------------|--------------------------------------|

| 3.3 (2.6 to 5.5) | 333.3 (300 to 1300)     | 2000                                 |

Table 7. Pressure Sensor Circuit Calculations Compared to AD8290 Minimum/Maximum Specifications

| Specification                                           | Calculation | Unit | Allowable Range of AD8290 |

|---------------------------------------------------------|-------------|------|---------------------------|

| Supply Current                                          | 1.867       | mA   |                           |

| Current Setting Resistor (RSET)                         | 2700        | Ω    | 692 Ω to 3000 Ω           |

| Minimum Equivalent Resistance to IOUT Pin               | 1333        | Ω    |                           |

| Maximum Equivalent Resistance to IOUT Pin               | 1500        | Ω    |                           |

| Minimum Current into Bridge                             | 83.333      | μΑ   |                           |

| Maximum Current into Bridge                             | 111.111     | μΑ   |                           |

| Minimum Bridge Midpoint Voltage (Excluding Offset/Span) | 0.222       | V    |                           |

| Maximum Bridge Midpoint Voltage (Excluding Offset/Span) | 0.250       | V    |                           |

| Minimum Voltage at Current Output Pin (IOUT)            | 0.444       | V    | >0.0 V                    |

| Maximum Voltage at Current Output Pin (IOUT)            | 0.500       | V    | <2.3 V                    |

| Input Voltage Minimum                                   | 0.218       | V    | >0.2 V                    |

| Input Voltage Maximum                                   | 0.266       | V    | <1.6 V                    |

| Output Voltage Minimum                                  | 0.643       | V    | >0.075 V                  |

| Output Voltage Maximum                                  | 1.852       | V    | <3.225 V                  |

### **TEMPERATURE SENSOR APPLICATION**

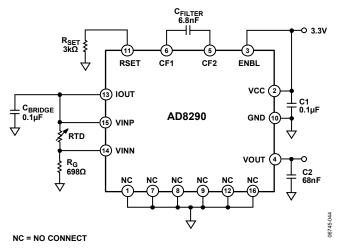

The AD8290 can be used with a temperature sensor. Figure 48 shows the AD8290 in conjunction with an RTD, in this example, a 2-wire PT100. The specifications for the sensor are shown in Table 8 and the chosen conditions for the AD8290 are listed in Table 9.

Once again, care must be taken when picking the excitation current and R<sub>G</sub> such that the minimum and maximum specifications of the AD8290 are not exceeded. Sample calculations are shown in Table 10.

### ADC/MICROCONTROLLER

In both of the previous applications, an ADC or a microcontroller can be used to follow the AD8290 to convert the output analog signal to digital. For example, if there are multiple sensors in the system, the six channel ADuC814ARU microcontoller is an excellent candidate to interface with multiple AD8290s.

Figure 48. PT100 Temperature Sensor Application Connections

### **Table 8. PT100 Specifications**

| RTD Minimum @ 0°C | RTD Maximum @ 100°C |

|-------------------|---------------------|

| 100 Ω             | 138.5 Ω             |

### Table 9. Typical AD8290 Conditions for Temperature Sensor Circuit

| AD8290 Vcc (V)    | Excitation Current (μA) | Resistor from RTD to GND, $R_G(\Omega)$ |

|-------------------|-------------------------|-----------------------------------------|

| 3.30 (2.6 to 5.5) | 300 (300 to 1300)       | 698                                     |

Table 10. Temperature Sensor Circuit Calculations Compared to AD8290 Minimum/Maximum Specifications

| Specification                                | Calculation | Unit | Allowable Range of AD8290 |

|----------------------------------------------|-------------|------|---------------------------|

| Supply Current                               | 1.8         | mA   |                           |

| Current Setting Resistor (R <sub>SET</sub> ) | 3000        | Ω    | 692 Ω to 3000 Ω           |

| Minimum Equivalent Resistance to IOUT Pin    | 798         | Ω    |                           |

| Maximum Equivalent Resistance to IOUT Pin    | 836.5       | Ω    |                           |

| Minimum Voltage @ Current Output Pin (IOUT)  | 0.239       | V    | >0.0 V                    |

| Maximum Voltage @ Current Output Pin (IOUT)  | 0.251       | V    | <2.3 V                    |

| Input Voltage Minimum                        | 0.209       | V    | >0.2 V                    |

| Input Voltage Maximum                        | 0.251       | V    | <1.6 V                    |

| Output Voltage Minimum                       | 2.365       | V    | >0.075 V                  |

| Output Voltage Maximum                       | 3.013       | V    | <3.225 V                  |

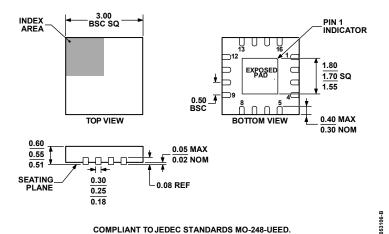

## **OUTLINE DIMENSIONS**

Figure 49. 16-Lead Lead Frame Chip Scale Package [LFCSP\_UQ] 3 mm × 3 mm Body, Ultra Thin Quad (CP-16-12) Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                      | Temperature Range | Package Description | Package Option | Branding |  |  |

|----------------------------|-------------------|---------------------|----------------|----------|--|--|

| AD8290ACPZ-R2 <sup>1</sup> | -40°C to +85°C    | 16-Lead LFCSP_UQ    | CP-16-12       | YOJ      |  |  |

| AD8290ACPZ-R71             | -40°C to +85°C    | 16-Lead LFCSP_UQ    | CP-16-12       | YOJ      |  |  |

| AD8290ACPZ-RL <sup>1</sup> | -40°C to +85°C    | 16-Lead LFCSP_UQ    | CP-16-12       | YOJ      |  |  |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

Rev. B | Page 20 of 20