# ORDERING INFORMATION®®

| PART NUMBER    | BATTERY<br>VOLTAGE | SYSTEM<br>VOLTAGE | PACKAGE   | PINS | TEMPERATURE<br>RANGE |

|----------------|--------------------|-------------------|-----------|------|----------------------|

| ACT3780QY-T    | 4.2V               | 4.6V              | TQFN44-20 | 20   | -40°C to 85°C        |

| ACT3780QY410-T | 4.1V               | 4.6V              | TQFN44-20 | 20   | -40°C to 85°C        |

①: All Active-Semi components are RoHS Compliant and with Pb-free plating unless specified differently. The term Pb-free means semiconductor products that are in compliance with current RoHS (Restriction of Hazardous Substances) standards.

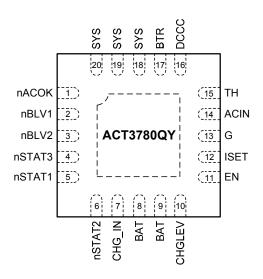

### PIN CONFIGURATION

Top View

Thin-QFN44-20

②: Standard product options are identified in this table. Contact factory for custom options. Minimum order quantity is 12,000 units.

# **PIN DESCRIPTIONS**

| PIN           | NAME   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                           |

|---------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | nACOK  | CHG_IN Status Output. nACOK is an open-drain which sinks current whenever V <sub>CHG_IN</sub> is within it's valid operating range.                                                                                                                                                                                                                   |

| 2             | nBLV1  | Battery Voltage level Monitor Output 1. Open-drain output that sinks current when asserted. Connect a 10k or greater pull-up resistors between nBLV1 and a suitable voltage supply. See Battery Voltage Level Indication Section for more information.                                                                                                |

| 3             | nBLV2  | Battery Voltage level Monitor Output 2. Open-drain output that sinks current when asserted. Connect a 10k or greater pull-up resistors between nBLV2 and a suitable voltage supply. See Battery Voltage Level Indication Section for more information.                                                                                                |

| 4             | nSTAT3 | CHG_IN OVP Status Output. Open-drain output that sinks current whenever V <sub>CHG_IN</sub> is greater than OVP threshold 6.9V (typ) while battery is present. For a logic-level charge status indicator, simply connect a 10k or greater pull-up resistor between nSTAT3 and a suitable voltage supply.                                              |

| 5             | nSTAT1 | Charge State Indicator. Open-drain output with an internal 6mA current limit, allowing this pin to directly drive an indicator LED. For a logic-level charge status indicator, simply connect a 10k or greater pull-up resistor between nSTAT1 and a suitable voltage supply. See the <i>Charging Status Indication</i> Section for more information. |

| 6             | nSTAT2 | Charge State Indicator. Open-drain output with an internal 6mA current limit, allowing this pin to directly drive an indicator LED. For a logic-level charge status indicator, simply connect a 10k or greater pull-up resistor between nSTAT2 and a suitable voltage supply. See the <i>Charging Status Indication</i> Section for more information. |

| 13            | G      | Ground.                                                                                                                                                                                                                                                                                                                                               |

| 7             | CHG_IN | Power Input. Bypass to G with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                                                                                                                                                 |

| 8, 9          | BAT    | Battery Charger output. Connect this pin to the positive terminal of the battery. Bypass to G with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                                                                            |

| 10            | CHGLEV | Charging State Select Input. Drive CHGLEV to VSYS or to a logic high for high-current charging mode or drive to G or a logic low for low-current charging mode. See the <i>ACIN</i> and <i>CHGLEV Inputs</i> section for more information.                                                                                                            |

| 11            | EN     | EN Charger Enable Input. Drive to a logic high to enable IC, drive to a logic low to disable the device and enter suspend mode.                                                                                                                                                                                                                       |

| 12            | ISET   | Charge Current Set Input. Connect a resistor from ISET to G to set the fast-charge current.                                                                                                                                                                                                                                                           |

| 14            | ACIN   | AC Adaptor Detect Logic Input. Detects presence of a wall adaptor and automatically adjusts the charge current to the maximum charge current level. See the ACIN and CHGLEV Inputs section for more information.                                                                                                                                      |

| 15            | TH     | Temperature Sensing Input. Connect to battery thermistor terminal. See the <i>Battery Temperature Monitoring</i> section for more information.                                                                                                                                                                                                        |

| 16            | DCCC   | Dynamic Control of Charging Current Set Input. Connect a resistor from DCCC to G to set the DCCC voltage. See the <i>Dynamic Charge Current Control</i> section for more information.                                                                                                                                                                 |

| 17            | BTR    | Safety Timer Programming Input. Connect a resistor from BTR to G to set the safety timers. Do not leave this pin floating. See the <i>Charging Safety Timers</i> Section for more information.                                                                                                                                                        |

| 18, 19,<br>20 | SYS    | System Power Output. Bypass to G with a high quality ceramic capacitor placed as close to the IC as possible.                                                                                                                                                                                                                                         |

|               | EP     | Exposed Pad. Must be soldered to ground on the PCB.                                                                                                                                                                                                                                                                                                   |

Downloaded from Arrow.com.

# **ABSOLUTE MAXIMUM RATINGS®**

| PARAMETER                                                                                         | VALUE        | UNIT |

|---------------------------------------------------------------------------------------------------|--------------|------|

| CHG_IN to G                                                                                       | -0.3 to + 14 | V    |

| BAT, SYS, BTR, ISET, DCCC, ACIN, CHGLEV, EN, TH, nACOK, nSTAT1, nSTAT2, nSTAT3, nBLV1, nBLV2 to G | -0.3 to + 6  | V    |

| Input Current                                                                                     | 3.5          | Α    |

| Output Current (Internal Limit) BAT to SYS                                                        | 4            | Α    |

| Maximum Junction Temperature                                                                      | -40 to 150   | °C   |

| Storage Temperature                                                                               | -60 to 150   | °C   |

| Lead Temperature (Soldering, 10 sec)                                                              | 300          | °C   |

①: Do not exceed these limits to prevent damage to the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CHG\_IN} = 5.0V, R_{ISET} = 1k\Omega, R_{BTR} = 62k\Omega, R_{DCCC} = 18.7k\Omega, T_A = 25^{\circ}C, unless otherwise specified.)$

| PARAMETER                   | SYMBOL                   | TEST CONDITIONS                                                                                                                              | MIN  | TYP  | MAX  | UNIT |  |

|-----------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| ActivePath                  |                          |                                                                                                                                              |      |      |      |      |  |

| CHG_IN Voltage Range        | $V_{\text{CHG\_IN}}$     |                                                                                                                                              | 4.35 |      | 12   | V    |  |

| CHG_IN UVLO Voltage         | $V_{\text{UVLO}}$        | Voltage Rising                                                                                                                               | 3.65 | 3.85 | 4.05 | V    |  |

| CHG_IN UVLO Hysteresis      | V <sub>HYS(UVLO)</sub>   |                                                                                                                                              |      | 1.25 |      | V    |  |

| CHG_IN OVP Threshold        | V <sub>OVP</sub>         | Voltage Rising                                                                                                                               | 6.60 | 6.90 | 7.20 | V    |  |

| CHG_IN OVP Hysteresis       | V <sub>HYS(OVP)</sub>    |                                                                                                                                              |      | 360  |      | mV   |  |

|                             | I <sub>SUP(CHG_IN)</sub> | V <sub>CHG_IN</sub> = 6V, V <sub>BAT</sub> float                                                                                             |      | 60   | 200  | μΑ   |  |

| CHG_IN Supply Current       |                          | $V_{CHG\_IN}$ = 6V, $V_{BAT}$ = 4.3V, <i>ActivePath</i> <sup>TM</sup> Enabled and SYS No Load, Charger in EOC or Time Out state or Disabled. |      | 1.8  |      | mA   |  |

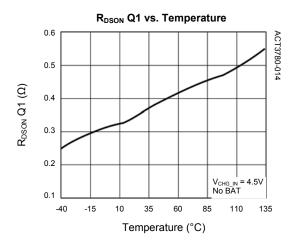

| CHG_IN to SYS On-Resistance | R <sub>DSON_Q1</sub>     | I <sub>SYS</sub> = 100mA                                                                                                                     |      | 0.3  | 0.5  | Ω    |  |

|                             | I <sub>AC</sub>          | ACIN = 1                                                                                                                                     |      | 2.5  |      | Α    |  |

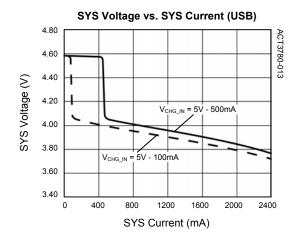

| CHG_IN to SYS Current Limit |                          | ACIN = G, CHGLEV = G                                                                                                                         | 80   | 90   | 100  | mA   |  |

|                             | I <sub>USB</sub>         | ACIN = G, CHGLEV = SYS                                                                                                                       | 400  | 450  | 500  | mA   |  |

| SYS and DCCC Regulation     | SYS and DCCC Regulation  |                                                                                                                                              |      |      |      |      |  |

| SYS Regulated Voltage       | V <sub>SYS_REG</sub>     | I <sub>SYS</sub> = 100mA                                                                                                                     | 4.4  | 4.6  | 4.8  | V    |  |

| DCCC Pull-Up Current        | I <sub>DCCC</sub>        |                                                                                                                                              | 90   | 100  | 110  | μΑ   |  |

# **ELECTRICAL CHARACTERISTICS CONT'D**

$(V_{CHG\_IN} = 5.0V, \, R_{ISET} = 1 k\Omega, \, R_{BTR} = 62 k\Omega, \, R_{DCCC} = 18.7 k\Omega, \, T_A = 25^{\circ}C, \, unless \, otherwise \, specified.)$

| PARAMETER                            | SYMBOL                   | TEST CONDITIONS                                                |                                                    | MIN    | TYP               | MAX   | UNIT |  |

|--------------------------------------|--------------------------|----------------------------------------------------------------|----------------------------------------------------|--------|-------------------|-------|------|--|

| Charger                              |                          |                                                                |                                                    |        |                   |       |      |  |

| BAT to SYS On Resistance             | R <sub>DSON_Q2</sub>     |                                                                |                                                    |        | 50                |       | mΩ   |  |

| SYS to BAT Turn On<br>Threshold      | V <sub>CHG_ON</sub>      | SYS - BAT                                                      |                                                    |        | 40                | 75    | mV   |  |

| SYS to BAT Turn Off<br>Threshold     | $V_{\text{CHG\_OFF}}$    | SYS - BAT                                                      |                                                    |        | -30               |       | IIIV |  |

| Charge Termination Voltage           | V                        | T <sub>A</sub> = 25°C                                          | ACT3780QY                                          | 4.179  | 4.200             | 4.221 | V    |  |

| Charge remination voltage            | $V_{TERM}$               | 1 <sub>A</sub> - 25 C                                          | ACT3780QY410                                       | 4.075  | 4.100             | 4.125 | V    |  |

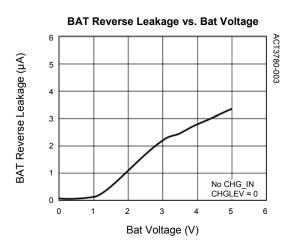

| Battery Reverse Leakage<br>Current   | I <sub>BAT_REV</sub>     | V <sub>SYS</sub> < V <sub>BAT</sub> -                          | + 100mV, I <sub>SYS</sub> = 0mA                    |        | 2.5               | 5     | μA   |  |

| Line Regulation                      |                          | V <sub>SYS</sub> = 4.5V                                        | to 5.5V, I <sub>BAT</sub> = 10mA                   |        | 0.025             |       | %/V  |  |

| ISET Pin Voltage                     | $V_{FSTSET}$             | Fast Charge                                                    | )                                                  |        | 1                 |       | · V  |  |

| ISET PIII Voltage                    | $V_{PRESET}$             | Precondition                                                   | n Charge                                           |        | 0.1               |       | V    |  |

|                                      |                          |                                                                | ACIN = G, CHGLEV = G <sup>©</sup>                  | 80     | 90                | 100   | -    |  |

| Charge Current                       | Іғѕтсне                  | $V_{BAT} = 3.5V$<br>$R_{ISET} = 1k\Omega$                      | ACIN = G, CHGLEV = SYS®                            | 400    | 450               | 500   |      |  |

| Charge Current                       |                          |                                                                | ACIN = SYS, CHGLEV = G                             | -17.5% | 0.5*ISET          | 17.5% |      |  |

|                                      |                          |                                                                | ACIN = SYS, CHGLEV = SYS                           | -12.5% | ISET <sup>®</sup> | 12.5% |      |  |

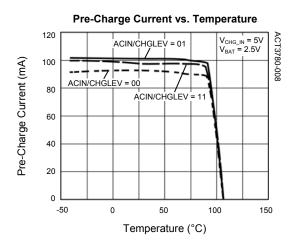

|                                      | I <sub>PRECHG</sub>      | V <sub>BAT</sub> = 2.5V                                        | ACIN = G, CHGLEV = G                               | MIN (1 | 0%ISET,           | 90mA) | mA   |  |

|                                      |                          |                                                                | ACIN = G, CHGLEV = SYS                             |        | 10%<br>ISET       |       |      |  |

| Precondition Charge Current          |                          |                                                                | ACIN = SYS, CHGLEV = G                             |        | 10%<br>ISET       |       |      |  |

|                                      |                          |                                                                | ACIN = SYS, CHGLEV = SYS                           |        | 10%<br>ISET       |       |      |  |

| Leakage Current to BAT               | I <sub>LKG_BAT</sub>     |                                                                | , Charger is in EOC state or lt state or disabled. |        | 0                 | 5     | μΑ   |  |

| Precondition Voltage<br>Threshold    | $V_{PRECHG}$             | V <sub>BAT</sub> Voltage                                       | e Rising                                           | 2.7    | 2.85              | 3.00  | V    |  |

| Precondition Threshold<br>Hysteresis | V <sub>HYS(PRECHG)</sub> | V <sub>BAT</sub> Voltage Falling                               |                                                    |        | 150               | 220   | mV   |  |

| End-of Charge Current                |                          |                                                                | ACIN = G                                           |        | 4                 |       |      |  |

| Threshold                            | I <sub>EOC</sub>         | $V_{BAT} = 4.2V$                                               | ACIN = SYS                                         |        | 10                |       | %    |  |

| Sleep-Mode Entry Threshold           | V <sub>SLPENT</sub>      |                                                                |                                                    |        | 150               | 250   | mV   |  |

| Sleep-Mode Exit Threshold            | V <sub>SLPEXIT</sub>     |                                                                |                                                    |        | 50                | 150   | mV   |  |

| Charge Restart Threshold             | $V_{RCH}$                | V <sub>SYS</sub> – V <sub>BAT</sub> , V <sub>BAT</sub> Falling |                                                    | 150    | 175               | 200   | mV   |  |

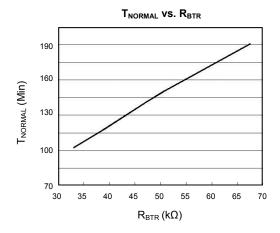

| Fast Charge Safety Timer             | T <sub>NORMAL</sub>      | $R_{BTR} = 62k\Omega$                                          |                                                    |        | 3                 |       | hr   |  |

| Precondition Safety Timer            | $T_PRE$                  | $R_{BTR} = 62k\Omega$                                          |                                                    | _      | 1®                |       | hr   |  |

### **ELECTRICAL CHARACTERISTICS CONT'D**

$(V_{CHG\_IN} = 5.0V, \, R_{ISET} = 1 k\Omega, \, R_{BTR} = 62 k\Omega, \, R_{DCCC} = 18.7 k\Omega, \, T_A = 25^{\circ}C, \, unless \, otherwise \, specified.)$

| PARAMETER                                              | SYMBOL                 | TEST CONDITIONS                                                                               | MIN   | TYP   | MAX   | UNIT     |

|--------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------|-------|-------|-------|----------|

| Temperature Sense Comparator                           | r                      |                                                                                               |       |       |       |          |

| TH Pull-Up Current                                     | I <sub>TH</sub>        | $V_{CHG_IN} > V_{BAT} + 200 \text{mV}$                                                        | 92    | 100   | 108   | μΑ       |

| V <sub>TH</sub> Upper Temperature Voltage Threshold    | $V_{THH}$              | Down-going, simulate a NTC going hotter                                                       | 0.475 | 0.505 | 0.535 | <b>V</b> |

| V <sub>TH</sub> Lower Temperature Voltage<br>Threshold | V <sub>THL</sub>       | Up-going, simulate a NTC going colder                                                         | 2.440 | 2.510 | 2.580 | ٧        |

| V <sub>TH</sub> Hysteresis                             | $V_{HYS}$              |                                                                                               |       | 30    | 45    | mV       |

| EN, ACIN and CHGLEV Inputs                             |                        |                                                                                               |       |       |       |          |

| EN, ACIN, CHGLEV Pin Logic<br>High Input Voltage       | V <sub>IH</sub>        |                                                                                               | 1.4   |       |       | V        |

| EN, ACIN, CHGLEV Pin Logic<br>Low Input Voltage        | V <sub>IL</sub>        |                                                                                               |       |       | 0.4   | ٧        |

| EN Pin Logic Leakage Current                           | I <sub>LKG1</sub>      | V <sub>CHG_IN</sub> = 4.2V, EN = SYS                                                          |       |       | 1     | μΑ       |

| nSTAT1, nSTAT2, nSTAT3, nAC                            | OK, nBLV1,             | nBLV2 Outputs                                                                                 |       |       |       |          |

| Sink Current                                           | I <sub>nSTATx</sub>    | nSTAT1, nSTAT2                                                                                | 4     | 6     | 8     | mA       |

| Output Low Voltage                                     | V <sub>OL</sub>        | nSTAT1, nSTAT2, nSTAT3, nACOK,<br>I <sub>sink</sub> = 1mA                                     |       |       | 0.5   | ٧        |

|                                                        | $V_{LOL}$              | nBLV1, nBLV2, I <sub>nBLVx</sub> = 2mA                                                        |       |       | 0.3   | V        |

| Leakage Current                                        | I <sub>LKG2</sub>      | nSTAT1, nSTAT2, nSTAT3, nACOK,<br>nBLV1, nBLV2, V <sub>nSTATx</sub> = V <sub>nACOK</sub> = 5V |       |       | 1     | μΑ       |

| Thermal Shutdown Regulation                            |                        |                                                                                               |       |       |       |          |

| Thermal Regulation Threshold                           | $T_TRH$                |                                                                                               |       | 110   |       | °C       |

| Thermal Shutdown Temperature                           | T <sub>SHTD</sub>      | Temperature Rising                                                                            |       | 160   |       | °C       |

| Thermal Shutdown Hysteresis                            | T <sub>HYS(SHTD)</sub> | Temperature Falling                                                                           |       | 25    |       | °C       |

①: Charge current is min of 90mA or ISET

②: Charge current is min of 450mA or ISET

③: ISET (mA) = 495 / ( $R_{ISET}(k\Omega)$  - 0.036)

<sup>4:</sup> T<sub>PRECONDITION</sub> = T<sub>NORMAL</sub> / 3 (typ)

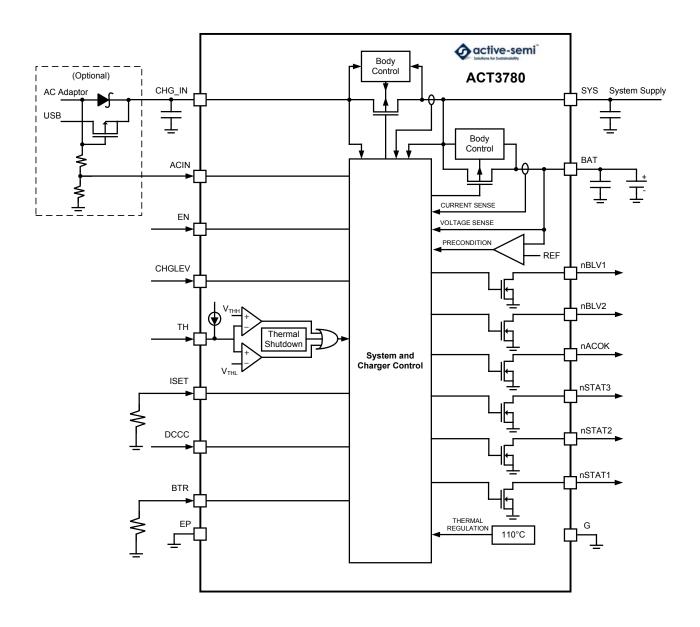

### **FUNCTIONAL BLOCK DIAGRAM**

### **FUNCTIONAL DESCRIPTION**

The ACT3780 is a complete battery-charging and system power management solution for portable hand-held equipment using single-cell Lithium-based batteries. The ACT3780 incorporates Active-Semi's patent-pending *ActivePath* architecture which automatically selects the best available input supply for the system, and additionally features a complete, high-accuracy (±0.5%), thermally regulated, Full-Featured single cell linear Li+charger with an integrated 12V power MOSFET.

#### ActivePath Architecture

Active-semi's proprietary *ActivePath* architecture performs three important functions:

### System Configuration Optimization

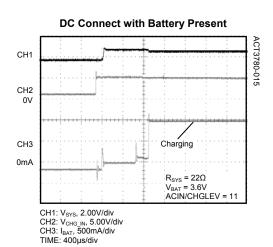

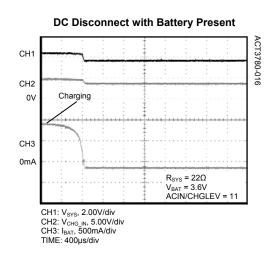

Depending upon the state of the input supply, ActivePath automatically optimizes the power system configuration. If the input supply is present, ActivePath powers the system in parallel with the battery, so that both system power and charge current can be independently managed to ensure that system power requirements are satisfied, the battery can charge as quickly as possible, and to ensure that the total system current does not exceed the capability of the input supply. If the input supply is not present, then ActivePath automatically configures the system to draw power from the battery. Finally, if the system current requirement exceeds the capability of the input supply, ActivePath automatically configures the battery to support the load in parallel with the input supply, to ensure maximum supply capability to the load under peak-power consumption conditions.

#### Input MOSFET Power (Q1)

At the input of the ACT3780's *ActivePath* circuit is Q1, an integrated 12V power MOSFET. Q1 is part of an internal low-dropout linear regulator that regulates the system voltage (V<sub>SYS</sub>) to 4.6V, protecting the system from high-voltage input supplies. Q1 includes several features that can be used to limit the total current drawn from the input supply.

ACIN's current limit is determined primarily by the ACIN input, Q1 operates in "AC-Mode" when ACIN is driven to a logic-high, and Q1 operates in "USB-Mode" when driven to a logic-low. When operating in "AC-Mode", Q1's internal current limit is programmed to 2.5A. When operating in "USB-Mode", Q1's current limit is set to either 450mA,

when CHGLEV is driven to a logic-high, or to 90mA, when CHGLEV is driven to a logic-low. This functionality provides simple means of implementing a solution that operates within the current-capability limitations of the USB port while taking advantage of the high output current capability of AC adapters. For more information about the ACIN input, see the ACIN and CHGLEV Inputs section.

#### **Dual-Function MOSFET (Q2)**

Q2 is a dual-function power MOSFET, that serves both as a low-resistance ( $50m\Omega$ ) switch that supplies the load current requirements of the system from the battery when no input supply is present or the system demands more current than the input can provide.

# **Current-Limits and Charge-Current Programming**

ACT3780 provides a flexible current programming scheme that combines the convenience of internal charge current programming with the flexibility of resistor-based charge current programming. Current limits and charge current programming are managed as a function of the ACIN and CHGLEV pins, in combination with  $R_{\rm ISET},$  the resistance connected to the ISET pin.

#### **ACIN and CHGLEV Inputs**

ACIN is a logic input that configures the current-limit of input transistor (Q1) as well as that of the battery charger. ACIN features an logic input threshold, so that the input voltage detection threshold may be adjusted with a simple resistive voltage divider. This input also allows a simple, low-cost dual-input charger switch to be implemented with just a few, low-cost components. As shown in the Functional Block Diagram.

When ACIN is driven to a logic high, the *ActivePath* operates in "AC-Mode" and the charger charges at the current programmed by  $R_{\text{ISET}}$ ,

ISET(mA) = 495 / (

$$R_{ISET}(k\Omega) - 0.036$$

) (1)

When ACIN is driven to a logic-low, the *ActivePath* circuitry operates in "USB-Mode", which enforces a maximum charge current setting of 450mA, if CHGLEV is driven to a logic-high, or 90mA, if CHGLEV is driven to a logic-low.

The ACT3780's charge current settings are summarized in the table below:

Table 1: ACIN and CHGLEV Inputs Table

| ACIN | CHGLEV | Fast Charge Current                               |

|------|--------|---------------------------------------------------|

| High | High   | ISET (mA) = 495 / ( $R_{ISET}(k\Omega) - 0.036$ ) |

| High | Low    | 0.5 × ISET                                        |

| Low  | High   | Min (450mA, ISET )                                |

| Low  | Low    | Min (90mA, ISET )                                 |

Note that the actual charging current may be limited to a current that is lower than the programmed fast-charge current due to the ACT3780's internal thermal regulation loop. See the *Thermal Regulation and Protection* section for more information.

### **Dynamic Charge Current Control (DCCC)**

The ACT3780's *ActivePath* Charger features Dynamic Charge Current Control (DCCC) circuitry, which continuously monitors the input supply to prevent input overload conditions. DCCC reduces the charge current when the SYS voltage decreases to  $V_{\rm DCCC}$  and stops charging when SYS drops below  $V_{\rm DCCC}$  by 1.5% (typical).

The DCCC voltage threshold is programmed by connecting a resistor from DCCC to GA according to the following equation:

$$V_{DCCC} = 2 \times (I_{DCCC} \times R_{DCCC}) \tag{2}$$

Where  $R_{DCCC}$  is the value of the external resistor, and  $I_{DCCC}$  (100 $\mu$ A typical) is the value of the current sourced from DCCC.

Given the tolerances of the  $R_{DCCC}$  and  $I_{DCCC}$ , the DCCC voltage threshold should be programmed to be no less than 3.3V to prevent triggering the UVLO, and to be no larger than 4.4V to prevent engaging DCCC prematurely. A 19.1k (1%), or 18.7k (1%) resistor for  $R_{DCCC}$  is recommended.

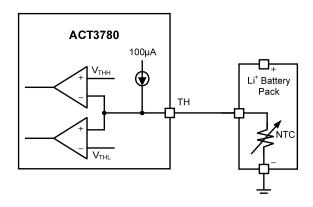

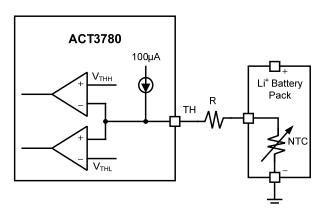

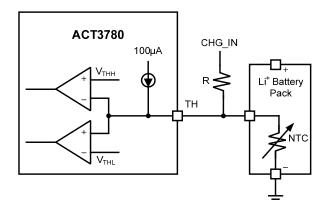

### **Battery Temperature Monitoring**

The ACT3780 continuously monitors the temperature of the battery pack by sensing the resistance of its thermistor, and suspends charging if the temperature of the battery pack exceeds the safety limits.

In a typical application, shown in Figure 1, the TH pin is connected to the battery pack's thermistor input. The ACT3780 injects a  $100\mu A$  current out of the TH pin into the thermistor, so that the thermistor

resistance is monitored by comparing the voltage at TH to the internal  $V_{THH}$  and  $V_{THL}$  thresholds of 0.5V and 2.5V, respectively. When  $V_{TH} > V_{THL}$  or  $V_{TH} < V_{THH}$  charging and the charge timers are suspended. When  $V_{TH}$  returns to the normal range, charging and the charge timers resume.

The net resistance from TH to G required to cross the threshold is given by:

100μA ×

$$R_{NOM}$$

×  $k_{HOT}$  = 0.5V  $\rightarrow$   $R_{NOM}$  ×  $k_{HOT}$  = 5kΩ

$$100\mu$$

A × R<sub>NOM</sub> × k<sub>COLD</sub> =  $2.5$ V  $\rightarrow$  R<sub>NOM</sub> × k<sub>COLD</sub> =  $25$ kΩ

where  $R_{\text{NOM}}$  is the nominal thermistor resistance at room temperature, and  $k_{\text{HOT}}$  and  $k_{\text{COLD}}$  are the ratios of the thermistor's resistance at the desired hot and cold thresholds, respectively.

Figure 1: Simple Configuration

### **Design Procedure**

When designing with thermistors it is important to keep in mind that their nonlinear behavior typically allows one to directly control no more than one threshold at a time. As a result, the design procedure can change depending on which threshold is most critical for a given application.

Most application requirements can be solved using one of three cases,

- 1) Simple solution

- 2) Fix  $V_{THH}$ , accept the resulting  $V_{THL}$

- 3) Fix  $V_{THL}$ , accept the resulting  $V_{THH}$

The ACT3780 was designed to achieve an operating temperature range that is suitable for most applications with very little design effort. The simple solution is often found to provide reasonable results and should always be used first, then the design procedure may proceed to one of the other solutions if necessary.

In each design example, we refer to the Vishay NTHS series of NTCs, and more specifically those which follow a "curve 2" characteristic. For more information on these NTCs, as well as access to the resistance/temperature characteristic tables referred to in the example, please refer to the Vishay website at http://www.vishay.com/thermistors.

#### Simple Solution

The ACT3780 was designed to accommodate most requirements with very little design effort, but also provides flexibility when additional control over a design is required. Initial thermistor selection is accomplished by choosing one that best meets the following requirements:

$R_{NOM} = 5k\Omega/k_{HOT}$ , and

$R_{NOM} = 25k\Omega/k_{COLD}$

where  $k_{\text{HOT}}$  and  $k_{\text{COLD}}$  for a given thermistor can be found on its characteristic tables.

Taking a 0°C to 40°C application using a "curve 2" NTC for this example, from the characteristic tables one finds that  $k_{HOT}$  and  $k_{COLD}$  are 0.5758 and 2.816, respectively, and the  $R_{NOM}$  that most closely satisfies these requirements is therefore around 8.8k $\Omega$ . Selecting 10k $\Omega$  as the nearest standard value, calculate  $k_{COLD}$  and  $k_{HOT}$  as:

$$\begin{split} k_{COLD} &= V_{THL}/(I_{TH} \times R_{NOM}) = 2.5 V/(100 \mu A \times 10 k \Omega) = 2.5 \\ k_{HOT} &= V_{THH}/(I_{TH} \times R_{NOM}) = 0.5 V/(100 \mu A \times 10 k \Omega) = 0.5 \end{split}$$

Identifying these values on the curve 2 characteristic tables indicates that the resulting operating temperature range is 2°C to 44°C, vs. the design goal of 0°C to 40°C. This example demonstrates that one can satisfy common operating temperature ranges with very little design effort.

For demonstration purposes, supposing that we had selected the next closest standard thermistor value of  $6.8k\Omega$  in the example above, we would have obtained the following results:

$$k_{COLD} = V_{THL}/(I_{TH} \times R_{NOM}) = 2.5V/(100 \mu A \times 6.8 k\Omega) = 3.67$$

$$k_{HOT} = V_{THH}/(I_{TH} \times R_{NOM}) = 0.5V/(100\mu A \times 6.8k\Omega) = 0.74$$

which, according to the characteristic tables would have resulted in an operating temperature range of -6°C to 33°C vs. the design goal of 0°C to 40°C.

In this case, one can add resistance in series with the thermistor to shift the range upwards, using the following equation:

$$(V_{THH}/I_{TH}) = k_{HOT} (@40^{\circ}C) \times R_{NOM} + R$$

$$R = (V_{THH}/I_{TH}) - k_{HOT} (@40^{\circ}C) \times R_{NOM}$$

$$R = (0.5V/100\mu A) - 0.5758 \times 6.8k\Omega$$

Finally,

$$R = 5k\Omega - 3.9k\Omega = 1.1k\Omega$$

This result shows that adding  $1.1k\Omega$  in series with the thermistor sets the net resistance from TH to G to be 0.5V at 40°C, satisfying  $V_{THH}$  at the correct temperature. Adding this resistance, however, also impacts the lower temperature limit as follows:

$$V_{THL}/I_{TH} = k_{COLD}(@TC) \times R_{NOM} + R$$

$$k_{COLD}(@TC) = (V_{THL}/I_{TH} - R)/R_{NOM}$$

Finally,

$$k_{COLD}(@TC) = (25k\Omega - 1.1k\Omega)/6.8k\Omega = 3.51$$

Reviewing the characteristic curves, the lower threshold is found to move to -5°C, a change of only 1°C. As a result, the system satisfies the upper threshold of 40°C with an operating temperature range of -5°C to 40°C, vs. our design target of 0°C to 40°C. It is informative to highlight that due to the NTC behavior of the thermistor, the relative impact on the lower threshold is significantly smaller than the impact on the upper threshold.

#### Fix V<sub>THH</sub>

Following the same example as above, the "unadjusted" results yield an operating temperature range of -6°C to 33°C vs. the design goal of 0°C to 40°C. In applications that favor  $V_{THH}$  over  $V_{THL}$ , however, one can control the voltage present at TH at low temperatures by connecting a resistor in parallel with  $I_{TH}$ . The desired resistance can be found using the following equation:

$$(I_{TH} + (V_{CHG IN} - V_{THL})/R) \times k_{COLD} @0^{\circ}C) \times R_{NOM} = V_{THL}$$

Rearranging yields

$$R = (V_{CHG\_IN} - V_{THL})/(V_{THL}/(k_{COLD}(@0^{\circ}C) \times R_{NOM}) - I_{TH})$$

$$R = (5V - 2.5V)/(2.5V/(2.816 \times 6.8k\Omega) - 100\mu A)$$

$$R = 82k\Omega$$

Adding  $82k\Omega$  in parallel with the current source increases the net current flowing into the thermistor, thus increasing the voltage at TH. Adding this resistance, however, also impacts the upper temperature limit:

$$V_{THH} = (I_{TH} + (V_{CHG\_IN} - V_{THH})/R) \times k_{HOT} (@40^{\circ}C) \times R_{NOM}$$

Rearranging yields,

$k_{HOT}(@TC) = V_{THH}/(R_{NOM} \times (I_{TH} + (V_{CHG} I_{N} - V_{THH})/R))$

$k_{HOT}(@TC) = 0.5V/(6.8k\Omega \times (100\mu A + (5V - 0.5V)/82k\Omega))$ = 0.4748

Reviewing the characteristic curves, the upper threshold is found to move to 45°C, a change of about 14°C. Adding the parallel resistance has allowed us to achieve our desired lower threshold of 0°C with an operating temperature range of 0°C to 45°C, vs. our design target of 0°C to 40°C.

### Thermal Regulation and Protection

The ACT3780 features an internal thermal regulation loop that reduces the charging current as necessary to ensure that the die temperature does not rise beyond the thermal regulation threshold of 110°C. This feature protects the ACT3780 against excessive junction temperature and makes the device more accommodating to aggressive thermal designs. Note, however, that attention to good thermal designs is required to achieve the fastest possible charge time by maximizing charge current. In order to account for the extended total charge time resulting from operation in thermal regulation mode, the charge timeout periods are extended proportionally to the reduction in charge current. The conditions that cause the ACT3780 to reduce charge current in accordance to the internal thermal regulation loop can be approximated by calculating the power dissipated in the part.

The ACT3780 also features thermal shutdown for further protection. When the device temperature exceeds 160°C, the device will automatically turn off to prevent the IC from damage. After the die temperature decreases below 135°C, the IC will automatically restart.

### **Charging Safety Timers**

The ACT3780 features a programmable safety charging timer by setting an external resistor from BTR pin to G  $(R_{BTR})$ . The time out period is calculated as shown in Figure 2. The maximum  $R_{\text{BTR}}$ should not be larger than  $68k\Omega$ .

If the timeout period expires without change termination, the ACT3780 will jump to EOC state.

If the ACT3780 detects that the charger remains in precondition for longer than the precondition time out period (which determined as T<sub>NORMAL</sub>/3), the ACT3780 turns off the charger and generates a FAULT to ensure prevent charging a bad cell.

Figure 2:

Figure 3: Fix V<sub>THL</sub> Configuration

Figure 4: Fix V<sub>THH</sub> Configuration

### **Charging Status Indication**

The ACT3780 provides nSTAT1 and nSTAT2 Outputs to indicate the Charging Status of the charger. These are two open-drain outputs which sink current went asserted and high-Z otherwise. These outputs have internal 6mA current limits, and are capable of directly driving LEDs, without the need of current-limiting resistors or other external circuitry, for a visual charge-status indication. To drive an LED, simply connect the LED between each pin and an appropriate supply (typically V<sub>SYS</sub>). For a logic level indication, simply connect a resistor from each output to a appropriate voltage supply. For more details, see table 2 for LED indication:

Table 2: Charging Status Indication Table

| STATE           | nSTAT1 | nSTAT2 |

|-----------------|--------|--------|

| Precondition    | Low    | Low    |

| Fast Charge     | Low    | High   |

| Charge Complete | High   | High   |

| Disabled        | High   | High   |

| Input Floating  | High   | High   |

| Fault           | High   | High   |

### **Battery Voltage Level Indication**

When the battery is being charged, the ACT3780 senses VBAT and features nBLV1 and nBLV2 as two battery voltage level indicator outputs. These are two open-drain outputs which sink current whenever asserted. For logic level indication, simply connect a resistor from each output to an appropriate voltage supply. See below table 3 for more information:

Table 3:

Battery Voltage Level Indication Table

| V <sub>BAT</sub> STATE    | nBLV2 | nBLV1 |

|---------------------------|-------|-------|

| V <sub>BAT</sub> < 2.8V   | Low   | Low   |

| $2.8V \le V_{BAT} < 3.6V$ | Low   | High  |

| $3.6V \le V_{BAT} < 4V$   | High  | Low   |

| 4V ≤ V <sub>BAT</sub>     | High  | High  |

### nACOK Output

The ACT3780's nACOK output provides a logic-level indication of the status of the voltage at CHG\_IN. nACOK is an open-drain output which sinks current when a valid input is applied to CHG\_IN.

#### Table 4:

#### **nACOK Output Table**

| CHG_IN Voltage                                          | nACOK | nSTAT3 |

|---------------------------------------------------------|-------|--------|

| $V_{\text{UVLO}} < V_{\text{CHG\_IN}} < V_{\text{OVP}}$ | Low   | Х      |

| $V_{CHG\_IN} > V_{OVP}$                                 | High  | Low    |

| $V_{CHG\_IN} < V_{UVLO}$                                | High  | High   |

### **Over Voltage Protection (OVP)**

The ACT3780 provides over voltage protection function. When the ACT3780 detects the voltage at CHG\_IN pin is greater than 6.9V, it automatically turns off the Q1 Power FET and turns on the Q2 to supply the system load from the battery.

### nSTAT3 Output

The ACT3780's nSTAT3 output provide a logic level indication of OVP. This is an open-drain Output which sinks current whenever  $V_{\text{CHG\_IN}}$  is greater than 6.9V.

### **Enable/Disable Input**

The ACT3780's EN is used to enable the IC. Driving this pin to a logic high enables the ACT3780. Driving EN pin to a logic low forces the device to enter suspend mode. In suspend mode, if a valid input is present at CHG\_IN pin, Q1 is turned off. And the system is powered by the battery via Q2. This feature is designed to limit the power drawn from the input supply (such as USB in suspend mode).

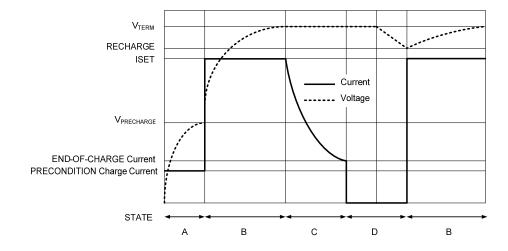

### **CC/CV Regulation Loop**

At the core of the ACT3780's battery charger is a CC/CV regulation loop, which regulates either current or voltage as necessary to ensure fast and safe charging of the battery. In a normal charge cycle, this loop regulates the current to the value set by the external resistor at the ISET pin. Charging continues at this current until the battery cell voltage reaches the termination voltage (default is 4.2V or 4.1V). At this point the CV loop takes over, and charge current is allowed to decrease as necessary to maintain charging at the termination voltage.

### **Enable/Disable Charging**

The ACT3780's DCCC pin can be used to disable charging. By floating the DCCC pin, the charger will be disabled.

Figure 5:

Typical Li+ Charge Profile and ACT3780 Charge States

A: PRECONDITION State B: FAST-CHARGE State C: TOP-OFF State

D: END-OF-CHARGE State

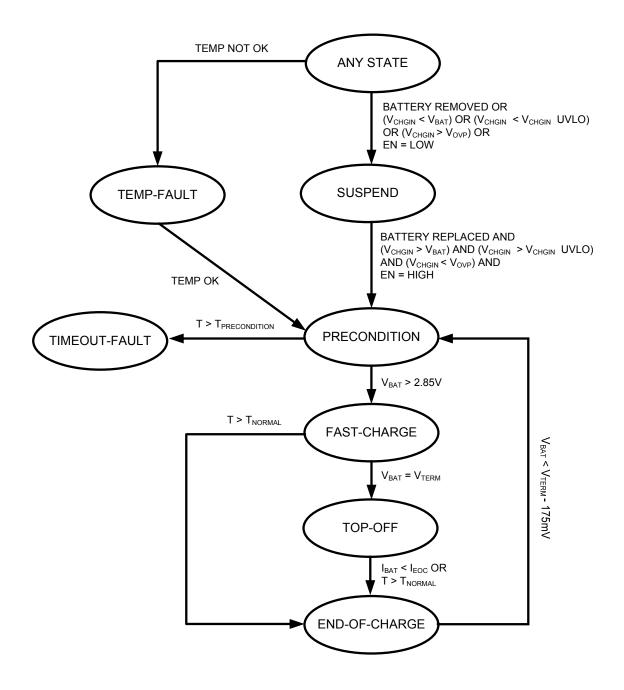

### **Charger State-Machine**

#### **PRECONDITION State**

new charging cycle begins with the PRECONDITION state, and operation continues in this state until  $V_{BAT}$  exceeds the Precondition Threshold Voltage of 2.85V (typ). When operating in PRECONDITION state, the cell is charged at a reduced current, 10% of the programmed maximum fast-charge constant current, ISET. Once V<sub>BAT</sub> reaches the Precondition Threshold Voltage the state machine jumps to the FAST-CHARGE state. If V<sub>BAT</sub> does not reach the Precondition Threshold Voltage before the Precondition Timeout period T<sub>PRECONDITION</sub> expires, then a damaged cell is detected and the state machine jumps to the TIMEOUT- FAULT State. For the Precondition Timeout period, see the Charging Safety Timers section for more information.

#### **FAST-CHARGE State**

In FAST-CHARGE state, the ACT3780 charges at the current programmed by RISET (see the *Current Limits* and *Charge Current Programming* section for more information). During a normal charge cycle fast-charge continues in CC mode until VBAT reaches the charge termination voltage (VTERM), at which point the ACT3780 charges in TOP-OFF state. If VBAT does not proceed out of the FAST-CHARGE state before the Normal Timeout period (TNORMAL) expires, then the state machine jumps to the END-OF-CHARGE state and will re-initiate a new charge cycle after 2-4ms "relax".

#### TOP-OFF State

In the TOP-OFF state, the cell is charged in constant-voltage (CV) mode. Charge current decreases as charging continues. During a normal charging cycle charging proceeds until the charge current decreases below the END-OF-CHARGE (EOC) threshold, defined as 10% of ISET (ACIN = 1) or 4% of ISET (ACIN = 0) . When this happens, the state-machine terminates the charge cycle and jumps to the EOC state. If the state-machine does not jump out of the TOP-OFF state before the Total-Charge Timeout period expires, the state machine jumps to the EOC state and will re-initiate a new charge cycle when  $V_{BAT}$  falls 175 mV(typ) below the charge termination voltage.

### **END-OF-CHARGE State**

In the END-OF-CHARGE (EOC) state, the ACT3780 presents a high-impedance to the battery, allowing the cell to "relax" and minimizes battery leakage current. The ACT3780 continues to monitor the cell voltage, however, so that it can re-initiate charging cycles when VBAT falls 175mV(typ) below the charge termination voltage.

#### SUSPEND State

The ACT3780 features an user-selectable suspend charge mode, which disables the charger but keeps other circuiting functional. The charger can be put into suspend mode by driving EN to logic low. Upon exiting the SUSPEND State, the charge timer is reset and the state machine jumps to PRECONDITION state.

Figure 6: Charger State Diagram

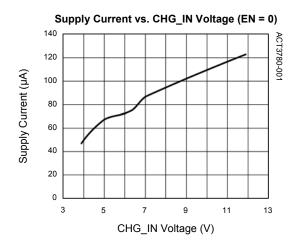

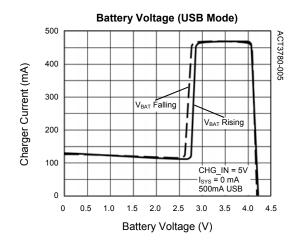

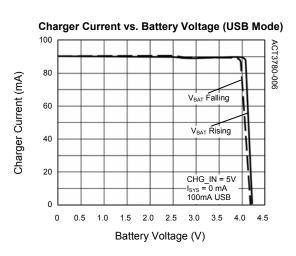

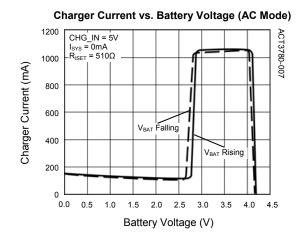

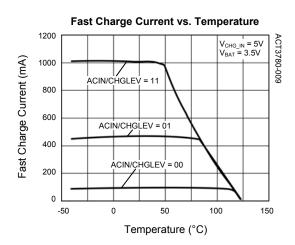

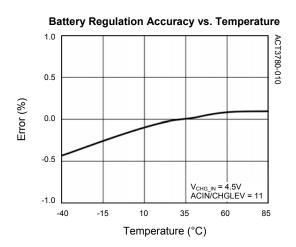

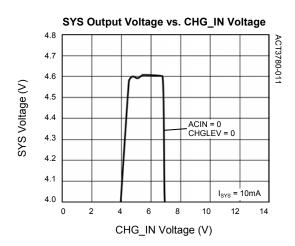

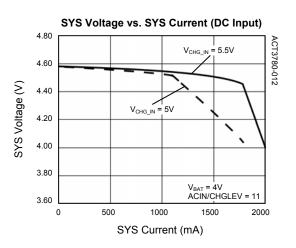

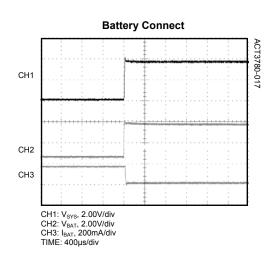

$(V_{CHG\_IN} = 5V, R_{DCCC} = 18.7k\Omega, T_A = 25^{\circ}C, unless otherwise specified.)$

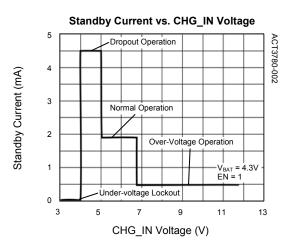

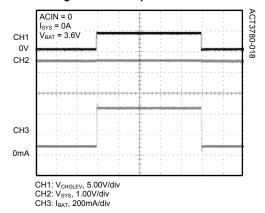

$(V_{CHG\_IN} = 5V, R_{DCCC} = 18.7k\Omega, T_A = 25^{\circ}C, unless otherwise specified.)$

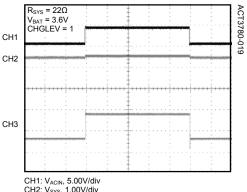

$(V_{CHG\_IN} = 5V, R_{DCCC} = 18.7k\Omega, T_A = 25^{\circ}C, unless otherwise specified.)$

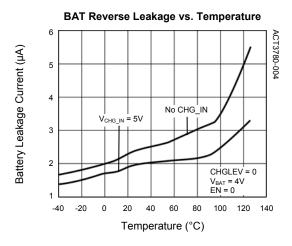

$(V_{CHG\_IN} = 5V, R_{DCCC} = 18.7k\Omega, T_A = 25^{\circ}C, unless otherwise specified.)$

### Charge Current Response vs. CHGLEV

#### Charge Current Response vs. ACIN

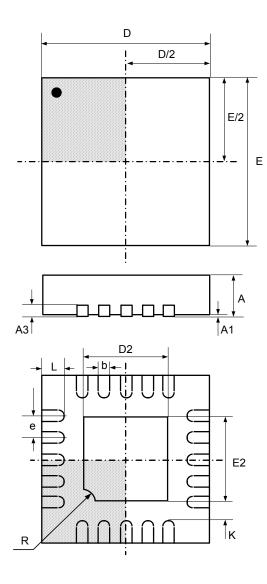

### **PACKAGE OUTLINE**

### **TQFN44-20 PACKAGE OUTLINE AND DIMENSIONS**

| SYMBOL |           | SION IN<br>ETERS | DIMENSION IN INCHES |       |  |

|--------|-----------|------------------|---------------------|-------|--|

|        | MIN       | MAX              | MIN                 | MAX   |  |

| Α      | 0.700     | 0.800            | 0.028               | 0.031 |  |

| A1     | 0.000     | 0.050            | 0.000               | 0.002 |  |

| A3     | 0.200     | REF              | 0.008               | REF   |  |

| b      | 0.180     | 0.300            | 0.039               | 0.012 |  |

| D      | 3.900     | 4.100            | 0.154               | 0.161 |  |

| E      | 3.900     | 4.100            | 0.154               | 0.161 |  |

| D2     | 2.550     | 2.80             | 0.090               | 0.100 |  |

| E2     | 2.550     | 2.80             | 0.090               | 0.100 |  |

| е      | 0.500 BSC |                  | 0.020 BSC           |       |  |

| L      | 0.300     | 0.500            | 0.012               | 0.020 |  |

| R      | 0.200 TYP |                  | 0.008               | TYP   |  |

| K      | 0.200     |                  | 0.008               |       |  |

Active-Semi, Inc. reserves the right to modify the circuitry or specifications without notice. Users should evaluate each product to make sure that it is suitable for their applications. Active-Semi products are not intended or authorized for use as critical components in life-support devices or systems. Active-Semi, Inc. does not assume any liability arising out of the use of any product or circuit described in this datasheet, nor does it convey any patent license.

Active-Semi and its logo are trademarks of Active-Semi, Inc. For more information on this and other products, contact sales @active-semi.com or visit <a href="http://www.active-semi.com">http://www.active-semi.com</a>.

**Ogactive-semi** is a registered trademark of Active-Semi.