# **TABLE OF CONTENTS**

| Features                                                   | . 1 |

|------------------------------------------------------------|-----|

| Applications                                               | . 1 |

| General Description                                        | . 1 |

| Functional Block Diagram                                   | . 1 |

| Revision History                                           | . 2 |

| Specifications                                             |     |

| Absolute Maximum Ratings                                   |     |

| Thermal Resistance                                         |     |

| ESD Caution                                                |     |

| Pin Configuration and Function Descriptions                |     |

| Typical Performance Characteristics                        |     |

|                                                            |     |

| I/Q Mode                                                   |     |

| IF Mode                                                    |     |

| Output Detector Performance                                |     |

| Return Loss                                                | 20  |

| Theory of Operation                                        | 21  |

| Baseband                                                   | 21  |

| Single Sideband (SSB) Upconversion                         | 21  |

| LO Input Path                                              | 21  |

| Serial Port Interface (SPI)                                | 21  |

| Applications Information                                   |     |

|                                                            |     |

| REVISION HISTORY                                           |     |

| 1/2019—Rev. C to Rev. D                                    |     |

| Changes to ADC Section                                     | 23  |

| 7/2018—Rev. B to Rev. C                                    |     |

| Changed 32.95 to 9.18 in $\theta_{JA}$ Column, Table 3     | . 6 |

| Changes to Ordering Guide                                  |     |

| 10/2017—Rev. A to Rev. B                                   |     |

| Changes to Maximum Junction Temperature Parameter, Table 2 | 6   |

| Change to Table 4                                          |     |

| Changes to Figure 31 Caption                               |     |

| Changes to Ordering Guide                                  |     |

| 5/2016—Rev. 0 to Rev. A                                    |     |

| Change to Table 4                                          | . 7 |

| Changes to Figure 40                                       |     |

| Changes to Figure 47                                       |     |

| Changes to Figure 58                                       |     |

| Change to Figure 84                                        |     |

| Changes to Table 16                                        | 34  |

| Carrier Feedthrough Nulling                   | 3 |

|-----------------------------------------------|---|

| Sideband Suppression Optimization             | 3 |

| Linearity2                                    | 3 |

| ADC2                                          | 3 |

| Wide Frequency Performance                    | 4 |

| Layout2                                       | 4 |

| LO Input Driven Differential vs. Single Ended | 5 |

| Register Summary                              | 7 |

| Register Details: Wideband Upconverter        | 8 |

| Control Register2                             | 8 |

| ALARM_READBACK Register2                      | 8 |

| ALARM_MASK Register2                          | 9 |

| Enable Register                               | 9 |

| Linearize Register3                           | 0 |

| LO_PATH Register3                             | 0 |

| ADC_CONTROL Register 3                        | 1 |

| ADC_OUTPUT Register3                          | 1 |

| Basic Connections for Operation               | 2 |

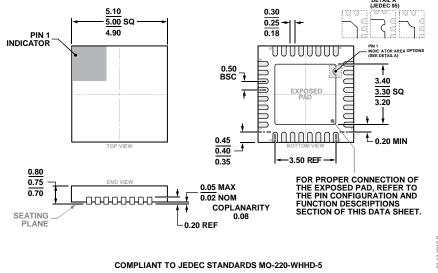

| Outline Dimensions                            | 5 |

| Ordering Guide                                | 5 |

3/2016—Revision 0: Initial Version

# **SPECIFICATIONS**

VPBB = VPBI = VPLO = 3.3 V, VP18 = 1.8 V, VPDT = VPRF = 5 V,  $T_A$  = 25°C, LO = 0 dBm differential drive; baseband I/Q amplitude = -15 dBm differential sine waves in quadrature with a 500 mV dc bias, baseband input termination with 100  $\Omega$  externally, IF amplitude = -12 dBm differential sine waves, unless otherwise noted.

## Table 1.

| Parameter                                      | Test Conditions/Comments                                                                                                                             | Min | Тур  | Max  | Unit   |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|------|--------|

| RF OUTPUT FREQUENCY RANGE                      |                                                                                                                                                      | 5.9 |      | 23.6 | GHz    |

| LOCAL OSCILLATOR (LO) INPUT<br>FREQUENCY RANGE |                                                                                                                                                      | 5.4 |      | 14   | GHz    |

| LO AMPLITUDE RANGE                             |                                                                                                                                                      | -6  | 0    | +6   | dBm    |

| IF INPUT FREQUENCY RANGE                       |                                                                                                                                                      | 0.8 |      | 3.5  | GHz    |

| BASEBAND (BB) I/Q INPUT FREQUENCY<br>RANGE     |                                                                                                                                                      | DC  |      | 750  | MHz    |

| I/Q MODULATOR PERFORMANCE                      |                                                                                                                                                      |     |      |      |        |

| Modulator Voltage Gain                         | Maximum gain at maximum gain setting                                                                                                                 | 10  | 13   |      | dB     |

|                                                | Minimum gain at minimum gain setting                                                                                                                 |     | -12  |      | dB     |

| Output Noise Density                           | Output carrier > -5 dBm                                                                                                                              |     | -147 |      | dBc/Hz |

|                                                | Output carrier > -14 dBm                                                                                                                             |     | -145 |      | dBc/Hz |

|                                                | Output carrier > -22.5 dBm                                                                                                                           |     | -136 |      | dBc/Hz |

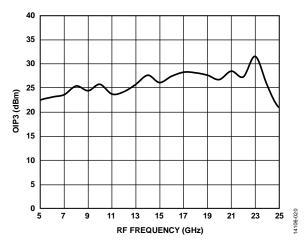

| Output Third-Order Intercept (OIP3)            | $f_1BB = 10$ MHz, $f_2BB = 12$ MHz, baseband I/Q amplitude per tone = $-15$ dBm sine waves in quadrature with a 500 mV dc bias, 10 dB gain setting   |     |      |      |        |

| 5.9 GHz to 10 GHz                              |                                                                                                                                                      |     | 24   |      | dBm    |

| 10 GHz to 14 GHz                               |                                                                                                                                                      |     | 25   |      | dBm    |

| 14 GHz to 20 GHz                               |                                                                                                                                                      |     | 27   |      | dBm    |

| 20 GHz to 23.6 GHz                             |                                                                                                                                                      |     | 27   |      | dBm    |

| Fifth-Order Intermodulation Distortion (IMD5)  | $f_1$ BB = 10 MHz, $f_2$ BB = 12 MHz, baseband I/Q amplitude per tone = $-15$ dBm sine waves in quadrature with a 500 mV dc bias, 10 dB gain setting |     | 65   |      | dBm    |

| Output Second-Order Intercept (OIP2)           | $f_1$ BB = 10 MHz, $f_2$ BB = 12 MHz, baseband I/Q amplitude per tone = $-15$ dBm sine waves in quadrature with a 500 mV dc bias, 10 dB gain setting |     |      |      |        |

| 5.9 GHz to 10 GHz                              |                                                                                                                                                      |     | 65   |      | dBm    |

| 10 GHz to 14 GHz                               |                                                                                                                                                      |     | 65   |      | dBm    |

| 14 GHz to 20 GHz                               |                                                                                                                                                      |     | 66   |      | dBm    |

| 20 GHz to 23.6 GHz                             |                                                                                                                                                      |     | 50   |      | dBm    |

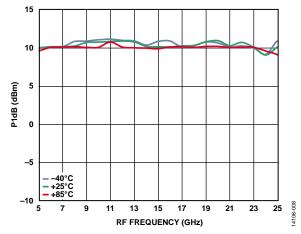

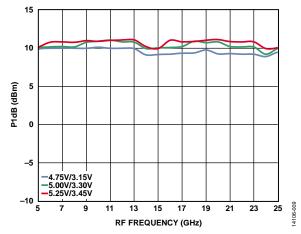

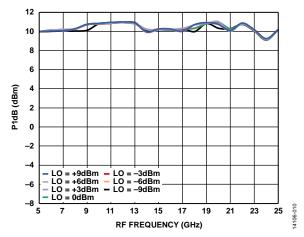

| Output 1 dB Compression Point (P1dB)           |                                                                                                                                                      |     |      |      |        |

| 5.9 GHz to 10 GHz                              | At 10 dB gain setting                                                                                                                                |     | 10.5 |      | dBm    |

|                                                | At maximum gain setting                                                                                                                              |     | 11   |      | dBm    |

| 10 GHz to 14 GHz                               | At 10 dB gain setting                                                                                                                                |     | 11   |      | dBm    |

|                                                | At maximum gain setting                                                                                                                              |     | 12   |      | dBm    |

| 14 GHz to 20 GHz                               | At 10 dB gain setting                                                                                                                                |     | 10   |      | dBm    |

|                                                | At maximum gain setting                                                                                                                              |     | 12   |      | dBm    |

| 20 GHz to 23.6 GHz                             | At 10 dB gain setting                                                                                                                                |     | 10   |      | dBm    |

|                                                | At maximum gain setting                                                                                                                              |     | 11   |      | dBm    |

| LO Feedthrough                                 | At 10 dB gain setting (can be improved baseband dc offset adjustment)                                                                                |     | -25  |      | dBm    |

| Sideband Suppression                           | At 10 dB gain setting                                                                                                                                |     | 25   |      | dBc    |

| Parameter                                         | Test Conditions/Comments                                                                        | Min        | Тур Ма | x Unit |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------|------------|--------|--------|

| IF UPCONVERTER PERFORMANCE                        |                                                                                                 |            |        |        |

| Upconversion Voltage Gain                         | Maximum gain at maximum gain setting                                                            | 7          | 11     | dB     |

|                                                   | Minimum gain at minimum gain setting                                                            |            | -14    | dB     |

| Output Noise Density                              | Output carrier > −5 dBm                                                                         |            | -147   | dBc/Hz |

|                                                   | Output carrier > -14 dBm                                                                        |            | -145   | dBc/Hz |

|                                                   | Output carrier > -22.5 dBm                                                                      |            | -136   | dBc/Hz |

| OIP3                                              | $f_1$ IF = 1810 MHz, $f_2$ IF = 1812 MHz, amplitude per tone                                    |            | 23.5   |        |

|                                                   | = –15 dBm sine waves in quadrature with ac bias, 7 dB gain setting                              |            |        |        |

| 5.9 GHz to 10 GHz                                 |                                                                                                 |            | 27     | dBm    |

| 10 GHz to 14 GHz                                  |                                                                                                 |            | 24     | dBm    |

| 14 GHz to 20 GHz                                  |                                                                                                 |            | 22.5   | dBm    |

| 20 GHz to 23.6 GHz                                |                                                                                                 |            | 22.5   | dBm    |

| IMD5                                              | $f_1$ IF = 1810 MHz, $f_2$ IF = 1812 MHz, amplitude per tone                                    |            | 80     | dBm    |

|                                                   | =-15 dBm sine waves in quadrature with ac bias,                                                 |            |        |        |

|                                                   | 7 dB gain setting                                                                               |            |        |        |

| Output P1dB                                       |                                                                                                 |            |        |        |

| 5.9 GHz to 10 GHz                                 | At 7 dB gain setting                                                                            |            | 10.5   | dBm    |

|                                                   | At maximum gain setting                                                                         |            | 11.5   | dBm    |

| 10 GHz to 14 GHz                                  | At 7 dB gain setting                                                                            |            | 10     | dBm    |

|                                                   | At maximum gain setting                                                                         |            | 12     | dBm    |

| 14 GHz to 20 GHz                                  | At 7 dB gain setting                                                                            |            | 9.5    | dBm    |

|                                                   | At maximum gain setting                                                                         |            | 12     | dBm    |

| 20 GHz to 23.6 GHz                                | At 7 dB gain setting                                                                            |            | 9.5    | dBm    |

|                                                   | At maximum gain setting                                                                         |            | 11.5   | dBm    |

| LO Feedthrough                                    | At 7 dB gain setting (can be improved by baseband dc                                            |            | -35    | dBm    |

| J                                                 | offset adjustment)                                                                              |            |        |        |

| Sideband Suppression                              | At 7 dB gain setting                                                                            |            | 25     | dBc    |

| Tx POWER DETECTOR PERFORMANCE                     |                                                                                                 |            |        |        |

| Output Level                                      |                                                                                                 |            |        |        |

| Maximum                                           |                                                                                                 |            | 2      | dBm    |

| Minimum                                           |                                                                                                 |            | -30    | dBm    |

| ±1 dB Dynamic Range                               |                                                                                                 |            | 34     | dB     |

| Output Voltage                                    |                                                                                                 |            |        |        |

| Maximum                                           |                                                                                                 |            | 1      | V      |

| Minimum                                           |                                                                                                 |            | 0.2    | V      |

| Log Slope                                         |                                                                                                 |            | 25     | mV/dB  |

| Time                                              |                                                                                                 |            |        |        |

| Rise                                              | $P_{IN} = \text{off to } -10 \text{ dBm}, 10\% \text{ to } 90\%,$<br>C7 = 10 pF (see Figure 83) |            | 134    | ns     |

| Fall                                              | $P_{IN} = -10$ dBm to off, 10% to 90%, C7 = 10 pF (see Figure 83)                               |            | 190    | ns     |

| Response                                          | C7 = 10 pF (see Figure 83)                                                                      |            | 30     | ns     |

| RETURN LOSS                                       | -                                                                                               |            |        |        |

| RF Output                                         | 100 $\Omega$ differential                                                                       |            | 12     | dB     |

| LO Input                                          | 100 Ω differential                                                                              |            | 12     | dB     |

| IF Input                                          | $100 \Omega$ differential                                                                       |            | 17     | dB     |

| Baseband I/Q Input Impedance                      |                                                                                                 |            | 1      | МΩ     |

| LOGIC INPUTS                                      |                                                                                                 | 1          |        |        |

| Input High Voltage Range, V <sub>INH</sub>        |                                                                                                 | VP18 – 0.4 | 1.8    | s v    |

| Input Low Voltage Range, V <sub>INL</sub>         |                                                                                                 | 0          | 0.4    |        |

| Input Current, I <sub>INH</sub> /I <sub>INL</sub> |                                                                                                 |            | 100    | μΑ     |

| Input Canerit, INF/ INF                           |                                                                                                 |            | 100    | μA     |

| Parameter                                  | Test Conditions/Comments                | Min        | Тур  | Max  | Unit |

|--------------------------------------------|-----------------------------------------|------------|------|------|------|

| LOGIC OUTPUTS                              |                                         |            |      |      |      |

| Output High Voltage Range, V <sub>OH</sub> |                                         | VP18 - 0.4 |      | 1.8  | V    |

| Output Low Voltage Range, Vol              |                                         | 0          |      | 0.4  | V    |

| Output High Current, IoH                   |                                         |            |      | 500  | μΑ   |

| POWER INTERFACE                            |                                         |            |      |      |      |

| VPBB, VPLO, VPBI                           |                                         | 3.15       | 3.3  | 3.45 | V    |

| VPBB, VPLO, VPBI Supply Current            | ×1 LO path enabled, IF path disabled    |            | 340  |      | mA   |

| ,                                          | ×2 LO path enabled, IF path disabled    |            | 390  |      | mA   |

|                                            | ×1 LO path enabled, IF path enabled     |            | 490  |      | mA   |

|                                            | ×2 LO path enabled, IF path enabled     |            | 540  |      | mA   |

| VP18                                       |                                         | 1.7        | 1.8  | 1.9  | V    |

| VP18 Supply Current                        |                                         |            | 1    |      | mA   |

| VPDT, VPRF                                 |                                         | 4.75       | 5    | 5.25 | V    |

| VPDT, VPRF Supply Current                  | ×1/×2 LO path enabled, IF path disabled |            | 180  |      | mA   |

|                                            | ×1/×2 LO path enabled, IF path enabled  |            | 160  |      | mA   |

| Total Power Consumption                    | ×2 LO path enabled, IF path enabled     |            | 2.58 |      | W    |

|                                            | Power down                              |            | 35   | 50   | mW   |

## **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                 | Rating          |

|-------------------------------------------|-----------------|

| Supply Voltage                            |                 |

| VPDT, VPRF                                | 6.5 V           |

| VPBB, VPLO, VPBI                          | 4.3 V           |

| VP18                                      | 2.3 V           |

| Maximum Junction Temperature              | 125°C           |

| Operating Temperature Range               | -40°C to +85°C  |

| Storage Temperature Range                 | −55°C to +125°C |

| Lead Temperature Range (Soldering 60 sec) | −65°C to +150°C |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is thermal resistance, junction to ambient (°C/W), and  $\theta_{JC}$  is thermal resistance, junction to case (°C/W).

**Table 3. Thermal Resistance**

| Package Type  | $\theta_{JA}^1$ | $\theta_{JC}^{1}$ | Unit |

|---------------|-----------------|-------------------|------|

| 32-Lead LFCSP | 9.18            | 1.14              | °C/W |

$<sup>^1</sup>$  See JEDEC Standard JESD51-2 for additional information on optimizing the thermal impedance (printed circuit board (PCB) with 3  $\times$  3 vias).

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

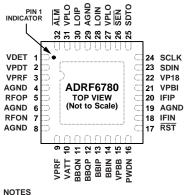

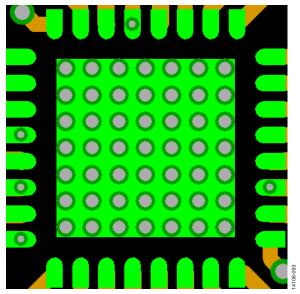

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. SOLDER THE EXPOSED PAD TO A LOW IMPEDANCE GROUND PLANE.

2. THE DEVICE NUMBER ON THE FIGURE DOES NOT INDICATE THE LABEL ON THE PACKAGE. PLEASE REFER TO PIN 1 INDICATOR FOR PIN LOCATIONS.

Figure 2. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No.            | Mnemonic                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | VDET                      | RF Detector Output. The voltage output is proportional to the decibel RF output power. The detector slope is nominally 50 mV/dB.                                                                                                                                                                                                                                                                                                                 |

| 2                  | VPDT                      | Power Supply Connection for the RF Detector. Decouple the VPDT pin with 100 pF and 0.1 $\mu$ F capacitors as close as possible to the pin. Note that this pin must always be supplied with 5 V.                                                                                                                                                                                                                                                  |

| 3, 9               | VPRF                      | Power Supply Connections for the RF Path. Decouple the VPRF pin with 100 pF and 0.1 $\mu$ F capacitors as close as possible to the pins.                                                                                                                                                                                                                                                                                                         |

| 4, 6, 8,<br>19, 29 | AGND                      | Analog Grounds. Connect these pins to a low impedance ground plane.                                                                                                                                                                                                                                                                                                                                                                              |

| 5, 7               | RFOP, RFON                | RF Outputs. These outputs are $100 \Omega$ differential outputs for the RF path. Frequency range is $5.9  \text{GHz}$ to $23.6  \text{GHz}$ .                                                                                                                                                                                                                                                                                                    |

| 10                 | VATT                      | Modulator Output Attenuator Control Input. The RF voltage variable attenuator is controlled by applying a 0 V to 2.6 V control voltage to the VATT pin. Increase the gain when VATT voltage increases. This pin is linear in dB over central gain range.                                                                                                                                                                                         |

| 11 to<br>14        | BBQN, BBQP,<br>BBIP, BBIN | I Channel and Q Channel Baseband Inputs. These inputs are high input impedance and are typically differentially terminated to a $100 \Omega$ resistor using an off chip termination. The nominal common-mode bias level on these pins must be $0.5 \text{ V}$ .                                                                                                                                                                                  |

| 15                 | VPBB                      | Power Supply Connection for Baseband Path. Decouple the VPBB pin with 100 pF and 0.1 $\mu$ F capacitors as close as possible to the pin.                                                                                                                                                                                                                                                                                                         |

| 16                 | PWDN                      | Power Down. The ADRF6780 powers up when the PWDN pin is at a low logic level ( $<0.5$ V). To power down the ADRF6780, apply a logic high level ( $>1.2$ V). When the ADRF6780 is powered up, the SPI can also be used as a power-down capability. The PWDN pin has an internal 18 k $\Omega$ pull-down resistor.                                                                                                                                 |

| 17                 | RST                       | Reset. This pin provides the ability to reset the SPI to the default register settings. Pull the $\overline{\text{RST}}$ pin to a logic high level in normal operation. Driving the $\overline{\text{RST}}$ pin to a logic low level loads the default SPI register settings. The $\overline{\text{RST}}$ pin has an internal 7.75 k $\Omega$ pull-up resistor.                                                                                  |

| 18, 20             | IFIN, IFIP                | IF Inputs. These inputs are $100 \Omega$ differential inputs for IF upconversion, and they must be ac-coupled. When the IF mode is set, remove the $0 \Omega$ R10 to R13 resistors from the I/Q lines.                                                                                                                                                                                                                                           |

| 21                 | VPBI                      | Power Supply Connection. Decouple the VPBI pin with 100 pF and 0.1 µF capacitors as close as possible to the pin.                                                                                                                                                                                                                                                                                                                                |

| 22                 | VP18                      | 1.8 V Power Supply. Decouple the VP18 pin with 100 pF and 0.1 µF capacitors as close as possible to the pin.                                                                                                                                                                                                                                                                                                                                     |

| 23                 | SDIN                      | Serial Data Input. Serial data applied to the SDIN pin is loaded into the SPI register upon a successful write command as indicated in the timing diagrams (see Figure 68 to Figure 70). The first most significant bit (MSB) is a control bit and it determines whether data is written to the register (logic high) or read from the serial data output pin (logic low). The SDIN pin has an internal $18 \text{ k}\Omega$ pull-down resistor. |

| 24                 | SCLK                      | Serial Clock. This pin is the clock input for the SPI interface. The SCLK pin has an internal $18 \text{ k}\Omega$ pull-down resistor.                                                                                                                                                                                                                                                                                                           |

| 25                 | SDTO                      | Serial Data Output. The SDTO pin provides a SPI readback capability. See the timing diagrams for normal operation (see Figure 68 to Figure 70). The SDTO pin has an internal 18 kΩ pull-down resistor.                                                                                                                                                                                                                                           |

| 26                 | SEN                       | Serial Enable. When the $\overline{\text{SEN}}$ input pin goes high, the data stored in the shift registers is loaded into the register. The $\overline{\text{SEN}}$ pin has an internal 7.75 k $\Omega$ pull-up resistor.                                                                                                                                                                                                                       |

| Pin No. | Mnemonic   | Description                                                                                                                                                                                         |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27, 31  | VPLO       | Power Supply Connections for the LO Path. Decouple the VPLO pin with 100 pF and 0.1 $\mu$ F capacitors as close as possible to the pin.                                                             |

| 28, 30  | LOIN, LOIP | LO Inputs. These inputs are $100 \Omega$ differential inputs for the LO path. The LO input frequency range is 5.4 GHz to 14 GHz. The on-chip LO frequency doubler can be enabled via a SPI command. |

| 32      | ALM        | Alarm. The ALM pin indicates internal alarm conditions. The ALM pin is logic low when an alarm condition is detected.                                                                               |

|         | EP         | Exposed Pad. Solder the exposed pad to a low impedance ground plane.                                                                                                                                |

## TYPICAL PERFORMANCE CHARACTERISTICS

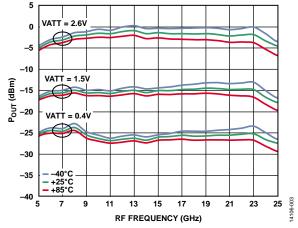

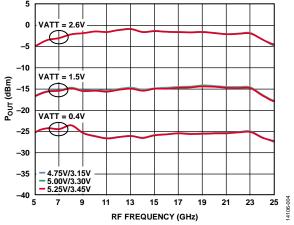

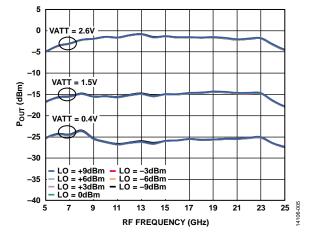

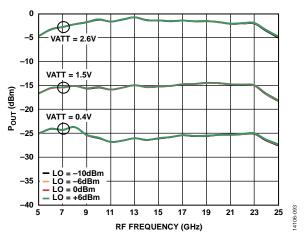

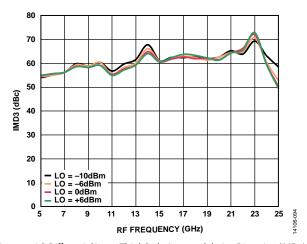

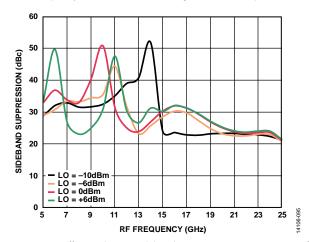

$VPBB = VPBI = VPLO = 3.3 \text{ V}, VP18 = 1.8 \text{ V}, VPDT = VPRF = 5 \text{ V}, T_A = 25^{\circ}\text{C}, LO = 0 \text{ dBm differential drive, polyphase filter (PPF, <math>\times 1$ ) mode below 14 GHz and differential drive doubler ( $\times 2$ ) mode above 14 GHz, VATT = 2.6 V, unless otherwise noted.

#### I/Q MODE

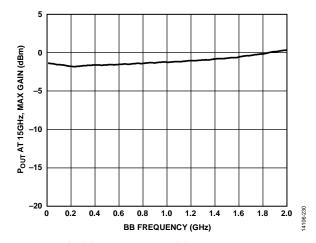

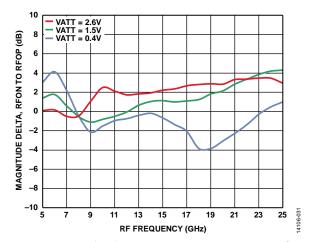

Baseband (BB) I/Q amplitude = -15 dBm, differential sine waves in quadrature with a 500 mV dc bias, BB I/Q frequency ( $f_x$  BB) = 10 MHz, BB input termination with 100  $\Omega$  externally, unless otherwise noted.

Figure 3. Output Power (Pout) vs. RF Frequency (fRF) at Three Gain Settings for Various Temperatures, BB I/Q Amplitude = −15 dBm

Figure 4. Output Power (Pout) vs. RF Frequency (f<sub>RF</sub>) at Three Gain Settings for Various Supply Voltages, BB I/Q Amplitude = –15 dBm

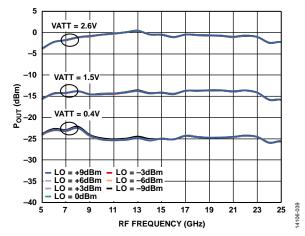

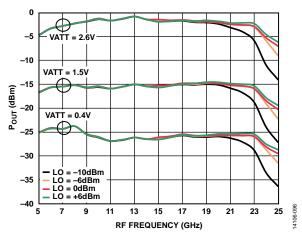

Figure 5. Output Power ( $P_{OUT}$ ) vs. RF Frequency ( $f_{RF}$ ) at Three Gain Settings for Various LO Inputs, BB I/Q Amplitude = -15 dBm

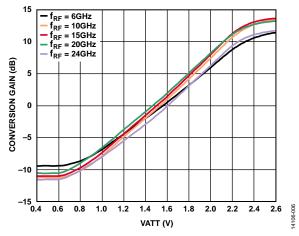

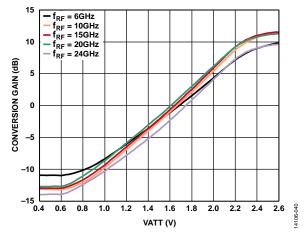

Figure 6. Conversion Gain vs. VATT for Various RF Frequencies ( $f_{RF}$ )

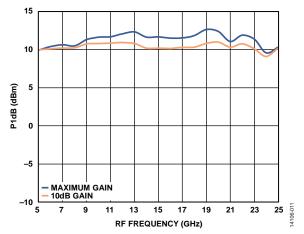

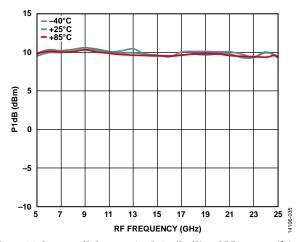

Figure 7. Output 1 dB Compression Point (P1dB) vs. RF Frequency ( $f_{RF}$ ) at a 10 dB Gain Setting for Various Temperatures

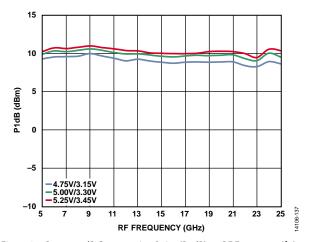

Figure 8. Output 1 dB Compression Point (P1dB) vs. RF Frequency ( $f_{RF}$ ) at a 10 dB Gain Setting for Various Supply Voltages

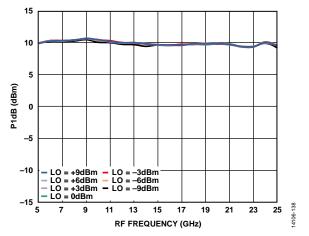

Figure 9. Output 1 dB Compression Point (P1dB) vs. RF Frequency ( $f_{RF}$ ) at a 10 dB Gain Setting for Various LO Inputs

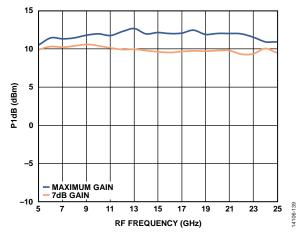

Figure 10. Output 1 dB Compression Point (P1dB) vs. RF Frequency (f<sub>№</sub>) at a 10 dB Gain Setting and the Maximum Gain Setting

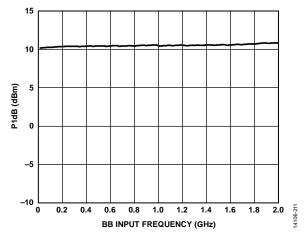

Figure 11. Output 1 dB Compression Point (P1dB) vs. BB Input Frequency at a 10 dB Gain Setting

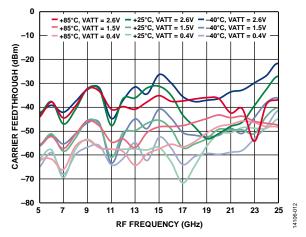

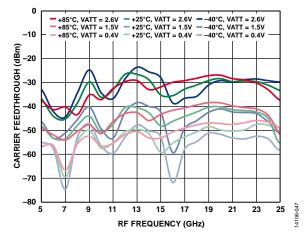

Figure 12. Carrier Feedthrough vs. RF Frequency ( $f_{\rm RF}$ ) at Three Gain Settings and Temperatures Before Nulling

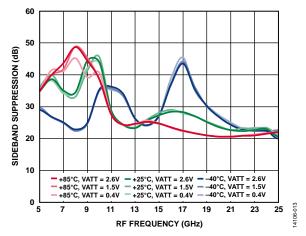

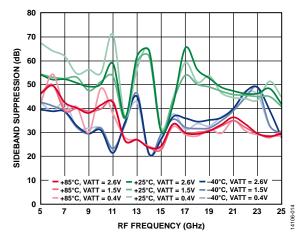

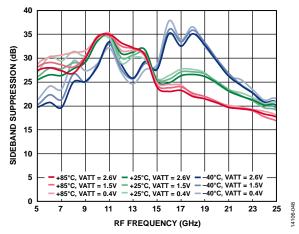

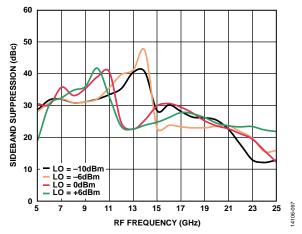

Figure 13. Sideband Suppression vs. RF Frequency (f<sub>RF</sub>) at Three Gain Settings and Temperatures Before Nulling

Figure 14. Sideband Suppression vs. RF Frequency (f<sub>RF</sub>) at Three Gain Settings and Temperatures after Nulling Using I\_PATH\_PHASE\_ACCURACY and Q\_PATH\_PHASE\_ACCURACY at 25°C

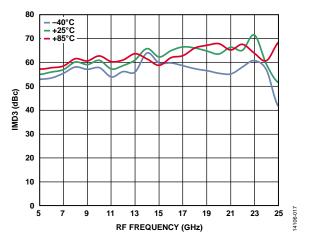

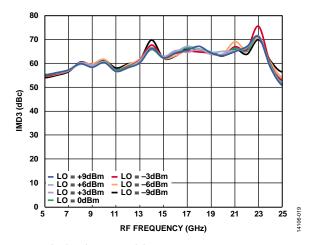

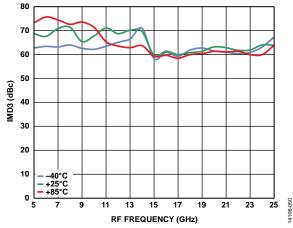

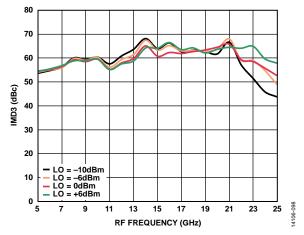

Figure 15. Third-Order Intermodulation Distortion (IMD3) vs. RF Frequency ( $f_{RF}$ ) at a 10 dB Gain Setting for Various Temperatures, BB I/Q Amplitude = -15 dBm per Tone

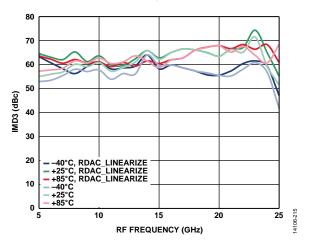

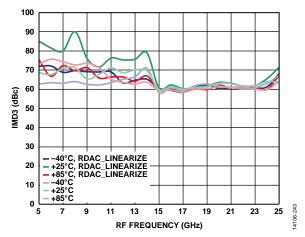

Figure 16. Third-Order Intermodulation Distortion (IMD3) vs. RF Frequency ( $f_{RF}$ ) at a 10 dB Gain Setting for Various RDAC\_LINEARIZE Settings and Various Temperatures, BB I/Q Amplitude = -15 dBm per Tone

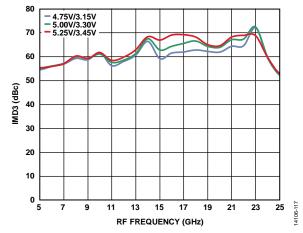

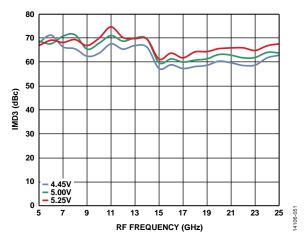

Figure 17. Third-Order Intermodulation Distortion (IMD3) vs. RF Frequency (fRF) for Various Supply Voltages,

BB I/Q Amplitude = −15 dBm per Tone

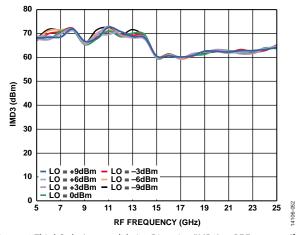

Figure 18. Third-Order Intermodulation Distortion (IMD3) vs. RF Frequency (f<sub>RF</sub>) at a 10 dB Gain Setting for Various LO Inputs, BB I/Q Amplitude = −15 dBm per Tone

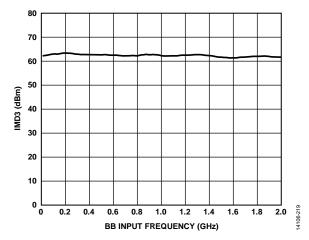

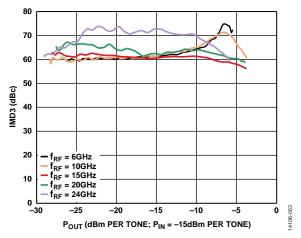

Figure 19. Third-Order Intermodulation Distortion (IMD3) vs. BB Input Frequency at a 10 dB Gain Setting, BB I/Q Amplitude = -15 dBm per Tone

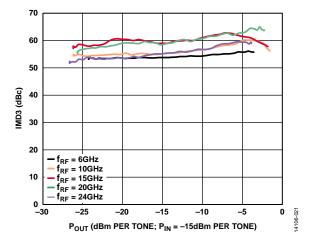

Figure 20. Third-Order Intermodulation Distortion (IMD3) vs. Output Power  $(P_{OUT})$  for Various RF Frequencies  $(f_{RF})$ , BB I/Q Amplitude = -15 dBm per Tone

Figure 21. Output Third-Order Intercept (OIP3) vs. RF Frequency ( $f_{\rm RF}$ ) at a 10 dB Gain Setting, BB I/Q Amplitude = -15 dBm per Tone

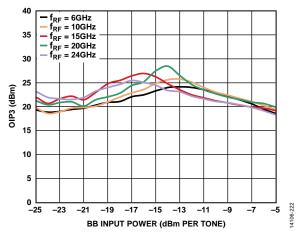

Figure 22. Output Third-Order Intercept (OIP3) vs. BB Input Power at a 10 dB Gain Setting for Various RF Frequencies ( $f_{RF}$ )

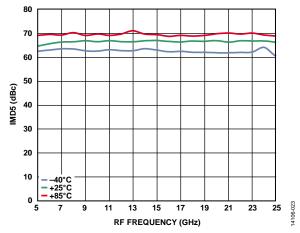

Figure 23. Fifth-Order Intermodulation Distortion (IMD5) vs. RF Frequency ( $f_{RF}$ ) at a 10 dB Gain Setting for Various Temperatures, BB I/Q Amplitude = -15 dBm per Tone

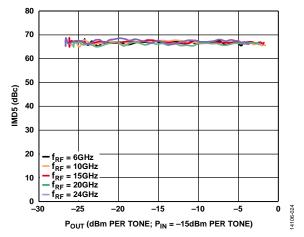

Figure 24. Fifth-Order Intermodulation Distortion (IMD5) vs. Output Power  $(P_{OUT})$  for Various RF Frequencies,

BB I/Q Amplitude = -15 dBm per Tone

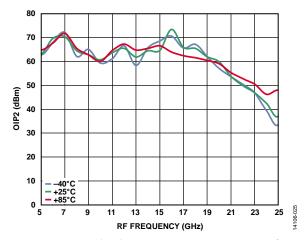

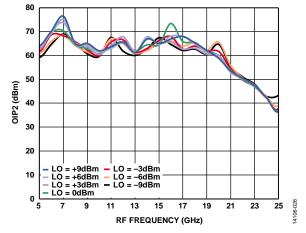

Figure 25. Output Second-Order Intercept (OIP2) vs. RF Frequency ( $f_{RF}$ ) at a 10 dB Gain Setting for Various Temperatures, BB I/Q Amplitude = -15 dBm per Tone

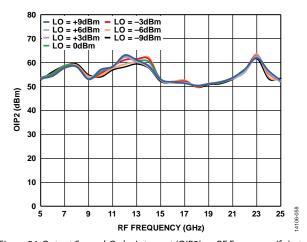

Figure 26. Output Second-Order Intercept (OIP2) vs. RF Frequency (f<sub>RF</sub>) at a 10 dB Gain Setting for Various LO Inputs, BB I/Q Amplitude = −15 dBm per Tone

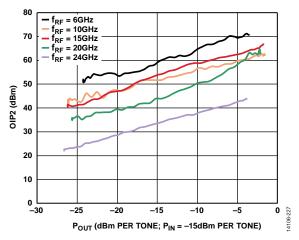

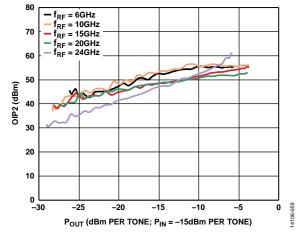

Figure 27. Output Second-Order Intercept (OIP2) vs. Output Power ( $P_{OUT}$ ) for Various RF Frequencies ( $f_{RF}$ ), BB I/Q Amplitude = -15 dBm per Tone

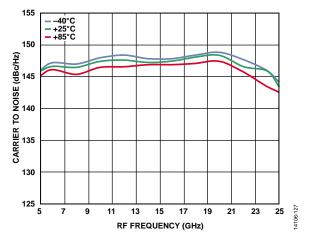

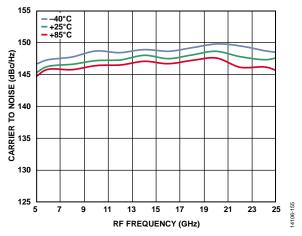

Figure 28. Output Noise Density vs. RF Frequency (f<sub>RF</sub>) at a 10 dB Gain Setting for Various Temperatures with an Output Carrier of –5 dBm

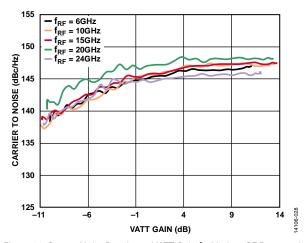

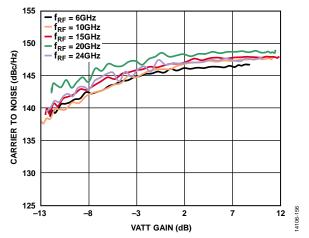

Figure 29. Output Noise Density vs. VATT Gain for Various RF Frequencies  $(f_{RF})$  with an Input Carrier of -15 dBm

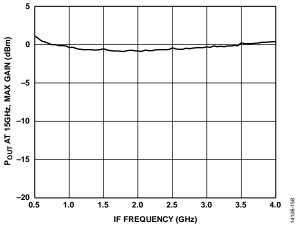

Figure 30. Bandwidth,  $P_{OUT}$  at 15 GHz and the Maximum Gain Setting vs. BB Input Frequency

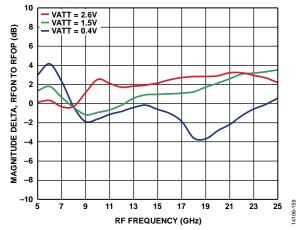

Figure 31. Magnitude Delta, RFON minus RFOP vs. RF Frequency ( $f_{\it RF}$ ) at Three Different Gain Settings

#### IF MODE

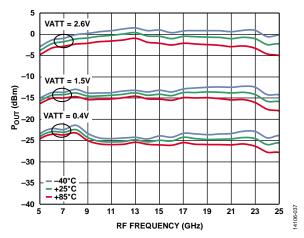

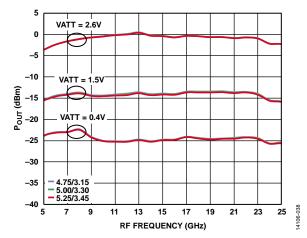

IF frequency (IF mode) = 1900 MHz, IF amplitude = -12 dBm, input ac-coupled, unless otherwise noted.

Figure 32. Output Power ( $P_{OUT}$ ) vs. RF Frequency ( $f_{RF}$ ) at Three Gain Settings for Various Temperatures, IF Amplitude = -12 dBm

Figure 33. Output Power ( $P_{OUT}$ ) vs. RF Frequency ( $f_{RF}$ ) at Three Gain Settings for Various Supply Voltages, IF Amplitude = -12 dBm

Figure 34. Output Power ( $P_{OUT}$ ) vs. RF Frequency ( $f_{RF}$ ) at Three Gain Settings for Various LO Inputs, IF Amplitude = -12 dBm

Figure 35. Conversion Gain vs. VATT at Various RF Frequencies ( $f_{RF}$ )

Figure 36. Output 1 dB Compression Point (P1dB) vs. RF Frequency ( $f_{\rm RF}$ ) at a 7 dB Gain Setting for Various Temperatures

Figure 37. Output 1 dB Compression Point (P1dB) vs. RF Frequency (f<sub>№</sub>) at a 7 dB Gain Setting for Various Supply Voltages

Figure 38. Output 1 dB Compression Point (P1dB) vs. RF Frequency ( $f_{\rm RF}$ ) at a 7 dB Gain Setting for Various LO Inputs

Figure 39. 1 dB Output Compression Point (P1dB) vs. RF Frequency ( $f_{RF}$ ) at a 7 dB Gain Setting and the Maximum Gain Setting

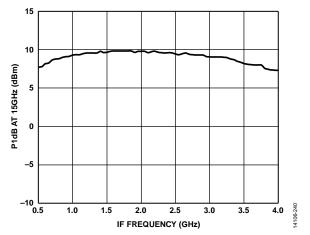

Figure 40. Output 1 dB Compression Point (P1dB) at 15 GHz vs. IF Frequency at a 7 dB Gain Setting

Figure 41. Carrier Feedthrough vs. RF Frequency ( $f_{\rm RF}$ ) at Three Gain Settings for Various Temperatures Before Nulling

Figure 42. Sideband Suppression vs. RF Frequency ( $f_{\rm RF}$ ) at Three Different Gain Settings for Various Temperatures Before Nulling

Figure 43. Third-Order Intermodulation Distortion (IMD3) vs. RF Frequency ( $f_{RF}$ ) at a 7 dB Gain Setting for Various Temperatures, IF Amplitude = -15 dBm per

Figure 44. Third-Order Intermodulation Distortion (IMD3) vs. RF Frequency ( $f_{\rm RF}$ ) at 7 dB Gain Setting for Various RDAC\_LINEARIZE Settings and Various Temperatures, IF Amplitude = -15 dBm per Tone

Figure 45. Third-Order Intermodulation Distortion (IMD3) vs. RF Frequency ( $f_{\it RF}$ ) at a 7 dB Gain Setting and for Various Supply Voltages, IF Amplitude = -15 dBm per Tone

Figure 46. Third-Order Intermodulation Distortion (IMD3) vs. RF Frequency ( $f_{\rm RF}$ ) at a 7 dB Gain Setting for Various LO Inputs, IF Amplitude = -15 dBm per Tone

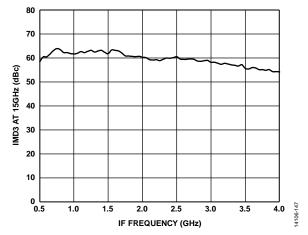

Figure 47. Third-Order Intermodulation Distortion (IMD3) at 15 GHz vs.

IF Frequency at a 7 dB Gain Setting

Figure 48. Third-Order Intermodulation Distortion (IMD3) vs. Output Power ( $P_{OUT}$ ) for Various RF Frequencies ( $f_{RF}$ ), IF Amplitude = -15 dBm per Tone

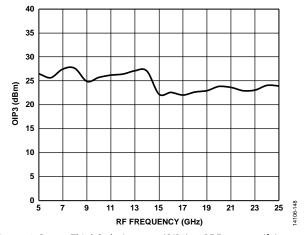

Figure 49. Output Third-Order Intercept (OIP3) vs. RF Frequency ( $f_{RF}$ ) at a 7 dB Gain Setting, IF Amplitude = -15 dBm per Tone

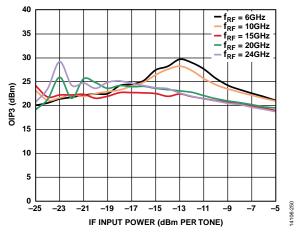

Figure 50. Output Third-Order Intercept (OIP3) vs. IF Input Power at a 7 dB Gain Setting for Various RF Frequencies ( $f_{RF}$ )

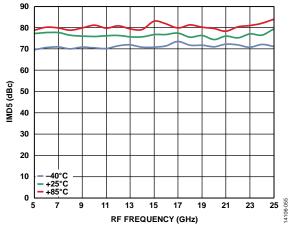

Figure 51. Fifth-Order Intermodulation Distortion (IMD5) vs. RF Frequency ( $f_{\rm RF}$ ) at a 7 dB Gain Setting for Various Temperatures, IF Amplitude = -15 dBm per Tone

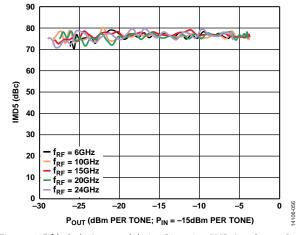

Figure 52. Fifth-Order Intermodulation Distortion (IMD5) vs. Output Power ( $P_{OUT}$ ) for Various RF Frequencies ( $f_{RF}$ ), IF Amplitude = -15 dBm per Tone

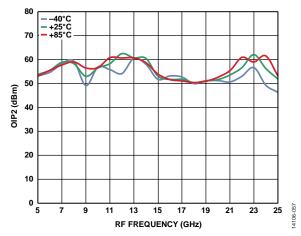

Figure 53. Output Second-Order Intercept (OIP2) vs. RF Frequency ( $f_{\rm RF}$ ) at a 7 dB Gain Setting for Various Temperatures, IF Amplitude = -15 dBm per Tone

Figure 54. Output Second-Order Intercept (OIP2) vs. RF Frequency ( $f_{\rm RF}$ ) at a 7 dB Gain Setting for Various LO Inputs, IF Amplitude = -15 dBm per Tone

Figure 55. Output Second-Order Intercept (OIP2) vs. Output Power ( $P_{OUT}$ ) for Various RF Frequencies ( $f_{RF}$ ), IF Amplitude = -15 dBm per Tone

Figure 56. Output Noise Density vs. RF Frequency ( $f_{RF}$ ) at a 7 dB Gain Setting for Various Temperatures with an Output Carrier of -5 dBm

Figure 57. Output Noise Density vs. VATT Gain for Various RF Frequencies ( $f_{RF}$ ) with an Input Carrier of -12 dBm

Figure 58. Bandwidth,  $P_{OUT}$  at 15 GHz and Maximum Gain Setting vs. IF Frequency ( $f_{\rm lF}$ )

Figure 59. Magnitude Delta, RFON to RFOP vs. RF Frequency ( $f_{\it RF}$ ) at Three Different Gain Settings

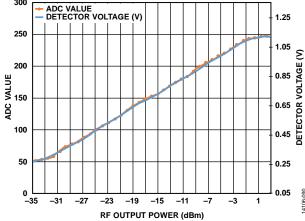

#### **OUTPUT DETECTOR PERFORMANCE**

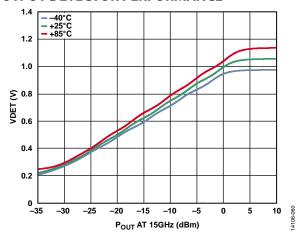

Figure 60. Detector Output (VDET) vs. Output Power (Роит) at 15 GHz for Various Temperatures

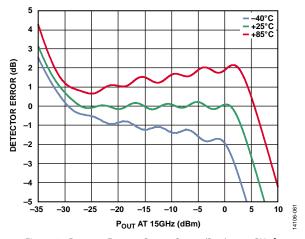

Figure 61. Detector Error vs. Output Power (P<sub>OUT</sub>) at 15 GHz for Various Temperatures

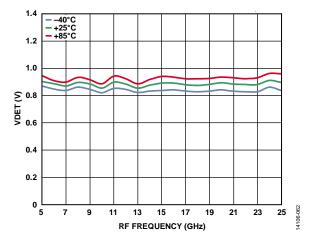

Figure 62. Detector Output (VDET) vs. RF Frequency (f<sub>RF</sub>), –5 dBm Output Power (P<sub>OUT</sub>) for Various Temperatures

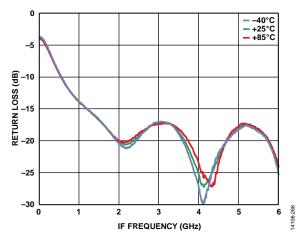

#### **RETURN LOSS**

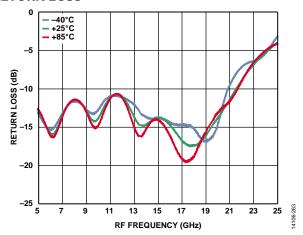

Figure 63. RF Output Return Loss S11 vs. RF Frequency for Various Temperatures

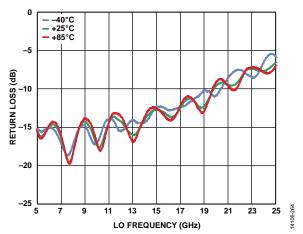

Figure 64. LO Input Return Loss S11 vs. LO Frequency for Various Temperatures

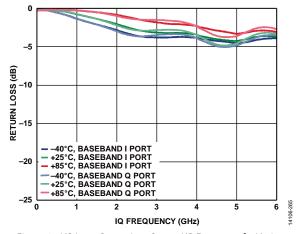

Figure 65. I/Q Input Return Loss S11 vs. I/Q Frequency for Various Temperatures

Figure 66. IF Input Return Loss S11 vs. IF Frequency for Various Temperatures

# THEORY OF OPERATION

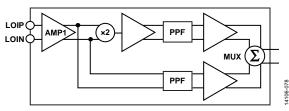

The ADRF6780 is a wideband microwave upconverter optimized for point to point microwave radio designs operating in the 5.9 GHz to 23.6 GHz frequency range. A functional block diagram of the device is shown in Figure 1. The ADRF6780 is programmed via an SPI.

#### **BASEBAND**

The input impedance of the basebands are high input impedance. These inputs are designed to operate with a 0.5 V common-mode voltage. These inputs are differentially terminated to a 100  $\Omega$  resistor using an off chip termination.

The linearity can be optimized by adding phase correction signals to the current output via adjusting the I\_PATH\_PHASE\_ACCURACY register (Register 0x05, Bits[3:0]) and the Q\_PATH\_PHASE\_ACCURACY (Register 0x05, Bits[7:4]) register.

#### SINGLE SIDEBAND (SSB) UPCONVERSION

The IF input path can be fed anywhere from 0.8 GHz to 3.5 GHz. The IF inputs path can be upconverted to 5.9 GHz to 23.6 GHz, while suppressing the unwanted sideband by typically better than 25 dBc. The IF upconversion inputs are 100  $\Omega$  differential and must be ac-coupled. In addition, the I/Q baseband input must stay floating without any termination on their inputs.

#### **LO INPUT PATH**

The LO input path operates from 5.4 GHz to 14 GHz with a LO amplitude range of -6 dBm to +6 dBm. It is built from two modes:  $\times 1$  mode (Register 0x03, Bit 2), which provides an LO output frequency equal to the LO input frequency, and  $\times 2$  mode (Register 0x03, Bit 3), which doubles the LO output frequency from the LO input frequency. Note that, when enabling the LO  $\times 2$  mode (Register 0x03, Bit 3), the LO  $\times 1$  mode (Register 0x03, Bit 2) must be disabled.

The LO path is designed to operate differentially. LOIP and LOIN are the inputs to the LO path. It is recommended to use the ADRF6780 with a LO differential input to achieve the best performance.

Figure 67 shows a block diagram of the LO path.

Figure 67. LO Path Block Diagram

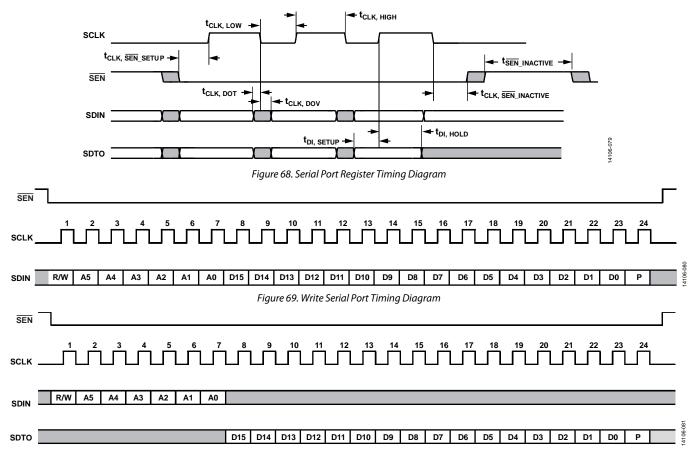

#### **SERIAL PORT INTERFACE (SPI)**

The SPI of the ADRF6780 allows the user to configure the device for specific functions or operations via a 4-pin SPI port. This interface provides users with added flexibility and customization. The  $\overline{\text{SPI}}$  consists of four control lines: SCLK, SDIN, SDTO, and  $\overline{\text{SEN}}$ .

The ADRF6780 protocol consists of a write/read bit followed by six register address bits, 16 data bits, and a parity bit. Both the address and data fields are organized MSB first and end with the least significant bit (LSB). For a write, set the first bit to 0, and for a read, set this bit to 1.

The write cycle sampling must be done on the rising edge. The 16 bits of the serial write data are shifted in, MSB to LSB. The ADRF6780 input logic level for the write cycle supports an 1.8 V interface.

For a read cycle, up to 16 bits of serial read data are shifted out, MSB first. After the 16 bits of data shift out, the parity bit shifts out. The output logic level for a read cycle is 1.8 V.

The parity bit always follows the direction of the data. If parity is not used, the transmitting end transmits zero instead of parity. The parity is odd, which means that the total number of ones transmitted during a command, including the read/write bit, the address bit, the data bit, and the parity bit, must be odd.

**Table 5. Serial Port Register Timing**

| Parameter                                               | Description                           | Min      | Тур | Max | Unit |

|---------------------------------------------------------|---------------------------------------|----------|-----|-----|------|

| <b>t</b> DI, SETUP                                      | Data to clock setup time              | 10       |     |     | ns   |

| t <sub>DI, HOLD</sub>                                   | Data to clock hold time               | 10       |     |     | ns   |

| <b>t</b> CLK, HIGH                                      | Clock high duration                   | 40 to 60 |     |     | %    |

| t <sub>CLK, LOW</sub>                                   | Clock low duration                    | 40 to 60 |     |     | %    |

| t <sub>CLK</sub> , <del>SEN</del> _SETUP                | Clock to SEN setup time               | 30       |     |     | ns   |

| t <sub>CLK, DOT</sub>                                   | Clock to data out transition time     |          |     | 10  | ns   |

| t <sub>CLK, DOV</sub>                                   | Clock to data out valid time          |          |     | 10  | ns   |

| $t_{\text{CLK},\overline{\text{SEN}}\_\text{INACTIVE}}$ | Clock to SEN inactive                 | 20       |     |     | ns   |

| t <sub>SEN_INACTIVE</sub>                               | Inactive SEN (between two operations) | 80       |     |     | ns   |

Figure 70. Read Serial Port Timing Diagram

# APPLICATIONS INFORMATION CARRIER FEEDTHROUGH NULLING

Carrier feedthrough results from minute dc offsets that occur on the differential baseband inputs. In an I/Q modulator, nonzero differential offsets mix with the LO and result in carrier feedthrough to the RF output. In addition to this effect, some of the signal power at the LO input couples directly to the RF output (this may be because of the bond wire to bond wire coupling or coupling through the silicon substrate). The net carrier feedthrough at the RF output is the vector combination of the signals that appear at the output because of these two effects. A TxDAC can externally accomplish carrier feedthrough nulling.

#### SIDEBAND SUPPRESSION OPTIMIZATION

Sideband results from gain and phase imperfections between the I and Q channels. Sideband also results from the quadrature error in generating the quadrature LO signals. Quadrature I and Q signals are constructed in the LO path, and the vector combination of these signals at the RF output results in suppression of the unwanted sideband. Deviation from perfect quadrature on these signals limits the amount of achievable sideband suppression.

The ADRF6780 offers quadrature phase adjustment in the LO path quadrature signals. Make these adjustments through the I\_PATH\_PHASE\_ACCURACY bits (Register 0x05, Bits[3:0]) and Q\_PATH\_PHASE\_ACCURACY (Register 0x05, Bits[7:4]) bits to reject the unwanted sideband signal.

Figure 14 shows the level of unwanted sideband signal achievable from the ADRF6780 across the I\_PATH\_PHASE\_ACCURACY bits (Register 0x05, Bits[3:0]) and Q\_PATH\_PHASE\_ACCURACY (Register 0x05, Bits[7:4]) bits.

If further optimization is needed, adjust the amplitude and phase externally through a TxDAC.

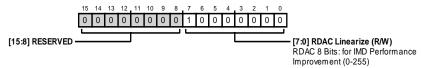

#### **LINEARITY**

The linearity in the ADRF6780 can be optimized through the distortion cancellation circuit that is set up by the RDAC\_LINEARIZE bits (Register 0x04, Bits[7:0]) SPI settings. The distortion cancellation circuit connects in parallel with the baseband signal path in such a way that the fundamental is minimally affected whereas the third-order portions cancel to some degree. Adjusting the value of the RDAC\_LINEARIZE bits (Register 0x04, Bits[7:0]) changes the resistance value in the cancellation path by fine tuning the amount of third-order destructively added to the main signal path. It also serves as a form or predistortion for third-order impedance generated further down in the signal path.

Figure 16 and Figure 44 show the level of linearity improvement achievable across the ADRF6780 RDAC\_LINEARIZE bits.

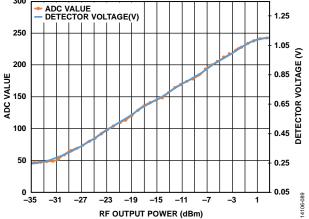

#### **ADC**

The ADRF6780 includes an ADC that connects to a detector. The user has an option to read the detector output from the detector output pin (VDET, Pin 1) or using the ADC from the

SPI. Figure 71 shows normal operation at I/Q mode, an RF output of 6.7 GHz, an I/Q input of 1 MHz, and a maximum gain. Figure 72 shows normal operation at IF mode and an RF output of 6.7 GHz, an IF input of 800 MHz, and a maximum gain.

Figure 71. ADC Detector Output and Detector Output Power, I/Q Mode

Figure 72. ADC Detector Output and Detector Output Power, IF Mode

The following procedure is to read back from the detector for the first time. For each subsequent readback, repeat Step 4 to Step 8. To read back from the detector using the ADC, take the following steps:

- 1. Set Bit 7 of Register 0x03 to 1 (DETECTOR\_ENABLE).

- 2. Set Bit 1 of Register 0x06 to 1 (ADC\_ENABLE). Write 0x02 to Register 0x06.

- 3. Set Bit 0 of Register 0x06 to 1 (ADC\_CLOCK\_ENABLE). Write 0x03 to Register 0x06.

- 4. Set Bit 2 of Register 0x06 to 1 (ADC\_START). Write 0x07 to Register 0x06.

- 5. Wait approximately 200 μs for the ADC to be ready.

- 6. Read back Bit 8 of Register 0x0C to 1 (ADC\_STATUS). When the bit is high, proceed to Step 7.

- 7. Set Bit 2 of Register 0x06 to 0 (ADC\_START).

- 8. Read back Bits[7:0] of Register 0x0C for the ADC value (ADC\_VALUE).

To disable the ADC, disable the ADC\_CLOCK\_ENABLE, ADC\_ENABLE, and ADC\_START bits.

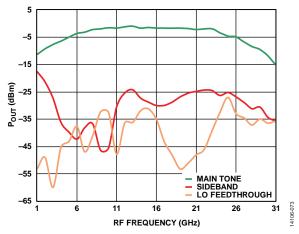

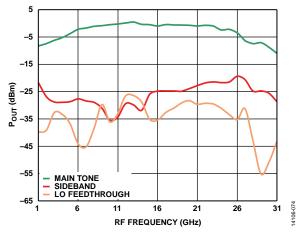

#### **WIDE FREQUENCY PERFORMANCE**

Figure 73 and Figure 74 show the typical performance of the ADRF6780 when using values outside of the RF output frequency range. It is important to understand that this performance is typical and not guaranteed.

Figure 73 was tested in I/Q mode with an RF output frequency of 1 GHz to 31 GHz. The LO input frequency was switched to LO ×2 doubler mode above 14 GHz.

Figure 74 was tested in IF mode with an RF output frequency of 1 GHz to 31 GHz. The LO input frequency was switched to LO ×2 doubler mode above 14 GHz.

Figure 73. Output Power ( $P_{OUT}$ ) vs. RF Frequency ( $f_{RF}$ ) in I/Q Mode at the Maximum Gain Setting, BB I/Q Amplitude = -15 dBm

Figure 74. Output Power ( $P_{OUT}$ ) vs. RF Frequency ( $f_{RF}$ ) in IF Mode at the Maximum Gain Setting, IF Amplitude = -12 dBm

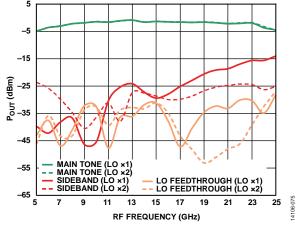

#### LO Path ×1, ×2 Full Range

Figure 75 shows the typical performance of the ADRF6780 when the LO input frequency is used within the full frequency range. It is important to understand that this performance is typical and not guaranteed.

Figure 75 was tested with the LO path set to  $\times 1$  mode and  $\times 2$  mode with a 5.9 GHz to 23.6 GHz frequency range in I/Q mode. It is recommended to switch to LO  $\times 2$  doubler mode above 14 GHz to achieve better performance out of the device.

Figure 75. LO  $\times$ 1 Mode and LO  $\times$ 2 Mode, Output Power ( $P_{Out}$ ) vs. RF Frequency ( $f_{RF}$ ) in I/Q Mode at the Maximum Gain Setting, BB I/Q Amplitude = -15 dBm

#### **LAYOUT**

Solder the exposed pad on the underside of the ADRF6780 to a low thermal and electrical impedance ground plane. This pad is typically soldered to an exposed opening in the solder mask on the evaluation board. Connect these ground vias to all other ground layers on the evaluation board to maximize heat dissipation from the device package.

Figure 76. Evaluation Board Layout for the ADRF6780 Package

## LO INPUT DRIVEN DIFFERENTIAL vs. SINGLE ENDED

This section provides performance measurements that compare the ADRF6780 using a differential LO input vs. a single-ended LO input. When the device uses a single-ended configuration, LOIP drives while LOIN terminates to 50  $\Omega$ .

The subharmonic measurement compares the two settings. The LO input was set to doubler mode ( $\times$ 2) at a LO frequency of 9 GHz, and the I/Q mode was set with a 10 MHz sine wave. Table 6 represents the output frequencies of the upper sideband, the lower sideband, and the LO leakage at the fundamental output as well as the subharmonic output frequency at a maximum gain.

Table 6. LO Single-Ended vs. Differential Configuration Performance

|              |                         | Fu                                          | Fundamental Output                            |                     |                                                 | Subharmonic Output                              |                       |  |  |

|--------------|-------------------------|---------------------------------------------|-----------------------------------------------|---------------------|-------------------------------------------------|-------------------------------------------------|-----------------------|--|--|

| Mode         | LO Input<br>Power (dBm) | Wanted Upper<br>Sideband,<br>LO – I/Q (dBm) | Unwanted Lower<br>Sideband,<br>LO + I/Q (dBm) | LO Leakage<br>(dBm) | Unwanted Upper<br>Sideband,<br>LO/2 – I/Q (dBm) | Unwanted Lower<br>Sideband,<br>LO/2 + I/Q (dBm) | LO/2 Leakage<br>(dBm) |  |  |

| Single Ended | -10                     | -2.20                                       | -28.83                                        | -32.36              | -16.26                                          | -32.85                                          | -36.16                |  |  |

|              | -6                      | -2.09                                       | -25.15                                        | -33.22              | -18.01                                          | -35.78                                          | -35.46                |  |  |

|              | 0                       | -1.94                                       | -28.36                                        | -38.08              | -22.83                                          | -42.97                                          | -41.50                |  |  |

|              | +6                      | -2.01                                       | -28.36                                        | -42.58              | -20.17                                          | -39.80                                          | -38.08                |  |  |

| Differential | -10                     | -1.84                                       | -24.96                                        | -43.49              | -29.66                                          | -51.54                                          | -45.85                |  |  |

|              | -6                      | -1.85                                       | -27.19                                        | -38.86              | -33.18                                          | -51.25                                          | -47.12                |  |  |

|              | 0                       | -1.84                                       | -29.46                                        | -37.84              | -38.04                                          | -56.50                                          | -58.25                |  |  |

|              | +6                      | -1.85                                       | -29.55                                        | -37.70              | -40.08                                          | -58.46                                          | -60.16                |  |  |

Gain, third-order intermodulation distortion (IMD3), and sideband rejection are also measured. RF frequencies from 5 GHz to 13 GHz are produced in LO  $\times$ 1 mode, while LO  $\times$ 2 mode produced RF frequencies from 14 GHz to 25 GHz. In both differential (Figure 77 to Figure 79) and single-ended (Figure 80 to Figure 82) configurations, the total LO power was swept from -10 dBm to +6 dBm. In differential mode, the amplitude was the sum of the LOIP and LOIN inputs.

Figure 77. LO Differential Input, Output Power ( $P_{OUT}$ ) vs. RF Frequency ( $f_{RF}$ ) at Three Gain Settings for Various LO Inputs, BB I/Q Amplitude = -15 dBm

Figure 78. LO Differential Input, Third-Order Intermodulation Distortion (IMD3) vs. RF Frequency ( $f_{RF}$ ) at a 10 dB Gain Setting ( $P_{OUT} \approx -5$  dBm per Tone)

Figure 79. LO Differential Input, Sideband Suppression vs. RF Frequency ( $f_{RF}$ )

Before Nulling

Figure 80. LO Single-Ended Input, Output Power ( $P_{OUT}$ ) vs. RF Frequency ( $f_{RF}$ ) at Three Gain Settings for Various LO Inputs, BB I/Q Amplitude = -15 dBm

Figure 81.LO Single-Ended Input, Third-Order Intermodulation Distortion (IMD3) vs. RF Frequency ( $f_{\mathbb{R}^{2}}$ ) at a 10 dB Gain Setting ( $P_{OUT} \approx -5$  dBm per Tone)

Figure 82. LO Single-Ended Input, Sideband Suppression vs. RF Frequency  $(f_{RF})$  Before Nulling

# **REGISTER SUMMARY**

Table 7. Register Summary

| Hex  |                    |        | Bit 15                    | Bit 14                         | Bit 13                    | Bit 12                      | Bit 11                     | Bit 10            | Bit 9                 | Bit 8                |        |     |  |  |

|------|--------------------|--------|---------------------------|--------------------------------|---------------------------|-----------------------------|----------------------------|-------------------|-----------------------|----------------------|--------|-----|--|--|

| Addr | Name               | Bits   | Bit 7                     | Bit 6                          | Bit 5                     | Bit 4                       | Bit 3                      | Bit 2             | Bit 1                 | Bit 0                | Reset  | R/W |  |  |

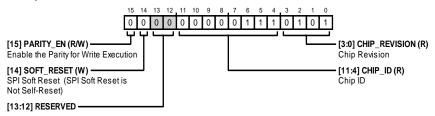

| 0x00 | Control            | [15:8] | PARITY_EN                 | SOFT_RESET                     | SET RESERVED CHIP_ID[7:4] |                             |                            |                   | 0x0075                | R/W                  |        |     |  |  |

|      |                    | [7:0]  |                           | CHIP                           | IP_ID[3:0] CHIP_REVISION  |                             |                            |                   |                       |                      |        |     |  |  |

| 0x01 | ALARM_<br>READBACK | [15:8] | PARITY_<br>ERROR          | TOO_FEW_<br>ERRORS             | TOO_MANY_<br>ERRORS       | ADDRESS_<br>RANGE_<br>ERROR | RESERVED                   |                   |                       |                      | 0x0000 | R   |  |  |

|      |                    | [7:0]  |                           |                                |                           | RESERVED                    | )                          |                   |                       |                      |        |     |  |  |

| 0x02 | ALARM_MASK         | [15:8] | PARITY_<br>ERROR_<br>MASK | TOO_FEW_<br>ERRORS_<br>MASK    | RS_ ERRORS_ RANGE_        |                             |                            | RESERVED          |                       |                      |        | R/W |  |  |

|      |                    | [7:0]  |                           |                                |                           | RESERVED                    | )                          |                   |                       |                      |        |     |  |  |

| 0x03 | Enable             | [15:8] |                           | RESERVED VGA_BUFFER_<br>ENABLE |                           |                             |                            |                   | VGA_BUFFER_<br>ENABLE | 0x0157               | R/W    |     |  |  |

|      |                    | [7:0]  | DETECTOR_<br>ENABLE       | LO_BUFFER_<br>ENABLE           | IF_MODE_<br>ENABLE        | IQ_MODE_<br>ENABLE          | LO_X2_<br>ENABLE           | LO_PPF_<br>ENABLE | LO_<br>ENABLE         | UC_BIAS_<br>ENABLE   |        |     |  |  |

| 0x04 | Linearize          | [15:8] |                           |                                | RESERVED                  |                             |                            |                   |                       | 0x0080               | R/W    |     |  |  |

|      |                    | [7:0]  |                           |                                |                           | RDAC_LINEA                  | RIZE                       |                   |                       |                      |        |     |  |  |

| 0x05 | LO_PATH            | [15:8] |                           |                                | RESERVED                  |                             | LO_ RESERVED<br>SIDEBAND   |                   |                       |                      | 0x0000 | R/W |  |  |

|      |                    | [7:0]  |                           | Q_PATH_PH                      | ASE_ACCURACY              |                             |                            | I_PATH_PH         | ASE_ACCUR             | ACY                  |        |     |  |  |

| 0x06 | ADC_<br>CONTROL    | [15:8] | RESERVED                  |                                |                           |                             |                            |                   |                       | 0x0000               | R/W    |     |  |  |

|      |                    | [7:0]  |                           | RES                            | ERVED                     |                             | VDET_<br>OUTPUT_<br>SELECT | ADC_<br>START     | ADC_<br>ENABLE        | ADC_CLOCK_<br>ENABLE |        |     |  |  |

| 0x0C | ADC_OUTPUT         | [15:8] |                           |                                | F                         | RESERVED                    |                            |                   |                       | ADC_STATUS           | 0x0010 | R   |  |  |

|      |                    | [7:0]  |                           |                                |                           | ADC_VALU                    | JE                         |                   |                       |                      | 7      |     |  |  |

## **REGISTER DETAILS: WIDEBAND UPCONVERTER**

#### **CONTROL REGISTER**

Address: 0x00, Reset: 0x0075, Name: Control

**Table 8. Bit Descriptions for Control**

| Bits    | Bit Name      | Settings | Description                                       | Reset | Access |

|---------|---------------|----------|---------------------------------------------------|-------|--------|

| 15      | PARITY_EN     |          | Enable the Parity for Write Execution             | 0x0   | R/W    |

| 14      | SOFT_RESET    |          | SPI Soft Reset (SPI Soft Reset is Not Self-Reset) | 0x0   | W      |

| [13:12] | RESERVED      |          | Reserved                                          | 0x0   | R/W    |

| [11:4]  | CHIP_ID       |          | Chip ID                                           | 0x7   | R      |

| [3:0]   | CHIP_REVISION |          | Chip Revision                                     | 0x5   | R      |

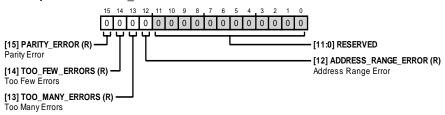

#### **ALARM READBACK REGISTER**

Address: 0x01, Reset: 0x0000, Name: ALARM\_READBACK

Table 9. Bit Descriptions for ALARM\_READBACK

| Bits   | Bit Name            | Settings | Description         | Reset | Access |

|--------|---------------------|----------|---------------------|-------|--------|

| 15     | PARITY_ERROR        |          | Parity Error        | 0x0   | R      |

| 14     | TOO_FEW_ERRORS      |          | Too Few Errors      | 0x0   | R      |

| 13     | TOO_MANY_ERRORS     |          | Too Many Errors     | 0x0   | R      |

| 12     | ADDRESS_RANGE_ERROR |          | Address Range Error | 0x0   | R      |

| [11:0] | RESERVED            |          | Reserved            | 0x0   | R      |

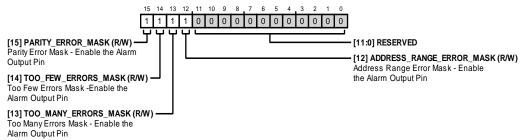

#### ALARM\_MASK REGISTER

Address: 0x02, Reset: 0xFFFF, Name: ALARM\_MASK

Table 10. Bit Descriptions for ALARM\_MASK

| Bits   | Bit Name                 | Settings | Description                                          | Reset | Access |

|--------|--------------------------|----------|------------------------------------------------------|-------|--------|

| 15     | PARITY_ERROR_MASK        |          | Parity Error Mask—Enable the Alarm Output Pin        | 0x1   | R/W    |

| 14     | TOO_FEW_ERRORS_MASK      |          | Too Few Errors Mask—Enable the Alarm Output Pin      | 0x1   | R/W    |

| 13     | TOO_MANY_ERRORS_MASK     |          | Too Many Errors Mask—Enable the Alarm Output Pin     | 0x1   | R/W    |

| 12     | ADDRESS_RANGE_ERROR_MASK |          | Address Range Error Mask—Enable the Alarm Output Pin | 0x1   | R/W    |

| [11:0] | RESERVED                 |          | Reserved                                             | 0xFFF | R/W    |

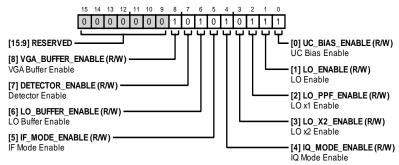

#### **ENABLE REGISTER**

Address: 0x03, Reset: 0x0157, Name: Enable

Table 11. Bit Descriptions for Enable

| Bits   | Bit Name          | Settings | Description       | Reset | Access |

|--------|-------------------|----------|-------------------|-------|--------|

| [15:9] | RESERVED          |          | Reserved          | 0x0   | R/W    |

| 8      | VGA_BUFFER_ENABLE |          | VGA Buffer Enable | 0x1   | R/W    |

| 7      | DETECTOR_ENABLE   |          | Detector Enable   | 0x0   | R/W    |

| 6      | LO_BUFFER_ENABLE  |          | LO Buffer Enable  | 0x1   | R/W    |

| 5      | IF_MODE_ENABLE    |          | IF Mode Enable    | 0x0   | R/W    |

| 4      | IQ_MODE_ENABLE    |          | IQ Mode Enable    | 0x1   | R/W    |

| 3      | LO_X2_ENABLE      |          | LO ×2 Enable      | 0x0   | R/W    |

| 2      | LO_PPF_ENABLE     |          | LO ×1 Enable      | 0x1   | R/W    |

| 1      | LO_ENABLE         |          | LO Enable         | 0x1   | R/W    |

| 0      | UC_BIAS_ENABLE    |          | UC Bias Enable    | 0x1   | R/W    |

#### **LINEARIZE REGISTER**

Address: 0x04, Reset: 0x0080, Name: Linearize

**Table 12. Bit Descriptions for Linearize**

| Bits   | Bit Name       | Settings | Description                                             |      | Access |

|--------|----------------|----------|---------------------------------------------------------|------|--------|

| [15:8] | RESERVED       |          | Reserved                                                | 0x0  | R/W    |

| [7:0]  | RDAC_LINEARIZE |          | RDAC 8 Bits: for IMD Performance Improvement (0 to 255) | 0x80 | R/W    |

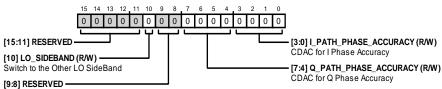

#### LO\_PATH REGISTER

Address: 0x05, Reset: 0x0000, Name: LO\_PATH

Table 13. Bit Descriptions for LO\_PATH

| Bits    | Bit Name              | Settings | Description                     | Reset | Access |

|---------|-----------------------|----------|---------------------------------|-------|--------|

| [15:11] | RESERVED              |          | Reserved                        | 0x0   | R/W    |

| 10      | LO_SIDEBAND           |          | Switch to the Other LO Sideband | 0x0   | R/W    |

| [9:8]   | RESERVED              |          | Reserved                        | 0x0   | R/W    |

| [7:4]   | Q_PATH_PHASE_ACCURACY |          | CDAC for Q Phase Accuracy       | 0x0   | R/W    |

| [3:0]   | I_PATH_PHASE_ACCURACY |          | CDAC for I Phase Accuracy       | 0x0   | R/W    |

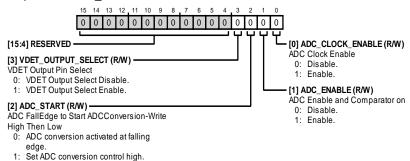

#### **ADC\_CONTROL REGISTER**

Address: 0x06, Reset: 0x0000, Name: ADC\_CONTROL

Table 14. Bit Descriptions for ADC\_CONTROL

| Bits   | Bit Name           | Settings | Description                                               | Reset | Access |

|--------|--------------------|----------|-----------------------------------------------------------|-------|--------|

| [15:4] | RESERVED           |          | Reserved                                                  | 0x0   | R/W    |

| 3      | VDET_OUTPUT_SELECT |          | VDET Output Pin Select                                    | 0x0   | R/W    |

|        |                    | 0        | VDET Output Select Disable                                |       |        |

|        |                    | 1        | VDET Output Select Enable                                 |       |        |

| 2      | ADC_START          |          | ADC Fall Edge to Start ADC Conversion Write High Then Low | 0x0   | R/W    |

|        |                    | 0        | ADC Conversion Activated at Falling Edge                  |       |        |

|        |                    | 1        | Set ADC conversion control High                           |       |        |

| 1      | ADC_ENABLE         |          | ADC Enable and Comparator On                              | 0x0   | R/W    |

|        |                    | 0        | Disable                                                   |       |        |

|        |                    | 1        | Enable                                                    |       |        |

| 0      | ADC_CLOCK_ENABLE   |          | ADC Clock Enable                                          | 0x0   | R/W    |

|        |                    | 0        | Disable                                                   |       |        |

|        |                    | 1        | Enable                                                    |       |        |

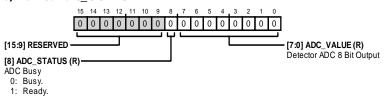

#### **ADC\_OUTPUT REGISTER**

Address: 0x0C, Reset: 0x0010, Name: ADC\_OUTPUT

Table 15. Bit Descriptions for ADC\_OUTPUT

| Bits   | Bit Name   | Settings | Description               | Reset | Access |

|--------|------------|----------|---------------------------|-------|--------|

| [15:9] | RESERVED   |          | Reserved                  | 0x0   | R/W    |

| 8      | ADC_STATUS |          | ADC Busy                  | 0x0   | R      |

|        |            | 0        | Busy                      |       |        |

|        |            | 1        | Ready                     |       |        |

| [7:0]  | ADC_VALUE  |          | Detector ADC 8-Bit Output | 0x0   | R      |

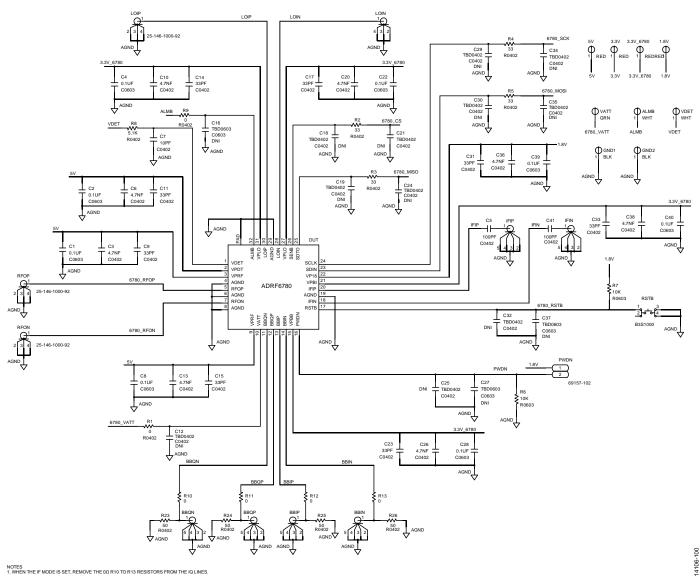

# **BASIC CONNECTIONS FOR OPERATION**

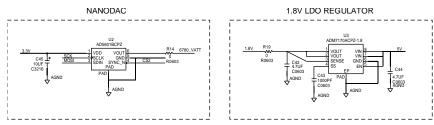

Figure 83 to Figure 85 show the basic connections for operating the ADRF6780 as it is implemented on the evaluation board of the device.

Figure 83. ADRF6780 Evaluation Board Schematic Page 1

Figure 84. ADRF6780 Evaluation Board Schematic Page 2

Figure 85. ADRF6780 Evaluation Board Schematic Page 3

**Table 16. Evaluation Board Configuration Options**

| Table 10. Evaluation Board Configuration O                                                                                         | ptions                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                   |