# **Contents**

| 1 | Bloc               | k diagra  | am                                   | 7  |

|---|--------------------|-----------|--------------------------------------|----|

| 2 | Pin o              | descripti | ion                                  | 8  |

|   | 2.1                | Pinout    |                                      | 8  |

|   | 2.2                | Pin list  |                                      | 9  |

| 3 | Elec               | trical sp | pecifications                        | 11 |

|   | 3.1                | Absolut   | te maximum ratings                   | 11 |

|   | 3.2                | Therma    | al data                              | 11 |

|   | 3.3                | Recom     | mended operating conditions          | 12 |

|   | 3.4                | Electric  | cal specifications - digital section | 12 |

|   | 3.5                | Electric  | cal specifications - power section   | 12 |

|   | 3.6                | Power-    | on/off sequences                     | 15 |

|   | 3.7                | Testing   | l                                    | 16 |

| 4 | Fund               | ctional d | lescription                          | 17 |

|   | 4.1                | Functio   | onal pins                            | 17 |

|   |                    | 4.1.1     | Power-down function                  | 17 |

|   |                    | 4.1.2     | Reset function                       | 17 |

|   | 4.2                | Serial a  | audio interface description          | 18 |

|   |                    | 4.2.1     | Serial audio interface protocols     | 18 |

| 5 | I <sup>2</sup> C b | ous spec  | cification                           | 19 |

|   | 5.1                | Commu     | unication protocol                   | 19 |

|   |                    | 5.1.1     | Data transition or change            | 19 |

|   |                    | 5.1.2     |                                      |    |

|   |                    | 5.1.3     | Stop condition                       |    |

|   |                    | 5.1.4     | Data input                           |    |

|   | 5.2                |           | addressing                           |    |

|   | 5.3                |           | peration                             |    |

|   |                    | 5.3.1     | Byte write                           |    |

|   | - 4                | 5.3.2     | Multi-byte write                     |    |

|   | 5.4                | Read o    | pperation                            | 20 |

### **STA380WS**

|   |         | 5.4.1    | Current address byte read                             | 20   |

|---|---------|----------|-------------------------------------------------------|------|

|   |         | 5.4.2    | Current address multi-byte read                       | 20   |

|   |         | 5.4.3    | Random address byte read                              | 20   |

|   |         | 5.4.4    | Random address multi-byte read                        | 21   |

| 6 | Regis   | ter des  | cription                                              | 22   |

|   | 6.1     | Configu  | ration registers (addr 0x00 to 0x05)                  | 23   |

|   |         | 6.1.1    | Configuration register A (addr 0x00)                  | 23   |

|   |         | 6.1.2    | Configuration register B (addr 0x01)                  | 25   |

|   |         | 6.1.3    | Configuration register C (addr 0x02)                  | 28   |

|   |         | 6.1.4    | Configuration register D (addr 0x03)                  | 29   |

|   |         | 6.1.5    | Configuration register E (addr 0x04)                  | 29   |

|   |         | 6.1.6    | Configuration register F (addr 0x05)                  | 31   |

|   | 6.2     | Volume   | control registers (addr 0x06 to 0x09)                 | 33   |

|   |         | 6.2.1    | Mute/line output configuration register (addr 0x06)   | 33   |

|   |         | 6.2.2    | Master volume register (addr 0x07)                    |      |

|   |         | 6.2.3    | Channel volume (addr 0x08, 0x09)                      |      |

|   | 6.3     | Automo   | de register (0x0C)                                    | 35   |

|   | 6.4     | Channe   | l configuration registers (addr 0x0E, 0x0F)           | 36   |

|   | 6.5     | Variable | e max power correction registers (addr 0x27, 0x28)    | 36   |

|   | 6.6     | Variable | e distortion compensation registers (addr 0x29, 0x2A) | 37   |

|   | 6.7     | Fault de | etect recovery constant registers (addr 0x2B, 0x2C)   | 37   |

|   | 6.8     | Device   | status register (addr 0x2D)                           | 37   |

|   | 6.9     | Reserve  | ed registers (addr 0x2E, 0x2F, 0x30, 0x31)            | 38   |

|   | 6.10    | Postsca  | ıle registers (addr 0x32, 0x33)                       | 38   |

|   | 6.11    |          | limit register (addr 0x34)                            |      |

|   | <b></b> | 6.11.1   | Thermal and overcurrent warning output limit register |      |

| 7 | Annli   | nation i | nformation                                            | 40   |

| , |         |          |                                                       |      |

|   | 7.1     |          | ion scheme for power supplies                         |      |

|   | 7.2     |          | эг                                                    |      |

|   | 7.3     | Typical  | output configuration                                  | 41   |

| 8 | Chara   | cteriza  | tion data                                             | 42   |

| 9 | Packa   | age med  | chanical data                                         | 45   |

|   |         |          | DocID024426 Rev 1                                     | 3/48 |

| 1 N | Revision history | A | 17  |

|-----|------------------|---|-----|

| IU  | KENISIOH HISIOIV |   | t / |

STA380WS List of tables

# List of tables

| Table 1.               | Device summary                                                 | . 1 |

|------------------------|----------------------------------------------------------------|-----|

| Table 2.               | Pin description                                                |     |

| Table 3.               | Absolute maximum ratings                                       |     |

| Table 4.               | Thermal data                                                   |     |

| Table 5.               | Recommended operating conditions                               |     |

| Table 6.               | Electrical characteristics for digital section                 |     |

| Table 7.               | Electrical specifications for power section                    |     |

| Table 8.               | Register summary                                               |     |

| Table 9.               | Master clock select                                            |     |

| Table 10.              | MCS bits                                                       | 23  |

| Table 11.              | Interpolation ratio select                                     | 24  |

| Table 12.              | IR bit settings as a function of input sample rate             | 24  |

| Table 13.              | Thermal warning recovery                                       | 24  |

| Table 14.              | Thermal warning adjustment                                     | 25  |

| Table 15.              | Fault detect recovery                                          | 25  |

| Table 16.              | Serial audio input interface format                            | 26  |

| Table 17.              | Serial data first bit                                          |     |

| Table 18.              | Support serial audio input formats for MSB first (SAIFB = 0)   |     |

| Table 19.              | Supported serial audio input formats for LSB-first (SAIFB = 1) |     |

| Table 20.              | Channel input mapping                                          |     |

| Table 21.              | FFX power output mode                                          |     |

| Table 22.              | FFX compensating pulse size                                    |     |

| Table 23.              | Overcurrent warning detect adjustment bypass                   |     |

| Table 24.              | Zero detect mute enable                                        |     |

| Table 25.              | Max power correction variable                                  |     |

| Table 26.              | Max power correction                                           |     |

| Table 27.              | Noise-shaper bandwidth selection                               |     |

| Table 28.              | AM mode enable                                                 |     |

| Table 29.              | PWM speed mode                                                 |     |

| Table 30.              | Distortion compensation variable enable                        |     |

| Table 31.              | Zero-crossing volume enable                                    |     |

| Table 32.              | Soft volume update enable                                      |     |

| Table 33.              | Invalid input detect mute enable                               |     |

| Table 34.<br>Table 35. |                                                                |     |

| Table 35.              | LRCK double trigger protection                                 |     |

| Table 36.              | Power-down                                                     |     |

| Table 37.              | External amplifier power-down                                  |     |

| Table 39.              | Master mute                                                    |     |

| Table 39.              | Channel mute                                                   |     |

| Table 41.              | Master volume offset as a function of MV                       |     |

| Table 42.              | Channel volume as a function of CxV                            |     |

| Table 43.              | AM interference frequency switching                            |     |

| Table 44.              | Automode AM switching frequency selection                      |     |

| Table 45.              | Status bits description.                                       |     |

| Table 46.              | Output limit values for thermal and overcurrent warnings       |     |

| Table 47.              | Document revision history                                      |     |

|                        | ,                                                              |     |

List of figures STA380WS

# List of figures

| Figure 1.  | Block diagram                                        | 7    |

|------------|------------------------------------------------------|------|

| Figure 2.  | Pin connections (package top view)                   |      |

| Figure 3.  | Power-on sequence                                    | . 15 |

| Figure 4.  | Power-off sequence                                   | . 15 |

| Figure 5.  | Test circuit                                         | . 16 |

| Figure 6.  | Current dead-time test circuit                       | . 16 |

| Figure 7.  | l <sup>2</sup> S                                     | . 18 |

| Figure 8.  | Left justified                                       | . 18 |

| Figure 9.  | Write mode sequence                                  | . 20 |

| Figure 10. | Read mode sequence                                   | . 21 |

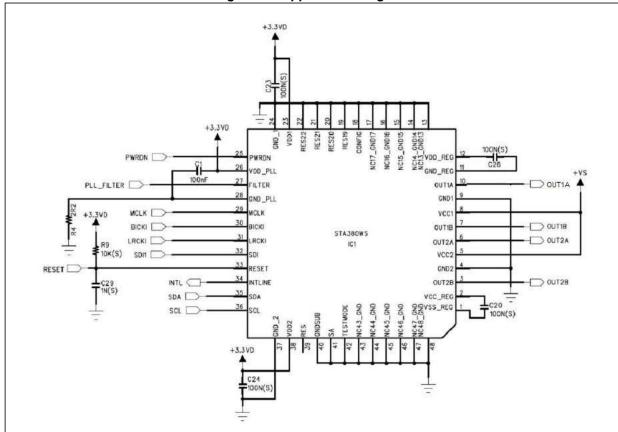

| Figure 11. | Application diagram                                  | . 40 |

| Figure 12. | PLL filter circuit                                   | . 41 |

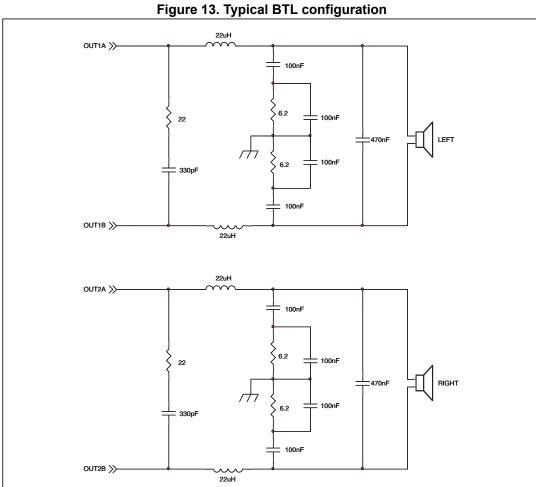

| Figure 13. | Typical BTL configuration                            | . 41 |

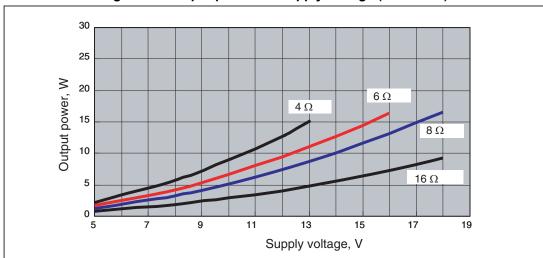

| Figure 14. | Output power vs. supply voltage (THD = 1%)           | . 42 |

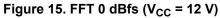

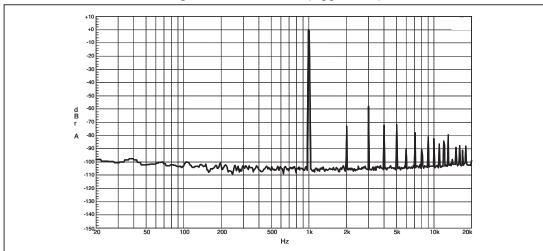

| Figure 15. | FFT 0 dBfs (V <sub>CC</sub> = 12 V)                  | . 42 |

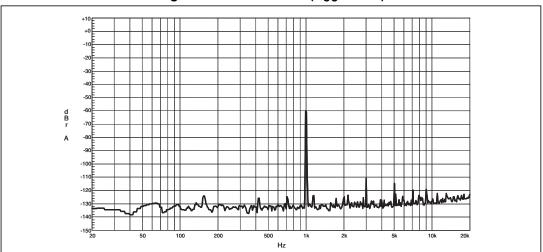

| Figure 16. | FFT -60 dBfs (V <sub>CC</sub> = 12 V)                | . 43 |

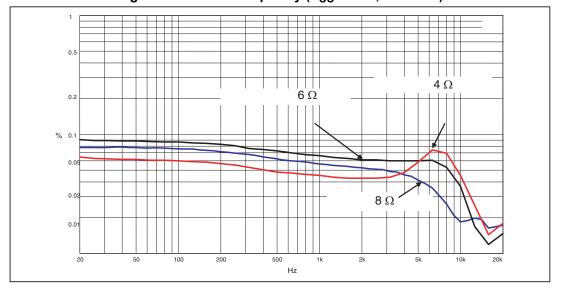

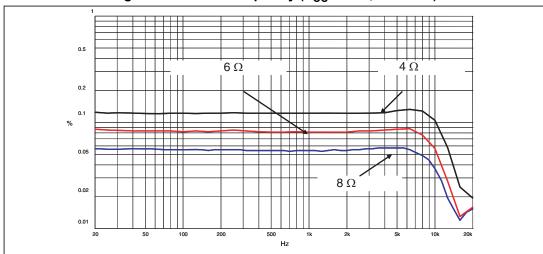

| Figure 17. | THD vs. frequency (V <sub>CC</sub> = 12 V, Po = 1 W) |      |

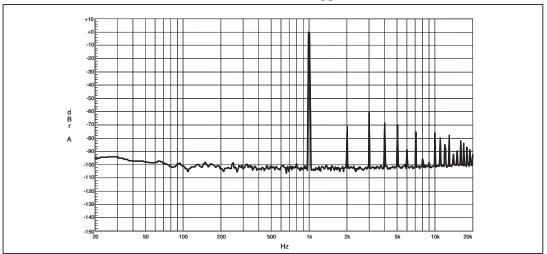

| Figure 18. | FFT 0 dBfs (V <sub>CC</sub> = 18 V)                  |      |

| Figure 19. | FFT -60 dBfs (V <sub>CC</sub> = 18 V)                |      |

| Figure 20. | THD vs. frequency (V <sub>CC</sub> = 18 V, Po = 1 W) | . 44 |

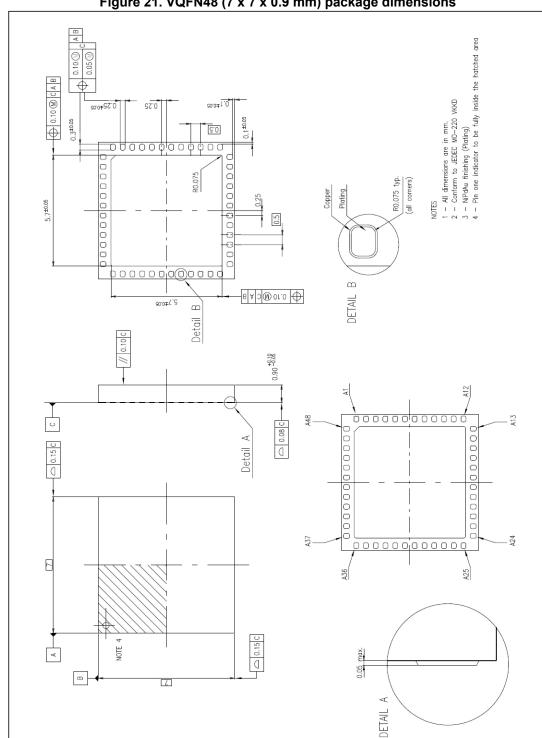

| Figure 21  | VOEN48 (7 x 7 x 0 9 mm) nackage dimensions           | 45   |

STA380WS Block diagram

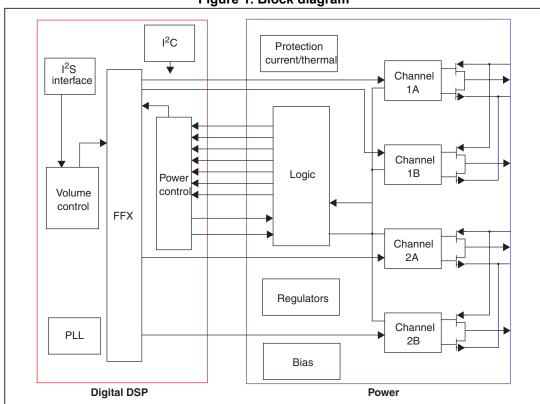

# 1 Block diagram

Figure 1. Block diagram

Pin description STA380WS

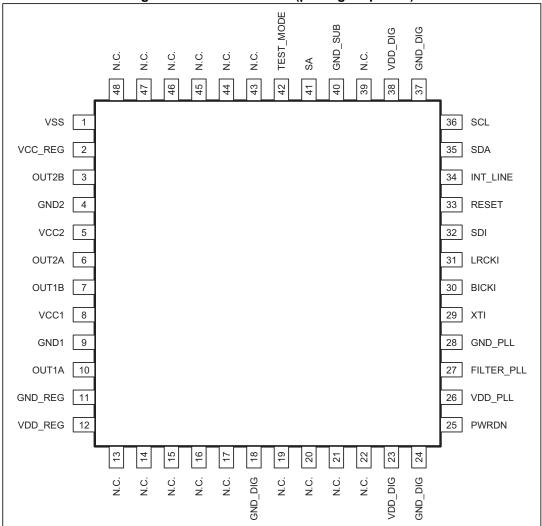

# 2 Pin description

## 2.1 Pinout

Figure 2. Pin connections (package top view)

8/48 DocID024426 Rev 1

STA380WS Pin description

# 2.2 Pin list

Table 2. Pin description

| Number | Туре | Name       | Description                                                                                                                                     |

|--------|------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | I/O  | VSS        | Internal reference at V <sub>CC</sub> - 3.3 V                                                                                                   |

| 2      | I/O  | VCC_REG    | Internal V <sub>CC</sub> reference                                                                                                              |

| 3      | 0    | OUT2B      | Output half-bridge 2B                                                                                                                           |

| 4      | PWR  | GND2       | Power negative supply                                                                                                                           |

| 5      | PWR  | VCC2       | Power positive supply                                                                                                                           |

| 6      | 0    | OUT2A      | Output half-bridge 2A                                                                                                                           |

| 7      | 0    | OUT1B      | Output half-bridge 1B                                                                                                                           |

| 8      | PWR  | VCC1       | Power positive supply                                                                                                                           |

| 9      | PWR  | GND1       | Power negative supply                                                                                                                           |

| 10     | 0    | OUT1A      | Output half-bridge 1A                                                                                                                           |

| 11     | PWR  | GND_REG    | Internal ground reference                                                                                                                       |

| 12     | PWR  | VDD_REG    | Internal 3.3-V reference voltage                                                                                                                |

| 13     | -    | N.C.       | No internal connection                                                                                                                          |

| 14     | -    | N.C.       | No internal connection                                                                                                                          |

| 15     | -    | N.C.       | No internal connection                                                                                                                          |

| 16     | -    | N.C.       | No internal connection                                                                                                                          |

| 17     | -    | N.C.       | No internal connection                                                                                                                          |

| 18     | PWR  | GND_DIG    | Digital ground                                                                                                                                  |

| 19     | -    | N.C.       | No internal connection                                                                                                                          |

| 20     | -    | N.C.       | No internal connection                                                                                                                          |

| 21     | -    | N.C.       | No internal connection                                                                                                                          |

| 22     | -    | N.C.       | No internal connection                                                                                                                          |

| 23     | PWR  | VDD_DIG    | Positive supply digital                                                                                                                         |

| 24     | PWR  | GND_DIG    | Digital ground                                                                                                                                  |

| 25     | I    | PWRDN      | Power down: 0: power stage is switched off then the PLL is also switched off (this operation takes 13 million clock cycles) 1: normal operation |

| 26     | PWR  | VDD_PLL    | Positive supply for PLL                                                                                                                         |

| 27     | I    | FILTER_PLL | Connection to PLL filter                                                                                                                        |

| 28     | PWR  | GND_PLL    | Negative supply for PLL                                                                                                                         |

| 29     | I    | XTI        | PLL input clock, 256 * f <sub>S</sub> , or 384 * f <sub>S</sub>                                                                                 |

| 30     | I    | BICKI      | I <sup>2</sup> S serial clock                                                                                                                   |

| 31     | I    | LRCKI      | I <sup>2</sup> S left/right clock                                                                                                               |

Pin description STA380WS

Table 2. Pin description (continued)

| Number | Туре | Name      | Description                                                                                                    |

|--------|------|-----------|----------------------------------------------------------------------------------------------------------------|

| 32     | I    | SDI       | I <sup>2</sup> S serial data channel                                                                           |

| 33     | I    | RESET     | Reset: 0: reset state, power stage is switched off, all registers are set to default value 1: normal operation |

| 34     | 0    | INT_LINE  | Fault interrupt                                                                                                |

| 35     | I/O  | SDA       | I <sup>2</sup> C serial data                                                                                   |

| 36     | I    | SCL       | I <sup>2</sup> C serial clock                                                                                  |

| 37     | PWR  | GND_DIG   | Digital ground                                                                                                 |

| 38     | PWR  | VDD_DIG   | Digital supply                                                                                                 |

| 39     | -    | N.C.      | No internal connection                                                                                         |

| 40     | PWR  | GND_SUB   | Substrate ground                                                                                               |

| 41     | I    | SA        | I <sup>2</sup> C select address                                                                                |

| 42     | I    | TEST_MODE | This pin must be connected to ground                                                                           |

| 43     | -    | N.C.      | No internal connection                                                                                         |

| 44     | -    | N.C.      | No internal connection                                                                                         |

| 45     | -    | N.C.      | No internal connection                                                                                         |

| 46     | -    | N.C.      | No internal connection                                                                                         |

| 47     | -    | N.C.      | No internal connection                                                                                         |

| 48     | -    | N.C.      | No internal connection                                                                                         |

| -      | -    | EP        | Exposed pad for ground-plane heatsink, to be connected to GND                                                  |

Note: To increase thermal dissipation, all N.C. (no internal connection) pins must be connected to GND.

10/48 DocID024426 Rev 1

# 3 Electrical specifications

## 3.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol           | Parameter                             | Min  | Тур | Max | Unit |

|------------------|---------------------------------------|------|-----|-----|------|

| V <sub>CC</sub>  | Analog supply voltage (pins VCCx)     | -    | -   | 23  | V    |

| $V_{DD}$         | Digital supply voltage (pins VDD_DIG) | -    | -   | 4.0 | ٧    |

| IL               | Logic input interface                 | -0.3 | -   | 4.0 | ٧    |

| T <sub>op</sub>  | Operating junction temperature        | 0    | -   | 150 | °C   |

| T <sub>stg</sub> | Storage temperature                   | -40  | -   | 150 | °C   |

#### Warning:

Stresses beyond those listed in *Table 3: Absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in *Table 5: Recommended operating conditions* are not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability. In the real application, a power supply with nominal value rated within the limits of the recommended operating conditions, may rise beyond the maximum operating conditions for a short time when no or very low current is being sunk (amplifier in mute state). In this case the reliability of the device is guaranteed, provided that the absolute maximum ratings are not exceeded.

### 3.2 Thermal data

Table 4. Thermal data

| Symbol                  | Parameter                                         |     | Тур | Max | Unit |

|-------------------------|---------------------------------------------------|-----|-----|-----|------|

| R <sub>Th(j-case)</sub> | Thermal resistance junction to case (thermal pad) | -   | -   | 1.5 | °C/W |

| T <sub>sd</sub>         | Thermal-shutdown junction temperature             | 140 | 150 | 160 | °C   |

| T <sub>w</sub>          | Thermal-warning temperature                       | -   | 130 | -   | °C   |

| T <sub>hsd</sub>        | Thermal-shutdown hysteresis                       | 18  | 20  | 22  | °C   |

## 3.3 Recommended operating conditions

Table 5. Recommended operating conditions

| Symbol           | Parameter                        | Min | Тур | Max  | Unit |

|------------------|----------------------------------|-----|-----|------|------|

| V <sub>CC</sub>  | Analog supply voltage (VCCx)     | 4.5 | -   | 20.0 | V    |

| V <sub>DD</sub>  | Digital supply voltage (VDD_DIG) | 2.7 | 3.3 | 3.6  | V    |

| IL               | Logic input interface            | 2.7 | 3.3 | 3.6  | V    |

| T <sub>amb</sub> | Ambient temperature              | 0   | -   | 70   | °C   |

# 3.4 Electrical specifications - digital section

Table 6. Electrical characteristics for digital section

| Symbol          | Parameter                     | Conditions                               | Min                      | Тур | Max                      | Unit |

|-----------------|-------------------------------|------------------------------------------|--------------------------|-----|--------------------------|------|

| I <sub>il</sub> | Input current, no pull-up or  | V <sub>i</sub> = 0 V                     | -                        | -   | ±10                      | μΑ   |

| I <sub>ih</sub> | pull-down resistor            | V <sub>i</sub> = V <sub>DD</sub> = 3.6 V | -                        | -   | ±10                      | μΑ   |

| V <sub>il</sub> | Low-level input voltage       | -                                        | -                        | -   | 0.2 *<br>V <sub>DD</sub> | V    |

| V <sub>ih</sub> | High-level input voltage      | -                                        | 0.8 *<br>V <sub>DD</sub> | -   | -                        | V    |

| V <sub>ol</sub> | Low-level output voltage      | I <sub>ol</sub> = 2 mA                   | -                        | -   | 0.4 *<br>V <sub>DD</sub> | V    |

| V <sub>oh</sub> | High-level output voltage     | I <sub>oh</sub> = 2 mA                   | 0.8 *<br>V <sub>DD</sub> | -   | -                        | V    |

| I <sub>pu</sub> | Pull-up current               | -                                        | 25                       | 66  | 125                      | μΑ   |

| R <sub>pu</sub> | Equivalent pull-up resistance | -                                        | -                        | 50  | -                        | kΩ   |

# 3.5 Electrical specifications - power section

The specifications in *Table 7* below are given for the conditions  $V_{CC}$  = 18 V,  $V_{DD}$  = 3.3 V,  $f_{SW}$  = 384 kHz,  $T_{amb}$  = 25 °C and  $R_L$  = 8  $\Omega$ , unless otherwise specified.

Table 7. Electrical specifications for power section

| Symbol            | Parameter                                       | Conditions             | Min | Тур | Max | Unit |

|-------------------|-------------------------------------------------|------------------------|-----|-----|-----|------|

| Ро                | Output power BTL                                | THD = 1%               | -   | 16  | -   | W    |

|                   | Output power BTL                                | THD = 10%              | -   | 20  | -   | VV   |

| R <sub>dsON</sub> | Power P-channel/N-channel MOSFET (total bridge) | ld = 1 A               | -   | 180 | 250 | mΩ   |

| I <sub>dss</sub>  | Power P-channel/N-channel leakage               | V <sub>CC</sub> = 18 V | -   | -   | 10  | μΑ   |

12/48 DocID024426 Rev 1

Table 7. Electrical specifications for power section (continued)

| Symbol              | Parameter                                          | Conditions                                                                              | Min | Тур  | Max | Unit |

|---------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------|-----|------|-----|------|

| gP                  | Power P-channel R <sub>dsON</sub> matching         | ld = 1 A                                                                                | 95  | -    | -   | %    |

| gN                  | Power N-channel R <sub>dsON</sub> matching         | ld = 1 A                                                                                | 95  | -    | -   | %    |

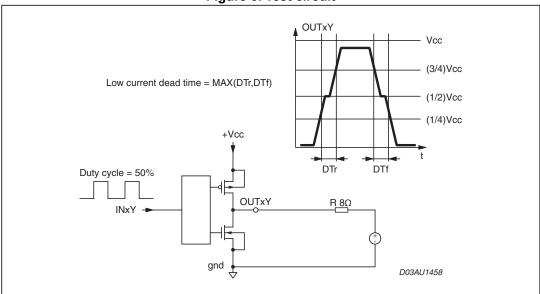

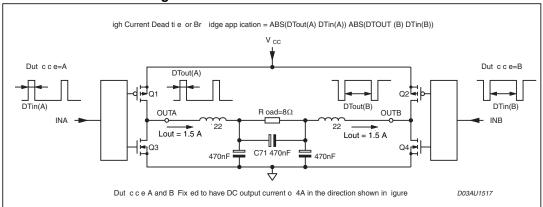

| I <sub>LDT</sub>    | Low-current dead time (static)                     | Resistive load, refer to Figure 5                                                       | -   | 5    | 10  | ns   |

| I <sub>HDT</sub>    | High-current dead time (dynamic)                   | Refer to Figure 6                                                                       | -   | 10   | 20  | ns   |

| t <sub>r</sub>      | Rise time                                          | Resistive load, refer to Figure 5                                                       | -   | 8    | 10  | ns   |

| t <sub>f</sub>      | Fall time                                          | Resistive load, refer to Figure 5                                                       | -   | 8    | 10  | ns   |

| V <sub>CC</sub>     | Supply voltage                                     | -                                                                                       | 4.5 | -    | 20  | V    |

|                     | Supply current from V <sub>CC</sub> in power down  | PWRDN = 0                                                                               | 30  | 60   | 200 | μA   |

| l <sub>vcc</sub>    | Supply current from V <sub>CC</sub> in operation   | PCM input signal = -60 dBfs<br>Switching frequency =<br>384 kHz<br>No LC filters        | -   | 30   | 50  | mA   |

| I <sub>VDD_DI</sub> | Supply current for FFX processing (reference only) | Internal clock = 49.152 MHz                                                             | 10  | 30   | 50  | mA   |

| G                   | Supply current in standby                          | -                                                                                       | 8   | 11   | 25  | mA   |

| I <sub>LIM</sub>    | Overcurrent limit                                  | Non-linear output (1)                                                                   | 2.2 | 3.5  | 4.3 | Α    |

| I <sub>SCP</sub>    | Short-circuit protection                           | High-impedance output (2)                                                               | 2.7 | 3.8  | 5.0 | Α    |

| V <sub>OVP</sub>    | Overvoltage protection threshold                   |                                                                                         |     | 22.9 |     | V    |

| V <sub>UVP</sub>    | Undervoltage protection threshold                  | -                                                                                       | -   | 3.5  | 4.3 | V    |

| t <sub>min</sub>    | Output minimum pulse width                         | No load                                                                                 | 20  | 30   | 60  | ns   |

| THD+N               | Total harmonic distortion and noise                | FFX stereo mode, Po = 1 W, f = 1 kHz                                                    | -   | 0.05 | 0.2 | %    |

| DR                  | Dynamic range                                      | -                                                                                       | -   | 100  | -   | dB   |

| CNID                | Signal-to-noise ratio in ternary mode              | A-weighted                                                                              | -   | 100  | -   | 4D   |

| SNR                 | Signal-to-noise ratio in binary mode               | A-weighted                                                                              | -   | 90   | -   | – dB |

| PSRR                | Power supply rejection ratio                       | FFX stereo mode, < 5 kHz,<br>V <sub>RIPPLE</sub> = 1 V RMS<br>audio input = dither only | -   | 80   | -   | dB   |

Table 7. Electrical specifications for power section (continued)

| Symbol            | Parameter                   | Conditions                                                                           | Min | Тур | Max | Unit |

|-------------------|-----------------------------|--------------------------------------------------------------------------------------|-----|-----|-----|------|

| X <sub>TALK</sub> | Crosstalk                   | FFX stereo mode, < 5 kHz,<br>One channel driven at 1 W<br>the other channel measured | -   | 80  | -   | dB   |

| η                 | Peak efficiency in FFX mode | Po = 2 x 20 W into 8 Ω                                                               | -   | 90  | -   | %    |

The I<sub>LIM</sub> data is for 1 channel of BTL configuration, thus, 2 \* I<sub>LIM</sub> drives the 2-channel BTL configuration.

The current limit is active when OCRB = 0 (see *Table 23: Overcurrent warning detect adjustment bypass on page 29.* When OCRB = 1 then I<sub>SC</sub> applies.

<sup>2.</sup> The I<sub>SCP</sub> current limit data is for 1 channel of BTL configuration, thus, 2 \* I<sub>SCP</sub> drives the 2-channel BTL configuration. The short-circuit current is applicable when OCRB = 1 (see *Table 23: Overcurrent warning detect adjustment bypass on page 29.*

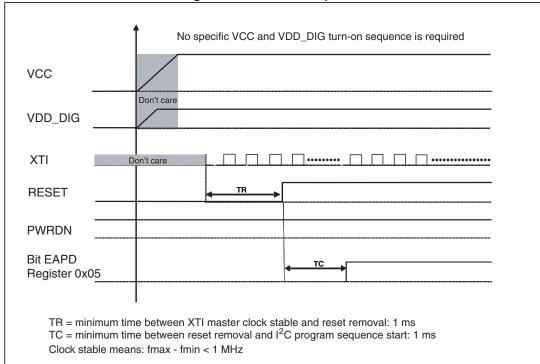

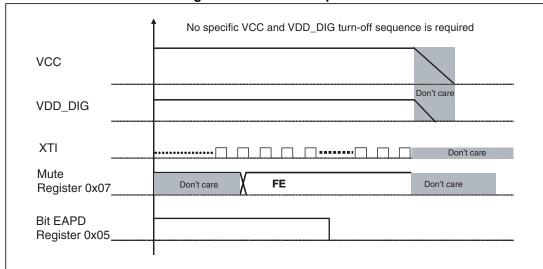

## 3.6 Power-on/off sequences

The power-on/off sequences shown in *Figure 3* and *Figure 4* below ensure a pop-free turn-on and turn-off.

Figure 3. Power-on sequence

47/

# 3.7 Testing

Figure 5. Test circuit

Figure 6. Current dead-time test circuit

# 4 Functional description

## 4.1 Functional pins

#### 4.1.1 Power-down function

Pin PWRDN (23) is used to power down the STA380WS.

PWRDN = 0 (0 V): power-down state

PWRND = 1 ( $V_{DD}$ ): normal operation

During the power-down sequence the output begins to mute. After the mute condition is reached, the power stage is switched off and the output becomes high impedance. Then the master clock to all internal hardware blocks is gated off. The PLL is also switched off. The complete power-down sequence takes 13 million cycles.

#### 4.1.2 Reset function

Pin RESET (31) is used to reset the STA380WS.

RESET = 0 (0 V): reset state

RESET = 1 ( $V_{DD}$ ): normal operation

When pin RESET is forced to 0, the power stage is switched off (with high-impedance output) and the master clock to all internal hardware blocks is gated off.

Note: Reset has a higher priority than power-down.

47/

## 4.2 Serial audio interface description

## 4.2.1 Serial audio interface protocols

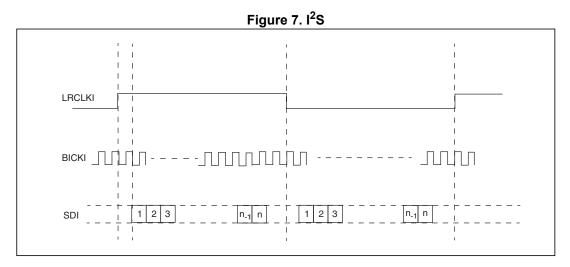

The STA380WS serial audio input was designed to interface with standard digital audio components and to accept serial data formats. The STA380WS always acts as a slave when receiving audio input from standard digital audio components. Serial data for two channels is provided using 3 input pins: left/right clock LRCKI (pin 29), serial clock BICKI (pin 28), and serial data SDI (pin 30).

The available formats are shown in *Table 7* and *Table 8*, and set through *Configuration register B (addr 0x01) on page 25*.

Figure 8. Left justified

STA380WS I<sup>2</sup>C bus specification

# 5 I<sup>2</sup>C bus specification

The STA380WS supports the I<sup>2</sup>C protocol via the input ports SCL and SDA. This protocol defines any device that sends data to the bus as a transmitter and any device that reads the data as a receiver. The device that controls the data transfer is known as the master and the other as the slave. The master always starts the transfer and provides the serial clock for synchronization. The STA380WS is always a slave device in all of its communications. It supports up to 400 kb/s (fast-mode bit rate).

## 5.1 Communication protocol

#### 5.1.1 Data transition or change

Data changes on the SDA line must only occur when the SCL clock is low. An SDA transition while the clock is high is used to identify a START or STOP condition.

#### 5.1.2 Start condition

START is identified by a high to low transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A START condition must precede any command for data transfer.

### 5.1.3 Stop condition

STOP is identified by low to high transition of the data bus SDA signal while the clock signal SCL is stable in the high state. A STOP condition terminates communication between the STA380WS and the bus master.

#### 5.1.4 Data input

During the data input the STA380WS samples the SDA signal on the rising edge of clock SCL. For correct device operation the SDA signal must be stable during the rising edge of the clock and the data can change only when the SCL line is low.

# 5.2 Device addressing

To start communication between the master and the STA380WS, the master must initiate a start condition. Following this, the master sends to the SDA line 8 bits (MSB first) corresponding to the device-select address and read or write mode.

The 7 most significant bits are the device address identifiers, corresponding to the  $I^2C$  bus definition. In the STA380WS the  $I^2C$  interface has two device addresses depending on the SA port configuration, 0x38 when SA = 0, and 0x3A when SA = 1.

The 8th bit (LSB) identifies read or write operation RW, this bit is set to 1 for read mode and 0 for write mode. After a START condition the STA380WS identifies the device address on the SDA bus and if a match is found, acknowledges the identification during the 9th bit time. The byte following the device identification byte is the internal space address.

DocID024426 Rev 1 19/48

## 5.3 Write operation

Following the START condition the master sends a device select code with the RW bit set to 0. The STA380WS acknowledges this and then waits for the byte of internal address. After receiving the internal byte address the STA380WS again responds with an acknowledgement.

#### 5.3.1 Byte write

In the byte write mode the master sends one data byte which is acknowledged by the STA380WS. The master then terminates the transfer by generating a STOP condition.

#### 5.3.2 Multi-byte write

The multi-byte write modes can start from any internal address. The master generating a STOP condition terminates the transfer.

BYTE DEV-ADDR SUB-ADDR DATAIN

START RW STOP

ACK ACK ACK ACK ACK

MULTIBYTE DEV-ADDR SUB-ADDR DATAIN

START RW STOP

ACK ACK ACK ACK ACK

SUB-ADDR DATAIN

STOP

Figure 9. Write mode sequence

# 5.4 Read operation

#### 5.4.1 Current address byte read

Following the START condition the master sends a device select code with the RW bit set to 1. The STA380WS acknowledges this and then responds by sending one byte of data. The master then terminates the transfer by generating a STOP condition.

#### 5.4.2 Current address multi-byte read

The multi-byte read modes can start from any internal address. Sequential data bytes are read from sequential addresses within the STA380WS. The master acknowledges each data byte read and then generates a STOP condition terminating the transfer.

#### 5.4.3 Random address byte read

Following the START condition the master sends a device select code with the RW bit set to 0. The STA380WS acknowledges this and then the master writes the internal address byte. After receiving the internal byte address, the STA380WS again responds with an acknowledgement. The master then initiates another START condition and sends the device select code with the RW bit set to 1. The STA380WS acknowledges this and then responds by sending one byte of data. The master then terminates the transfer by generating a STOP condition.

STA380WS I<sup>2</sup>C bus specification

## 5.4.4 Random address multi-byte read

The multi-byte read modes could start from any internal address. Sequential data bytes are read from sequential addresses within the STA380WS. The master acknowledges each data byte read and then generates a STOP condition to terminate the transfer.

Figure 10. Read mode sequence

Register description STA380WS

# 6 Register description

Table 8. Register summary

| Addr | Name   | D7       | D6       | D5       | D4       | D3      | D2     | D1     | D0     |

|------|--------|----------|----------|----------|----------|---------|--------|--------|--------|

| 0x00 | CONFA  | FDRB     | TWAB     | TWRB     | IR1      | IR0     | MCS2   | MCS1   | MCS0   |

| 0x01 | CONFB  | C2IM     | C1IM     | Reserved | SAIFB    | SAI3    | SAI2   | SAI1   | SAI0   |

| 0x02 | CONFC  | OCRB     | Reserved | CSZ3     | CSZ2     | CSZ1    | CSZ0   | OM1    | ОМО    |

| 0x03 | CONFD  | Reserved | ZDE      |          |          | Reser   | ved    |        |        |

| 0x04 | CONFE  | SVE      | ZCE      | DCCV     | PWMS     | AME     | NSBW   | MPC    | MPCV   |

| 0x05 | CONFF  | EAPD     | PWDN     | ECLE     | LDTE     | BCLE    | IDE    | Rese   | erved  |

| 0x06 | MUTE   |          |          | Reserved |          |         | C2M    | C1M    | MMUTE  |

| 0x07 | MVOL   | MV7      | MV6      | MV5      | MV4      | MV3     | MV2    | MV1    | MV0    |

| 0x08 | C1VOL  | C1V7     | C1V6     | C1V5     | C1V4     | C1V3    | C1V2   | C1V1   | C1V0   |

| 0x09 | C2VOL  | C2V7     | C2V6     | C2V5     | C2V4     | C2V3    | C2V2   | C2V1   | C2V0   |

| 0x0C | AUTO   |          | Rese     | rved     |          | AMAM2   | AMAM1  | AMAM0  | AMAME  |

| 0x0E | C1CFG  |          |          | Reserved |          |         | C1VBP  | Rese   | erved  |

| 0x0F | C2CFG  |          |          | Reserved |          |         | C2VBP  | Rese   | erved  |

| 0x27 | MPCC1  | MPCC15   | MPCC14   | MPCC13   | MPCC12   | MPCC11  | MPCC10 | MPCC9  | MPCC8  |

| 0x28 | MPCC2  | MPCC7    | MPCC6    | MPCC5    | MPCC4    | мрсс3   | MPCC2  | MPCC1  | MPCC0  |

| 0x29 | DCC1   | DCC15    | DCC14    | DCC13    | DCC12    | DCC11   | DCC10  | DCC9   | DCC8   |

| 0x2A | DCC2   | DCC7     | DCC6     | DCC5     | DCC4     | DCC3    | DCC2   | DCC1   | DCC0   |

| 0x2B | FDRC1  | FDRC15   | FDRC14   | FDRC13   | FDRC12   | FDRC11  | FDRC10 | FDRC9  | FDRC8  |

| 0x2C | FDRC2  | FDRC7    | FDRC6    | FDRC5    | FDRC4    | FDRC3   | FDRC2  | FDRC1  | FDRC0  |

| 0x2D | STATUS | PLLUL    | FAULT    | UVFAULT  | Reserved | OCFAULT | OCWARN | TFAULT | TWARN  |

| 0x2E | BIST1  | Rese     | erved    | RO1BACT  | R5BACT   | R4BACT  | R3BACT | R2BACT | R1BACT |

| 0x2F | BIST2  | Rese     | erved    | R01BEND  | R5BEND   | R4BEND  | R3BEND | R2BEND | R1BEND |

| 0x30 | BIST3  |          | Reserved |          | R5BBAD   | R4BBAD  | R3BBAD | R1BBAD | R1BBAD |

| 0x31 | TSTCTL |          |          |          | Reserve  | ed      |        |        |        |

| 0x32 | C1PS   | C1PS7    | C1PS6    | C1PS5    | C1PS4    | C1PS3   | C1PS2  | C1PS1  | C1PS0  |

| 0x33 | C2PS   | C2PS7    | C2PS6    | C2PS5    | C2PS4    | C2PS3   | C2PS2  | C2PS1  | C2PS0  |

| 0x34 | OLIM   | OLIM7    | OLIM6    | OLIM5    | OLIM4    | OLIM3   | OLIM2  | OLIM1  | OLIM0  |

## 6.1 Configuration registers (addr 0x00 to 0x05)

## 6.1.1 Configuration register A (addr 0x00)

| D7   | D6   | D5   | D4  | D3  | D2   | D1   | D0   |

|------|------|------|-----|-----|------|------|------|

| FDRB | TWAB | TWRB | IR1 | IR0 | MCS2 | MCS1 | MCS0 |

| 0    | 1    | 1    | 0   | 0   | 0    | 1    | 1    |

#### Master clock select

Table 9. Master clock select

| Bit | R/W | RST | Name | Description                                                                                                     |

|-----|-----|-----|------|-----------------------------------------------------------------------------------------------------------------|

| 0   | R/W | 1   | MCS0 |                                                                                                                 |

| 1   | R/W | 1   | MCS1 | Master clock select: Selects the ratio between the input I <sup>2</sup> S sample frequency and the input clock. |

| 2   | R/W | 0   | MCS2 |                                                                                                                 |

The STA380WS supports sample rates of 32 kHz, 44.1 kHz, 48 KHz, 88.2 kHz, 96 kHz, 176.4 kHz, and 192 kHz. Therefore the internal clock is:

- 32.768 MHz for 32 kHz

- 45.1584 MHz for 44.1 kHz, 88.2 kHz, and 176.4 kHz

- 49.152 MHz for 48 kHz, 96 kHz, and 192 kHz

The external clock frequency provided to the XTI pin must be a multiple of the input sample frequency ( $f_S$ ).

The relationship between the input clock and the input sample rate is determined by both the MCSx and the IR (input rate) register bits. The MCSx bits determine the PLL factor generating the internal clock and the IR bit determines the oversampling ratio used internally.

Table 10. MCS bits

| Input sample rate    | IR |                      |                      | MCS[2                | :0]                  |                      |                      |

|----------------------|----|----------------------|----------------------|----------------------|----------------------|----------------------|----------------------|

| f <sub>S</sub> (kHz) | IK | 101                  | 100                  | 011                  | 010                  | 001                  | 000                  |

| 32, 44.1, 48         | 00 | 576 * f <sub>S</sub> | 128 * f <sub>S</sub> | 256 * f <sub>S</sub> | 384 * f <sub>S</sub> | 512 * f <sub>S</sub> | 768 * f <sub>S</sub> |

| 88.2, 96             | 01 | NA                   | 64 * f <sub>S</sub>  | 128 * f <sub>S</sub> | 192 * f <sub>S</sub> | 256 * f <sub>S</sub> | 384 * f <sub>S</sub> |

| 176.4, 192           | 1X | NA                   | 32 * f <sub>S</sub>  | 64 * f <sub>S</sub>  | 96 * f <sub>S</sub>  | 128 * f <sub>S</sub> | 192 * f <sub>S</sub> |

Register description STA380WS

#### Interpolation ratio select

Table 11. Interpolation ratio select

| Bit | R/W | RST | Name     | Description                                                                                                        |

|-----|-----|-----|----------|--------------------------------------------------------------------------------------------------------------------|

| 4:3 | R/W | 00  | IR [1:0] | Interpolation ratio select: Selects internal interpolation ratio based on input I <sup>2</sup> S sample frequency. |

The STA380WS has variable interpolation (oversampling) settings such that internal processing and FFX output rates remain consistent. The first processing block interpolates by either 2 times or 1 time (pass-through) or provides a 2-times downsample. The oversampling ratio of this interpolation is determined by the IR bits.

Table 12. IR bit settings as a function of input sample rate

| Input sample rate f <sub>S</sub> (kHz) | IR                      | 1 <sup>st</sup> stage interpolation ratio |

|----------------------------------------|-------------------------|-------------------------------------------|

| 32                                     | 00                      | 2-times oversampling                      |

| 44.1                                   | 00                      | 2-times oversampling                      |

| 48                                     | 00 2-times oversampling |                                           |

| 88.2                                   | 01                      | Pass-through                              |

| 96                                     | 01                      | Pass-through                              |

| 176.2                                  | 10                      | 2-times downsampling                      |

| 192                                    | 10                      | 2-times downsampling                      |

#### Thermal warning recovery bypass

Table 13. Thermal warning recovery

| Bit | R/W | RST | Name | Description                                                                                               |

|-----|-----|-----|------|-----------------------------------------------------------------------------------------------------------|

| 5   | R/W | 1   | TWRB | Thermal warning recovery bypass: 0: thermal warning recovery enabled 1: thermal warning recovery disabled |

If the thermal warning adjustment is enabled (TWAB = 0), then the thermal warning recovery determines if the -3 dB output limit is removed when the thermal warning is negative.

If TWRB = 0 and TWAB = 0, then when a thermal warning disappears, the -3 dB output limit is removed and the gain is added back to the system. If TWRB = 1 and TWAB = 0, then when a thermal warning disappears, the -3 dB output limit remains until TWRB is changed to zero or the device is reset.

#### Thermal warning adjustment bypass

Table 14. Thermal warning adjustment

| Bit | R/W | RST | Name | Description                                                                                                     |

|-----|-----|-----|------|-----------------------------------------------------------------------------------------------------------------|

| 6   | R/W | 1   | TWAB | Thermal warning adjustment bypass: 0: thermal warning adjustment enabled 1: thermal warning adjustment disabled |

The on-chip STA380WS power output block provides feedback to the digital controller using inputs to the power control block. The TWARN input is used to indicate a thermal warning condition. When TWARN is asserted (set to 0) for a period of time greater than 400 ms, the power control block will force a -3 dB output limit (determined by TWOCL in coefficient RAM) to the modulation limit in an attempt to eliminate the thermal warning condition. Once the thermal warning output limit adjustment is applied, it remains in this state until reset, unless FDRB = 0.

#### Fault detect recovery bypass

Table 15. Fault detect recovery

| Bit | R/W | RST | Name | Description                                                                                      |

|-----|-----|-----|------|--------------------------------------------------------------------------------------------------|

| 7   | R/W | 0   | FDRB | Fault detect recovery bypass: 0: fault detect recovery enabled 1: fault detect recovery disabled |

The on-chip STA380WS power output block provides feedback to the digital controller using inputs to the power control block. The FAULT input is used to indicate a fault condition (either overcurrent or thermal). When FAULT is asserted (set to 0), the power control block attempts a recovery from the fault by asserting the 3-state output (setting it to 0 which directs the power output block to begin recovery), holding it at 0 for period of time in the range of 0.1 ms to 1 second as defined by the fault detect recovery constant register (FDRC registers 0x2B, 0x2C), then toggling it back to 1. This sequence is repeated as long as the fault indication exists. This feature is enabled by default but can be bypassed by setting the FDRB control bit to 1.

## 6.1.2 Configuration register B (addr 0x01)

| D7   | D6   | D5       | D4    | D3   | D2   | D1   | D0   |

|------|------|----------|-------|------|------|------|------|

| C2IM | C1IM | Reserved | SAIFB | SAI3 | SAI2 | SAI1 | SAI0 |

| 1    | 0    | 0        | 0     | 0    | 0    | 0    | 0    |

Register description STA380WS

#### Serial audio input interface format

Table 16. Serial audio input interface format

| Bit | R/W | RST | Name | Description                                         |

|-----|-----|-----|------|-----------------------------------------------------|

| 0   | R/W | 0   | SAI0 |                                                     |

| 1   | R/W | 0   | SAI1 | Determines the interface format of the input serial |

| 2   | R/W | 0   | SAI2 | digital audio interface.                            |

| 3   | R/W | 0   | SAI3 |                                                     |

#### Serial data interface

The STA380WS audio serial input interfaces with standard digital audio components and accepts a number of serial data formats. STA380WS always acts a slave when receiving audio input from standard digital audio components. Serial data for two channels is provided using three inputs: left/right clock LRCKI, serial clock BICKI, and serial data SDI.

Bits SAI and bit SAIFB are used to specify the serial data format. The default serial data format is I<sup>2</sup>S, MSB first. Available formats are shown in the tables and figure that follow.

#### Serial data first bit

Table 17. Serial data first bit

| SAIFB | Format    |  |  |  |  |  |

|-------|-----------|--|--|--|--|--|

| 0     | MSB-first |  |  |  |  |  |

| 1     | LSB-first |  |  |  |  |  |

Table 18. Support serial audio input formats for MSB first (SAIFB = 0)

| ВІСКІ               | SAI [3:0] | SAIFB | Interface format                    |  |  |

|---------------------|-----------|-------|-------------------------------------|--|--|

| 32 * f <sub>S</sub> | 0000      | 0     | I <sup>2</sup> S 15-bit data        |  |  |

| 32   IS             | 0001      | 0     | Left/right justified 16-bit data    |  |  |

|                     | 0000      | 0     | I <sup>2</sup> S 16- to 23-bit data |  |  |

|                     | 0001      | 0     | Left-justified 16- to 24-bit data   |  |  |

| 10* f               | 0010      | 0     | Right-justified 24-bit data         |  |  |

| 48* f <sub>S</sub>  | 0110      | 0     | Right-justified 20-bit data         |  |  |

|                     | 1010      | 0     | Right-justified 18-bit data         |  |  |

|                     | 1110      | 0     | Right-justified 16-bit data         |  |  |

|                     | 0000 0    |       | I <sup>2</sup> S 16- to 24-bit data |  |  |

|                     | 0001      | 0     | Left-justified 16- to 24-bit data   |  |  |

| 64* f <sub>S</sub>  | 0010      | 0     | Right-justified 24-bit data         |  |  |

| 04 IS               | 0110      | 0     | Right-justified 20-bit data         |  |  |

|                     | 1010      | 0     | Right-justified 18-bit data         |  |  |

|                     | 1110      | 0     | Right-justified 16-bit data         |  |  |

26/48 DocID024426 Rev 1

Table 19. Supported serial audio input formats for LSB-first (SAIFB = 1)

| віскі              | SAI[3:0] | SAIFB | Interface format                       |

|--------------------|----------|-------|----------------------------------------|

| 22* f              | 1100     | 1     | I <sup>2</sup> S 15-bit data           |

| 32* f <sub>S</sub> | 1110     | 1     | Left/right justified 16-bit data       |

|                    | 0100     | 1     | I <sup>2</sup> S 23-bit data           |

|                    | 0100     | 1     | I <sup>2</sup> S 20-bit data           |

|                    | 1000     | 1     | I <sup>2</sup> S 18-bit data           |

|                    | 1100     | 1     | LSB-first I <sup>2</sup> S 16-bit data |

| 48* f <sub>S</sub> | 0001     | 1     | Left-justified 24-bit data             |

|                    | 0101     | 1     | Left-justified 20-bit data             |

|                    | 1001     | 1     | Left-justified 18-bit data             |

|                    | 1101     | 1     | Left-justified 16-bit data             |

|                    | 0010     | 1     | Right-justified 24-bit data            |

|                    | 0110     | 1     | Right-justified 20-bit data            |

| 48* f <sub>S</sub> | 1010     | 1     | Right-justified 18-bit data            |

|                    | 1110     | 1     | Right-justified 16-bit data            |

|                    | 0000     | 1     | I <sup>2</sup> S 24-bit data           |

|                    | 0100     | 1     | I <sup>2</sup> S 20-bit data           |

|                    | 1000     | 1     | I <sup>2</sup> S 18-bit data           |

|                    | 1100     | 1     | LSB-first I <sup>2</sup> S 16-bit data |

|                    | 0001     | 1     | Left-justified 24-bit data             |

| C 4 * 5            | 0101     | 1     | Left-justified 20-bit data             |

| 64* f <sub>S</sub> | 1001     | 1     | Left-justified 18-bit data             |

|                    | 1101     | 1     | Left-justified 16-bit data             |

|                    | 0010     | 1     | Right-justified 24-bit data            |

|                    | 0110     | 1     | Right-justified 20-bit data            |

|                    | 1010     | 1     | Right-justified 18-bit data            |

|                    | 1110     | 1     | Right-justified 16-bit data            |

Register description STA380WS

#### **Channel input mapping**

Table 20. Channel input mapping

| Bit | Bit R/W RST Name |   | Name | Description                                                                                                                   |  |  |  |

|-----|------------------|---|------|-------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 6   | R/W              | 0 | C1IM | 0: processing channel 1 receives left I <sup>2</sup> S input 1: processing channel 1 receives right I <sup>2</sup> S input    |  |  |  |

| 7   | R/W 0 C2IM       |   | C2IM | 0: processing channel 2 receives left I <sup>2</sup> S input<br>1: processing channel 2 receives right I <sup>2</sup> S input |  |  |  |

Each channel received via I<sup>2</sup>S can be mapped to any internal processing channel via the channel input mapping registers. This allows for flexibility in processing. The default settings of these registers map each I<sup>2</sup>S input channel to its corresponding processing channel.

## 6.1.3 Configuration register C (addr 0x02)

| D7   | D6       | D5   | D4   | D3   | D2   | D1  | D0  |

|------|----------|------|------|------|------|-----|-----|

| OCRB | Reserved | CSZ3 | CSZ2 | CSZ1 | CSZ0 | OM1 | OM0 |

| 1    | 0        | 0    | 1    | 0    | 1    | 1   | 1   |

#### FFX power output mode

Table 21. FFX power output mode

| Bit | R/W | RST | Name | Description                                                                                                                                                 |  |  |  |  |

|-----|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0   | R/W | 1   | ОМ0  | The FFX power output mode selects the configuration                                                                                                         |  |  |  |  |

| 1   | R/W | 1   | OM1  | of the FFX output:  00: drop compensation  01: discrete output stage: tapered compensation  10: full-power mode  11: variable drop compensation (CSZx bits) |  |  |  |  |

### FFX compensation pulse size register

Table 22. FFX compensating pulse size

|     |     |     |      | <u> </u>                                                                                            |  |  |  |  |

|-----|-----|-----|------|-----------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit | R/W | RST | Name | Description                                                                                         |  |  |  |  |

| 2   | R/W | 1   | CSZ0 | When OM[1:0] = 11, this register determines the size of                                             |  |  |  |  |

| 3   | R/W | 0   | CSZ1 | the FFX compensating pulse from 0 to 15 clock periods: 0000: 0 ns (0 ticks) compensating pulse size |  |  |  |  |

| 4   | R/W | 1   | CSZ2 | 0001: 20 ns (1 tick) clock period compensating pulse                                                |  |  |  |  |

| 5   | R/W | 0   | CSZ3 | size 1111: 300 ns (15 ticks) clock period compensating pulse size                                   |  |  |  |  |

#### Overcurrent warning detect adjustment bypass

Table 23. Overcurrent warning detect adjustment bypass

|   | Bit | Bit R/W RST Name |   | Name | Description                                                                        |  |  |

|---|-----|------------------|---|------|------------------------------------------------------------------------------------|--|--|

| 7 | 7   | R/W              | 1 | OCRB | overcurrent warning adjustment enabled     overcurrent warning adjustment disabled |  |  |

The status bit OCWARN warns that an overcurrent condition is present. When OCWARN is asserted (set to 0), the power control block forces an adjustment to the modulation limit (default -3 dB) in an attempt to eliminate the overcurrent warning condition. Once the overcurrent warning volume adjustment is applied, it remains applied until the device is reset. The overcurrent limit can be changed via register OLIM (*Output limit register (addr 0x34) on page 39*).

#### 6.1.4 Configuration register D (addr 0x03)

| D7       | D6  | D5        | D4       | D3 | D2 | D1 | D0 |  |  |

|----------|-----|-----------|----------|----|----|----|----|--|--|

| Reserved | ZDE |           | Reserved |    |    |    |    |  |  |

| 0        | 1   | 0 0 0 0 0 |          |    |    |    |    |  |  |

#### Zero-detect mute enable

Table 24. Zero detect mute enable

| Bit | R/W RST Name |   | Name | Description                              |  |  |  |  |

|-----|--------------|---|------|------------------------------------------|--|--|--|--|

| 6   | R/W          | 1 | ZDE  | 1: enable the automatic zero-detect mute |  |  |  |  |

Setting the ZDE bit enables the zero-detect automatic mute. The zero-detect circuit looks at the data for each processing channel at the output of the crossover (bass management) filter. If any channel receives 2048 consecutive zero value samples (regardless of  $f_S$ ), then that individual channel is muted if this function is enabled.

#### 6.1.5 Configuration register E (addr 0x04)

| D7  | D6  | D5   | D4   | D3  | D2   | D1  | D0   |

|-----|-----|------|------|-----|------|-----|------|

| SVE | ZCE | DCCV | PWMS | AME | NSBW | MPC | MPCV |

| 1   | 1   | 0    | 0    | 0   | 0    | 1   | 0    |

#### Max power correction variable

Table 25. Max power correction variable

| Bit | R/W | RST | Name | Description                                                        |

|-----|-----|-----|------|--------------------------------------------------------------------|

| 0   | R/W | 0   | MPCV | use standard MPC coefficient     use MPCC bits for MPC coefficient |

Register description STA380WS

#### Max power correction

Table 26. Max power correction

| Bit | R/W | RST | Name | Description                                                                    |

|-----|-----|-----|------|--------------------------------------------------------------------------------|

| 1   | R/W | 1   | MPC  | 1: enable power bridge correction for THD reduction near maximum power output. |

Setting the MPC bit turns on special processing that corrects the STA380WS power device at high power. This mode lowers the THD+N of a full FFX system at maximum power output and slightly below. If enabled, MPC is operational in all output modes except tapered (OM[1:0] = 01) and binary. When OCFG = 00, MPC does not affect channels 3 and 4, the line-out channels.

#### Noise-shaper bandwidth selection

Table 27. Noise-shaper bandwidth selection

| Bit | R/W | RST | Name | Description                                                |

|-----|-----|-----|------|------------------------------------------------------------|

| 2   | R/W | 0   | NSBW | 1: 3 <sup>rd</sup> order NS<br>0: 4 <sup>th</sup> order NS |

#### AM mode enable

Table 28. AM mode enable

| Bit | R/W | RST | Name       | Description                                              |

|-----|-----|-----|------------|----------------------------------------------------------|

| 3   | R/W | 0   | Ι Δ Ι//II— | normal FFX operation     AM reduction mode FFX operation |

The STA380WS features an FFX processing mode that minimizes the amount of noise generated in the frequency range of AM radio. This mode is intended for use when FFX is operating in a device with an active AM tuner. The SNR of the FFX processing is reduced to approximately 83 dB in this mode, which is still greater than the SNR of AM radio.

#### **PWM** speed mode

Table 29. PWM speed mode

| Bit | R/W | RST | Name | Description                                                                     |

|-----|-----|-----|------|---------------------------------------------------------------------------------|

| 4   | R/W | 0   | PWMS | 0: normal speed (384 kHz) all channels<br>1: odd speed (341.3 kHz) all channels |

#### Distortion compensation variable enable

Table 30. Distortion compensation variable enable

| Bit | R/W | RST | Name | Description                                           |

|-----|-----|-----|------|-------------------------------------------------------|

| 5   | R/W | 0   | DCCV | 0: uses preset DC coefficient 1: uses DCC coefficient |

#### Zero-crossing volume enable

Table 31. Zero-crossing volume enable

| Bit | R/W | RST | Name | Description                                                                                                |

|-----|-----|-----|------|------------------------------------------------------------------------------------------------------------|

| 6   | R/W | 1   | ZCE  | volume adjustments will only occur at digital zero-crossings     volume adjustments will occur immediately |

The ZCE bit enables zero-crossing volume adjustments. When volume is adjusted on digital zero-crossings, no clicks will be audible.

#### Soft volume update enable

Table 32. Soft volume update enable

| Bit | R/W | RST | Name | Description                                                                                     |

|-----|-----|-----|------|-------------------------------------------------------------------------------------------------|

| 7   | R/W | 1   | SVE  | volume adjustments ramp according to SVR settings     volume adjustments will occur immediately |

### 6.1.6 Configuration register F (addr 0x05)

| D7   | D6   | D5   | D4   | D3   | D2  | D1   | D0    |   |

|------|------|------|------|------|-----|------|-------|---|

| EAPD | PWDN | ECLE | LDTE | BCLE | IDE | Rese | erved | ] |

| 0    | 1    | 0    | 1    | 1    | 1   | 0    | 0     |   |

#### Invalid input detect mute enable

Table 33. Invalid input detect mute enable

| Bit | R/W | RST | Name | Description                                        |

|-----|-----|-----|------|----------------------------------------------------|

| 2   | R/W | 1   | IDE  | 1: enables the automatic invalid input detect mute |

Setting the IDE bit enables this function, which looks at the input I<sup>2</sup>S data and will automatically mute if the signals are perceived as invalid.

#### Binary output mode clock loss detection

Table 34. Binary output mode clock loss detection

| Bi | R/W | RST | Name | Description                                    |

|----|-----|-----|------|------------------------------------------------|

| 3  | R/W | 1   | BCLE | Binary output mode clock loss detection enable |

Detects loss of input MCLK in binary mode and outputs 50% of the duty cycle.

47/

Register description STA380WS

#### LRCK double trigger protection

Table 35. LRCK double trigger protection

| Bit | R/W | RST | Name | Description                            |

|-----|-----|-----|------|----------------------------------------|

| 4   | R/W | 1   | LDTE | LRCLK double trigger protection enable |

Actively prevents double triggering of LRCLK.

#### **Auto EAPD on clock loss**

Table 36. Auto EAPD on clock loss

| Bit | R/W | RST | Name | Description             |

|-----|-----|-----|------|-------------------------|

| 5   | R/W | 0   | ECLE | Auto EAPD on clock loss |

When active, will issue a power stage device power-down signal (EAPD) on clock loss detection.

#### IC power-down

Table 37. Power-down

| Bit | R/W | RST | Name | Description                                          |

|-----|-----|-----|------|------------------------------------------------------|

| 6   | R/W | 1   | PWDN | power-down, low-power condition     normal operation |

The PWDN register is used to put the IC in a low-power state. When PWDN is 0, the output begins a soft-mute. After the mute condition is reached, EAPD is asserted to power down the power stage, then the master clock to all internal hardware except the I<sup>2</sup>C block is gated. This puts the IC in a very low power consumption state.

#### **External amplifier power-down**

Table 38. External amplifier power-down

| Bit | R/W | RST | Name | Description                                                       |

|-----|-----|-----|------|-------------------------------------------------------------------|

| 7   | R/W | 1   | EAPD | 0: external power stage power-down active     1: normal operation |

The EAPD register directly disables/enables the internal power circuitry.

When EAPD = 0, the internal power section is placed in a low-power state (disabled).

# 6.2 Volume control registers (addr 0x06 to 0x09)

## 6.2.1 Mute/line output configuration register (addr 0x06)

| D7        | D6 | D5       | D4  | D3  | D2    | D1 | D0 |

|-----------|----|----------|-----|-----|-------|----|----|

|           |    | Reserved | C2M | C1M | MMUTE |    |    |

| 0 0 0 0 0 |    |          |     |     | 0     | 0  | 0  |

#### Master mute

#### Table 39. Master mute

| Bit | R/W | RST | Name  | Description                                             |

|-----|-----|-----|-------|---------------------------------------------------------|

| 0   | R/W | 0   | MMUTE | normal operation     all channels are in mute condition |

#### **Channel mute**

#### Table 40. Channel mute

| Bit | R/W | RST | Name | Description                                                                              |  |  |  |

|-----|-----|-----|------|------------------------------------------------------------------------------------------|--|--|--|

| 1   | R/W | 0   | C1M  | Channel 1 mute: 0: not muted, it is possible to set the channel volume 1: hardware muted |  |  |  |

| 2   | R/W | 0   | C2M  | Channel 2 mute: 0: not muted, it is possible to set the channel volume 1: hardware muted |  |  |  |

Register description STA380WS

#### 6.2.2 Master volume register (addr 0x07)

| D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |  |

|-----|-----|-----|-----|-----|-----|-----|-----|--|

| MV7 | MV6 | MV5 | MV4 | MV3 | MV2 | MV1 | MV0 |  |

| 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |  |

### 6.2.3 Channel volume (addr 0x08, 0x09)

| D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|------|------|------|------|------|------|------|------|

| C1V7 | C1V6 | C1V5 | C1V4 | C1V3 | C1V2 | C1V1 | C1V0 |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    |

|      |      |      |      |      | •    |      |      |

| D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

| C2V7 | C2V6 | C2V5 | C2V4 | C2V3 | C2V2 | C2V1 | C2V0 |

| 0    | 1    | 1    | 0    | 0    | 0    | 0    | 0    |

#### Volume setting

The volume structure of the STA380WS consists of individual volume registers for each channel and a master volume register that provides an offset to each channel's volume setting. The individual channel volumes are adjustable in 0.5-dB steps from +48 dB to -80 dB. As an example, if C2V = 0x00 or +48 dB and MV = 0x18 or -12 dB, then the total gain for channel 2 = +36 dB.

The master mute, when set to 1, will mute all channels at once, whereas the individual channel mutes (CxM) mute only that channel. Both the master mute and the channel mutes provide a "soft mute" with the volume ramping down to mute in 4096 samples from the maximum volume setting at the internal processing rate (about 96 kHz). A hard mute can be obtained by commanding a value of all 1's (255) to any channel volume register or the master volume register. When volume offsets are provided via the master volume register, any channel that whose total volume is less than -80 dB is muted.

All changes in volume take place at zero-crossings when ZCE = 1 (configuration register F) on a per-channel basis as this creates the smoothest possible volume transitions. When ZCE = 0, volume updates will occur immediately.

Table 41. Master volume offset as a function of MV

| MV[7:0]         | Volume offset from channel value |

|-----------------|----------------------------------|

| 00000000 (0x00) | 0 dB                             |

| 00000001 (0x01) | -0.5 dB                          |

| 00000010 (0x02) | -1 dB                            |

|                 |                                  |

| 01001100 (0x4C) | -38 dB                           |

|                 |                                  |

| 11111110 (0xFE) | -127.5 dB                        |

| 11111111 (0xFF) | Hard master mute                 |

Table 42. Channel volume as a function of CxV

| CxV[7:0]        | Volume            |

|-----------------|-------------------|

| 00000000 (0x00) | +48 dB            |

| 00000001 (0x01) | +47.5 dB          |

| 0000010 (0x02)  | +47 dB            |

|                 |                   |

| 01011111 (0x5F) | +0.5 dB           |

| 01100000 (0x60) | 0 dB              |

| 01100001 (0x61) | -0.5 dB           |

|                 |                   |

| 11010111 (0xD7) | -59.5 dB          |

| 11011000 (0xD8) | -60 dB            |

| 11011001 (0xD9) | -61 dB            |

| 11011010 (0xDA) | -62 dB            |

|                 |                   |

| 11101100 (0xEC) | -80 dB            |

| 11101101 (0xED) | Hard channel mute |

|                 |                   |

| 11111111 (0xFF) | Hard channel mute |

# 6.3 Automode register (0x0C)

| D7       | D6 | D5 | D4 | D3    | D2    | D1    | D0    |

|----------|----|----|----|-------|-------|-------|-------|

| Reserved |    |    |    | AMAM2 | AMAM1 | AMAM0 | AMAME |

| 0        | 0  | 0  | 0  | 0     | 0     | 0     | 0     |

#### AM interference frequency switching

Table 43. AM interference frequency switching

| Bit | R/W | RST | Name  | Description                                                                                       |

|-----|-----|-----|-------|---------------------------------------------------------------------------------------------------|

| 0   | R/W | 0   | AMAME | switching frequency determined by PWMS setting     switching frequency determined by AMAM setting |

#### **AMAM** bits

Table 44. Automode AM switching frequency selection

| AMAM[2:0] | 48 kHz / 96 kHz input f <sub>S</sub> | 44.1 kHz / 88.2 kHz input f <sub>S</sub> |

|-----------|--------------------------------------|------------------------------------------|

| 000       | 0.535 MHz - 0.720 MHz                | 0.535 MHz - 0.670 MHz                    |

| 001       | 0.721 MHz - 0.900 MHz                | 0.671 MHz - 0.800 MHz                    |

| 010       | 0.901 MHz - 1.100 MHz                | 0.801 MHz - 1.000 MHz                    |

| 011       | 1.101 MHz - 1.300 MHz                | 1.001 MHz - 1.180 MHz                    |

| 100       | 1.301 MHz - 1.480 MHz                | 1.181 MHz - 1.340 MHz                    |

| 101       | 1.481 MHz - 1.600 MHz                | 1.341 MHz - 1.500 MHz                    |

| 110       | 1.601 MHz - 1.700 MHz                | 1.501 MHz - 1.700 MHz                    |

# 6.4 Channel configuration registers (addr 0x0E, 0x0F)

| D7       | D6       | D5    | D4   | D3    | D2 | D1   | D0    |

|----------|----------|-------|------|-------|----|------|-------|

| Reserved |          |       |      |       |    | Rese | erved |

| 0        | 0        | 0     | 0    | 0     | 0  | 0    | 0     |

|          |          |       |      |       |    |      |       |

| D7       | D6       | D5    | D4   | D3    | D2 | D1   | D0    |

|          | Reserved | C2VBP | Rese | erved |    |      |       |

| 0        | 0        | 0     | 0    | 0     | 0  | 0    | 0     |

## **Volume bypass**

Each channel contains an individual channel volume bypass. If a particular channel has volume bypassed via the CxVBP = 1 register, then only the channel volume setting for that particular channel affects the volume setting. The master volume setting will not affect that channel.

## 6.5 Variable max power correction registers (addr 0x27, 0x28)