PERICOM<sup>®</sup>

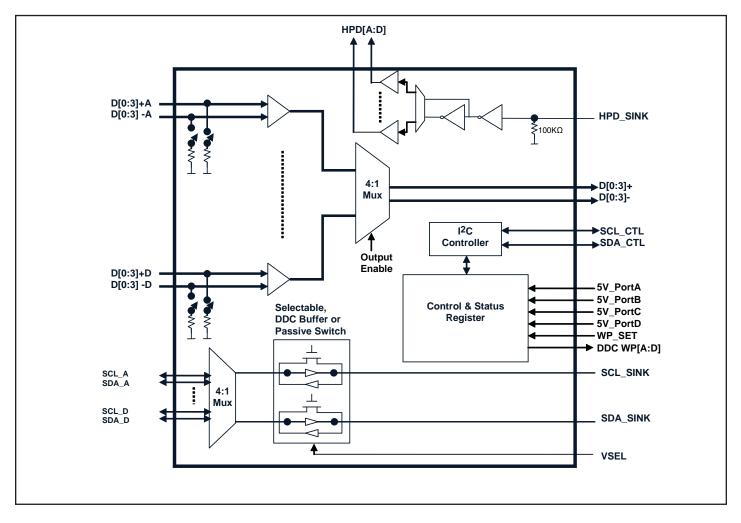

#### **Block Diagram**

#### **PI3HDMI2410** 4-Port HDMI<sup>™</sup> Signal Switch with I<sup>2</sup>C Control

## Pin Assignment – 80-Contact LQFP

|                                                                                                                                                                                              |                                                                         | D0-B<br>VDD<br>D3-A<br>D2-A<br>VDD<br>D1-A<br>VDD<br>D1+A<br>D1-A<br>D1-A<br>D0-A<br>VDD<br>D0-A<br>VDC<br>VDC<br>VDD<br>D0C_WPB<br>DDC_WPD<br>DDC_WPD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                    | 1                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0+B<br>D1-B<br>D1+B<br>D2-B<br>D2+B<br>D3-B<br>D3+B<br>D0-C<br>D0+C<br>D1-C<br>D1+C<br>D1+C<br>D2-C<br>D2+C<br>D3-C<br>D3+C<br>D3+C<br>D3+C<br>D0+D<br>D1-D<br>D1+D<br>D1+D<br>D1+D<br>D2-D | 1 2 3 4 5 6 7 8 9 10 11 2 3 4 5 6 7 8 9 10 11 2 13 14 15 16 17 18 19 20 | 0 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\begin{array}{c} 60\\ 59\\ 58\\ 57\\ 56\\ 55\\ 54\\ 53\\ 52\\ 51\\ 50\\ 49\\ 48\\ 47\\ 46\\ 45\\ 44\\ 43\\ 42\\ 41\\ \end{array}$ | 5V_PORTA<br>5V_PORTB<br>5V_PORTC<br>5V_PORTD<br>SDA_CTL<br>SCL_CTL<br>D0-<br>D0+<br>D1-<br>D1+<br>VDD<br>D2-<br>D2+<br>D3-<br>D3+<br>A0<br>A1<br>HPD_SINK<br>HPD_A<br>HPD B |

|                                                                                                                                                                                              |                                                                         | D2+D<br>D3-D<br>D3-D<br>D3-D<br>D3-D<br>CND<br>CND<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SDA_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCL_A<br>SCA<br>SCL_A<br>SCA<br>SCA<br>SCA<br>SCA<br>SCA<br>SCA<br>SCA<br>SCA<br>SCA<br>SC |                                                                                                                                    | _                                                                                                                                                                           |

PERICOM<sup>®</sup>

#### **Pinout Table**

| Pin Name                                                     | I/O Type | Description                                                                                                                                                                                  |

|--------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub>                                              | I/O      | 3.3V power supply. When $V_{DD}$ is off, the TMDS channels will be powered down.                                                                                                             |

| SV <sub>DD</sub>                                             | I/O      | 3.3V standby power supply. SV_{DD} is for all side band signals, I <sup>2</sup> C register and I <sup>2</sup> C bus.                                                                         |

| HPD_SINK                                                     | I        | Sink side hot plug detector input.<br>High: 5-V power signal asserted from source to sink and EDID is ready.<br>Low: No 5-V power signal asserted from source to sink, or EDID is not ready. |

| HPD_A                                                        | 0        | Port A HPD output                                                                                                                                                                            |

| HPD_B                                                        | 0        | Port B HPD output                                                                                                                                                                            |

| HPD_C                                                        | 0        | Port C HPD output                                                                                                                                                                            |

| HPD_D                                                        | 0        | Port D HPD output                                                                                                                                                                            |

| D0+A<br>D0-A<br>D1+A<br>D1-A<br>D2+A<br>D2-A<br>D3+A<br>D3-A | I        | Port A TMDS inputs                                                                                                                                                                           |

| D0+B<br>D0-B<br>D1+B<br>D1-B<br>D2+B<br>D2-B<br>D3+B<br>D3-B | Ι        | Port B TMDS inputs                                                                                                                                                                           |

| D0+C<br>D0-C<br>D1+C<br>D1-C<br>D2+C<br>D2-C<br>D3+C<br>D3-C | Ι        | Port C TMDS inputs                                                                                                                                                                           |

# PERICOM<sup>®</sup>

### **PI3HDMI2410** 4-Port HDMI<sup>™</sup> Signal Switch with I<sup>2</sup>C Control

| Pin Name   | I/O Type | Description                                                                                         |  |  |  |

|------------|----------|-----------------------------------------------------------------------------------------------------|--|--|--|

| D0+D       |          |                                                                                                     |  |  |  |

| D0-D       |          |                                                                                                     |  |  |  |

| D1+D       |          |                                                                                                     |  |  |  |

| D1-D       | Ι        | Port D TMDS inputs                                                                                  |  |  |  |

| D2+D       | 1        |                                                                                                     |  |  |  |

| D2-D       |          |                                                                                                     |  |  |  |

| D3+D       |          |                                                                                                     |  |  |  |

| D3-D       |          |                                                                                                     |  |  |  |

| D0+        |          |                                                                                                     |  |  |  |

| D0-        |          |                                                                                                     |  |  |  |

| D1+<br>D1- |          |                                                                                                     |  |  |  |

| D1-<br>D2+ | 0        | TMDS outputs                                                                                        |  |  |  |

| D2-        |          |                                                                                                     |  |  |  |

| D3+        |          |                                                                                                     |  |  |  |

| D3-        |          |                                                                                                     |  |  |  |

| SCL_A      | I/O      | Port A DDC Clock                                                                                    |  |  |  |

| SCL_B      | I/O      | Port B DDC Clock                                                                                    |  |  |  |

| SCL_C      | I/O      | Port C DDC Clock                                                                                    |  |  |  |

| SCL_D      | I/O      | Port D DDC Clock                                                                                    |  |  |  |

| SDA_A      | I/O      | Port A DDC Data                                                                                     |  |  |  |

| SDA_B      | I/O      | Port B DDC Data                                                                                     |  |  |  |

| SDA_C      | I/O      | Port C DDC Data                                                                                     |  |  |  |

| SDA_D      | I/O      | Port D DDC Data                                                                                     |  |  |  |

| SCL_SINK   | I/O      | Sink side DDC Clock                                                                                 |  |  |  |

| SDA_SINK   | I/O      | Sink side DDC Data                                                                                  |  |  |  |

| SCL_CTL    | I/O      | I <sup>2</sup> C Clock                                                                              |  |  |  |

| SDA_CTL    | I/O      | I <sup>2</sup> C Data                                                                               |  |  |  |

| WP_SET     | Ι        | WP_SET = 0 (Default), Set B1b[1] as INT Flag.<br>WP_SET = 1, DDC_WP[A:D] is programmable by B1b[1]. |  |  |  |

| DDC_WPA,   |          |                                                                                                     |  |  |  |

| DDC_WPB,   |          |                                                                                                     |  |  |  |

| DDC_WPC,   | 0        | Open drain output. When WP_SET = 1, general purpose logic configured by B1b[1]                      |  |  |  |

| DDC_WPD,   |          |                                                                                                     |  |  |  |

| ŌĒ         | Ι        | Output Enable control. Active low.                                                                  |  |  |  |

| A1         | Ι        | I <sup>2</sup> C Address 1                                                                          |  |  |  |

| A0         | Ι        | I <sup>2</sup> C Address 0                                                                          |  |  |  |

| Pin Name  | I/O Type | Description                           |  |

|-----------|----------|---------------------------------------|--|

| 5V_PortA, |          |                                       |  |

| 5V_PortB, | Ι        | Connector 5V port.                    |  |

| 5V_PortC, |          |                                       |  |

| 5V_PortD  |          |                                       |  |

|           |          | DDC buffer V <sub>IL</sub> selection. |  |

| VCEL      | Ι        | $VSEL = 0V, V_{IL} = 0.5V$            |  |

| VSEL      |          | $VSEL = 0.5 V_{DD}, V_{IL} = 0.45 V$  |  |

|           |          | $VSEL = V_{DD}, V_{IL} = 0.6V$        |  |

#### **Truth Table**

| WP_SET | B1_b[1] | DDC_WP[A:D] |

|--------|---------|-------------|

| 1      | 0       | Hi_Z        |

| 1      | 1       | 0           |

| 0      | Х       | Hi_Z        |

#### I<sup>2</sup>C Control Register

|              | b7 | b6 | b5 | <b>b</b> 4 | b3 | b2                  | b1                  | <b>b</b> 0 |

|--------------|----|----|----|------------|----|---------------------|---------------------|------------|

| Address Byte | 1  | 0  | 1  | 0          | 1  | A1                  | A0                  | 0/1 *      |

|              |    |    |    |            |    | Hardware Selectable | Hardware Selectable |            |

\* 0:Write; 1:Read

## Data Byte 0: Control Register

| Bit | Description               | Туре    | Power Up<br>Condition | Logic Settings                        |

|-----|---------------------------|---------|-----------------------|---------------------------------------|

| 7   | HDMI input port selection | R/W     | 0                     | 00 = Port A                           |

| /   |                           |         | 0                     | 01 = Port B                           |

| 6   | HDMI input port selection | R/W     | 0                     | 10 = Port C                           |

| 0   | mput port selection       | 10/ 10  | 0                     | 11 = Port D                           |

| F   | LIDD Logic Colection      | D / 147 | 1                     | 0 = Inverted                          |

| 5   | HPD Logic Selection       | R/W     | 1                     | 1 = Non Inverted                      |

| 4   |                           | D /147  | 0                     | 0 = HPD_SINK                          |

| 4   | HPD Input Selection       | R/W     | 0                     | $1 = I^2 C$ Register Setting B0b[3:0] |

|     |                           |         |                       | I. Byte0 $b[4] = 1$                   |

| 2   |                           | D /147  |                       | HPD Port D Register setting           |

| 3   | HPD Port D Logic Setting  | R/W     | 0                     | II. Byte0 $b[4] = 0$                  |

|     |                           |         |                       | Test mode                             |

|     |                           |         |                       | I. Byte0 $b[4] = 1$                   |

| 2   |                           | R/W     |                       | HPD Port C Register setting           |

| 2   | HPD Port C Logic Setting  |         | 0                     | II. Byte0 $b[4] = 0$                  |

|     |                           |         |                       | Test mode                             |

|     |                           |         |                       | I. Byte0 $b[4] = 1$                   |

| 1   |                           | D /147  |                       | HPD Port B Register setting           |

| 1   | HPD Port B Logic Setting  | R/W     | 0                     | II. Byte0 $b[4] = 0$                  |

|     |                           |         |                       | Test mode                             |

|     |                           |         |                       | I. Byte0 b[4] = 1                     |

| 0   |                           | D /347  |                       | HPD Port A Register setting           |

| 0   | HPD Port A Logic Setting  | R/W     | 0                     | II. Byte0 $b[4] = 0$                  |

|     |                           |         |                       | Test mode                             |

#### **Data Byte 1: Control Register**

| Bit | Description                | Туре | Power Up<br>Condition | Logic Settings                                                                                              |

|-----|----------------------------|------|-----------------------|-------------------------------------------------------------------------------------------------------------|

| 7   | HPD Output Stage selection | R/W  | 0                     | 0 = Open Drain<br>1 = Output Buffer                                                                         |

| 6   | Output Enable              | R/W  | 1                     | 0 = Output Disable (also drives switch into power down mode)                                                |

| 5   | 5V_Port D connect          | R    | 0                     | <ul><li>1 = Output Enable</li><li>0 = Disconnected</li><li>1 = Connected; Set INT Flag</li></ul>            |

| 4   | 5V_Port C connect          | R    | 0                     | 0 = Disconnected<br>1 = Connected; Set INT Flag                                                             |

| 3   | 5V_Port B connect          | R    | 0                     | 0 = Disconnected<br>1 = Connected; Set INT Flag                                                             |

| 2   | 5V_Port A connect          | R    | 0                     | 0 = Disconnected<br>1 = Connected; Set INT Flag                                                             |

|     |                            |      |                       | When WP_SET = 0, B1b[1] is configured as<br>INT flag.                                                       |

| 1   | INT Flag                   | R/W  | 0                     | 0 = INT Flag Clear<br>1 = INT Flag Set<br>When WP_SET = 1, B1b[1] is configured as<br>DDC_WP input setting. |

| 0   | DDC channel selection      | R/W  | 0                     | 0 = Passive switch<br>1 = Active switch buffer                                                              |

\* External hardware control pin WP\_SET will set B1b1 to be INT Flag or DDC\_WP[0:3] input.

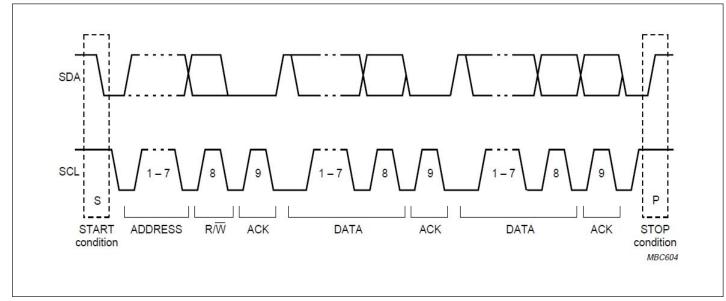

#### **Bus transactions**

Data transfers follow the format shown in Fig.1. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master. However, if a master still wishes to communicate on the bus, it can generate a repeated START condition (Sr) and address another slave without first generating a STOP condition. Various combinations of read/write formats are then possible within such a transfer.

Figure 1: A Complete Data Transfer

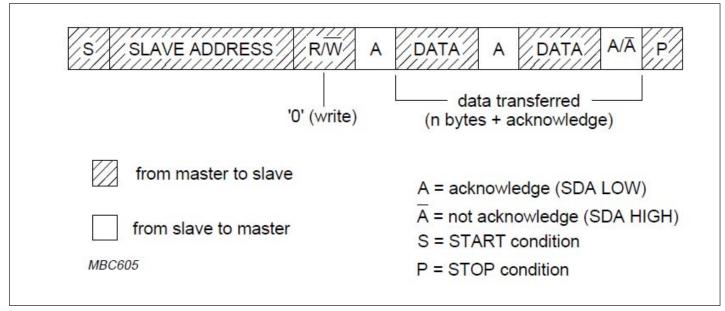

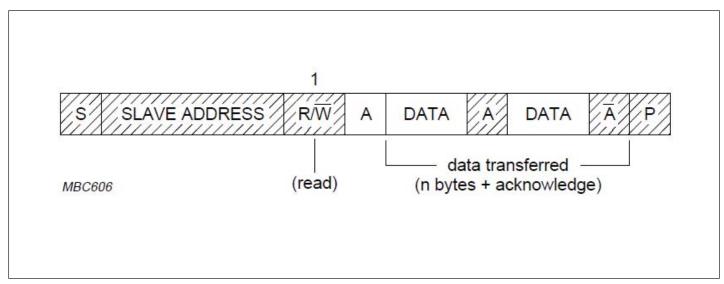

Data is transmitted to the PI3HDMI2410 registers using the Write mode as shown in Figure 2. Data is read from the PI3HDMI2410 registers using the Read mode as shown in Figure 3.

Figure 2 : Write to Control Register

Figure 2 : Read to Control Register

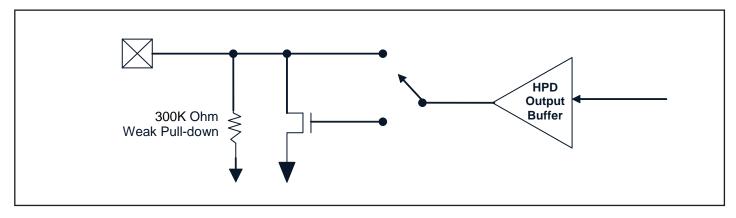

#### **HPD Output Buffer**

#### **Data Channel Pull-down Resistor Control**

Pull-down resistor active conditions:

- 1. The Data Channel is unselected

- 2. Output enable control /OE is disable(/OE=High) or B1b[6]=Low, pull down on all channels

- 3. No normal operation voltage input (but standby voltage SVDD is still On), pull down on all channels

#### **Output Enable control**

Output Disable can be asserted through external  $\overline{OE}$  pin or through I<sup>2</sup>C.

| ŌĒ   | OE_I <sup>2</sup> C B1b[6] | Operation |

|------|----------------------------|-----------|

| Low  | High                       | Enable    |

| Low  | Low                        | Disable   |

| High | Х                          | Disable   |

Default value:  $\overline{OE} = Low$ ; Byte 1 b[6] = High

| Item                               | Rating                         |

|------------------------------------|--------------------------------|

| Supply Voltage to Ground Potential | 5.5V                           |

| All Inputs and Outputs             | -0.5V to V <sub>DD</sub> +0.5V |

| Ambient Operating Temperature      | -40 to +85°C                   |

| Storage Temperature                | -65 to +150°C                  |

| Junction Temperature               | 150°C                          |

| Soldering Temperature              | 260°C                          |

#### Absolute Maximum Ratings (Over operating free-air temperature range)

Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

#### **Recommended Operation Conditions**

| Parameter                                         | Min. | Тур. | Max. | Unit |

|---------------------------------------------------|------|------|------|------|

| Ambient Operating Temperature                     | -40  |      | +85  | °C   |

| Power Supply Voltage (measured in respect to GND) | +3.0 |      | +3.6 | V    |

#### **DC** Specifications

$V_{DD}$  = 3.3V ±10%, Ambient Temperature 0 to +70°C

| Symbol  | Parameter                                 | Conditions                                                                                     | Min                   | Nom  | Max  | Units |

|---------|-------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------|------|------|-------|

| VDD     | Operating Voltage                         |                                                                                                | 3.0                   | 3.3  | 3.6  | V     |

| Idd     | Supply Current                            | Output Enable                                                                                  |                       | 5.0  | 6    |       |

| Iddq    | Quiescent Supply Cur-<br>rent             | Output Disable                                                                                 |                       | 1.7  | 2    | mA    |

| Voh_ddc | DDC passive switch<br>Output High Voltage | Test condition as $I_O = 0$ (open load), $V_I = 5.5V$                                          | SV <sub>DD</sub> -1.0 |      |      |       |

| Vol_ddc | DDC Buffer Output<br>Low Voltage          | Source side, $I_{OL} = 3mA$<br>External pull-up to 3.3V from<br>1.5k $\Omega$ to 4.7k $\Omega$ |                       |      | 0.4  | V     |

|         | Low vonage                                | Sink side, I <sub>OL</sub> = 3mA                                                               | 0.65                  | 0.75 | 0.95 |       |

| Symbol                                 | Parameter                                      | Conditions                                | Min  | Nom | Max | Units  |  |

|----------------------------------------|------------------------------------------------|-------------------------------------------|------|-----|-----|--------|--|

| Vih_ddc                                | DDC Buffer Input High<br>Voltage               | Source side (VSEL = 0)                    |      | 1.7 |     |        |  |

|                                        |                                                | Sink side (VSEL = 0)                      |      | 0.5 |     |        |  |

| Vil_ddc                                | DDC Buffer Input Low                           | Source side                               |      |     | 0.8 |        |  |

|                                        | Voltage                                        | Sink side (VSEL = 0)                      | 0.45 | 0.5 | 0.6 |        |  |

| V <sub>IH_V5_A</sub> ,                 |                                                |                                           |      |     |     |        |  |

| $V_{IH}V5_B$ ,                         | Input High Voltage of                          |                                           | 2.4  |     |     | V      |  |

| V <sub>IH_V5_C</sub> ,                 | 5V ports                                       |                                           |      |     |     |        |  |

| V <sub>IH_V5_D</sub> ,                 |                                                |                                           |      |     |     | •<br>• |  |

| $V_{IL}V_{5}A'$                        |                                                |                                           |      |     |     |        |  |

| $V_{^{IL}V5_B},$                       | Input Low Voltage of 5V                        |                                           |      |     | 0.8 |        |  |

| $V_{IL_V5_C}$ ,                        | ports                                          |                                           |      |     |     |        |  |

| $V_{IL}V_{5}D'$                        |                                                |                                           |      |     |     |        |  |

| Vol_hpd C                              | Buffer Output Low<br>Voltage                   | $I_{OL} = 4 \text{ mA}$                   |      |     | 0.4 |        |  |

|                                        | Open Drain Output<br>Low Voltage               | $I_{OL} = 4 \text{ mA}$                   | 0    |     | 0.4 |        |  |

| Voh_hpd                                | Buffer Output High<br>Voltage                  | $I_{OH} = 3 \text{ mA}$                   | 2.4  |     |     |        |  |

| Ioff (HPD)                             | Off Leakage Current                            | $V_{\rm DD} = 0$ V, $V_{\rm IN} = 3.6$ V  |      | 12  | 20  |        |  |

|                                        | On Leakage Current                             | $V_{\rm DD}$ = 0V, $V_{\rm IN}$ = 5.5V    |      | 20  | 35  |        |  |

| Ioz_hpd                                | Open Drain Output<br>Leakage Current           | $V_{DD} = 3.6 V, V_{IN} = 3.6 V$          |      | 12  | 15  | — μΑ   |  |

|                                        |                                                | $V_{DD} = 3.6V, V_{IN} = 5.5V$            |      | 21  | 38  |        |  |

| $V_{\text{OL}\_\text{DDC}\_\text{WP}}$ | Open Drain Output<br>Low Voltage               | $I_{OL} = 4 \text{ mA}$                   |      |     | 0.4 | V      |  |

| C <sub>IO</sub> <sup>1</sup>           | Input/output capaci-<br>tance (Passive Switch) | $V_{DD} = 0V$ or 3.0V, Frequency = 100kHz |      | 6   | 9   | pF     |  |

#### Note:

1. Measured at Vbias = 0V or 5V, Vrms = 0.2V;

Vbias = 1.65V, Vrms = 0.9V; Vbias = 2.5V, Vrms = 1.2V.

#### **Dynamic Specifications**

$V_{DD}$  = 3.3V ±10%,  $T_{A}$  -40 to +85°C, GND = 0V

| Parameter        | Description                                           | Conditions    | Min | Тур   | Max | Units |

|------------------|-------------------------------------------------------|---------------|-----|-------|-----|-------|

| Xtalk            | Crosstalk on High-speed<br>Channels                   | f = 1.13 GHz  |     | -34   |     | — dB  |

|                  |                                                       | f = 825 GHz   |     | -36   |     |       |

| O <sub>IRR</sub> | OFF Isolation on High-speed<br>Channels               | f = 1.13 GHz  |     | -28   |     |       |

|                  |                                                       | f = 825 GHz   |     | -32   |     |       |

| ILOSS            | Defferential Insertion Loss on<br>High-speed Channels | DR = 1.65Gbps |     | -1.5  |     | dB    |

|                  |                                                       | DR = 2.0Gbps  |     | -1.73 |     |       |

|                  |                                                       | DR = 2.25Gbps |     | -1.82 |     |       |

|                  |                                                       | DR = 3.0Gbps  |     | -1.99 |     |       |

|                  |                                                       | DR = 3.4Gbps  |     | -2.08 |     |       |

| BW               | -3dB BW for TMDS channels                             |               |     | 2.5   |     | GHz   |

#### **Capacitance Measurement** ( $V_{DD} = 3.3V$ , $T_A = 25^{\circ}C$ )

| Test Condition | Capacitance | Units |

|----------------|-------------|-------|

| SDA_CTL        | 3.0         |       |

| SCL_CTL        | 2.3         | pF    |

| HPD_Sink       | 1.7         |       |

Vbias=0.6V

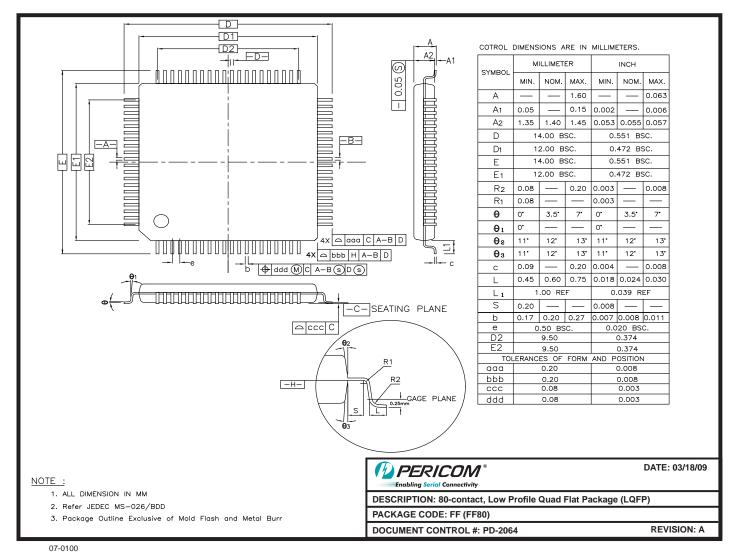

#### Packaging Mechanical: 80-Contact LQFP (FF)

Note:

• For latest package info, please check: http://www.pericom.com/products/packaging/mechanicals.php

#### **Ordering Information**

| Ordering Code  | Package Code | Package Type                      |

|----------------|--------------|-----------------------------------|

| PI3HDMI2410FFE | FF           | Pb-free & Green, 80-Contact, LQFP |

1. Thermal characteristics can be found on the company web site at www.pericom.com/packaging/

2. E = Pb-free and Green

3. Adding an X suffix = Tape/Reel

#### Pericom Semiconductor Corporation • 1-800-435-2336