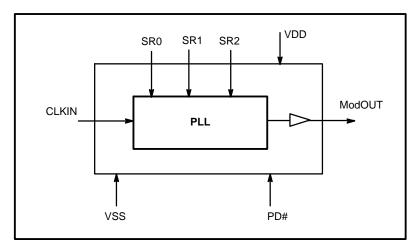

Figure 1. Block Diagram

PCS3PS550A modulates the output of a single PLL in order to "spread" the bandwidth of a synthesized clock, and more importantly, decreases the peak amplitudes of its harmonics. This results in significantly lower system EMI compared to the typical narrow band signal produced by oscillators and most frequency generators. Lowering EMI by increasing a signal's bandwidth is called 'spread spectrum clock generation'.

PCS3PS550A accepts an input from an external reference clock and locks to a 1x modulated clock output. SR0, SR1 and SR2 pins enable selecting one of the eight different frequency deviations (Refer *Frequency Deviation Selection table*). PCS3PS550A also features power down option for power save. PCS3PS550A operates over a supply voltage range of 2.3 V to 3.6 V. PCS3PS550A is available in an 8 Pin WDFN, (2 mm x 2 mm) Package.

**Table 1. PIN DESCRIPTION**

| Pin# | Pin Name | Туре | Description                                                                                                                                                                                                   |  |  |

|------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1    | CLKIN    | 1    | External reference clock input.                                                                                                                                                                               |  |  |

| 2    | SR2      | I    | Digital logic input used to select Spreading Range. There is NO default state. Refer Frequency Deviation Selection Table.                                                                                     |  |  |

| 3    | PD#      | I    | Power–down control pin. Powers down the entire chip. There is NO default state. Pull low to enable power–down mode. Connect to VDD to disable Power Down. Output Clock will be LOW when power down is enabled |  |  |

| 4    | VSS      | Р    | Ground connection.                                                                                                                                                                                            |  |  |

| 5    | ModOUT   | 0    | Spread Spectrum Clock Output.                                                                                                                                                                                 |  |  |

| 6    | SR1      | I    | Digital logic input used to select Spreading Range. This pin has an internal pull-up resistor.<br>Refer Modulation Selection Table.                                                                           |  |  |

| 7    | SR0      | l    | Digital logic input used to select Spreading Range. There is NO default state. Refer Frequency Deviation Selection Table.                                                                                     |  |  |

| 8    | VDD      | Р    | Power supply for the entire chip                                                                                                                                                                              |  |  |

**Table 2. FREQUENCY DEVIATION SELECTION TABLE**

| SR2 | SR1 | SR0 | Spreading Range<br>(±%) (@ 24 MHz) |

|-----|-----|-----|------------------------------------|

| 0   | 0   | 0   | 1                                  |

| 0   | 0   | 1   | 2.5                                |

| 0   | 1   | 0   | 1.25                               |

| 0   | 1   | 1   | 1.5                                |

| 1   | 0   | 0   | 0.4                                |

| 1   | 0   | 1   | 0.75                               |

| 1   | 1   | 0   | 1.75                               |

| 1   | 1   | 1   | 2                                  |

## **Table 3. OPERATING CONDITIONS**

| Symbol          | Parameter                                      |     | Max | Unit |

|-----------------|------------------------------------------------|-----|-----|------|

| $V_{DD}$        | Supply Voltage with respect to V <sub>SS</sub> | 2.3 | 3.6 | V    |

| T <sub>A</sub>  | Operating temperature                          | -20 | +85 | °C   |

| C <sub>L</sub>  | Load Capacitance                               |     | 15  | pF   |

| C <sub>IN</sub> | Input Capacitance                              |     | 7   | pF   |

#### **Table 4. ABSOLUTE MAXIMUM RATING**

| Symbol              | Parameter                                            | Rating       | Unit |

|---------------------|------------------------------------------------------|--------------|------|

| $V_{DD}$ , $V_{IN}$ | Voltage on any input pin with respect to VSS         | -0.5 to +4.6 | V    |

| T <sub>STG</sub>    | Storage temperature                                  | -65 to +125  | °C   |

| T <sub>A</sub>      | Operating temperature                                | -40 to +85   | °C   |

| T <sub>s</sub>      | Max. Soldering Temperature (10 sec)                  | 260          | °C   |

| TJ                  | Junction Temperature                                 | 150          | °C   |

| $T_DV$              | Static Discharge Voltage (As per JEDEC STD22-A114-B) | 2            | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

## **Table 5. DC ELECTRICAL CHARACTERISTICS**

| Symbol           | Parameter                                              | Min                    | Тур | Max                   | Unit |

|------------------|--------------------------------------------------------|------------------------|-----|-----------------------|------|

| $V_{DD}$         | Supply Voltage with respect to V <sub>SS</sub>         | 2.3                    | 2.8 | 3.6                   | V    |

| V <sub>IH</sub>  | Input high voltage                                     | 0.65 * V <sub>DD</sub> |     |                       | V    |

| V <sub>IL</sub>  | Input low voltage                                      |                        |     | 0.3 * V <sub>DD</sub> | V    |

| I <sub>IH</sub>  | Input high current (SR1 control pin)                   |                        |     | 50                    | μΑ   |

| I <sub>IL</sub>  | Input low current (SR1 control pin)                    |                        |     | 50                    | μΑ   |

| V <sub>OH</sub>  | Output high voltage (I <sub>OH</sub> = -8 mA)          | 0.75 * V <sub>DD</sub> |     |                       | V    |

| V <sub>OL</sub>  | Output low voltage (I <sub>OL</sub> = 8 mA)            |                        |     | 0.2 * V <sub>DD</sub> | V    |

| I <sub>CC</sub>  | Static supply current (PD# pulled to V <sub>SS</sub> ) |                        |     | 1                     | μΑ   |

| I <sub>DD</sub>  | Dynamic supply current (Unloaded Output @ 24 MHz)      |                        | 6   | 9                     | mA   |

| Z <sub>OUT</sub> | Output impedance                                       |                        | 40  |                       | Ω    |

#### **Table 6. AC ELECTRICAL CHARACTERISTICS**

| Symbol                   | Parameter                                                                    | Min             | Тур   | Max   | Unit |    |

|--------------------------|------------------------------------------------------------------------------|-----------------|-------|-------|------|----|

| CLKIN                    | Input Clock frequency                                                        | 18              | 24    | 40    | MHz  |    |

| ModOUT                   | Output Clock frequency                                                       | 18              | 24    | 40    | MHz  |    |

| t <sub>LH</sub> (Note 1) | Output rise time                                                             | Unloaded Output |       | 0.8   | 1.2  | ns |

|                          | (Measured between 20% to 80%)                                                | CL = 15 pF      |       | 2.4   | 3    |    |

| t <sub>HL</sub> (Note 1) | Output fall time<br>(Measured between 80% to 20%)                            | Unloaded Output |       | 0.6   | 1    | ns |

|                          |                                                                              | CL = 15 pF      |       | 1.9   | 2.8  | 1  |

| t <sub>JC</sub> (Note 1) | Jitter (cycle to cycle) Unloaded Output                                      |                 | ± 175 | ± 250 | ps   |    |

| t <sub>D</sub> (Note 1)  | Output duty cycle                                                            | 45              | 50    | 55    | %    |    |

| t <sub>ON</sub> (Note 1) | PLL lock Time (Stable power supply, va CLKIN pin, PD# toggled from Low to Hi |                 |       | 3     | ms   |    |

| fd <sub>var</sub>        | Frequency Deviation Variation across F                                       | PVT             |       | ±2.5  | ±5   | %  |

<sup>1.</sup> Parameter is guaranteed by design and characterization. Not 100% tested in production

NOTE: Refer Pin Description table for Functionality details.

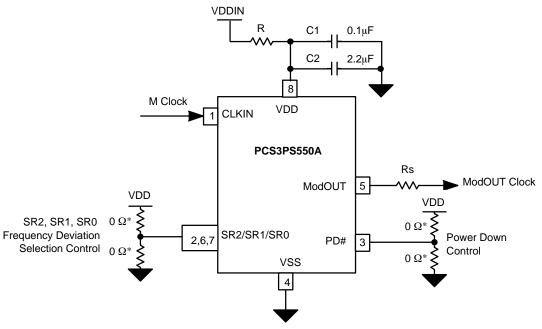

\*Choose the 0 Ohms resistor either to VDD or to VSS based on the logic state to be set for the control signal

Figure 2. Typical Application Schematic

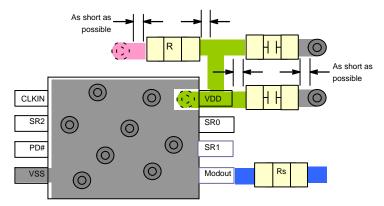

### **PCB Layout Recommendation**

For optimum device performance, following guidelines are recommended.

- Dedicated V<sub>DD</sub> and V<sub>SS</sub> (GND) planes.

- The device must be isolated from system power supply noise. A 0.1µF and a 2.2 µF decoupling capacitor should be mounted on the component side of the board as close to the VDD pin as possible. No vias should be used between the decoupling capacitor and VDD pin. The PCB trace to VDD pin and the ground via should be kept as short as possible. All the VDD pins should have decoupling capacitors.

- In an optimum layout all components are on the same side of the board, minimizing vias through other signal layers. A typical layout is shown in the figure

Figure 3.

#### **ORDERING INFORMATION**

| Part Number      | Top Marking | Temperature    | Package Type                 | Shipping <sup>†</sup> |

|------------------|-------------|----------------|------------------------------|-----------------------|

| PCS3PS550AG-08CR | CA          | –20°C to +85°C | 8L- WDFN (TDFN)<br>(Pb-Free) | 3000 / Tape & Reel    |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

\*A "microdot" placed at the end of last row of marking or just below the last row toward the center of package indicates Pb–Free.

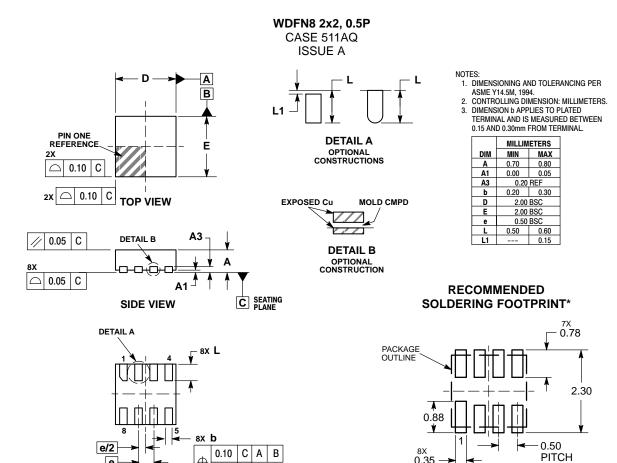

#### PACKAGE DIMENSIONS

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

DIMENSIONS: MILLIMETERS

Timing-Safe is a trademark of Semiconductor Components Industries, LLC (SCILLC).

**BOTTOM VIEW**

0.05 C

NOTE 3

ON Semiconductor and the unare registered trademarks of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries. SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/sike/pdf/Patent–Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regardin

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center Phone: 81-3-5817-1050 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative