### **ABSOLUTE MAXIMUM RATINGS**

| VCCA to AGND                    | 0.3V, +6.0V                     |

|---------------------------------|---------------------------------|

| VCCD to DGND                    | 0.3V, +6.0V                     |

| VCCA to VCCD                    | ±6.3V                           |

| Digital I/O Pins (D0-D6, CLK, F | RXEN, TXEN)                     |

|                                 | 0.3V to (VCCD + 0.3V) or 6.0V   |

|                                 | (whichever is smaller)          |

| Analog I/O Pins (AIO+, AIO-)    | , ,                             |

| to AGND                         | .(VCCA - 1.5V) to (VCCA + 0.3V) |

| AGND to DGND                    | -0.3V, +0.3V                    |

| W  |

|----|

|    |

| °C |

| °C |

| °C |

| °C |

|    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

(VCCA = VCCD = 3.0V,  $f_{CLK}$  = 15MHz,  $R_L$  =  $\infty$ ,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                               | SYMBOL             |                                                  | CONDITIONS                   | MIN | TYP  | MAX | UNITS         |  |

|-----------------------------------------|--------------------|--------------------------------------------------|------------------------------|-----|------|-----|---------------|--|

| TRANSMIT DAC DC ACCURAC                 | Y (Note 1)         |                                                  |                              |     |      |     | -             |  |

| Resolution                              | N                  |                                                  |                              | 7   |      |     | Bits          |  |

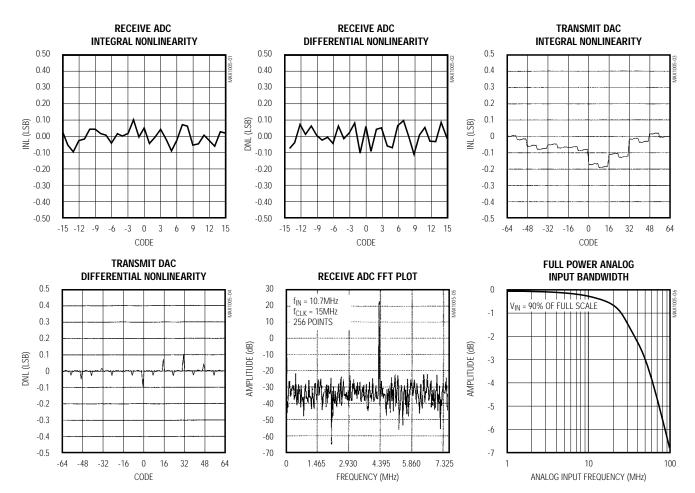

| Integral Nonlinearity                   | INL                |                                                  |                              |     | ±0.2 | ±1  | LSB           |  |

| Differential Nonlinearity               | DNL                |                                                  |                              |     | ±0.2 | ±1  | LSB           |  |

| Offset Error                            |                    |                                                  |                              |     |      | ±1  | LSB           |  |

| Transmit Full-Scale Output Voltage      | Vout               |                                                  |                              | 736 | 800  | 864 | mVp-p         |  |

| TRANSMIT DAC DYNAMIC PERI               | FORMANCE           | $E(T_A = +25^{\circ}C)$ (I                       | Note 2)                      |     |      |     |               |  |

| Spurious-Free Dynamic Range             | SFDR               | (Note 3)                                         | VCCA = VCCD = 3.0V           | 28  | 39   |     | dBc           |  |

| Spurious-Free Dynamic Range             | SFUR               | (Note 3)                                         | VCCA = VCCD = 2.7V to 5.5V   |     | 39   |     |               |  |

| Total Harmonic Distortion plus<br>Noise | THD+N              | (Note 4)                                         | VCCA = VCCD = 3.0V           |     |      | -28 | dBc           |  |

| Wakeup Time Exiting Shutdown            | twake              |                                                  |                              |     | 0.7  | 2.4 | μs            |  |

| Clock Feedthrough                       |                    | (Note 5)                                         |                              |     | -50  |     | dBc           |  |

| DAC Latency                             |                    | (Notes 6, 7)                                     |                              |     |      | 0.5 | CLK<br>period |  |

| Power-Supply Rejection                  | PSR                | VCC_ (A or D or both) = 3.0V ±100mVp-p at 100kHz |                              |     | 67   |     | dB            |  |

| TRANSMIT ADC DC ACCURAC                 | <b>Y</b> (Note 8)  |                                                  |                              |     |      |     |               |  |

| Resolution                              | N                  |                                                  |                              | 5   |      |     | Bits          |  |

| Integral Nonlinearity                   | INL                |                                                  |                              |     | ±0.2 |     | LSB           |  |

| Differential Nonlinearity               | DNL                |                                                  |                              |     | ±0.2 |     | LSB           |  |

| Offset Error                            |                    | AIO+ = AIO-                                      |                              |     | ±2   |     | LSB           |  |

| Full-Scale Input Range                  | VIN                |                                                  |                              | 368 | 400  | 432 | mV            |  |

| RECEIVE ADC DYNAMIC PERFO               | RMANCE             | $(T_A = +25^{\circ}C)$ (No                       | ote 8)                       |     |      |     |               |  |

| Total Harmania Distortion               | TUD                | (Natao 0, 10)                                    | VCCA = VCCD = 3.0V           |     | -42  | -24 | dП            |  |

| Total Harmonic Distortion               | THD                | (Notes 9, 10)                                    | VCCA = VCCD = 2.7V to 5.5V   |     | -42  |     | - dB          |  |

| Courieus Fras Dunamia Dezes             | SFDR               | (Noto 0)                                         | VCCA = VCCD = 3.0V           | 24  | 44   |     | — dB          |  |

| Spurious-Free Dynamic Range             | SFUR               | (Note 9)                                         | VCCA = VCCD = 2.7V to 5.5V   |     | 44   |     |               |  |

| Effective Number of Rits                | ENOR               | (Note 9)                                         | VCCA = VCCD = 3.0V           | 4.5 | 4.9  |     | Bits          |  |

| Effective Number of Bits                | er of Bits ENOB (N | (11016 9)                                        | VCCA = VCCD = 2.7V  to  5.5V |     | 4.9  |     | — BIIS        |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

(VCCA = VCCD = 3.0V,  $f_{CLK}$  = 15MHz,  $R_L$  =  $\infty$ ,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                   | SYMBOL          |                                                             | CONDITIONS                               | MIN           | TYP                     | MAX                                    | UNITS  |     |     |       |

|---------------------------------------------|-----------------|-------------------------------------------------------------|------------------------------------------|---------------|-------------------------|----------------------------------------|--------|-----|-----|-------|

| Input Full-Power Bandwidth (-1dB)           |                 | V <sub>IN</sub> = 90% of full scale                         |                                          | 15            | 25                      |                                        | MHz    |     |     |       |

| Conversion Rate                             |                 |                                                             |                                          | 15            |                         |                                        | Msps   |     |     |       |

| Wakeup Time Exiting Shutdown Mode           | twake           |                                                             |                                          |               | 0.6                     | 2.4                                    | μs     |     |     |       |

| Power-Supply Rejection                      | PSR             | VCC_ (A or D or 100kHz                                      | both) = $3.0V \pm 100$ mVp-p at          |               | <0.1                    |                                        | LSB    |     |     |       |

| ANALOG INPUT/OUTPUT (AIO+                   | , AIO-) (Note   | e 11)                                                       |                                          |               |                         |                                        |        |     |     |       |

| Input Resistance                            | R <sub>IN</sub> | $T_A = +25$ °C, diff<br>AIO-                                | ferential between AIO+ and               | 1.56          | 2.00                    | 2.44                                   | kΩ     |     |     |       |

| Input Resistance Temperature<br>Coefficient | TCRIN           |                                                             |                                          |               | -2000                   |                                        | ppm/°C |     |     |       |

| Input Canaditance (Note 4)                  | Civi            | Differential betw                                           | een AIO+ and AIO-                        |               |                         | 4                                      | »E     |     |     |       |

| Input Capacitance (Note 6)                  | CIN             | AIO+ or AIO- to                                             | GND                                      |               |                         | 4                                      | pF     |     |     |       |

| POWER REQUIREMENTS                          |                 |                                                             |                                          |               |                         |                                        |        |     |     |       |

| Supply Voltage                              | VCCA,<br>VCCD   |                                                             |                                          | 2.7           |                         | 5.5                                    | V      |     |     |       |

| Analog Cumhi Current                        | ICCA            | VCCA = VCCD                                                 | RXEN = 1, TXEN = 0,<br>ADC on, DAC off   |               | 9.0                     | 14.8                                   | A      |     |     |       |

| Analog Supply Current                       | ICCA            | = 3.0V,<br>C <sub>L</sub> ≤ 12.5pF                          |                                          |               | C <sub>L</sub> ≤ 12.5pF | RXEN = 0, TXEN = 1,<br>ADC off, DAC on |        | 2.5 | 3.8 | MA mA |

| District Coursels Coursels                  | 1000            | VCCA = VCCD                                                 | RXEN = 1, TXEN = 0,<br>ADC on, DAC off   |               | 4.0                     | 6.4                                    | 0      |     |     |       |

| Digital Supply Current                      | ICCD            | = 3.0V,<br>C <sub>L</sub> ≤ 12.5pF                          | RXEN = 0, TXEN = 1,<br>ADC off, DAC on   |               | 3.0                     | 5.6                                    | - mA   |     |     |       |

| Shutdown Supply Current                     | ICCA +<br>ICD   | VCCA = VCCD = 3.0V, C <sub>L</sub> ≤ 12.5pF,<br>RXEN = TXEN |                                          |               | <0.1                    | 5                                      | μΑ     |     |     |       |

| DIGITAL INPUTS/OUTPUTS (D0                  | D6, RXEN,       | TXEN, CLK) (No                                              | ote 12)                                  |               |                         |                                        |        |     |     |       |

| Output High Voltage                         | VoH             | D0-D4, VCCD = ISOURCE = 200µ                                |                                          | VCCD - 1      | 1.0                     | VCCD                                   | V      |     |     |       |

| Output Low Voltage                          | VoL             | D0-D4, VCCD =                                               | = 2.7V to 5.5V, I <sub>SINK</sub> = 50µA | 0             |                         | 0.5                                    | V      |     |     |       |

|                                             | VIH             | VCCD = 2.7V<br>to 5.5V                                      | D0-D6, CLK                               | 0.7VCCE       | )                       |                                        |        |     |     |       |

| Input High Voltage                          |                 |                                                             | RXEN, TXEN                               | VCCD -<br>0.5 |                         | VCCD + 0.1                             | V      |     |     |       |

| Input Low Voltage                           | \ /             | VCCD = 2.7V                                                 | D0-D6, CLK                               |               |                         | 0.3VCCD                                | V      |     |     |       |

| Input Low Voltage                           | VIL             | to 5.5V RXEN, TXEN                                          |                                          | -0.1          |                         | 0.5                                    | ] v    |     |     |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

(VCCA = VCCD = 3.0V, f<sub>CLK</sub> = 15MHz, R<sub>L</sub> = ∞, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted.)

| PARAMETER                    | SYMBOL                       |                                       | CONDITIONS                                         | MIN        | TYP        | MAX       | UNITS |

|------------------------------|------------------------------|---------------------------------------|----------------------------------------------------|------------|------------|-----------|-------|

|                              |                              | D0-D6, CLK; VCCD = 2.7V to 5.5V       |                                                    | -1         |            | 7         |       |

|                              |                              | RXEN, TXEN;                           | TXEN = RXEN                                        |            |            | ±1        |       |

| Input Current                | nput Current I <sub>IN</sub> | VCCD = 2.7V<br>to 3.6V                | TXEN = 0 and RXEN = 1, or<br>TXEN = 1 and RXEN = 0 |            |            | ±2        | μΑ    |

|                              |                              | VCCD = 3.6V TXEN                      | TXEN = RXEN                                        |            |            | ±1        |       |

|                              |                              |                                       | TXEN = 0 and RXEN = 1, or<br>TXEN = 1 and RXEN = 0 |            |            | ±4        |       |

| Input Capacitance            | CIN                          | D0-D6, CLK; T                         | KEN = 1, RXEN = 0 (Note 6)                         |            |            | 8         | pF    |

| TIMING CHARACTERISTICS (Da   | ta Outputs:                  | $R_L = 1M\Omega$ , $C_L =$            | 15pF, $T_A = T_{MIN}$ to $T_{MAX}$ , unless        | s otherwis | se noted.) | (Note 12) |       |

| DAC Data Setup Time          | t <sub>DS</sub>              | $T_A = +25^{\circ}C \text{ (Note 6)}$ |                                                    | 5          | 0.6        |           | ns    |

| DAC Data Hold Time           | tHOLD                        | $T_A = +25^{\circ}C \text{ (Note 6)}$ |                                                    | 5          | 0.3        |           | ns    |

| CLK Duty Cycle               |                              |                                       |                                                    | 45         |            | 55        | %     |

| ADC CLK to Output Data Valid | t <sub>DO</sub>              | C <sub>L</sub> ≤ 12.5pF               |                                                    |            | 13         | 20        | ns    |

- Note 1: TXEN = 1, RXEN = 0. All DAC transfer function parameters are measured differentially from AIO+ to AIO- using the End-Point Linearity method.

- Note 2:  $f_{IN} = 4.3$ MHz digital sine wave applied to DAC data inputs;  $f_{CLK} = 15$ MHz. The reference frequency ( $f_{REF}$ ) is defined to be 10.7MHz ( $f_{CLK} f_{IN}$ ). All frequency components present in the DAC output waveform except for  $f_{REF}$  and  $f_{IN}$  are considered spurious.

- **Note 3:** For DAC SFDR measurements, the amplitude of f<sub>REF</sub> (10.7MHz) is compared to the amplitudes of all frequency components of the output waveform except for f<sub>IN</sub> (4.3MHz).

- Note 4: For DAC measurements, THD+N is defined as the ratio of the square-root of the sum-of-the-squares of the RMS values of all harmonic and noise components of the output waveform (except for f<sub>IN</sub> and f<sub>REF</sub>) to the RMS amplitude of the f<sub>REF</sub> component

- **Note 5:** Clock feedthrough is defined as the difference in amplitude between the f<sub>REF</sub> component and the f<sub>CLK</sub> component when measured differentially from AIO+ to AIO-.

- Note 6: Guaranteed by design. Not production tested.

- **Note 7:** The DAC input interface is a master/slave register. An additional half clock cycle is required for data at the digital inputs to propagate through to the DAC switches.

- Note 8: RXEN = 1, TXEN = 0. Unless otherwise noted, for all receive ADC measurements, the analog input signal is applied differentially from AIO+ to AIO-, specified using the Best-Fit Straight-Line Linearity method.

- Note 9:  $f_{IN} = 10.7 \text{MHz}$ ,  $f_{CLK} = 15 \text{MHz}$ . Amplitude is 1dB below full-scale. The reference frequency (f<sub>REF</sub>) is defined to be 4.3MHz (f<sub>CLK</sub> f<sub>IN</sub>). All components except for f<sub>REF</sub> and f<sub>IN</sub> are considered spurious.

- Note 10: Receive ADC THD measurements include the first five harmonics.

- **Note 11:** CAUTION: Operation of the analog inputs AIO+ and AIO- (pins 4 and 5) at more than 1.5V below VCCA could cause latchup and possible destruction of the part. Avoid shunt capacitances to GND on these pins. If shunt capacitances are required, then bypass these pins only to VCCA.

- Note 12: All digital input signals are measured from 50% amplitude reference points. All digital output signal propagation delays are measured to V<sub>OH(AC)</sub> for rising output signals and to V<sub>OL(AC)</sub> for falling output signals. The values for V<sub>OH(AC)</sub> and V<sub>OL(AC)</sub> as a function of the VCCD supply are shown in the following table:

| VCCD (V)   | V <sub>OH(AC)</sub> (V) | V <sub>OL(AC)</sub> (V) |

|------------|-------------------------|-------------------------|

| 2.7 to 3.3 | VCCD - 1.1              | 0.5                     |

| 3.3 to 5.5 | 2/3 x VCCD              | 0.5                     |

## Typical Operating Characteristics

(VCCA = VCCD = 3.0V,  $T_A = +25$ °C, unless otherwise noted.)

### Pin Description

| PIN   | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VCCD   | Digital Supply Voltage, +2.7V to +5.5V                                                                                                                                                                                                                                                                                                                                                                                                         |

| 2     | DGND   | Digital Ground. Connect to digital ground plane.                                                                                                                                                                                                                                                                                                                                                                                               |

| 3     | RXEN   | Receive ADC Enable Input. A logic-high level on this input combined with a logic-low level on TXEN enables the receive ADC and disables the transmit DAC. If RXEN = TXEN, the MAX1005 enters its low-power shut-down mode.                                                                                                                                                                                                                     |

| 4     | AIO+   | Positive Analog Input/Output Pin. If RXEN = 1 and TXEN = 0, then AIO+ is the positive analog input to the receive ADC. If RXEN = 0 and TXEN = 1, then AIO+ is the positive transmit DAC output pin.                                                                                                                                                                                                                                            |

| 5     | AIO-   | Negative Analog Input/Output Pin. If RXEN = 1 and TXEN = 0, then AIO- is the negative analog input to the receive ADC. If RXEN = 0 and TXEN = 1, then AIO- is the negative transmit DAC output pin.                                                                                                                                                                                                                                            |

| 6     | TXEN   | Transmit DAC Enable Input. A logic-high level on this input combined with a logic-low level on RXEN enables the transmit DAC and disables the receive ADC. If RXEN = TXEN, the MAX1005 enters its low-power shutdown mode.                                                                                                                                                                                                                     |

| 7     | AGND   | Analog Ground. Connect to analog ground plane.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8     | VCCA   | Analog Supply Voltage, +2.7V to +5.5V                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9, 10 | D6, D5 | Two MSBs for DAC input data. D6 is the MSB.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11–15 | D4-D0  | Data Input/Output Pins. If RXEN = 0 and TXEN = 1, then D4–D0 function as the five lower bits of DAC input data, with D0 as the LSB. If RXEN = 1 and TXEN = 0, then D4–D0 function as the five data outputs for the ADC, with D4 as the MSB and D0 as the LSB. In low-power shutdown mode (RXEN = TXEN), D0–D4 should not be externally held high, to prevent excessive input leakage currents.                                                 |

| 16    | CLK    | Clock Input. If the receive ADC is active (RXEN = 1, TXEN = 0), the analog input is sampled on the falling edge of clock and the data outputs (D4-D0) are updated on the rising edge of CLK. If the transmit DAC is active (TXEN = 1, RXEN = 0), input data is clocked in on the falling edge of CLK and the DAC output is updated on the rising edge of CLK. The input clock may continue to run when the MAX1005 is shut down (TXEN = RXEN). |

## **Detailed Description**

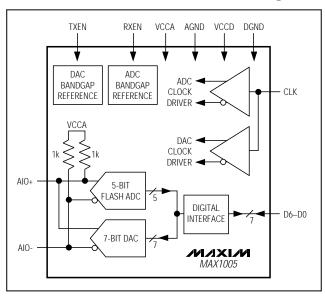

The MAX1005 is designed to operate with the Maxim PWT1900 (TAG-6) wireless transceiver chipset consisting of the MAX2411 RF transceiver, the MAX2511 IF transceiver, and the MAX1007 power-control/diversity IC. The MAX1005 integrates all the functions of an IF undersampler into a single low-power integrated circuit. It is also well suited for other time-division duplex (TDD) communications systems. This device includes a 7-bit transmit DAC, a 5-bit receive ADC, two internal bandgap references, clock drivers, and all necessary interface and control logic.

#### Transmit DAC

The low-side alias frequency (f<sub>CLK</sub> - f<sub>OUT</sub> = 10.7MHz) generated by the MAX1005's 7-bit DAC is used to recreate the IF sub-carrier and transmission data in TDD and other communications systems. The DAC accepts CMOS input data in the twos-complement format and outputs a corresponding analog voltage differentially between AIO+ and AIO-. The full-scale output voltage range is typically ±400mV. The DAC code table is shown in Table 1.

Table 1. Transmit DAC Code Table

| DAC INPUT DATA | ANALOG OUTPUT |

|----------------|---------------|

| 011 1111       | +FS           |

| 000 0000       | 0             |

| 100 0000       | -FS           |

#### Receive ADC

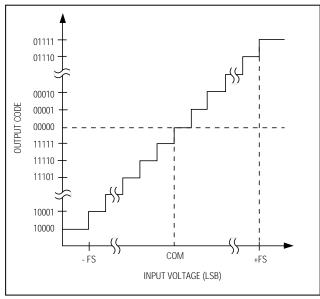

The 5-bit receive ADC is used to directly sample or undersample a downconverted RF signal. The ADC converts an analog input signal to a 5-bit digital output code in the twos-complement format. Figure 1 shows the ADC transfer function.

Analog input signals are applied differentially between AIO+ and AIO-, with a full-scale range of ±200mV. An internal amplifier buffers the input signal and drives the comparator array, minimizing loading on the external signal source. The input amplifier has a full-power -1dB bandwidth of at least 15MHz, making this device ideally suited for undersampling applications.

Figure 1. Receive ADC Transfer Function

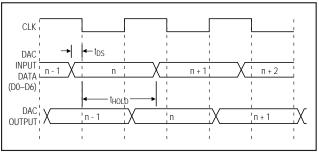

Figure 2. Transmit DAC Timing Diagram

#### Digital Interface

The DAC has a 7-bit parallel digital interface. Figure 2 shows the timing diagram for the transmit DAC. Digital data is latched into the DAC input register on the falling edge of CLK. On the next rising edge of CLK the data is transferred to the DAC register and the DAC output voltage is updated.

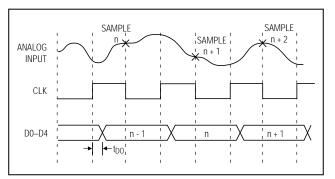

The ADC is enabled by setting TXEN = 0 and RXEN = 1. Figure 3 shows the ADC timing diagram. Input data is sampled on the falling edge of CLK, while output data changes state on the rising edge of CLK. This minimizes digital feedthrough and noise while the analog input is being sampled. The ADC output data is applied to the 5-bit parallel output pins (D0-D4), with the MSB at D4.

Figure 3. Receive ADC Timing Diagram

#### Operating Modes

The MAX1005 has three operating modes: transmit, receive, and shutdown. The operating mode is selected by the RXEN and TXEN inputs, as shown in Table 2.

In transmit mode, the DAC is active and the ADC is inactive. Power consumption is typically 16.5mW with a 3V supply voltage. In receive mode, the ADC is active and the DAC is inactive. Power consumption in this mode is typically 39mW with a 3V supply voltage.

The third mode is shutdown, in which both the DAC and the ADC are inactive. Select this mode by setting RXEN = TXEN at any voltage from DGND to VCCD. In shutdown mode, the CLK input can continue to run without damaging the device and with no significant increase in the typical shutdown supply current specification of  $0.1\mu A$ . When exiting shutdown, the MAX1005 is guaranteed to be operational within  $2.4\mu s$  after TXEN or RXEN is asserted, as shown in Table 2.

To prevent supply-current drain due to leakage currents from entering the ADC output bits, the ADC outputs (D0-D4) should not be held high in low-power shutdown mode.

### **Table 2. Operating Mode Selection**

| RXEN | TXEN | OPERATING MODE                           |

|------|------|------------------------------------------|

| 0    | 0    | Low-power shutdown: ADC and DAC disabled |

| 0    | 1    | Transmit mode: DAC active, ADC disabled  |

| 1    | 0    | Receive mode: ADC active, DAC disabled   |

| 1    | 1    | Low-power shutdown: ADC and DAC disabled |

#### Power-Supply Bypassing and Grounding

The MAX1005 has separate analog (VCCA) and digital (VCCD) power-supply connections, as well as separate analog and digital ground connections to minimize coupling of noisy digital signals into the circuit's analog portion. The device will operate with both of these power supplies connected to any voltage between +2.7V and +5.5V. This feature allows the digital circuitry to operate from a regulated logic power supply; this reduces power consumption and maintains compatibility with external logic, while allowing the analog circuitry to operate from an unregulated supply.

The analog ground (AGND) and digital ground (DGND) should be tied together close to the device. At no time should the voltage between AGND and DGND exceed  $\pm 0.3$ V.

The entire board needs good DC bypassing for both analog and digital supplies. Place the power-supply bypass capacitors close to where the power is routed onto board. 10µF electrolytic capacitors with low equivalent-series-resistance (ESR) ratings are recommended. For best effective bits performance, minimize capacitive loading at the digital outputs. Keep the digital output traces as short as possible. Bypass each of the VCC\_supply pins to its respective GND with high-quality ceramic capacitors located as close to the package as possible.

### Functional Diagram

## Chip Information

TRANSISTOR COUNT: 2377

SUBSTRATE CONNECTED TO AGND

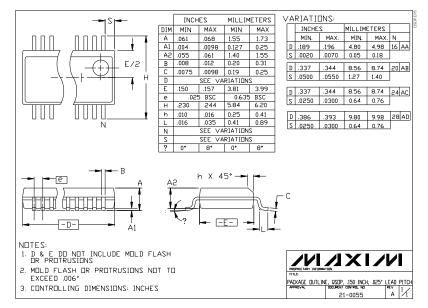

## \_Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

3 \_\_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 1997 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.