# Specifications

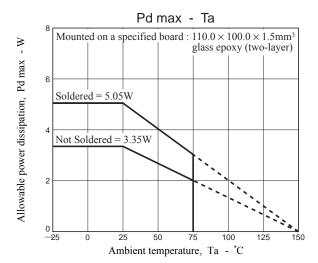

**Absolute Maximum Ratings** at  $Ta = 25^{\circ}C$

| Parameter                    | Symbol | Conditions              | Ratings     | Unit |

|------------------------------|--------|-------------------------|-------------|------|

| Maximum supply voltage       | VD     | Supply voltage          | 20          | V    |

| Allowable power dissipation  | Pd max | Our PCB, Soldered *     | 5.05        | W    |

| Package thermal resistance   | өјс    | Our PCB, Soldered *     | 2.1         | °C/W |

|                              |        | Our PCB, Not soldered * | 3.6         | °C/W |

| Maximum junction temperature | Tj max |                         | 150         | °C   |

| Operating temperature        | Topr   |                         | -25 to +75  | °C   |

| Storage temperature          | Tstg   |                         | -50 to +150 | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### **Recommended Operating Range** at $Ta = 25^{\circ}C$

| Devenuetori          | Ourseland | Quere la la constituire en |     | Ratings |     |      |

|----------------------|-----------|----------------------------|-----|---------|-----|------|

| Parameter            | Symbol    | Conditions                 | min | typ     | max | Unit |

| Supply voltage range | VD        | Supply voltage             | 9   | 15      | 18  | V    |

| Load impedance range | RL        | Speaker load               | 4   | 8       |     | Ω    |

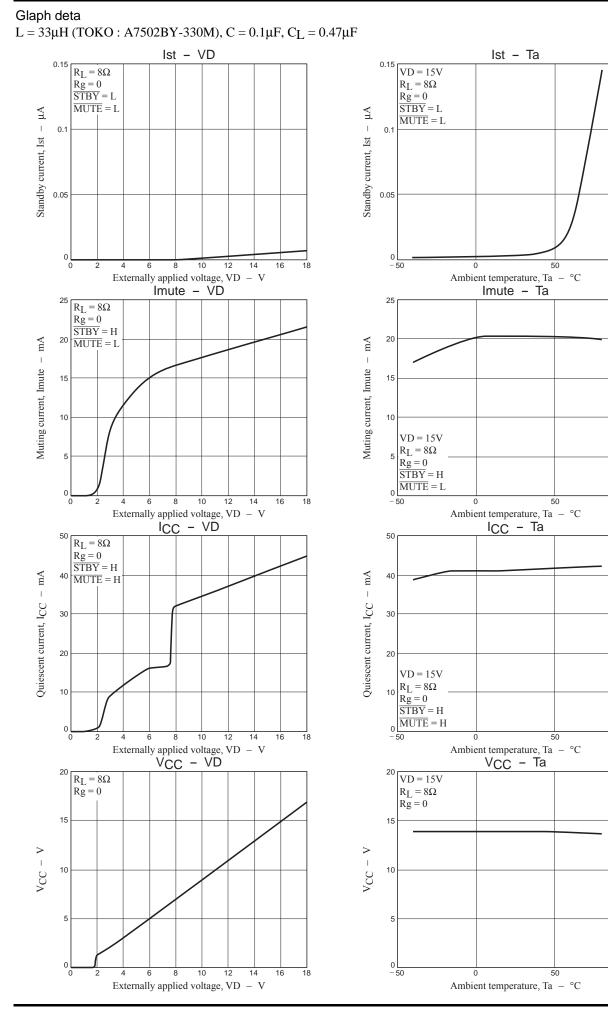

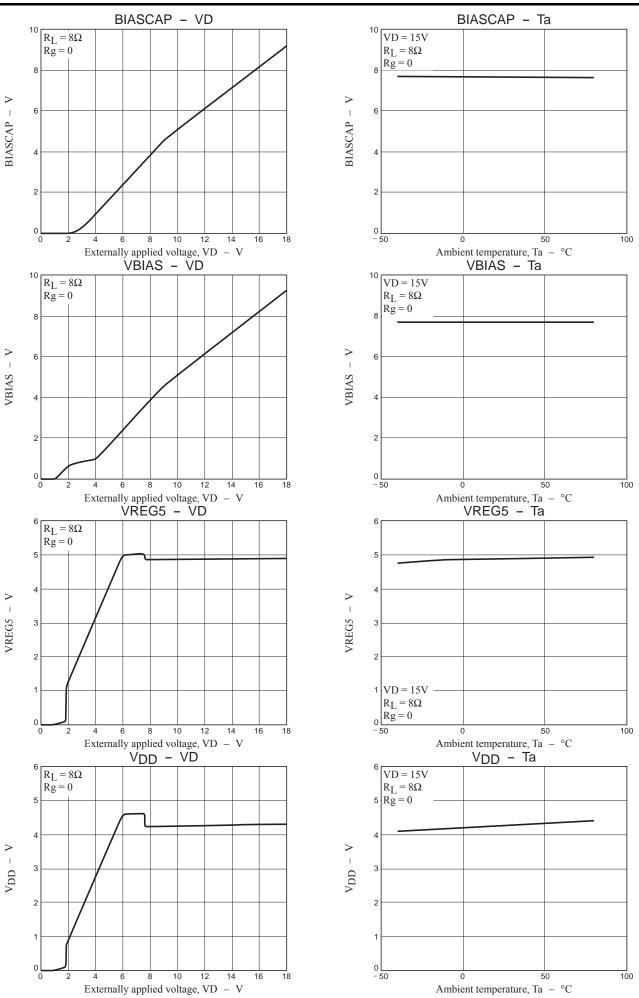

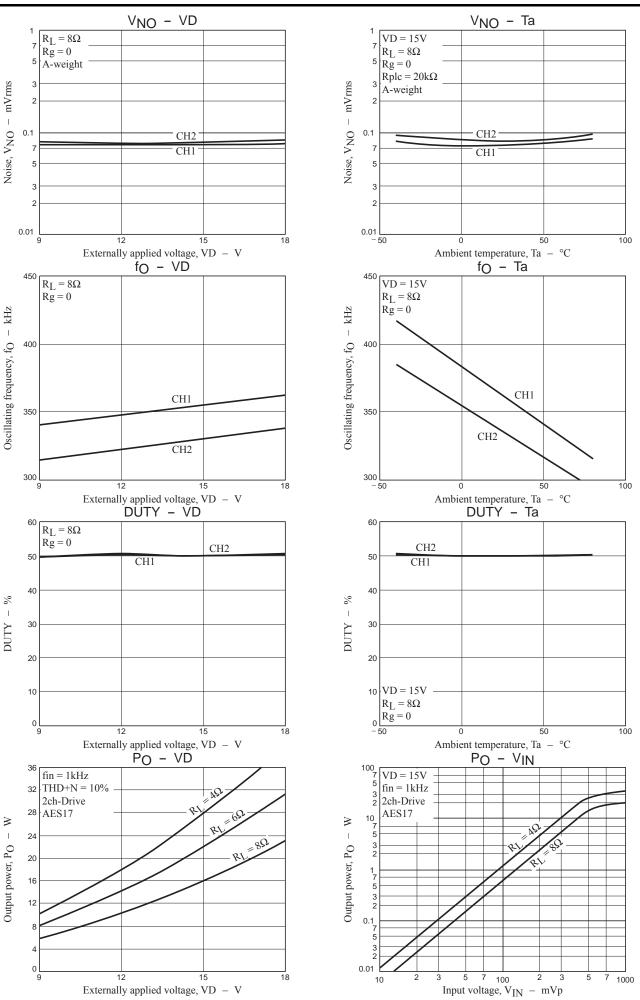

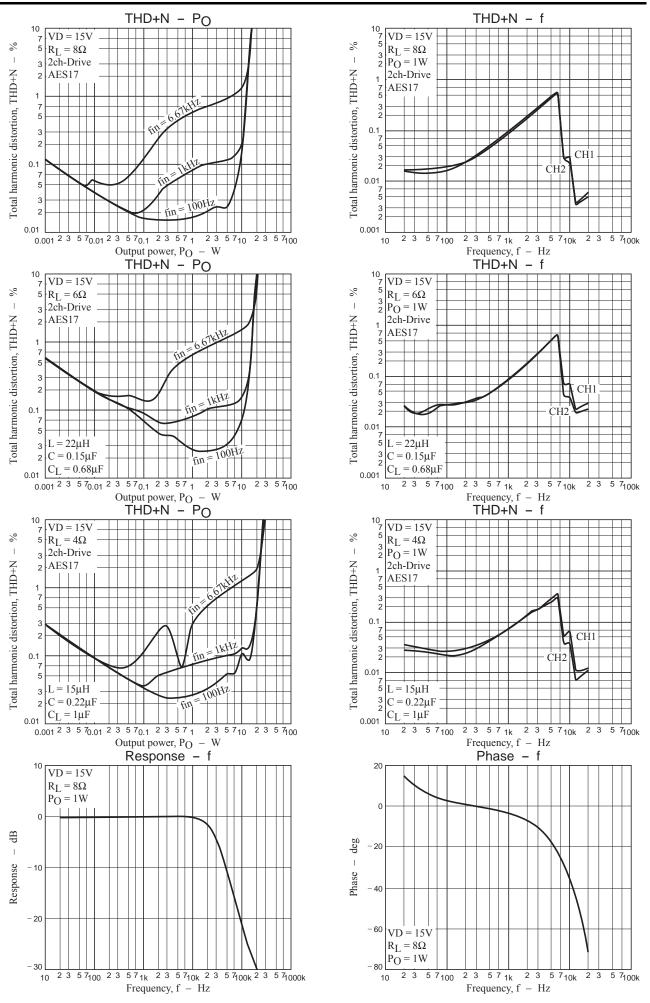

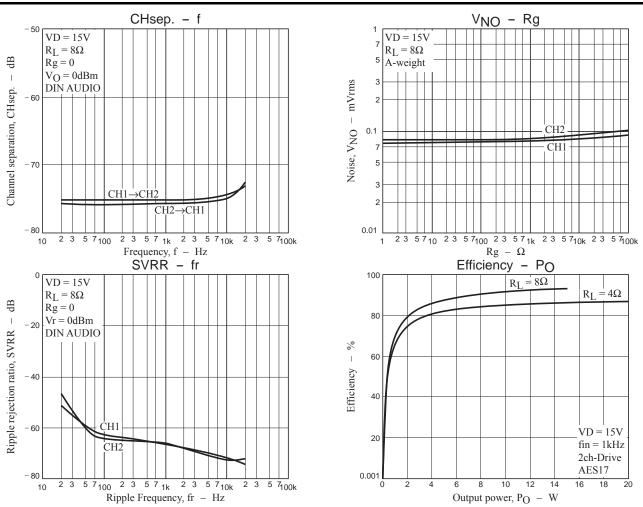

# Electrical Characteristics at Ta = 25°C, VD = 15V, R<sub>L</sub> = 8 $\Omega$ , L = 33 $\mu$ H (TOKO : A7502BY-330M), C = 0.1 $\mu$ F, C<sub>L</sub> = 0.47 $\mu$ F

|                                |                   | O maked                                                                | Ratings |      |     |       |  |

|--------------------------------|-------------------|------------------------------------------------------------------------|---------|------|-----|-------|--|

| Parameter                      | Symbol Conditions |                                                                        | min     | typ  | max | Unit  |  |

| Standby current                | lst               | $\overline{\text{STBY}} = L, \overline{\text{MUTE}} = L$               |         | 1    | 10  | μΑ    |  |

| Mute current                   | Imute             | $\overline{\text{STBY}} = \text{H}, \overline{\text{MUTE}} = \text{L}$ | 14      | 20   | 26  | mA    |  |

| Quiescent current              | ICCO              | $\overline{\text{STBY}} = \text{H}, \overline{\text{MUTE}} = \text{H}$ | 35      | 45   | 55  | mA    |  |

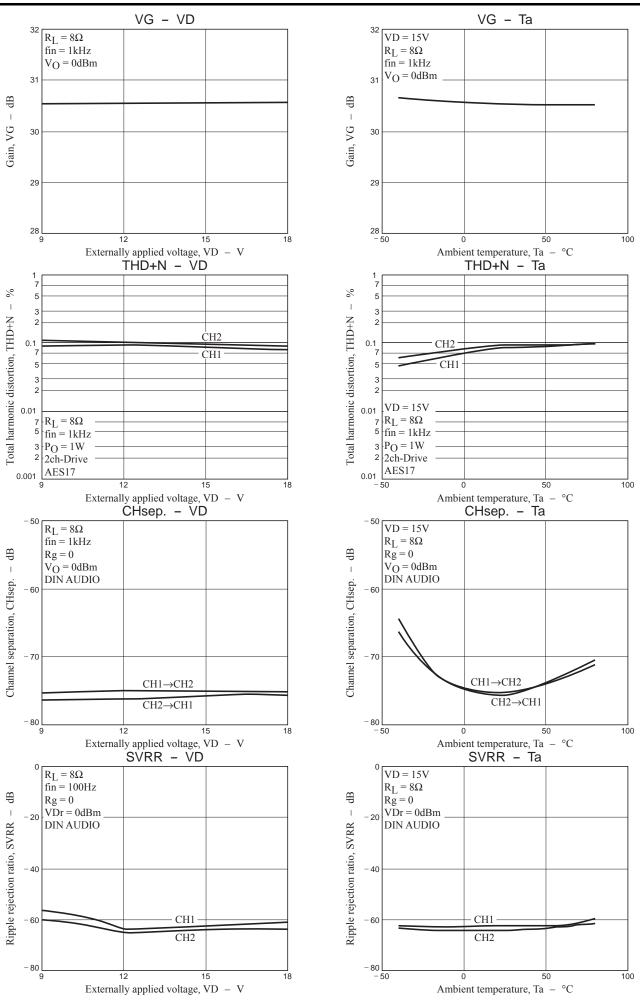

| Voltage gain                   | VG                | fin = 1kHz, V <sub>O</sub> = 0dBm                                      | 28      | 30   | 32  | dB    |  |

| Offset voltage                 | Voffset           | Rg = 0                                                                 | -150    |      | 150 | mV    |  |

| Total harmonic distortion      | THD+N             | P <sub>O</sub> = 1W, fin = 1kHz, AES17                                 |         | 0.08 | 0.4 | %     |  |

| Output power                   | PO@10%            | THD+N = 10%, AES17                                                     | 13      | 15   |     | W     |  |

| Channel separation             | CHsep.            | $Rg = 0, V_{O} = 0dBm, DIN AUDIO$                                      | 55      | 70   |     | dB    |  |

| Ripple rejection ratio         | SVRR              | fr = 100Hz, Vr = 0dBm, Rg = 0, DIN AUDIO                               | 50      | 60   |     | dB    |  |

| Noise                          | V <sub>NO</sub>   | Rg = 0, A-weight                                                       |         | 90   | 300 | μVrms |  |

| High-level input voltage       | VIH               | STBY and MUTE pin                                                      | 3       |      | VD  | V     |  |

| Low-level input voltage        | V <sub>IL</sub>   | STBY and MUTE pin                                                      | 0       |      | 1   | V     |  |

| Under voltage protection UPPER | UV_UPPER          | VD voltage measure                                                     |         | 8.0  |     | V     |  |

| Under voltage protection LOWER | UV_LOWER          | VD voltage measure                                                     |         | 7.0  |     | V     |  |

Note : The values of these characteristics were measured in the Our test environment. The actual values in an end system will vary depending on the printed circuit board pattern, the external components actually used, and other factors.

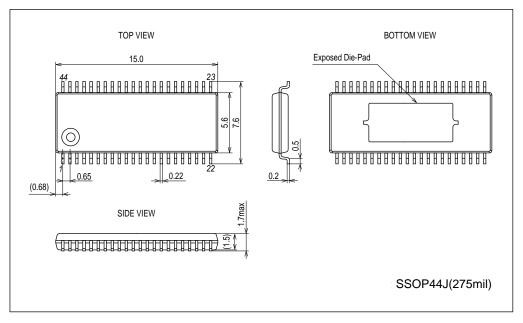

# Package Dimensions

unit : mm (typ) 3285

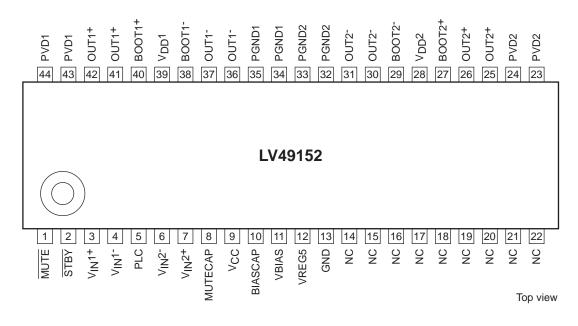

## **Pin Assignment**

## LV49152V

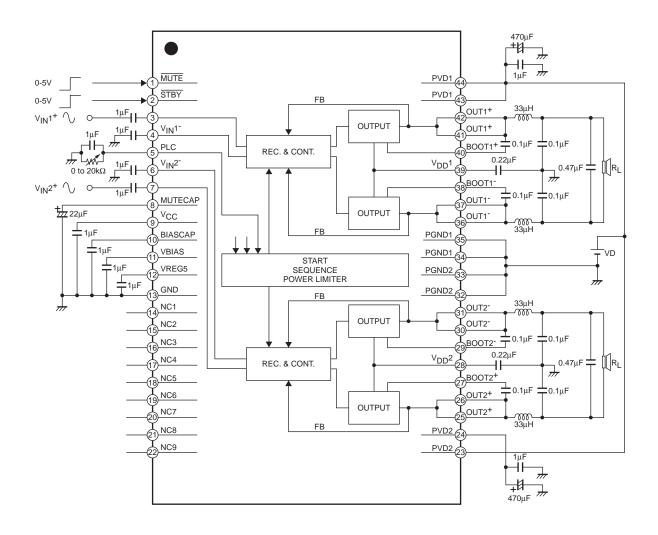

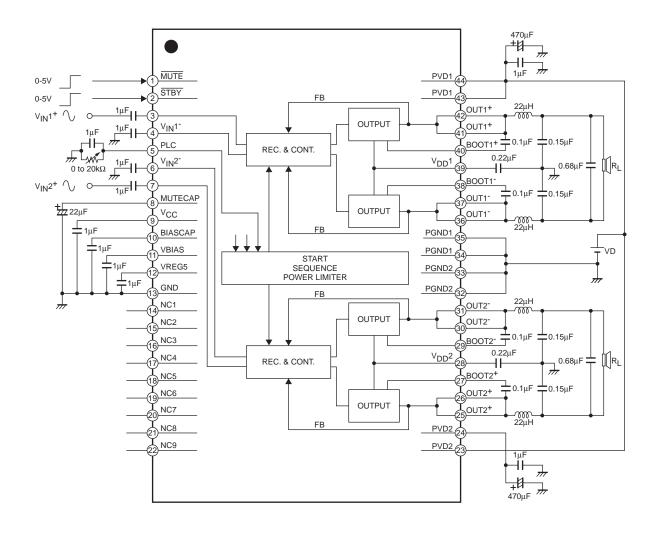

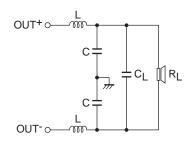

# Block Diagram and Application Circuit Example 1 $(R_L=8\Omega)$

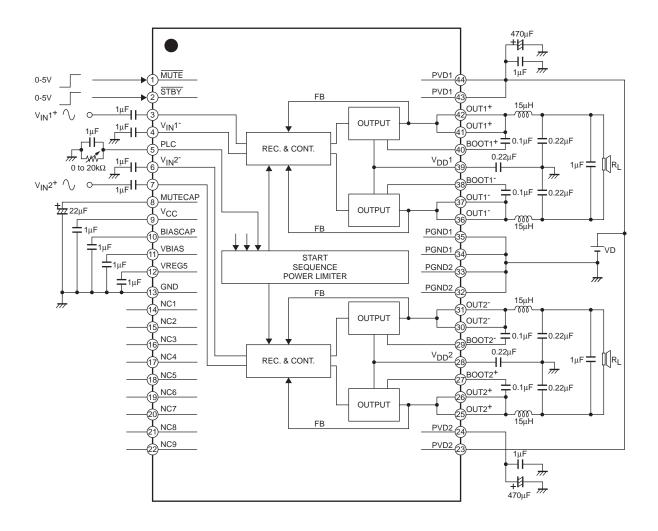

# Application Circuit Example 2 $(R_L=6\Omega)$

# Application Circuit Example 3 $(R_L=4\Omega)$

|         | in Equivalent Circuit          |     |                         |                                    |  |  |

|---------|--------------------------------|-----|-------------------------|------------------------------------|--|--|

| Pin No. | Pin name                       | I/O | Description             | Equivalent Circuit                 |  |  |

| 1       | MUTE                           | 1   | Mute control pin        | VD 250kΩ \$   10kΩ K   100kΩ \$ K  |  |  |

| 2       | STBY                           | 1   | Standby control pin     | VD                                 |  |  |

|         |                                |     |                         | 250kΩ<br>2<br>10kΩ<br>100kΩ<br>GND |  |  |

| 3       | VIN1+                          | 1   | Input pin, CH1 plus     |                                    |  |  |

| 4       | V <sub>IN</sub> 1 <sup>-</sup> | 1   | Input pin, CH1 minus    |                                    |  |  |

| 5       | PLC                            | I   | Power level control pin |                                    |  |  |

| Continued | Continued from preceding page. |     |                                                         |                                                                  |  |  |  |  |

|-----------|--------------------------------|-----|---------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|

| Pin No.   | Pin name                       | I/O | Description                                             | Equivalent Circuit                                               |  |  |  |  |

| 6         | V <sub>IN</sub> 2 <sup>-</sup> | 1   | Input pin, CH2 minus                                    | 6<br>300Ω<br>300Ω<br>S30kΩ<br>VBIAS<br>GND                       |  |  |  |  |

| 7         | VIN2+                          | 1   | Input pin, CH2 plus                                     | ₹300Ω                                                            |  |  |  |  |

| 8         | MUTECAP                        | 0   | Muteing sysytem capcitor connection                     |                                                                  |  |  |  |  |

| 9         | Vcc                            | 0   | Internal power supply<br>decupling capacitor connection | 9<br>GND                                                         |  |  |  |  |

| 10        | BIASCAP                        | 0   | Internal regulator<br>decupling capacitor connection    | VD<br>10<br>1kΩ<br>1kΩ<br>1kΩ<br>1kΩ<br>1kΩ<br>1kΩ<br>1kΩ<br>1kΩ |  |  |  |  |

| Continued | Continued from preceding page. |     |                                                      |                                                                |  |  |  |  |

|-----------|--------------------------------|-----|------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|

| Pin No.   | Pin name                       | I/O | Description                                          | Equivalent Circuit                                             |  |  |  |  |

| 11        | VBIAS<br>VREG5                 | 0   | Internal regulator<br>decupling capacitor connection | VD<br>500Ω<br>(11)<br>500Ω<br>(11)<br>S00Ω<br>(11)<br>VD<br>VD |  |  |  |  |

| 13        | GND                            |     | Analog Ground                                        | []                                                             |  |  |  |  |

| 14        | NC                             |     | Non connection                                       |                                                                |  |  |  |  |

| 15        | NC                             |     | Non connection                                       |                                                                |  |  |  |  |

| 16        | NC                             |     | Non connection                                       |                                                                |  |  |  |  |

| 17        | NC                             |     | Non connection                                       |                                                                |  |  |  |  |

| 18        | NC                             |     | Non connection                                       |                                                                |  |  |  |  |

| 19        | NC                             |     | Non connection                                       |                                                                |  |  |  |  |

| 20        | NC                             |     | Non connection                                       |                                                                |  |  |  |  |

| 21        | NC                             |     | Non connection                                       |                                                                |  |  |  |  |

| 22        | NC                             |     | Non connection                                       |                                                                |  |  |  |  |

| 23        | PVD2                           |     | CH2 power supply                                     |                                                                |  |  |  |  |

| 24        | PVD2                           |     | CH2 power supply                                     |                                                                |  |  |  |  |

| 25        | OUT2+                          | 0   | Output pin, CH2 plus                                 |                                                                |  |  |  |  |

| 26        | OUT2+                          | 0   | Output pin, CH2 plus                                 |                                                                |  |  |  |  |

|         | from preceding p   |     |                                                          |                    |

|---------|--------------------|-----|----------------------------------------------------------|--------------------|

| Pin No. | Pin name           | I/O | Description                                              | Equivalent Circuit |

| 27      | BOOT2+             | I/O | Boot strap pin, CH2 plus                                 |                    |

| 28      | V <sub>DD</sub> 2  | 0   | CH2 internal regulator decupling capacitor<br>connection |                    |

| 29      | BOOT2 <sup>-</sup> | I/O | Boot strap pin, CH2 minus                                |                    |

| 30      | OUT2-              | 0   | Output pin, CH2 minus                                    |                    |

| 31      | OUT2-              | 0   | Output pin, CH2 minus                                    |                    |

| 32      | PGND2              |     | CH2 Power Ground                                         |                    |

| 33      | PGND2              |     | CH2 Power Ground                                         |                    |

| 34      | PGND1              |     | CH1 Power Ground                                         |                    |

| 35      | PGND1              |     | CH1 Power Ground                                         |                    |

| 36      | OUT1"              | 0   | Output pin, CH1 minus                                    |                    |

| 37      | OUT1-              | 0   | Output pin, CH1 minus                                    |                    |

| 38      | BOOT1 <sup>-</sup> | I/O | Boot strap pin, CH1 minus                                |                    |

| 39      | V <sub>DD</sub> 1  | 0   | CH1 internal regulator decupling capacitor connection    |                    |

| 40      | BOOT1+             | I/O | Boot strap pin, CH1 plus                                 |                    |

| Continued | ontinued from preceding page. |     |                      |                    |  |  |  |

|-----------|-------------------------------|-----|----------------------|--------------------|--|--|--|

| Pin No.   | Pin name                      | I/O | Description          | Equivalent Circuit |  |  |  |

| 41        | OUT1+                         | 0   | Output pin, CH1 plus |                    |  |  |  |

| 42        | OUT1 <sup>+</sup>             | 0   | Output pin, CH1 plus |                    |  |  |  |

| 43        | PVD1                          |     | CH1 power supply     |                    |  |  |  |

| 44        | PVD1                          |     | CH1 power supply     |                    |  |  |  |

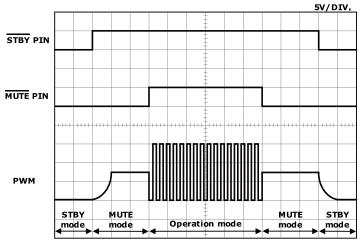

#### **Operation Mode Summary**

#### STBY mode (STBY = L and $\overline{MUTE}$ = L)

Each bias becomes off state when the regulator in IC has been turned off. The most of circuits becomes off state. The supply current :  $1\mu A$  (typical).

#### MUTE mode ( $\overline{\text{STBY}}$ = H and $\overline{\text{MUTE}}$ = L)

Each bias becomes on state when the regulator in IC has been turned on. When more than half of the circuits are active, the amplifier in the output stages become off. The supply current : 20mA (typical).

Operation mode ( $\overline{STBY}$  = H and  $\overline{MUTE}$  = H) The LV49152V operates as D-class amplifier.

The output signal is synchronized with the input signal.

The supply current : 45mA (typical)

Function image

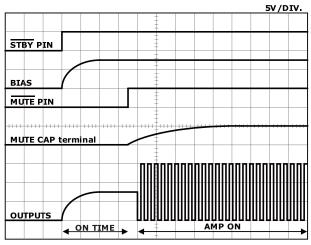

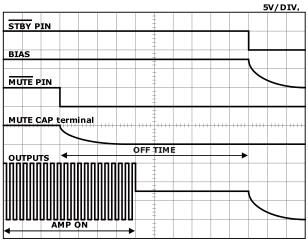

#### ON TIME/OFF TIME

#### ON TIME

Please secure ON TIME of 350msec or more for reducing Pop noise.

Function image

ON TIME ••• the time until the  $\overline{\text{MUTE}}$  pin is set to high level after the  $\overline{\text{STBY}}$  pin is set to high level

#### OFF TIME

Please secure OFF TIME of 1000msec or more for reducing Pop noise.

Function image

OFF TIME ••• the time until the  $\overline{\text{STBY}}$  pin is set to low level after the  $\overline{\text{MUTE}}$  pin is set to low level

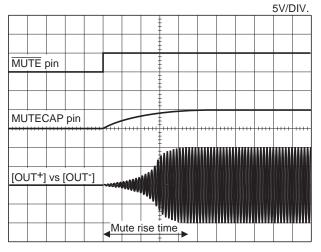

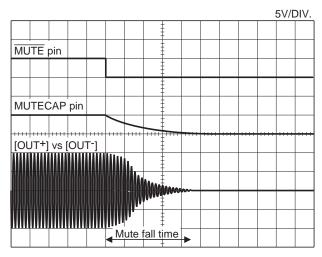

### SOFT MUTE

The soft mute circuit is able to use fade in/fade out function, and can set Rise time and fall time by the time constant of the MUTECAP capacitor.

### FADE IN

Mute rise time is Applpx.450msec in our recommended external components.

Function image

#### FADE OUT

Mute fall time is Applpx.450msec in our recommended external components.

Function image

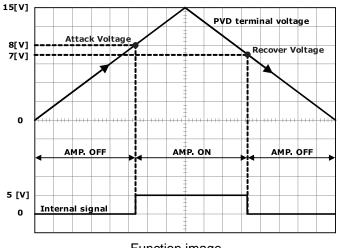

#### Power supply lowering protection circuit

Since the instable operation in the low voltage is prevented by using this circuit, after the voltage of the PVD pin is monitored and the voltage below the Attack voltage (PVD = 8V typ.), AMP is turned off.

Also, to prevent the instable operation when the voltage of the PVD pin is decreased by any cause during operations, the Attack voltage (PVD = 7V typ.) is set.

The voltage of Attack and Recover has hysteresis (About 1V) to prevent ON/OFF continuous action of the power supply lowering protection circuit.

Function image

Also, this IC is designed to turn off AMP in the same sequence that the MUTE is on as a pop noise measures when the plug of products are put off.

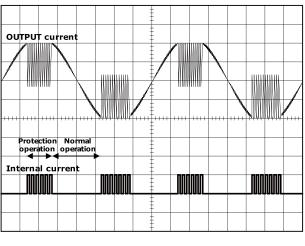

#### Over current protection circuit

The over current protection circuit is a protection circuit \* to protect the output DMOS from the over current and corresponds to any mode of the power supply, GND and a load short.

The protection operation is performed when the current reaches the detection current value set out in IC and the output DMOS is compulsorily turned off for about 20µsec.

After compulsorily tuning off the output DMOS, when the Amplifier is automatically reset in usual operation and the over current flows continuously, the protection operation is performed again.

Function image

\* The over current protection circuit is a function to avoid the abnormal state like the output short-circuit temporarily. Unfortunately, we cannot guarantee that IC is not destroyed.

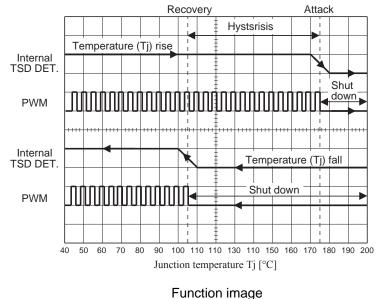

#### Thermal protection circuit

The LV49152V includes a thermal protection circuit to prevent damage to or destruction of the IC should abnormal internal heat generation occur.

This means that should the IC junction temperature (Tj) rise above about  $175^{\circ}$ C due to inadequate heat dissipation or other reason, the thermal protection circuit will operate to stop IC operation should the temperature rise further. If the temperature is reduced by lowering the input level or other means, the thermal protection circuit will recover automatically (about  $105^{\circ}$ C).

\* The thermal protection circuit is a function to avoid the abnormal state temporarily. Unfortunately, we cannot guarantee that IC is not destroyed.

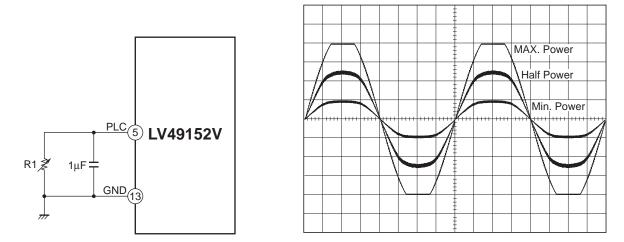

## PLC

The PLC (power level control) function is able to control the maximum index modulation by setting a value of external PLC resistance R1 voluntarily, and prevent a PWM signal from becoming the over modulation mode. In addition, this circuit can be use as output power limit circuit because the PLC function can set the maximum index modulation voluntarily, and variable from 2W to 15W with output power linearly in the state that made the power supply voltage and load resistance fixation. Because the PLC function can set the suitable rated output with the same power supply voltage/speaker regardless of screen size in flat screen televisions by this, set can plan the commonization of the board.

Furthermore, The PLC function can reduce abnormal noise in the hard clip so that output wave pattern becomes the soft clip when it limited output power.

#### Function image

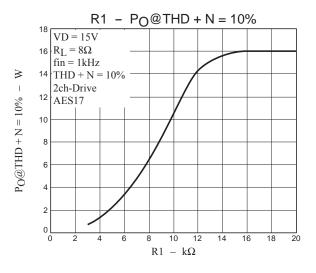

# Measuring condition VD = 15V, $R_L = 8\Omega$ , $L = 33\mu$ H (TOKO : A7502BY-330M), C = 0.1uF, $C_L = 0.47\mu$ F, $Ta = 25^{\circ}C$

| R1 [kΩ] | Po@10% [W] |

|---------|------------|

| 3.0     | 0.694      |

| 3.6     | 1.073      |

| 4.7     | 1.982      |

| 6.2     | 3.642      |

| 7.5     | 5.562      |

| 8.2     | 6.855      |

| 9.1     | 8.591      |

| 10      | 10.64      |

| 13      | 15.32      |

| 15      | 15.94      |

| 20      | 16.01      |

#### Setting example of the output power limit value

- \* When it is used this function as output power limit, please use the high-precision resistance such as the metal film resistor when precision of the electricity value is necessary.

- \* The value of external PLC resistance R1 please connects more than  $3k\Omega$ .

- \* When it is changed a value of external PLC resistance R1, please turn off an amplifier.

## Cut-off frequency calculation method and the output LC filter setting

The cut off frequency fc of the output LC filter is calculated by the following formula.

$$fc = \frac{1}{2\pi\sqrt{2LCL}}$$

Also, by setting the cut off frequency fc, the value of  $C_L$  and L is calculated by using the following formula.

$$C_{L} = \frac{1}{2\sqrt{2} \times \pi R_{L} fc}$$

$$L = \frac{\sqrt{2} \times R_{L}}{4\pi fc}$$

In general, the value from 20% to 30% of  $C_{\mbox{\scriptsize L}}$  is set to C.

In case of fc = 30kHz

| R <sub>L</sub> [Ω] | L [µH] | C <sub>L</sub> [μF] | C [μF] | Q     |

|--------------------|--------|---------------------|--------|-------|

| 4                  | 15     | 1                   | 0.22   | 0.650 |

| 6                  | 22     | 0.68                | 0.15   | 0.636 |

| 8                  | 33     | 0.47                | 0.1    | 0.704 |

| 16                 | 68     | 0.22                | 0.047  | 0.739 |

Above formula is common calculation method and is a measure of constant setting. In fact, it is necessary to set with each set that considers the speaker characteristics.

In addition, please set the fixed number to become  $Q \le 1$  in currents in the fc neighborhood increasing if Q value of the LC filter is big.

100

100

100

100

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typical" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affimative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.