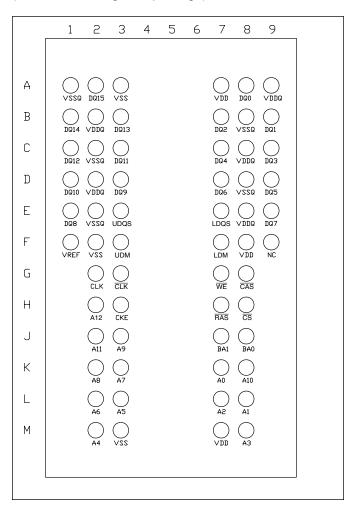

#### PIN CONFIGURATION

## Package Code B: 60-ball TF-BGA (top view)

(8mm x 13mm Body, 0.8mm x 1.0mm Ball Pitch)

#### **Top View**

(Balls seen through the package)

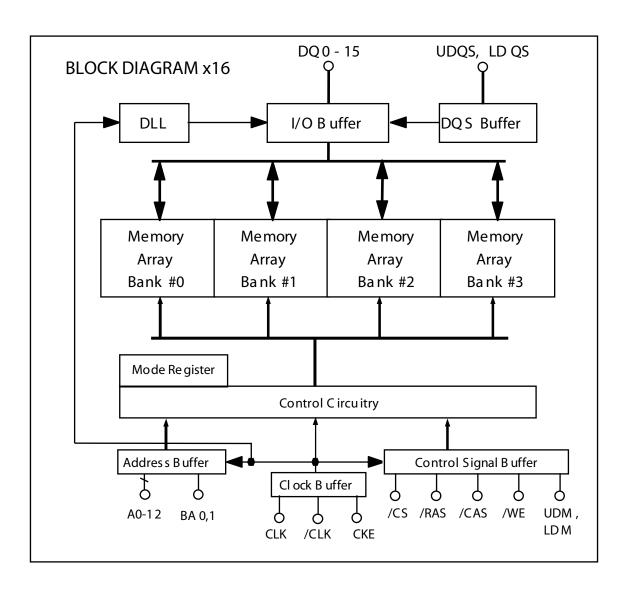

## PIN DESCRIPTION: for x16

| A0-A12          | Row Address Input                |

|-----------------|----------------------------------|

| A0-A8           | Column Address Input             |

| BA0, BA1        | Bank Select Address              |

| DQ0 - DQ15      | Data I/O                         |

| CLK, <b>CLK</b> | System Clock Input               |

| CKE             | Clock Enable                     |

| <u>cs</u>       | Chip Select                      |

| CAS             | Column Address Strobe<br>Command |

| RAS             | Row Address Strobe Command       |

| WE         | Write Enable              |

|------------|---------------------------|

| LDM, UDM   | Data Write Mask           |

| LDQS, UDQS | Data Strobe               |

| VDD        | Power                     |

| VDDQ       | Power Supply for I/O Pins |

| VSS        | Ground                    |

| VSSQ       | Ground for I/O Pins       |

| VREF       | SSTL_2 reference voltage  |

| NC         | No Connection             |

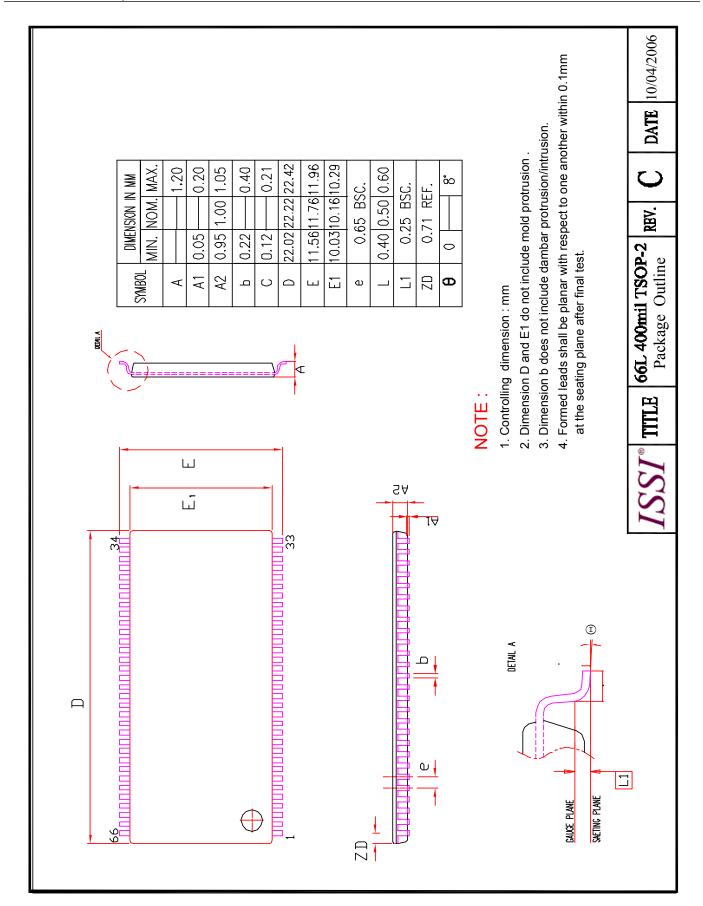

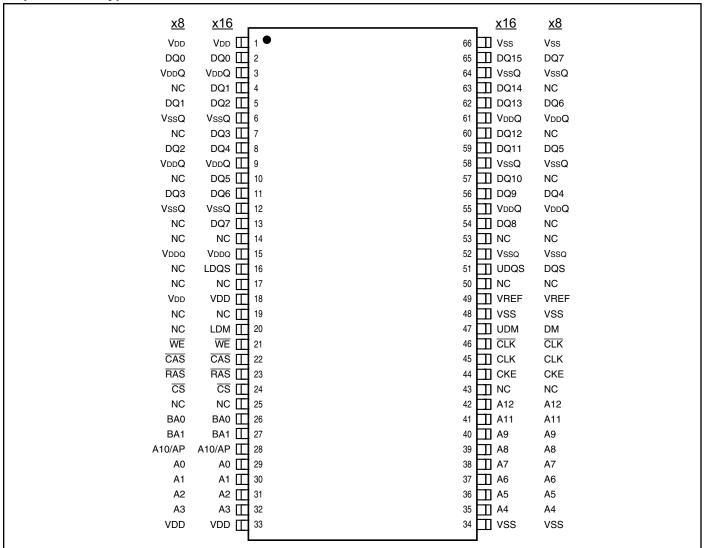

## PIN CONFIGURATIONS 66 pin TSOP - Type II for x8, x16

#### **PIN DESCRIPTION:**

| A0-A12                             | Row Address Input                |

|------------------------------------|----------------------------------|

| A0-A8 (x16)<br>A0-A9 (x8)          | Column Address Input             |

| BA0, BA1                           | Bank Select Address              |

| DQ0 – DQ15 (x16)<br>DQ0 – DQ7 (x8) | Data I/O                         |

| CLK, CLK                           | System Clock Input               |

| CKE                                | Clock Enable                     |

| CS                                 | Chip Select                      |

| CAS                                | Column Address Strobe<br>Command |

| RAS                                | Row Address Strobe<br>Command    |

| WE                           | Write Enable              |

|------------------------------|---------------------------|

| LDM, UDM (x16)<br>DM (x8)    | Data Write Mask           |

| LDQS, UDQS (x16)<br>DQS (x8) | Data Strobe               |

| VDD                          | Power                     |

| VDDQ                         | Power Supply for I/O Pins |

| VSS                          | Ground                    |

| VSSQ                         | Ground for I/O Pins       |

| VREF                         | SSTL_2 reference voltage  |

| NC                           | No Connection             |

# **PIN FUNCTION**

| SYMBOL                       | ТҮРЕ           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

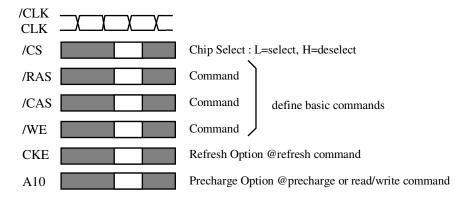

| CLK, /CLK                    | Input          | Clock: CLK and /CLK are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CLK and negative edge of /CLK. Output (read) data is referenced to the crossings of CLK and /CLK (both directions of crossing).                                                                                                 |  |  |  |  |  |

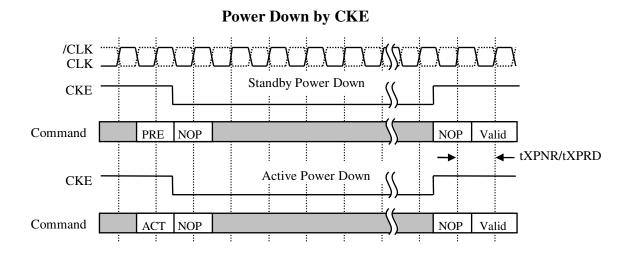

| CKE                          | Input          | Clock Enable: CKE controls internal clock. When CKE is low, internal clock for the following cycle is ceased. CKE is also used to select auto / self refresh. After self refresh mode is started, CKE becomes asynchronous input. Self refresh is maintained as long as CKE is low.                                                                                          |  |  |  |  |  |

| /CS                          | Input          | Chip Select: When /CS is high, any command means No Operation.                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| /RAS, /CAS, /WE              | Input          | Combination of /RAS, /CAS, /WE defines basic commands.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| A0-12                        | Input          | A0-12 specify the Row / Column Address in conjunction with BA0,1. The Row Address is specified by A0-12. The Column Address is specified by A0-9(x8) and A0-8(x16). A10 is also used to indicate precharge option. When A10 is high at a read / write command, an auto precharge is performed. When A10 is high at a precharge command, all banks are precharged.            |  |  |  |  |  |

| BA0,1                        | Input          | Bank Address: BA0,1 specifies one of four banks to which a command is applied. BA0,1 must be set with ACT, PRE, READ, WRITE commands.                                                                                                                                                                                                                                        |  |  |  |  |  |

| DQ0-7 (x8),<br>DQ0-15 (x16), | Input / Output | Data Input/Output: Data bus                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| DQS (x8)<br>UDQS, LDQS (x16) | Input / Output | Data Strobe: Output with read data, input with write data. Edge-aligned with read data, centered in write data. Used to capture write data. For the x16, LDQS corresponds to the data on DQ0-DQ7; UDQS correspond to the data on DQ8-DQ15                                                                                                                                    |  |  |  |  |  |

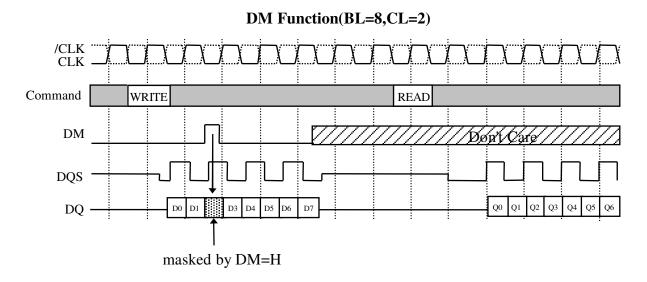

| DM (x8)<br>UDM, LDM (x16)    | Input          | Input Data Mask: DM is an input mask signal for write data. Input data is masked when DM is sampled HIGH along with that input data during a WRITE access. DM is sampled on both edges of DQS. Although DM pins are input only, the DM loading matches the DQ and DQS loading. For the x16, LDM corresponds to the data on DQ0-DQ7; UDM corresponds to the data on DQ8-DQ15. |  |  |  |  |  |

| Vdd, Vss                     | Power Supply   | Power Supply for the memory array and peripheral circuitry.                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Vddq, Vssq                   | Power Supply   | VDDQ, and VSSQ are supplied to the Output Buffers only.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Vref                         | Input          | SSTL_2 reference voltage.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

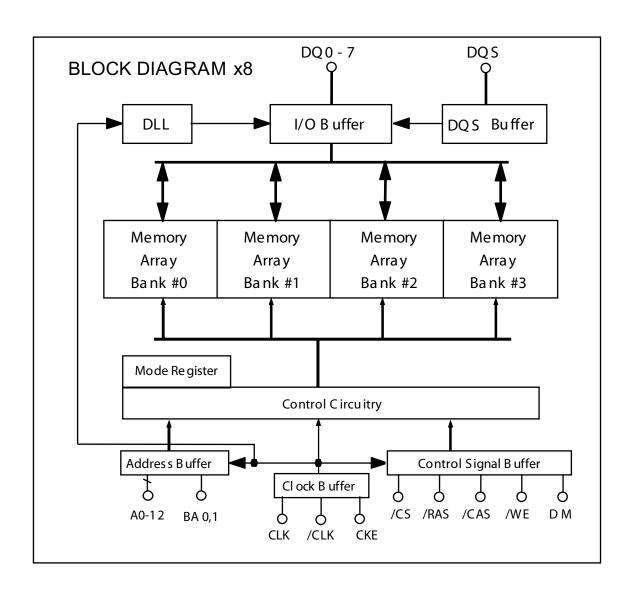

#### **BASIC FUNCTIONS**

ISSI's 256-Mbit DDR SDRAM provides basic functions, bank (row) activate, burst read / write, bank (row) precharge, and auto / self refresh. Each command is defined by control signals of /RAS, /CAS and /WE at CLK rising edge. In addition to 3 signals, /CS, CKE and A10 are used as chip select, refresh option, and precharge option, respectively. To know the detailed definition of commands, please see the command truth table.

### Activate (ACT) [/RAS =L, /CAS =/WE =H]

ACT command activates a row in an idle bank indicated by BA.

## Read (READ) [/RAS =H, /CAS =L, /WE =H]

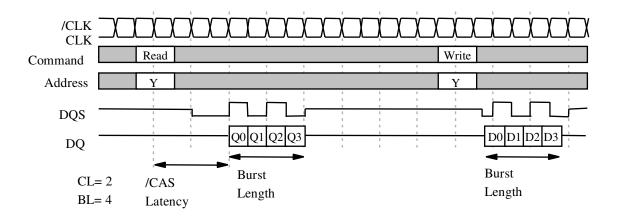

READ command starts burst read from the active bank indicated by BA. First output data appears after /CAS latency. When A10 =H at this command, the bank is deactivated after the burst read (autoprecharge, **READA**)

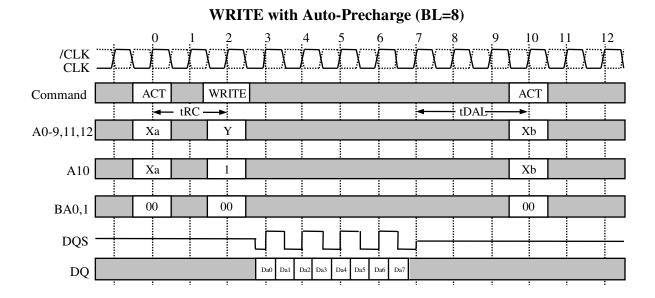

#### Write (WRITE) [/RAS =H, /CAS =/WE =L]

WRITE command starts burst write to the active bank indicated by BA. Total data length to be written is set by burst length. When A10 =H at this command, the bank is deactivated after the burst write (auto-precharge, WRITEA)

#### Precharge (PRE) [/RAS =L, /CAS =H, /WE =L]

PRE command deactivates the active bank indicated by BA. This command also terminates burst read /write operation. When A10 =H at this command, all banks are deactivated (precharge all, **PREA**).

#### Auto-Refresh (REFA) [/RAS =/CAS =L, /WE =CKE =H]

REFA command starts auto-refresh cycle. Refresh address including bank address are generated internally. After this command, the banks are precharged automatically.

# **COMMAND TRUTH TABLE**

| COMMAND                                                | MNEMONIC | CKE<br>n-1 | CKE<br>n | /CS | /RAS | /CAS | /WE | BA0,1 | A10<br>/AP | A0-9,<br>11-12 | note |

|--------------------------------------------------------|----------|------------|----------|-----|------|------|-----|-------|------------|----------------|------|

| Deselect                                               | DESEL    | Н          | X        | Н   | X    | X    | X   | X     | X          | X              |      |

| No Operation                                           | NOP      | Н          | X        | L   | Н    | Н    | Н   | X     | X          | X              |      |

| Row Address Entry &<br>Bank Activate                   | ACT      | Н          | Н        | L   | L    | Н    | Н   | V     | V          | V              |      |

| Single Bank Precharge                                  | PRE      | Н          | Н        | L   | L    | Н    | L   | V     | L          | X              |      |

| Precharge All Banks                                    | PREA     | Н          | Н        | L   | L    | Н    | L   | X     | Н          | X              |      |

| Column Address Entry & Write                           | WRITE    | Н          | Н        | L   | Н    | L    | L   | V     | L          | V              |      |

| Column Address Entry<br>& Write with<br>Auto-Precharge | WRITEA   | Н          | Н        | L   | Н    | L    | L   | V     | Н          | V              |      |

| Column Address Entry<br>& Read                         | READ     | Н          | Н        | L   | Н    | L    | Н   | V     | L          | V              |      |

| Column Address Entry<br>& Read with<br>Auto-Precharge  | READA    | Н          | Н        | L   | Н    | L    | Н   | V     | Н          | V              |      |

| Auto-Refresh                                           | REFA     | Н          | Н        | L   | L    | L    | Н   | X     | X          | X              |      |

| Self-Refresh Entry                                     | REFS     | Н          | L        | L   | L    | L    | Н   | X     | X          | X              |      |

| Self-Refresh Exit                                      | REFSX    | L          | Н        | Н   | X    | X    | X   | X     | X          | X              |      |

| Sen-Kenesh Exit                                        | KEFSA    | L          | Н        | L   | Н    | Н    | Н   | X     | X          | X              |      |

| Burst Terminate                                        | TERM     | Н          | Н        | L   | Н    | Н    | L   | X     | X          | X              | 1    |

| Mode Register Set                                      | MRS      | Н          | Н        | L   | L    | L    | L   | L     | L          | V              | 2    |

H=High Level, L=Low Level, V=Valid, X=Don't Care, n=CLK cycle number

#### NOTE:

- 1. Applies only to read bursts with autoprecharge disabled; this command is undefined (and should not be used) for read bursts with autoprecharge enabled, and for write bursts.

- 2. BA0-BA1 select either the Base or the Extended Mode Register (BA0 = 0, BA1 = 0 selects Mode Register; BA0=1, BA1 = 0 selects Extended Mode Register; other combinations of BA0-BA1 are reserved; A0-A12 provide the op-code to be written to the selected Mode Register.

# **FUNCTION TRUTH TABLE**

| Current State | /CS     | /RAS  | /CAS                  | /WE  | Address               | Command        | Action                                                                     | Notes |

|---------------|---------|-------|-----------------------|------|-----------------------|----------------|----------------------------------------------------------------------------|-------|

| IDLE          | Н       | X     | X                     | X    | X                     | DESEL          | NOP                                                                        |       |

|               | L       | Н     | Н                     | Н    | X                     | NOP            | NOP                                                                        |       |

|               | L       | Н     | Н                     | L    | BA                    | TERM           | ILLEGAL                                                                    | 2     |

|               | L       | Н     | L                     | X    | BA, CA, A10           | READ / WRITE   | ILLEGAL                                                                    | 2     |

|               | L       | L     | Н                     | Н    | BA, RA                | ACT            | Bank Active, Latch RA                                                      |       |

|               | L       | L     | Н                     | L    | BA, A10               | PRE / PREA     | NOP                                                                        | 4     |

|               | L L L H |       | X                     | REFA | Auto-Refresh          | 5              |                                                                            |       |

|               | L       | L     | L                     | L    | Op-Code, Mode-<br>Add | MRS            | Mode Register Set                                                          | 5     |

| ROW ACTIVE    | Н       | X     | X                     | X    | X                     | DESEL          | NOP                                                                        |       |

|               | L       | Н     | Н                     | Н    | X                     | NOP            | NOP                                                                        |       |

|               | L H H L |       |                       |      | BA                    | TERM           | ILLEGAL                                                                    |       |

|               | L       | H L H |                       |      | BA, CA, A10           | READ / READA   | Begin Read, Latch CA, Determine Auto-Precharge                             |       |

|               | L       | Н     | L                     | L    | BA, CA, A10           | WRITE / WRITEA | Begin Write, Latch CA, Determine Auto-Precharge                            |       |

|               | L       | L     | Н                     | Н    | BA, RA                | ACT            | Bank Active / ILLEGAL                                                      | 2     |

|               | L       | L     | Н                     | L    | BA, A10               | PRE / PREA     | Precharge / Precharge All                                                  |       |

|               | L       | L     | L                     | Н    | X                     | REFA           | ILLEGAL                                                                    |       |

|               | L       | L     | L                     | L    | Op-Code, Mode-<br>Add | MRS            | ILLEGAL                                                                    |       |

| READ(Auto-    | Н       | X     | X                     | X    | X                     | DESEL          | NOP (Continue Burst to END)                                                |       |

| Precharge     | L       | Н     | Н                     | Н    | X                     | NOP            | NOP (Continue Burst to END)                                                |       |

| Disabled)     | L       | Н     | Н                     | L    | BA                    | TERM           | Terminate Burst                                                            |       |

|               | L       | Н     | L                     | Н    | BA, CA, A10           | READ / READA   | Terminate Burst, Latch CA, Begin<br>New Read, Determine Auto-<br>Precharge | 3     |

|               | L       | Н     | L                     | L    | BA, CA, A10           | WRITE / WRITEA | ILLEGAL                                                                    |       |

|               | L       | L     | Н                     | Н    | BA, RA                | ACT            | Bank Active / ILLEGAL                                                      | 2     |

|               | L       | L     | Н                     | L    | BA, A10               | PRE / PREA     | Terminate Burst, Precharge                                                 |       |

|               | L       | L     | L                     | Н    | X                     | REFA           | ILLEGAL                                                                    |       |

|               |         |       | Op-Code, Mode-<br>Add | MRS  | ILLEGAL               |                |                                                                            |       |

# **FUNCTION TRUTH TABLE (continued)**

| Current State            | /CS | /RAS | /CAS | /WE | Address               | Command        | Action                                                           | Notes |

|--------------------------|-----|------|------|-----|-----------------------|----------------|------------------------------------------------------------------|-------|

| WRITE(Auto-              | Н   | X    | X    | X   | X                     | DESEL          | NOP (Continue Burst to END)                                      |       |

| Precharge                | L   | Н    | Н    | Н   | X                     | NOP            | NOP (Continue Burst to END)                                      |       |

| Disabled)                | L   | Н    | Н    | L   | BA                    | TERM           | ILLEGAL                                                          |       |

|                          | L   | Н    | L    | Н   | BA, CA, A10           | READ / READA   | Terminate Burst, Latch CA, Begin Read, Determine Auto-Precharge  | 3     |

|                          | L   | Н    | L    | L   | BA, CA, A10           | WRITE / WRITEA | Terminate Burst, Latch CA, Begin Write, Determine Auto-Precharge | 3     |

|                          | L   | L    | Н    | Н   | BA, RA                | ACT            | Bank Active / ILLEGAL                                            | 2     |

|                          | L   | L    | Н    | L   | BA, A10               | PRE / PREA     | Terminate Burst, Precharge                                       |       |

|                          | L   | L    | L    | Н   | ILLEGAL               |                |                                                                  |       |

|                          | L   | L    | L    | L   | ILLEGAL               |                |                                                                  |       |

| DEAD 31                  | Н   | X    | X    | X   | X                     | DESEL          | NOP (Continue Burst to END)                                      |       |

| READ with Auto-Precharge | L   | Н    | Н    | Н   | X                     | NOP            | NOP (Continue Burst to END)                                      |       |

| Auto-Frecharge           | L   | Н    | Н    | L   | BA                    | TERM           | ILLEGAL                                                          |       |

|                          | L   | Н    | L    | Н   | BA, CA, A10           | READ / READA   | ILLEGAL                                                          |       |

|                          | L   | Н    | L    | L   | BA, CA, A10           | WRITE / WRITEA | ILLEGAL                                                          |       |

|                          | L   | L    | Н    | Н   | BA, RA                | ACT            | Bank Active / ILLEGAL                                            | 2     |

|                          | L   | L    | Н    | L   | BA, A10               | PRE / PREA     | Precharge / ILLEGAL                                              | 2     |

|                          | L   | L    | L    | Н   | X                     | REFA           | ILLEGAL                                                          |       |

|                          | L   | L    | L    | L   | Op-Code, Mode-<br>Add | MRS            | ILLEGAL                                                          |       |

| WRITE with               | Н   | X    | X    | X   | X                     | DESEL          | NOP (Continue Burst to END)                                      |       |

| Auto-Precharge           | L   | Н    | Н    | Н   | X                     | NOP            | NOP (Continue Burst to END)                                      |       |

| Auto-1 recharge          | L   | Н    | Н    | L   | BA                    | TERM           | ILLEGAL                                                          |       |

|                          | L   | Н    | L    | Н   | BA, CA, A10           | READ / READA   | ILLEGAL                                                          |       |

|                          | L   | Н    | L    | L   | BA, CA, A10           | WRITE / WRITEA | ILLEGAL                                                          |       |

|                          | L   | L    | Н    | Н   | BA, RA                | ACT            | Bank Active / ILLEGAL                                            | 2     |

|                          | L   | L    | Н    | L   | BA, A10               | PRE / PREA     | Precharge / ILLEGAL                                              | 2     |

|                          | L   | L    | L    | Н   | X                     | REFA           | ILLEGAL                                                          |       |

|                          | L   | L    | L    | L   | Op-Code, Mode-<br>Add | MRS            | ILLEGAL                                                          |       |

# **FUNCTION TRUTH TABLE (continued)**

| Current State         | /CS | /RAS | /CAS | /WE | Address               | Command      | Action                      | Notes |

|-----------------------|-----|------|------|-----|-----------------------|--------------|-----------------------------|-------|

| PRE-                  | Н   | X    | X    | X   | X                     | DESEL        | NOP (Idle after tRP)        |       |

| CHARGING              | L   | Н    | Н    | Н   | X                     | NOP          | NOP (Idle after tRP)        |       |

|                       | L   | Н    | Н    | L   | BA                    | TERM         | ILLEGAL                     | 2     |

|                       | L   | Н    | L    | X   | BA, CA, A10           | READ / WRITE | ILLEGAL                     | 2     |

|                       | L   | L    | Н    | Н   | BA, RA                | ACT          | ILLEGAL                     | 2     |

|                       | L   | L    | Н    | L   | BA, A10               | PRE / PREA   | NOP (Idle after tRP)        | 4     |

|                       | L   | L    | L    | Н   | X                     | REFA         | ILLEGAL                     |       |

|                       | L   | L    | L    | L   | Op-Code, Mode-<br>Add | MRS          | ILLEGAL                     |       |

| DOW                   | Н   | X    | X    | X   | X                     | DESEL        | NOP (Row Active after tRCD) |       |

| ROW<br>ACTIVATING     | L   | Н    | Н    | Н   | X                     | NOP          | NOP (Row Active after tRCD) |       |

| ACIIVAIINO            | L   | Н    | Н    | L   | BA                    | TERM         | ILLEGAL                     | 2     |

|                       | L   | Н    | L    | X   | BA, CA, A10           | READ / WRITE | ILLEGAL                     | 2     |

|                       | L   | L    | Н    | Н   | BA, RA                | ACT          | ILLEGAL                     | 2     |

|                       | L   | L    | Н    | L   | BA, A10               | PRE / PREA   | ILLEGAL                     | 2     |

|                       | L   | L    | L    | Н   | X                     | REFA         | ILLEGAL                     |       |

|                       | L   | L    | L    | L   | Op-Code, Mode-<br>Add | MRS          | ILLEGAL                     |       |

| WIDITE DE             | Н   | X    | X    | X   | X                     | DESEL        | NOP                         |       |

| WRITE RE-<br>COVERING | L   | Н    | Н    | Н   | X                     | NOP          | NOP                         |       |

| COVERNING             | L   | Н    | Н    | L   | BA                    | TERM         | ILLEGAL                     | 2     |

|                       | L   | Н    | L    | X   | BA, CA, A10           | READ / WRITE | ILLEGAL                     | 2     |

|                       | L   | L    | Н    | Н   | BA, RA                | ACT          | ILLEGAL                     | 2     |

|                       | L   | L    | Н    | L   | BA, A10               | PRE / PREA   | ILLEGAL                     | 2     |

|                       | L   | L    | L    | Н   | X                     | REFA         | ILLEGAL                     |       |

|                       | L   | L    | L    | L   | Op-Code, Mode-<br>Add | MRS          | ILLEGAL                     |       |

# **FUNCTION TRUTH TABLE (continued)**

| Current State | /CS | /RAS | /CAS             | /WE | Address               | Command      | Action                      | Notes |

|---------------|-----|------|------------------|-----|-----------------------|--------------|-----------------------------|-------|

| REFRESHING    | Н   | X    | X                | X   | X                     | DESEL        | NOP (Idle after tRC)        |       |

|               | L   | Н    | Н                | Н   | X                     | NOP          | NOP (Idle after tRC)        |       |

|               | L   | Н    | Н                | L   | BA                    | TERM         | ILLEGAL                     |       |

|               | L   | Н    | L                | X   | BA, CA, A10           | READ / WRITE | ILLEGAL                     |       |

|               | L   | L    | L H H BA, RA ACT |     | ACT                   | ILLEGAL      |                             |       |

|               | L   | L    | Н                | L   | BA, A10               | PRE/PREA     | ILLEGAL                     |       |

|               | L   | L    | L                | Н   | X                     | REFA         | ILLEGAL                     |       |

|               | L   | L    | L                | L   | Op-Code, Mode-Add     | MRS          | ILLEGAL                     |       |

| MODE          | Н   | X    | X                | X   | X                     | DESEL        | NOP (Row Active after tRSC) |       |

| REGISTER      | L   | Н    | Н                | Н   | X                     | NOP          | NOP (Row Active after tRSC) |       |

| SETTING       | L   | Н    | Н                | L   | BA                    | TERM         | ILLEGAL                     |       |

|               | L   | Н    | L                | X   | BA, CA, A10           | READ / WRITE | ILLEGAL                     |       |

|               | L   | L    | Н                | Н   | BA, RA                | ACT          | ILLEGAL                     |       |

|               | L   | L    | Н                | L   | BA, A10               | PRE / PREA   | ILLEGAL                     |       |

|               | L   | L    | L                | Н   | X                     | REFA         | ILLEGAL                     |       |

|               | L   | L    | L                | L   | Op-Code, Mode-<br>Add | MRS          | ILLEGAL                     |       |

#### ABBREVIATIONS:

H=High Level, L=Low Level, X=Don't Care

BA=Bank Address, RA=Row Address, CA=Column Address, NOP=No Operation

#### NOTES:

- 1. All entries assume that CKE was High during the preceding clock cycle and the current clock cycle.

- 2. ILLEGAL to bank in specified state; function may be legal in the bank indicated by BA, depending on the state of that bank.

- 3. Must satisfy bus contention, bus turn around, write recovery requirements.

- 4. NOP to bank precharging or in idle state. May precharge bank indicated by BA.

- 5. ILLEGAL if any bank is not idle.

ILLEGAL = Device operation and/or data-integrity are not guaranteed.

## **FUNCTION TRUTH TABLE for CKE**

| Current State     | CKE n-1 | CKE n | /CS | /RAS | /CAS | /WE | Address | Action                             | Notes |

|-------------------|---------|-------|-----|------|------|-----|---------|------------------------------------|-------|

| SELF-             | Н       | X     | X   | X    | X    | X   | X       | INVALID                            | 1     |

| REFRESHING        | L       | Н     | Н   | X    | X    | X   | X       | Exit Self-Refresh (Idle after tRC) | 1     |

|                   | L       | Н     | L   | Н    | Н    | Н   | X       | Exit Self-Refresh (Idle after tRC) | 1     |

|                   | L       | Н     | L   | Н    | Н    | L   | X       | ILLEGAL                            | 1     |

|                   | L       | Н     | L   | Н    | L    | X   | X       | ILLEGAL                            | 1     |

|                   | L       | Н     | L   | L    | X    | X   | X       | ILLEGAL                            | 1     |

|                   | L       | L     | X   | X    | X    | X   | X       | NOP (Maintain Self-Refresh)        | 1     |

| POWER             | Н       | X     | X   | X    | X    | X   | X       | INVALID                            |       |

| DOWN              | L       | Н     | X   | X    | X    | X   | X       | Exit Power Down to Idle            |       |

|                   | L       | L     | X   | X    | X    | X   | X       | NOP (Maintain Self-Refresh)        |       |

| ALL BANKS         | Н       | Н     | X   | X    | X    | X   | X       | Refer to Function Truth Table      | 2     |

| IDLE              | Н       | L     | L   | L    | L    | Н   | X       | Enter Self-Refresh                 | 2     |

|                   | Н       | L     | Н   | X    | X    | X   | X       | Enter Power Down                   | 2     |

|                   | Н       | L     | L   | Н    | Н    | Н   | X       | Enter Power Down                   | 2     |

|                   | Н       | L     | L   | Н    | Н    | L   | X       | ILLEGAL                            | 2     |

|                   | Н       | L     | L   | Н    | L    | X   | X       | ILLEGAL                            | 2     |

|                   | Н       | L     | L   | L    | X    | X   | X       | ILLEGAL                            | 2     |

|                   | L       | X     | X   | X    | X    | X   | X       | Refer to Current State =Power Down | 2     |

| ANY STATE         | Н       | Н     | X   | X    | X    | X   | X       | Refer to Function Truth Table      |       |

| other than listed | Н       | L     | X   | X    | X    | X   | X       | Begin CLK Suspend at Next Cycle    | 3     |

| above             | L       | Н     | X   | X    | X    | X   | X       | Exit CLK Suspend at Next Cycle     | 3     |

|                   | L       | L     | X   | X    | X    | X   | Х       | Maintain CLK Suspend               |       |

### ABBREVIATIONS:

H=High Level, L=Low Level, X=Don't Care

#### NOTES:

- 1. CKE Low to High transition will re-enable CLK and other inputs asynchronously. A minimum setup time must be satisfied before any command other than EXIT.

- 2. Power-Down and Self-Refresh can be entered only from the All Banks Idle State.

- 3. Must be legal command.

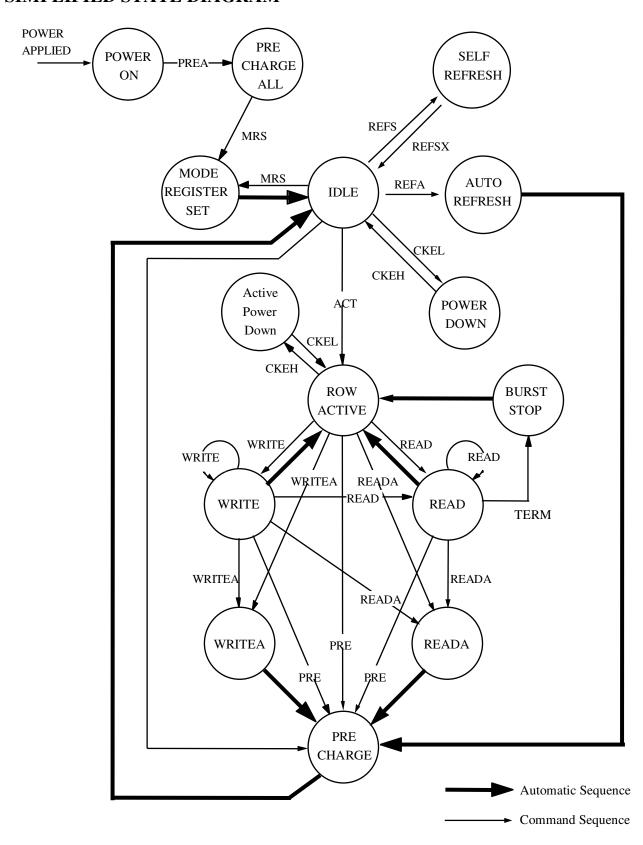

#### SIMPLIFIED STATE DIAGRAM

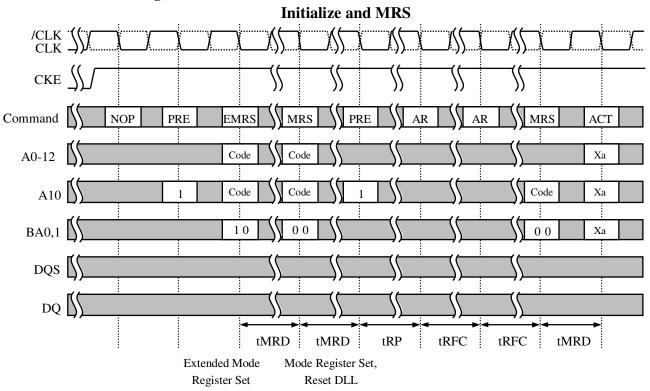

## **POWER ON SEQUENCE**

Before starting normal operation, the following power on sequence is necessary to prevent a SDRAM from damaged or multifunctioning.

- 1. Apply VDD before or the same time as VDDQ

- 2. Apply VDDQ before or at the same time as VTT & Vref

- 3. Maintain stable condition for 200us after stable power and CLK, apply NOP or DSEL

- 4. Issue precharge command for all banks of the device

- 5. Issue EMRS

- 6. Issue MRS for the Mode Register and to reset the DLL

- 7. Issue 2 or more Auto Refresh commands

- 8. Maintain stable condition for 200 cycle

After these sequence, the DDR SDRAM is idle state and ready for normal operation.

CLK

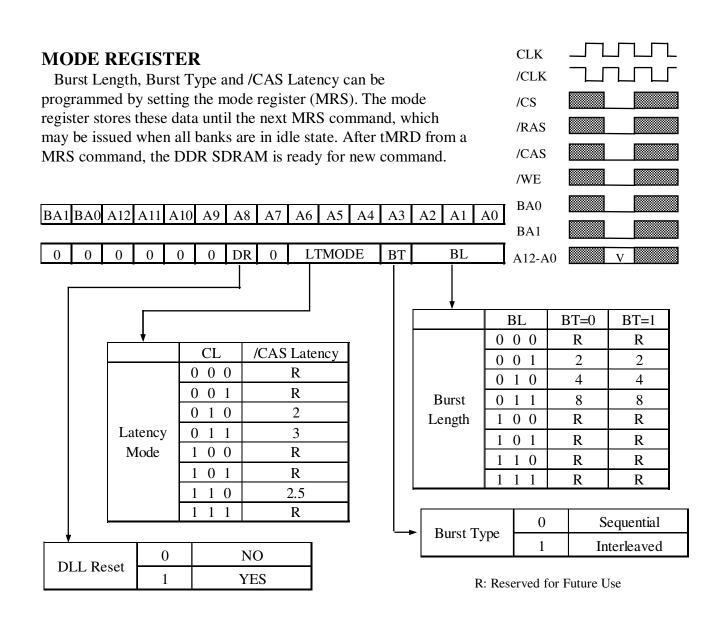

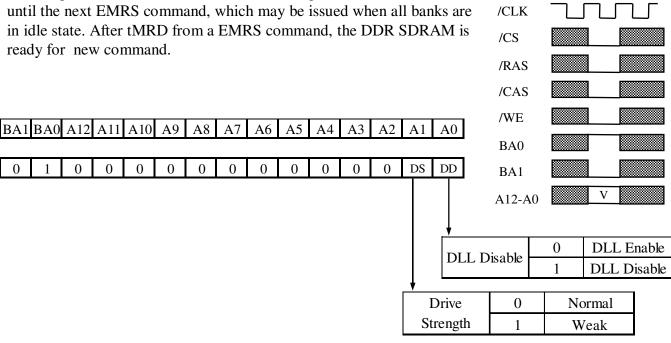

## EXTENDED MODE REGISTER

DLL disable / enable mode can be programmed by setting the extended mode register (EMRS). The extended mode register stores these data

| Initia | al Ado | lress | BL |   |            |   | Column Addressing |   |   |   |   |   |   |             |   |   |   |   |   |

|--------|--------|-------|----|---|------------|---|-------------------|---|---|---|---|---|---|-------------|---|---|---|---|---|

| A2     | A1     | A0    |    |   | Sequential |   |                   |   |   |   |   |   |   | Interleaved |   |   |   |   |   |

| 0      | 0      | 0     |    | 0 | 1          | 2 | 3                 | 4 | 5 | 6 | 7 | 0 | 1 | 2           | 3 | 4 | 5 | 6 | 7 |

| 0      | 0      | 1     |    | 1 | 2          | 3 | 4                 | 5 | 6 | 7 | 0 | 1 | 0 | 3           | 2 | 5 | 4 | 7 | 6 |

| 0      | 1      | 0     |    | 2 | 3          | 4 | 5                 | 6 | 7 | 0 | 1 | 2 | 3 | 0           | 1 | 6 | 7 | 4 | 5 |

| 0      | 1      | 1     | 0  | 3 | 4          | 5 | 6                 | 7 | 0 | 1 | 2 | 3 | 2 | 1           | 0 | 7 | 6 | 5 | 4 |

| 1      | 0      | 0     | 8  | 4 | 5          | 6 | 7                 | 0 | 1 | 2 | 3 | 4 | 5 | 6           | 7 | 0 | 1 | 2 | 3 |

| 1      | 0      | 1     |    | 5 | 6          | 7 | 0                 | 1 | 2 | 3 | 4 | 5 | 4 | 7           | 6 | 1 | 0 | 3 | 2 |

| 1      | 1      | 0     |    | 6 | 7          | 0 | 1                 | 2 | 3 | 4 | 5 | 6 | 7 | 4           | 5 | 2 | 3 | 0 | 1 |

| 1      | 1      | 1     |    | 7 | 0          | 1 | 2                 | 3 | 4 | 5 | 6 | 7 | 6 | 5           | 4 | 3 | 2 | 1 | 0 |

| -      | 0      | 0     |    | 0 | 1          | 2 | 3                 |   |   |   |   | 0 | 1 | 2           | 3 |   |   |   |   |

| -      | 0      | 1     | ,  | 1 | 2          | 3 | 0                 |   |   |   |   | 1 | 0 | 3           | 2 |   |   |   |   |

| -      | 1      | 0     | 4  | 2 | 3          | 0 | 1                 |   |   |   |   | 2 | 3 | 0           | 1 |   |   |   |   |

| -      | 1      | 1     |    | 3 | 0          | 1 | 2                 |   |   |   |   | 3 | 2 | 1           | 0 |   |   |   |   |

| -      | -      | 0     |    | 0 | 1          |   |                   |   |   |   |   | 0 | 1 |             |   |   |   |   |   |

| -      | -      | 1     | 2  | 1 | 0          |   |                   |   |   |   |   | 1 | 0 |             |   |   |   |   |   |

# **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                 | Conditions                                                           | Ratings                             | Unit |

|--------|---------------------------|----------------------------------------------------------------------|-------------------------------------|------|

| Vdd    | Supply Voltage            | with respect to Vss                                                  | -0.5 ~ 3.7                          | V    |

| VddQ   | Supply Voltage for Output | with respect to Vssq                                                 | -0.5 ~ 3.7                          | V    |

| VI     | Input Voltage             | with respect to Vss                                                  | -0.5 ~ VDD+0.5                      | V    |

| VO     | Output Voltage            | with respect to Vssq                                                 | -0.5 ~ VDDQ+0.5                     | V    |

| IO     | Output Current            |                                                                      | 50                                  | mA   |

| Pd     | Power Dissipation         | Ta = 25 °C                                                           | 1500                                | mW   |

| Topr   | Operating Temperature     | Commercial Temperature Industrial Temperature Automotive Temperature | 0 to 70<br>-40 to +85<br>-40 to +85 | °C   |

| Tstg   | Storage Temperature       |                                                                      | -65 ~ 150                           | °C   |

## DC OPERATING CONDITIONS

(Ta=0 ~  $70^{\circ}$ C for Commercial. Ta = -40 ~ +85°C for Industrial and Automotive)

| Cramb ol | Parameter                                                                                                                                                            |           | Limits   |           | Unit | Notes |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|-----------|------|-------|

| Symbol   | Parameter                                                                                                                                                            | Min.      | Typ.     | Max.      | Unit | Notes |

| Vdd      | Supply Voltage                                                                                                                                                       | 2.3       | 2.5      | 2.7       | V    |       |

| VddQ     | I/O Supply Voltage                                                                                                                                                   | 2.3       | 2.5      | 2.7       | V    |       |

| VREF     | I/O Reference Volatage                                                                                                                                               | 0.49*VddQ | 0.5*VddQ | 0.51*VddQ | V    |       |

| VTT      | I/O Termination Voltage                                                                                                                                              | VREF-0.04 | VREF     | VREF+0.04 | V    |       |

| VIH(DC)  | Input High Voltage                                                                                                                                                   | Vref+0.15 |          | Vdd+0.3   | V    |       |

| VIL(DC)  | Input Low Voltage                                                                                                                                                    | -0.3      |          | Vref-0.15 | V    |       |

| VIN(DC)  | Input Voltage Level, CK and /CK inputs                                                                                                                               | -0.3      |          | VddQ+0.3  | V    |       |

| VID(DC)  | Input Differential Voltage, CK and /CK inputs                                                                                                                        | 0.36      |          | VddQ+0.6  | V    |       |

| IL       | Input Leakage Current, Any input 0V <vin<vdd (all="" not="" other="" pins="" test="0V)&lt;/td" under=""><td>-2</td><td></td><td>2</td><td>uA</td><td></td></vin<vdd> | -2        |          | 2         | uA   |       |

| IOZ      | Output Leakage Current DQs are disabled; 0V <vout<vddq< td=""><td>-5</td><td></td><td>5</td><td>uA</td><td></td></vout<vddq<>                                        | -5        |          | 5         | uA   |       |

| IOH      | Output High Current (VOUT=1.95V)                                                                                                                                     | -16.2     |          |           | mA   |       |

| IOL      | Output Low Current (VOUT=0.35V)                                                                                                                                      | 16.2      |          |           | mA   |       |

## **AC OPERATING CONDITIONS**

(Ta=0 ~  $70^{\circ}$ C for Commercial. Ta = -40 ~ +85°C for Industrial and Automotive) (Vdd = VddQ = 2.5V  $\pm 0.2$ V, Vss = VssQ = 0V, unless otherwise noted)

| Symbol  | Parameter                                       |              | Limits   |              | Unit | Notes  |

|---------|-------------------------------------------------|--------------|----------|--------------|------|--------|

| Symbol  | r arameter                                      | Min.         | Тур.     | Max.         | Ont  | 110168 |

| VIH(AC) | Input High Voltage                              | Vref+0.31    |          |              | V    |        |

| VIL(AC) | Input Low Voltage                               |              |          | Vref-0.31    | V    |        |

| VID(AC) | Input Differential Voltage, CK and /CK inputs   | 0.7          |          | VddQ+0.6     | V    |        |

| VIX(AC) | Input Crossing Point Voltage, CK and /CK inputs | 0.5*VddQ-0.2 | 0.5*VddQ | 0.5*VddQ-0.2 | V    |        |

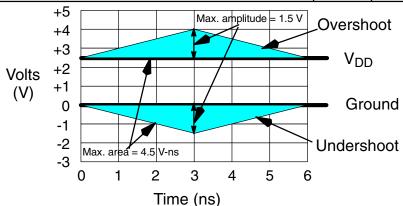

#### AC Overshoot/Undershoot Specification for Address and Control Pins

| Parameter                                                                | Max. | Unit |

|--------------------------------------------------------------------------|------|------|

| Peak amplitude allowed for overshoot                                     | 1.5  | ٧    |

| Peak amplitude allowed for undershoot                                    | 1.5  | V    |

| Area between the overshoot signal and VDD must be less than or equal to  | 4.5  | V-ns |

| Area between the undershoot signal and GND must be less than or equal to | 4.5  | V-ns |

**Address and Control AC Overshoot and Undershoot Definition**

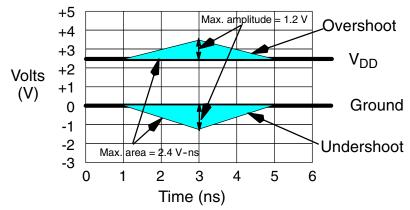

#### Overshoot/Undershoot Specification for Data, Strobe, and Mask Pins

| Parameter                                                                | Max | Unit |

|--------------------------------------------------------------------------|-----|------|

| Peak amplitude allowed for overshoot                                     | 1.2 | V    |

| Peak amplitude allowed for undershoot                                    | 1.2 | V    |

| Area between the overshoot signal and VDD must be less than or equal to  | 2.4 | V-ns |

| Area between the undershoot signal and GND must be less than or equal to | 2.4 | V-ns |

DQ/DM/DQS AC Overshoot and Undershoot Definition

# AVERAGE SUPPLY CURRENT from Vdd

$(Vdd = VddQ = 2.5V \pm 0.2V, Vss = VssQ = 0V, Output Open, unless otherwise noted)$

| G 1 1  | Parameter/Test Conditions                                                                                                                                                                                                                            | I   | _imits(Max | .)  | Unit | Notes |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|------|-------|

| Symbol | Parameter/Test Conditions                                                                                                                                                                                                                            | -5  | -6         | -75 | Unit | Notes |

| IDD1   | OPERATING CURRENT: One Bank; Active-Read-Precharge;Burst = 2; t<br>RC = t RC MIN; t CK = t CK MIN; IOUT= 0mA; Address and control<br>inputs changing once per clock cycle                                                                            | 185 | 165        | 150 |      |       |

| IDD2P  | PRECHARGE POWER-DOWN STANDBY CURRENT: All banks idle; power-down mode; CKE ≤VIL (MAX); t CK = t CK MIN                                                                                                                                               | 30  | 25         | 20  |      |       |

| IDD2N  | IDLE STANDBY CURRENT: /CS ≥ VIH (MIN); All banks idle; CKE ≥ VIH (MIN); t CK = t CK MIN; Address and other control inputs changing once per clock cycle                                                                                              | 60  | 55         | 50  |      |       |

| IDD3P  | ACTIVE POWER DOWN STANDBY CURRENT: One bank active; power down mode; CKE $\leq$ VIL(MAX); t CK = t CK MIN                                                                                                                                            | 50  | 45         | 40  |      |       |

| IDD3N  | ACTIVE STANDBY CURRENT: $/CS \ge VIH$ (MIN); CKE $\ge VIH$ (MIN); One bank; Active-Precharge; t RC = t RAS MAX; t CK = t CK MIN; DQ,DM and DQS inputs changing twice per clock cycle; address and other control inputs changing once per clock cycle | 95  | 90         | 75  | mA   |       |

| IDD4R  | OPERATING CURRENT: Burst =2; Read; Continuous burst; All banks active; Address and control inputs changing once per clock cycle; t CK = t CK MIN; IOUT = 0 mA                                                                                        | 290 | 250        | 210 |      |       |

| IDD4W  | OPERATING CURRENT: Burst =2; Write; Continuous burst; All banks active; Address and control inputs changing once per clock cycle; CK = t CK MIN; DQ and DQS inputs changing twice per clock cycle                                                    | 290 | 250        | 210 |      |       |

| IDD5   | AUTO REFRESH CURRENT: t RC = t RFC (MIN)                                                                                                                                                                                                             | 170 | 160        | 150 |      |       |

| IDD6   | SELF REFRESH CURRENT: CKE ≤ 0.2V                                                                                                                                                                                                                     | 5   | 5          | 5   |      |       |

# AC TIMING REQUIREMENTS

|        | AG GI                                                   |        | <u>-</u>                    | 5     | -                   | 6     | -7                  | 15    | ** * |       |

|--------|---------------------------------------------------------|--------|-----------------------------|-------|---------------------|-------|---------------------|-------|------|-------|

| Symbol | AC Characteristics Parameter                            |        | Min.                        | Max   | Min.                | Max   | Min.                | Max   | Unit | Notes |

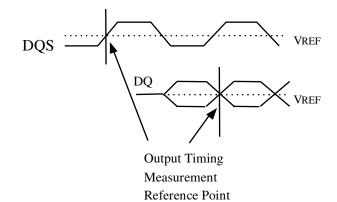

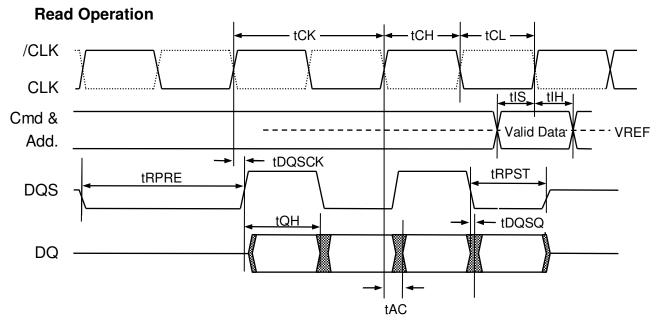

| tAC    | DQ Output access time from CLK//CLK                     |        | -0.70                       | +0.70 | -0.70               | +0.70 | -0.75               | +0.75 | ns   |       |

| tDQSCK | DQS Output access time from CLK//CLK                    |        | -0.6                        | +0.6  | -0.60               | +0.60 | -0.75               | +0.75 | ns   |       |

| tCH    | CLK High level width                                    |        | 0.45                        | 0.55  | 0.45                | 0.55  | 0.45                | 0.55  | tCK  |       |

| tCL    | CLK Low level width                                     |        | 0.45                        | 0.55  | 0.45                | 0.55  | 0.45                | 0.55  | tCK  |       |

|        |                                                         | CL=3.0 | 5                           | 7.5   | 6                   | 12    | 7.5                 | 12    | ns   |       |

| tCK    | CLK cycle time                                          | CL=2.5 | 5                           | 12    | 6                   | 12    | 7.5                 | 12    | ns   |       |

|        |                                                         | CL=2.0 | 7.5                         | 12    | 7.5                 | 12    | 7.5                 | 12    | ns   |       |

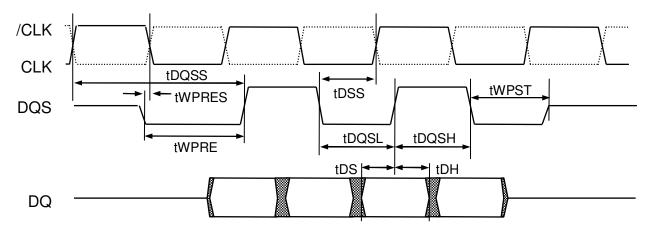

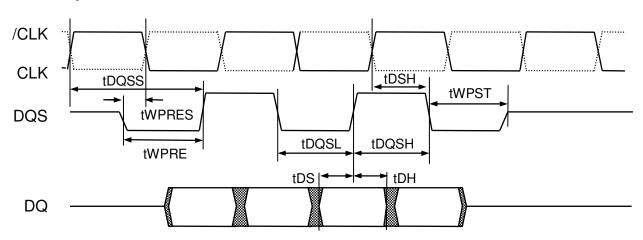

| tDS    | Input Setup time (DQ,DM)                                |        | 0.4                         |       | 0.45                |       | 0.5                 |       | ns   |       |

| tDH    | Input Hold time(DQ,DM)                                  |        | 0.4                         |       | 0.45                |       | 0.5                 |       | ns   |       |

| tIPW   | Control & address input pulse width (for each input)    |        | 2.2                         |       | 2.2                 |       | 2.2                 |       | ns   |       |

| tDIPW  | DQ and DM input pulse width (for each input)            |        | 1.75                        |       | 1.75                |       | 1.75                |       | ns   |       |

| tHZ    | Data-out-high impedance time from CLK//CLK              |        |                             | +0.70 |                     | +0.70 |                     | +0.75 | ns   | 14    |

| tLZ    | Data-out-low impedance time from CLK//CLK               |        | -0.70                       | +0.70 | -0.70               | +0.70 | -0.75               | +0.75 | ns   | 14    |

| tDQSQ  | DQ Valid data delay time from DQS                       |        |                             | 0.40  |                     | 0.45  |                     | 0.5   | ns   |       |

| tHP    | Clock half period                                       |        | tCLmin or<br>tCHmin         |       | tCLmin or<br>tCHmin |       | tCLmin or<br>tCHmin |       | ns   | 20    |

| tQH    | DQ output hold time from DQS (per access)               |        | tHP-tQHS                    |       | tHP-tQHS            |       | tHP-tQHS            |       | ns   |       |

| tQHS   | Data hold skew factor (for DQS & associated DQ signals) |        |                             | 0.50  |                     | 0.55  |                     | 0.75  |      |       |

| tDQSS  | Write command to first DQS latching transition          |        | 0.72                        | 1.25  | 0.75                | 1.25  | 0.75                | 1.25  | tCK  |       |

| tDQSH  | DQS input High level width                              |        | 0.35                        |       | 0.35                |       | 0.35                |       | tCK  |       |

| tDQSL  | DQS input Low level width                               |        | 0.35                        |       | 0.35                |       | 0.35                |       | tCK  |       |

| tDSS   | DQS falling edge to CLK setup time                      |        | 0.2                         |       | 0.2                 |       | 0.2                 |       | tCK  |       |

| tDSH   | DQS falling edge hold time from CLK                     |        | 0.2                         |       | 0.2                 |       | 0.2                 |       | tCK  |       |

| tMRD   | Mode Register Set command cycle time                    |        | 2                           |       | 2                   |       | 2                   |       | tCK  |       |

| tWPRES | Write preamble setup time                               |        | 0                           |       | 0                   |       | 0                   |       | ns   | 16    |

| tWPST  | Write postamble                                         |        | 0.4                         | 0.6   | 0.4                 | 0.6   | 0.4                 | 0.6   | tCK  | 15    |

| tWPRE  | Write preamble                                          |        | max<br>(0.25*tck,<br>1.5ns) |       | 0.25*tck            |       | 0.25*tck            |       | ns   |       |

| tIS    | Input Setup time (address and control)                  |        | 0.6                         |       | 0.75                |       | 0.9                 |       | ns   | 19    |

| tIH    | Input Hold time (address and control)                   |        | 0.6                         |       | 0.75                |       | 0.9                 |       | ns   | 19    |

| tRPST  | Read postamble                                          |        | 0.4                         | 0.6   | 0.4                 | 0.6   | 0.4                 | 0.6   | tCK  |       |

| tRPRE  | Read preamble                                           |        | 0.9                         | 1.1   | 0.9                 | 1.1   | 0.9                 | 1.1   | tCK  |       |

# **AC TIMING REQUIREMENTS(Continues)**

| Symbol | AC Characteristics Parameter                   |      | -5      |      | -6      | _    | 75      | Unit  | Notes |

|--------|------------------------------------------------|------|---------|------|---------|------|---------|-------|-------|

| Symbol | AC Characteristics Farameter                   | Min. | Max     | Min. | Max     | Min. | Max     | Oilit | Notes |

| tRAS   | Row Active time                                | 40   | 120,000 | 42   | 120,000 | 45   | 120,000 | ns    |       |

| tRC    | Row Cycle time(operation)                      | 55   |         | 60   |         | 65   |         | ns    |       |

| tRFC   | Auto Ref. to Active/Auto Ref. command period   | 70   |         | 72   |         | 75   |         | ns    |       |

| tRCD   | Row to Column Delay                            | 15   |         | 18   |         | 20   |         | ns    |       |

| tRP    | Row Precharge time                             | 15   |         | 18   |         | 20   |         | ns    |       |

| tRRD   | Act to Act Delay time                          | 10   |         | 12   |         | 15   |         | ns    |       |

| tWR    | Write Recovery time                            | 15   |         | 15   |         | 15   |         | ns    |       |

| tDAL   | Auto Precharge write recovery + precharge time | _    |         | -    |         | -    |         | tCK   | 21    |

| tWTR   | Internal Write to Read Command Delay           | 2    |         | 1    |         | 1    |         | tCK   |       |

| tXSNR  | Exit Self Ref. to non-Read command             | 75   |         | 75   |         | 75   |         | ns    |       |

| tXSRD  | Exit Self Ref. to -Read command                | 200  |         | 200  |         | 200  |         | tCK   |       |

| tXPNR  | Exit Power down to command                     | 1    |         | 1    |         | 1    |         | tCK   |       |

| tXPRD  | Exit Power down to -Read command               | 1    |         | 1    |         | 1    |         | tCK   | 18    |

| tREFI  | Average Periodic Refresh interval              |      | 7.8     |      | 7.8     |      | 7.8     | μs    | 17    |

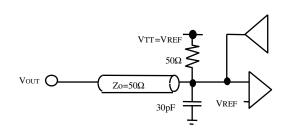

# **Output Load Condition**

## **CAPACITANCE**

$(Ta=25^{\circ}C, Vdd = VddQ = 2.5V \pm 0.2V \ Vss = VssQ = 0V, unless \ otherwise \ noted)$

| Symbol | Parameter                         | Test Condition | Liı  | nits | Delta      | Unit | Notes |

|--------|-----------------------------------|----------------|------|------|------------|------|-------|

| Symbol | r at attletet                     | Test Condition | Min. | Max. | Cap.(Max.) | UIII | Notes |

| CI(A)  | Input Capacitance, address pin    | VI=1.25v       | 1.3  | 2.5  | 0.75       | рF   |       |

| CI(C)  | Input Capacitance, control pin    | f=100MHz       | 1.3  | 2.5  | 0.73       | рF   |       |

| CI(K)  | Input Capacitance, CLK pin        | VI=25mVrms     | 1.3  | 2.5  | 0.25       | pF   |       |

| CI/O   | I/O Capacitance, I/O, DQS, DM pin |                | 2    | 4    | 1.3        | рF   |       |

# IS43R83200B, IS46R83200B IS43R16160B, IS46R16160B

#### Notes

- 1. All voltages referenced to Vss.

- 2. Tests for AC timing, IDD, and electrical, AC and DC characteristics, may be conducted at nominal reference/supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified.

- 3. AC timing and IDD tests may use a VIL to VIH swing of up to 1.5V in the test environment, but input timing is still referenced to VREF (or to the crossing point for CK//CK), and parameter specifications are guaranteed for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals is 1V/ns in the range between VIL(AC) and VIH(AC).

- 4. The AC and DC input level specifications are as defined in the SSTL\_2 Standard (i.e. the receiver will effectively switch as a result of the signal crossing the AC input level, and will remain in that state as long as the signal does not ring back above (below) the DC input LOW (HIGH) level.

- 5. VREF is expected to be equal to 0.5\*VddQ of the transmitting device, and to track variations in the DC level of the same. Peak-to-peak noise on VREF may not exceed +2% of the DC value.

- 6. VTT is not applied directly to the device. VTT is a system supply for signal termination resistors, is expected to be set equal to VREF, and must track variations in the DC level of VREF.

- 7. VID is the magnitude of the difference between the input level on CLK and the input level on /CLK.

- 8. The value of VIX is expected to equal 0.5\*VddQ of the transmitting device and must track variations in the DC level of the same.

- 9. Enables on-chip refresh and address counters.

- 10. IDD specifications are tested after the device is properly initialized.

- 11. This parameter is sampled.  $VddQ = 2.5V \pm 0.2V$ ,  $Vdd = 2.5V \pm 0.2V$ , f = 100 MHz,  $Ta = 25^{\circ}C$ , VOUT(DC) = VddQ/2,  $VOUT(PEAK\ TO\ PEAK) = 25mV$ . DM inputs are grouped with I/O pins reflecting the fact that they are matched in loading (to facilitate trace matching at the board level).

- 12. The CLK//CLK input reference level (for timing referenced to CLK//CLK) is the point at which CLK and /CLK cross; the input reference level for signals other than CLK//CLK, is VREF.

- 13. Inputs are not recognized as valid until VREF stabilizes. Exception: during the period before VREF stabilizes,  $CKE \le 0.3VddQ$  is recognized as LOW.

- 14. t HZ and tLZ transitions occur in the same access time windows as valid data transitions. These parameters are not referenced to a specific voltage level, but specify when the device output is no longer driving (HZ), or begins driving (LZ).

- 15. The maximum limit for this parameter is not a device limit. The device will operate with a greater value for this parameter, but system performance (bus turnaround) will degrade accordingly.

- 16. The specific requirement is that DQS be valid (HIGH, LOW, or at some point on a valid transition) on or before this CLK edge. A valid transition is defined as monotonic, and meeting the input slew rate specifications of the device. When no writes were previously in progress on the bus, DQS will be transitioning from High-Z to logic LOW. If a previous write was in progress, DQS could be HIGH, LOW, or transitioning from HIGH to LOW at this time, depending on tDQSS.

- 17. A maximum of eight AUTO REFRESH commands can be posted to any given DDR SDRAM device.

- 18. tXPRD should be 200 tCLK in the condition of the unstable CLK operation during the power down mode.

- 19. For command/address and CK & /CK slew rate > 1.0V/ns.

- 20. Min (tCL,tCH) refers to the smaller of the actual clock low time and the actual clock high time as provided to the device.

- 21. tDAL minimum = (tWR/tCK) + (tRP/tCK)

- If either addend is not an integer, it should be rounded up.

# Write Operation / tDQSS=max.

# Write Operation / tDQSS=min.

#### **OPERATIONAL DESCRIPTION**

#### BANK ACTIVATE

The DDR SDRAM has four independent banks. Each bank is activated by the ACT command with the bank addresses (BA0,1). A row is indicated by the row address A0-12. The minimum activation interval between one bank and the other bank is tRRD.

#### **PRECHARGE**

The PRE command deactivates the bank indicated by BA0,1. When multiple banks are active, the precharge all command (PREA,PRE+A10=H) is available to deactivate them at the same time. After tRP from the precharge, an ACT command to the same bank can be issued.

#### Bank Activation and Precharge All (BL=8, CL=2) /CLK CLK 2 ACT command / tRCmin tRCmin ACT ACT READ **PRE** ACT Command – tRRD tRP tRAS A0-9,11,12 Xb Y Xb tRCD BL/2 0 Xb Xa Xb A10 BA0,1 00 01 00 01 **DQS** DQ Precharge all

A precharge command can be issued at BL/2 from a read command without data loss.

#### **READ**

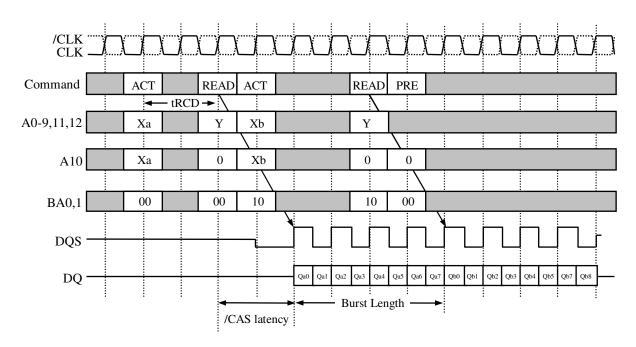

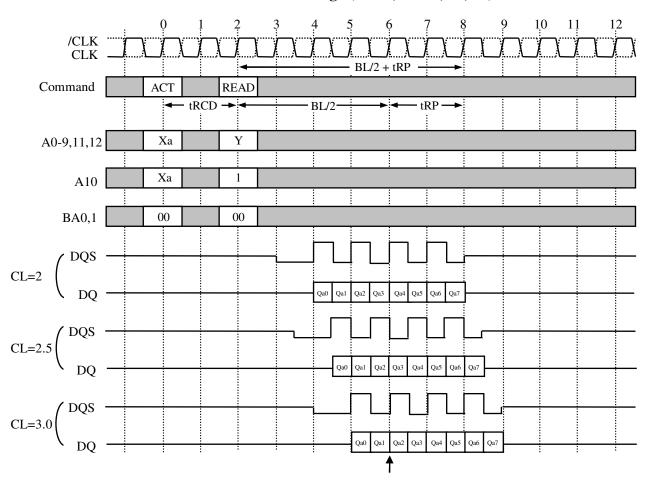

After tRCD from the bank activation, a READ command can be issued. 1st Output data is available after the /CAS Latency from the READ, followed by (BL-1) consecutive data when the Burst Length is BL. The start address is specified by A0-9(x8)/A0-8(x16), and the address sequence of burst data is defined by the Burst Type. A READ command may be applied to any active bank, so the row precharge time (tRP) can be hidden behind continuous output data by interleaving the multiple banks. When A10 is high at a READ command, the auto-precharge (READA) is performed. Any command(READ,WRITE,PRE,ACT) to the same bank is inhibited till the internal precharge is complete. The internal precharge starts at BL/2 after READA. The next ACT command can be issued after (BL/2+tRP) from the previous READA.

### Multi Bank Interleaving READ (BL=8, CL=2)

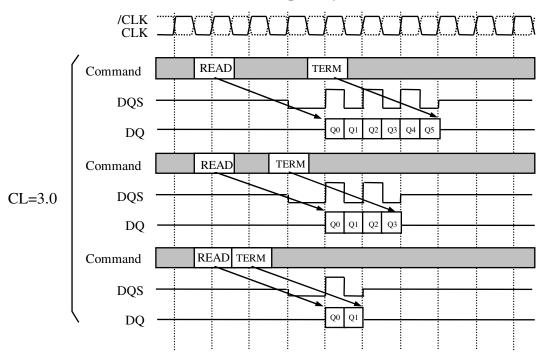

# READ with Auto-Precharge (BL=8, CL=2,2.5,3.0)

**Internal Precharge Start Timing**

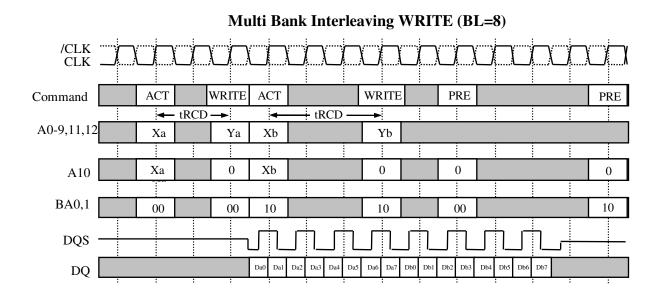

#### WRITE

After tRCD from the bank activation, a WRITE command can be issued. 1st input data is set from the WRITE command with data strobe input, following (BL-1) data are written into RAM, when the Burst Length is BL. The start address is specified by A0-9(x8)/A0-8(x16), and the address sequence of burst data is defined by the Burst Type. A WRITE command may be applied to any active bank, so the row precharge time (tRP) can be hidden behind continuous input data by interleaving the multiple banks. From the last data to the PRE command, the write recovery time (tWRP) is required. When A10 is high at a WRITE command, the auto-precharge(WRITEA) is performed. Any command(READ,WRITE,PRE,ACT) to the same bank is inhibited till the internal precharge is complete. The next ACT command can be issued after tDAL from the last input data cycle.

#### **BURST INTERRUPTION**

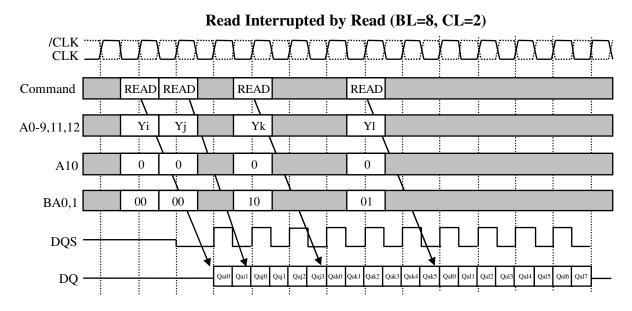

## [Read Interrupted by Read]

Burst read operation can be interrupted by new read of any bank. Random column access is allowed. READ to READ interval is minimum 1CLK.

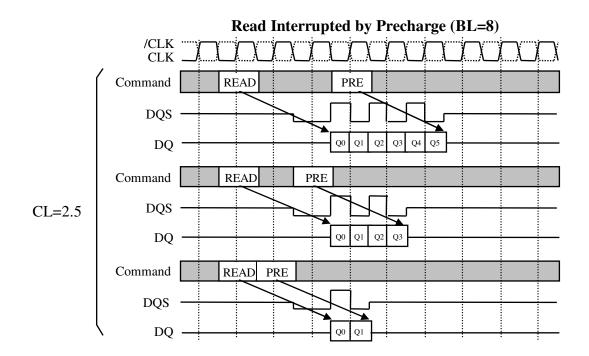

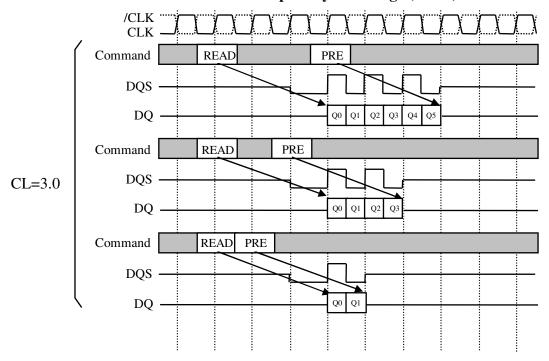

## [Read Interrupted by precharge]

Burst read operation can be interrupted by precharge of the same bank. READ to PRE interval is minimum 1 CLK. A PRE command to output disable latency is equivalent to the /CAS Latency. As a result, READ to PRE interval determines valid data length to be output. The figure below shows examples of BL=8.

Read Interrupted by Precharge (BL=8)

# Read Interrupted by Precharge (BL=8)

## [Read Interrupted by Burst Stop]

Burst read operation can be interrupted by a burst stop command(TERM). READ to TERM interval is minimum 1 CLK. A TERM command to output disable latency is equivalent to the /CAS Latency. As a result, READ to TERM interval determines valid data length to be output. The figure below shows examples of BL=8.

## Read Interrupted by TERM (BL=8) CLK **READ** TERM Command **DQS** Q1 Q3 Q2 Q4 DQ TERM READ Command DQS CL = 2.0DQ READ TERM Command DQS Q1 DQ READ TERM Command DQS Q1 Q2 DQ READ TERM Command DQS CL=2.5DQ READ TERM Command **DQS**

# Read Interrupted by TERM (BL=8)

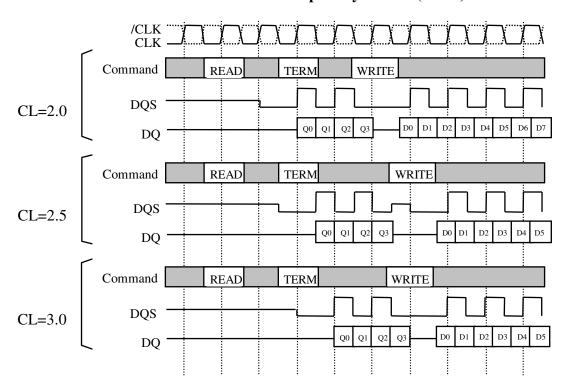

# [Read Interrupted by Write with TERM]

# Read Interrupted by TERM (BL=8)

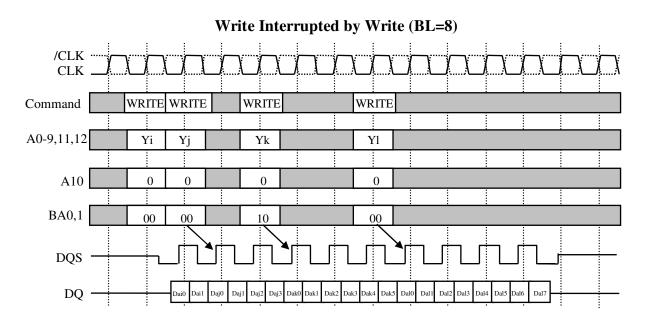

### [Write interrupted by Write]

Burst write operation can be interrupted by write of any bank. Random column access is allowed. WRITE to WRITE interval is minimum 1 CLK.

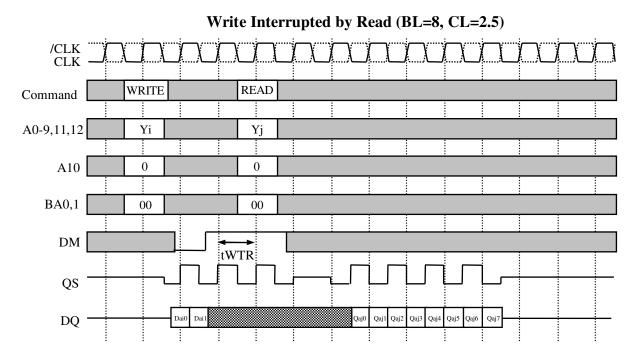

## [Write interrupted by Read]

Burst write operation can be interrupted by read of the same or the other bank. Random column access is allowed. Internal WRITE to READ command interval(tWTR) is minimum 1 CLK. The input data on DQ at the interrupting READ cycle is "don't care". tWTR is referenced from the first positive edge after the last data input.

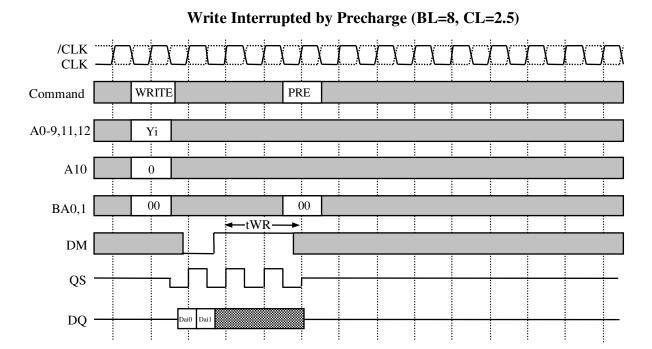

# [Write interrupted by Precharge]

Burst write operation can be interrupted by precharge of the same or all bank. Random column access is allowed. tWR is referenced from the first positive CLK edge after the last data input.

08/13/2010

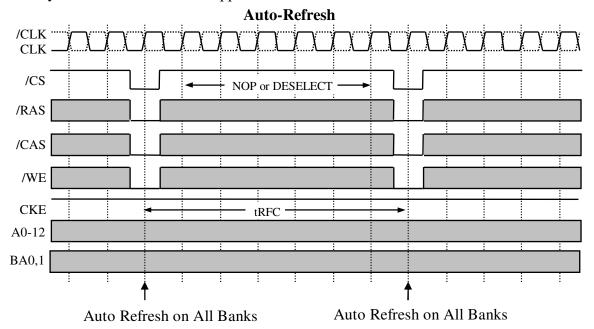

### [AUTO REFRESH]

Single cycle of auto-refresh is initiated with a REFA(/CS=/RAS=/CAS=L,/WE=CKE=H) command. The refresh address is generated internally. 8192 REFA cycles within 64ms refresh 256Mbits memory cells. The auto-refresh is performed on 4 banks concurrently. Before performing an auto refresh, all banks must be in the idle state. Auto-refresh to auto-refresh interval is minimum tRFC. Any command must not be supplied to the device before tRFC from the REFA command.

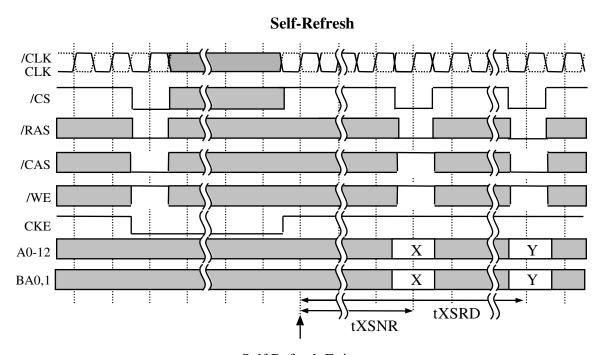

## [SELF REFRESH]

Self-refresh mode is entered by issuing a REFS command (/CS=/RAS=/CAS=L,/WE=H,CKE=L). Once the self-refresh is initiated, it is maintained as long as CKE is kept low. During the self-refresh mode, CKE is asynchronous and the only enable input, all other inputs including CLK are disabled and ignored, so that power consumption due to synchronous inputs is saved. To exit the self-refresh, supplying stable CLK inputs, asserting DESEL or NOP command and then asserting CKE for longer than tXSNR/tXSRD.

Self Refresh Exit

## [Power DOWN]

The purpose of CLK suspend is power down. CKE is synchronous input except during the self-refresh mode. A command at cycle is ignored. From CKE=H to normal function, DLL recovery time is NOT required in the condition of the stable CLK operation during the power down mode.

## [DM CONTROL]

DM is defined as the data mask for writes. During writes, DM masks input data word by word. DM to write mask latency is 0.

# **ORDERING INFORMATION - VDD = 2.5V**

Commercial Range: 0°C to +70°C

| Speed (ns) | Order Part No.  | Organization                                                                 | Package                                                                                                              |

|------------|-----------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 5          | IS43R83200B-5TL | 32Mx8                                                                        | 66-pin TSOP-II, Lead-free                                                                                            |

|            | IS43R16160B-5TL | 16Mx16                                                                       | 66-pin TSOP-II, Lead-free                                                                                            |

|            | IS43R16160B-5BL | 16Mx16                                                                       | 60-ball TF-BGA, Lead-free                                                                                            |

| 6          | IS43R83200B-6TL | 32Mx8                                                                        | 66-pin TSOP-II, Lead-free                                                                                            |

|            | IS43R16160B-6TL | 16Mx16                                                                       | 66-pin TSOP-II, Lead-free<br>60-ball TF-BGA, Lead-free                                                               |

|            | 5               | 5 IS43R83200B-5TL<br>IS43R16160B-5TL<br>IS43R16160B-5BL<br>6 IS43R83200B-6TL | 5 IS43R83200B-5TL 32Mx8 IS43R16160B-5TL 16Mx16 IS43R16160B-5BL 16Mx16 6 IS43R83200B-6TL 32Mx8 IS43R16160B-6TL 16Mx16 |

Industrial Range: -40°C to +85°C

| Frequency | Speed (ns) | Order Part No.   | Organization | Package                   |

|-----------|------------|------------------|--------------|---------------------------|

| 200 MHz   | 5          | IS43R83200B-5TLI | 32Mx8        | 66-pin TSOP-II, Lead-free |

|           |            | IS43R16160B-5TLI | 16Mx16       | 66-pin TSOP-II, Lead-free |

|           |            | IS43R16160B-5TI  | 16Mx16       | 66-pin TSOP-II            |

|           |            | IS43R16160B-5BLI | 16Mx16       | 60-ball TF-BGA, Lead-free |

|           |            | IS43R16160B-5BI  | 16Mx16       | 60-ball TF-BGA            |

| 166 MHz   | 6          | IS43R83200B-6TLI | 32Mx8        | 66-pin TSOP-II, Lead-free |

|           |            | IS43R16160B-6TLI | 16Mx16       | 66-pin TSOP-II, Lead-free |

|           |            | IS43R16160B-6BLI | 16Mx16       | 60-ball TF-BGA, Lead-free |

|           |            | IS43R16160B-6BI  | 16Mx16       | 60-ball TF-BGA            |

Automotive Range (A1): -40°C to +85°C

| Frequency | Speed (ns) | Order Part No.    | Organization | Package                   |

|-----------|------------|-------------------|--------------|---------------------------|

| 166 MHz   | 6          | IS46R83200B-6TLA1 | 32Mx8        | 66-pin TSOP-II, Lead-free |

|           |            | IS46R16160B-6TLA1 | 16Mx16       | 66-pin TSOP-II, Lead-free |

|           |            | IS46R16160B-6BLA1 | 16Mx16       | 60-ball TF-BGA, Lead-free |