### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to COM, all currents are defined positive into any lead. The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol              | Definition                                               |             | Min.                 | Max.                  | Units  |

|---------------------|----------------------------------------------------------|-------------|----------------------|-----------------------|--------|

| V <sub>B</sub>      | High side floating supply voltage                        |             | -0.3                 | 625                   |        |

| Vs                  | High side floating supply offset voltage                 |             | V <sub>B</sub> - 25  | V <sub>B</sub> + 0.3  | .,     |

| V <sub>HO</sub>     | High side floating output voltage                        |             | V <sub>S</sub> - 0.3 | V <sub>B</sub> + 0.3  | V      |

| V <sub>LO</sub>     | Low side output voltage                                  |             | -0.3                 | V <sub>CC</sub> + 0.3 |        |

| lvco                | Voltage controlled oscillator input current (Note 1)     |             | -5                   | + 5                   | mA     |

| lcc                 | Supply current (Note 2)                                  |             | -25                  | 25                    | mA     |

| dV <sub>S</sub> /dt | Allowable offset voltage slew rate                       |             | -50                  | 50                    | V/ns   |

| PD                  | Package power dissipation @ T <sub>A</sub> ≤ +25°C       | 8-Lead PDIP | _                    | 1                     | w      |

|                     | PD=(T <sub>JMAX</sub> -T <sub>A</sub> )Rth <sub>JA</sub> | 8-Lead SOIC | _                    | 0.625                 | VV     |

| RthJA               | Thermal resistance, junction to ambient                  | 8-Lead PDIP | _                    | 125                   | 00.004 |

|                     |                                                          | 8-Lead SOIC | _                    | 200                   | °C/W   |

| TJ                  | Junction temperature                                     |             | -55                  | 150                   |        |

| TS                  | Storage temperature                                      |             | -55                  | 150                   | °C     |

| TL                  | Lead temperature (soldering, 10 seconds)                 |             | _                    | 300                   |        |

Note 1: This IC contains a zener clamp structure between the chip VCO and COM, which has a nominal breakdown voltage of 6V. Please note that this pin should not be driven by a DC, low impedance power source greater than 6V.

Note 2: This IC contains a zener clamp structure between the chip VCC and COM, which has a nominal breakdown voltage of 15.6V. Please note that this supply pin should not be driven by a DC, low impedance power source greater than the VCLAMP specified in the Electrical Characteristics section.

### **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions.

| Symbol            | Definition                                            | Min.                  | Max.   | Units |

|-------------------|-------------------------------------------------------|-----------------------|--------|-------|

| V <sub>BS</sub>   | High side floating supply voltage                     | V <sub>CC</sub> - 0.7 | VCLAMP |       |

| Vs                | Steady state high side floating supply offset voltage | -1                    | 600    | V     |

| Vcc               | Supply voltage                                        | V <sub>CCUV+</sub>    | VCLAMP |       |

| Icc               | Supply current                                        | Note 3                | 10     | mA    |

| R <sub>FMIN</sub> | Minimum frequency setting resistance                  | 20                    | 140    | kΩ    |

| V <sub>VCO</sub>  | VCO pin voltage                                       | 0                     | 5      | V     |

| TJ                | Junction temperature                                  | -25                   | 125    | ဗ     |

Note 3: Enough current should be supplied into the VCC pin to keep the internal 15.6V zener clamp diode on this pin regulating its voltage, VCLAMP.

### **Electrical Characteristics**

$V_{CC} = V_{BS} = V_{BIAS} = 14V + /-0.25V, C_{LO} = C_{HO} = 1000 pF, R_{FMIN} = 82 k\Omega \ and \ T_{A} = 25 ^{\circ}C \ unless \ otherwise \ specified.$

| Symbol               | Definition                                                                       | Min.     | Тур. | Max. | Units  | Test Conditions                            |

|----------------------|----------------------------------------------------------------------------------|----------|------|------|--------|--------------------------------------------|

| Supply               | Characteristics                                                                  |          |      |      | •      |                                            |

| V <sub>CCUV+</sub>   | $V_{CC}$ and $V_{BS}$ supply undervoltage positive going threshold               | 11.4     | 12.6 | 13.8 |        | V <sub>CC</sub> rising from OV             |

| V <sub>CCUV</sub> -  | V <sub>CC</sub> and V <sub>BS</sub> supply undervoltage negative going threshold | 9.0      | 10.0 | 11.0 | V      |                                            |

| V <sub>UVHYS</sub>   | V <sub>CC</sub> supply undervoltage lockout hysteresis                           | _        | 2.7  | _    |        |                                            |

| IQCCUV               | UVLO quiescent current                                                           | _        | 45   | 80   |        | V <sub>CC</sub> = 10V                      |

| IQCCFLT              | Fault mode quiescent current                                                     | <u> </u> | 100  | _    | μΑ     |                                            |

| ICCHF                | V <sub>CC</sub> supply current f=85KHz                                           | T —      | 4.5  | _    | A      | V <sub>VCO</sub> =0V                       |

| ICCLF                | V <sub>CC</sub> supply current f=35KHz                                           | <u> </u> | 2.0  | _    | mA     | V <sub>VCO</sub> =6V                       |

| VCLAMP               | V <sub>CC</sub> Zener clamp voltage                                              | 14.4     | 15.4 | _    | V      | I <sub>CC</sub> = 10mA                     |

| Floating             | g Supply Characteristics                                                         | •        | •    | •    | •      | •                                          |

| I <sub>QBS0</sub>    | Quiescent V <sub>BS</sub> supply current                                         | I —      | 80   | 150  | _      | V <sub>CC</sub> =10V, V <sub>BS</sub> =14V |

| I <sub>QBSUV</sub>   | Quiescent V <sub>BS</sub> supply current                                         | _        | 20   | 40   | μΑ     | V <sub>CC</sub> =10V, V <sub>BS</sub> =7V  |

| V <sub>BSUV+</sub>   | VBS supply undervoltage positive going threshold                                 | 7.7      | 9.0  | 10.3 | V      |                                            |

| V <sub>BSUV</sub> -  | VBS supply undervoltage negative going threshold                                 | 6.8      | 8.0  | 9.2  | V      |                                            |

| I <sub>LK</sub>      | Offset supply leakage current                                                    | <u> </u> | _    | 50   | μΑ     | V <sub>B</sub> = V <sub>S</sub> = 600V     |

| Oscillat             | or I/O Characteristics                                                           | •        |      |      | •      |                                            |

| f <sub>(min)</sub>   | Minimum oscillator frequency (Note 4)                                            | 29.6     | 34   | 38.2 | 1.1.1- | V <sub>VCO</sub> =6V                       |

| f <sub>(max)</sub>   | Maximum oscillator frequency (Note 4)                                            | 67       | 86   | 96   | kHz    | V <sub>VCO</sub> =0V                       |

| D                    | Oscillator duty cycle                                                            | _        | 50   | _    | %      |                                            |

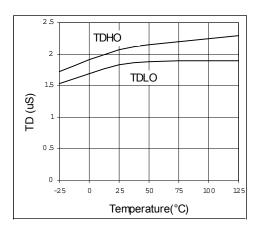

| DT <sub>LO</sub>     | LO output deadtime                                                               | _        | 2.0  | _    |        |                                            |

| DT <sub>HO</sub>     | HO output deadtime                                                               | <u> </u> | 2.0  | _    | μS     |                                            |

| l <sub>VCOQS</sub>   | I <sub>VCO</sub> quick start                                                     | _        | 50   | _    |        | V <sub>VCO</sub> =0V                       |

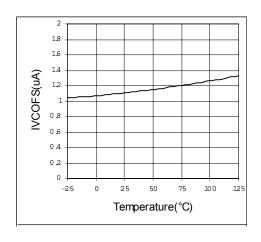

| l <sub>VCOFS</sub>   | I <sub>VCO</sub> frequency sweep                                                 | 0.8      | 1.3  | 1.7  | μΑ     | V <sub>VCO</sub> =2V                       |

| I <sub>VCO_5V</sub>  | I <sub>VCO</sub> when VCO is at 5V                                               | _        | 1.1  | _    |        |                                            |

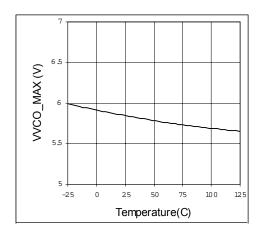

| V <sub>VCO_max</sub> | Maximum VCO voltage                                                              | _        | 6    | _    | V      |                                            |

| Gate Di              | river Output Characteristics                                                     | •        | •    |      | •      | •                                          |

| V <sub>LO=LOW</sub>  | LO output voltage when LO is low                                                 | -        | СОМ  | _    |        |                                            |

| V <sub>HO=LOW</sub>  | HO output voltage when HO is low                                                 |          | СОМ  | _    |        |                                            |

| V <sub>LO=HIGH</sub> | LO output voltage when LO is high                                                | _        | VCC  | _    | mV     |                                            |

| V <sub>HO=HIGH</sub> | HO output voltage when HO is high                                                | _        | VCC  | _    |        |                                            |

| T <sub>RISE</sub>    | Turn on rise time                                                                | I —      | 150  | 230  |        |                                            |

| T <sub>FALL</sub>    | Turn off fall time                                                               | <u> </u> | 75   | 120  | nS     |                                            |

| IO+                  | Output source short circuit pulsed current                                       | I —      | 140  | _    | mA     |                                            |

| 10-                  | Output sink short circuit pulse current                                          | 1        | 230  |      | mA     |                                            |

Note 4: Frequency shown is nominal for  $R_{FMIN}$ =82k $\Omega$ . Frequency can be programmed higher or lower with the value of  $R_{FMIN}$ .

### **Electrical Characteristics**

$V_{CC} = V_{BS} = V_{BIAS} = 14V + /-0.25V, C_{LO} = C_{HO} = 1000 pF, R_{FMIN} = 82 k\Omega \ \ and \ T_{A} = 25 ^{\circ}C \ unless \ otherwise \ specified.$

| Symbol                | Definition                                | Min. | Тур. | Max. | Units | <b>Test Conditions</b> |  |  |

|-----------------------|-------------------------------------------|------|------|------|-------|------------------------|--|--|

| Protectio             | Protection Characteristics                |      |      |      |       |                        |  |  |

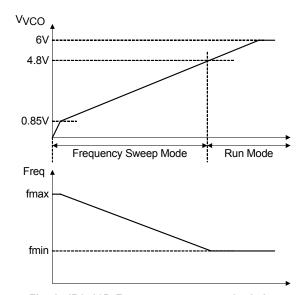

| V <sub>V</sub> CO_RUN | VCO voltage when entering run mode        | _    | 4.8  | _    | V     |                        |  |  |

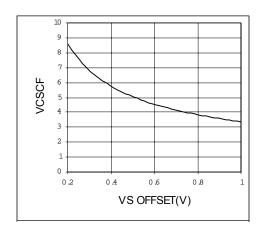

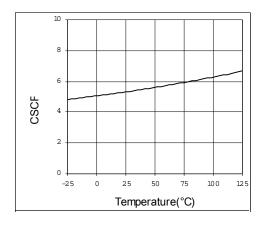

| CSCF                  | Crest factor peak-to-average fault factor | _    | 5.0  | _    | N/A   | Vs offset = 0.5V       |  |  |

| VS_<br>OFFSET_MAX     | Maximum crest factor VS offset voltage    | _    | 3.0  | _    | V     |                        |  |  |

| V <sub>V</sub> COSD   | V <sub>VCO</sub> shutdown voltage         | 0.74 | 0.82 | 0.91 | V     |                        |  |  |

| Minimum               | Minimum Frequency Setting Characteristics |      |      |      |       |                        |  |  |

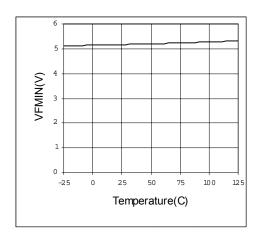

| V <sub>FMIN</sub>     | FMIN lead voltage during normal operation | 4.8  | 5.1  | 5.4  | V     |                        |  |  |

| VFMINFLT              | FMIN lead voltage during fault mode       | _    | 0    | _    | V     |                        |  |  |

| Bootstra              | Bootstrap FET                             |      |      |      |       |                        |  |  |

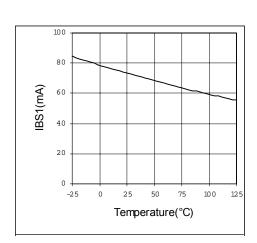

| IBS1                  | VB current                                | 30   | 70   | _    |       | CBS=0.1uF,<br>VS=0V    |  |  |

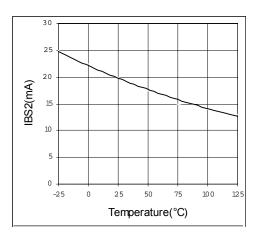

| IBS2                  | VB current                                | 10   | 20   |      | mA    | VBS = 10V              |  |  |

#### **Lead Definitions**

| Symbol | Description                           |                                                                   |      |

|--------|---------------------------------------|-------------------------------------------------------------------|------|

| VCC    | Supply voltage                        | VCC 1 0 8                                                         | ] VB |

| СОМ    | IC power and signal ground            |                                                                   | •    |

| FMIN   | Minimum frequency setting             | СОМ 2 况 7                                                         | ] HO |

| VCO    | Voltage controlled oscillator input   | 20                                                                | ,    |

| LO     | Low-side gate driver output           | COM 2 7<br>FMIN 3 6                                               | ] VS |

| VS     | High-side floating return             | $\bigvee_{VCO} \boxed{4} \boxed{\mathbf{\mathfrak{G}}} \boxed{5}$ | l LO |

| НО     | High-side gate driver output          |                                                                   | ,    |

| VB     | High-side gate driver floating supply |                                                                   |      |

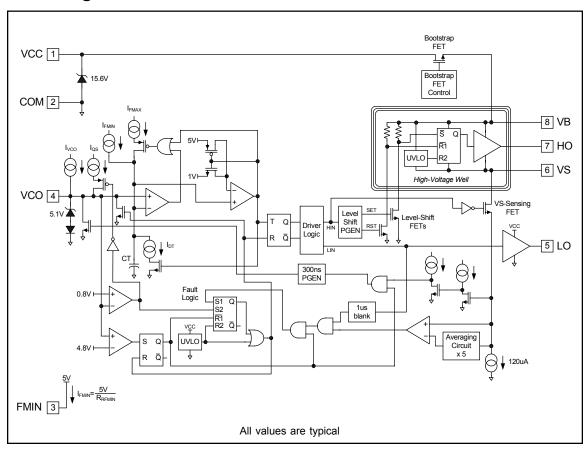

### **Block Diagram**

**State Diagram Power Turned** On **VCCUV Mode** 1/2-Bridge Off  $l_{QCC} \cong 45 \mu A$ **VCC < 10V**  $V_{VCO} = 0V$  $V_{FMIN} = 0V$ (VCCUV-) **FAULT** VCC > 12.6V Mode (VCCUV+) 1/2-Bridge Off  $V_{VCO} = 0V$ I<sub>QCCFLT</sub>≅100μA  $V_{FMIN} = 0V$ **VCC < 10V Frequency Sweep Mode** (VCCUV-) Crest Factor > 5.0  $V_{FMIN} = 5.1V$ (CSCF) VCO ramps up, frequency ramps down or V<sub>VCO</sub> < 0.82V Crest Factor Disabled (V<sub>VCOSD</sub>) ZVS Disabled V<sub>VCO</sub> >4.8V  $(V_{\text{VCO}} RUN)$ **RUN Mode** V<sub>VCO</sub> = 6.0V, Frequency = fmin Crest Factor Enabled ZVS Enabled If non-ZVS detected then  $W_{CO}$  decreases and frequency increases to maintain ZVS

6 www.irf.com

All values are typical

#### **Functional Description**

#### Under-voltage Lock-Out Mode

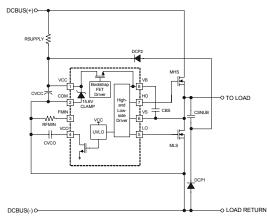

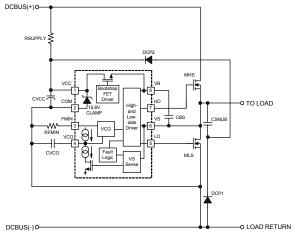

The under-voltage lock-out mode (UVLO) is defined as the state the IR2520D is in when VCC is below the turn-on threshold of the IC. The IR2520D UVLO is designed to maintain an ultra-low supply current (IOCCUV<80uA), and to guarantee that the IR2520D is fully functional before the high- and low-side output gate drivers are activated. The VCC capacitor, CVCC, is charged by current through supply resistor, RSUPPLY, minus the start-up current drawn by the IR2520D (Figure 1). This resistor is chosen to provide sufficient current to supply the IR2520D from the DC bus. Once the capacitor voltage on VCC reaches the start-up threshold, V<sub>CCUV+</sub>, the IR2520D turns on and HO and LO start oscillating. Capacitor CVCC should be large enough to hold the voltage at VCC above the  $V_{\mbox{CCUV+}}$  threshold for one half-cycle of the line voltage or until the external auxiliary supply can maintain the required supply voltage and current to the IC.

Fig. 1 Start-up circuitry

An internal bootstrap MOSFET between VCC and VB and external supply capacitor, CBS, determine the supply voltage for the high-side driver circuitry. An external charge pump circuit consisting of capacitor CSNUB and diodes DCP1 and DCP2, comprises the auxiliary supply voltage for the low-side driver circuitry. To guarantee that the high-side supply is charged up before the first pulse on pin HO, the first pulse from the output drivers comes from the LO pin. LO may oscillate several times until VB-VS exceeds the high-side UVLO rising threshold, VBSUV+ (9 Volts), and the

high-side driver is enabled. During UVLO mode, the high- and low-side gate driver outputs, HO and LO, are both low and pin VCO is pulled down to COM for resetting the starting frequency to the maximum.

#### Frequency Sweep Mode

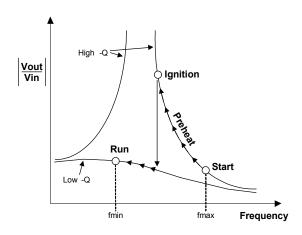

When VCC exceeds VCCUV+ threshold, the IR2520D enters frequency sweep mode. An internal current source (Figure 2) charges the external capacitor on pin VCO, CVCO, and the voltage on pin VCO starts ramping up linearly. An additional quick-start current (IVCOQS) is also connected to the VCO pin and charges the VCO pin initially to 0.85V. When the VCO voltage exceeds 0.85V, the quick-start current is then disconnected internally and the VCO voltage continues to charge up with the normal frequency sweep current source (IVCOFS) (Figure 3). This quick-start brings the VCO voltage quickly to the internal range of the VCO. The frequency ramps down towards the resonance frequency of the high-Q ballast output stage causing the lamp voltage and load current to increase. The voltage on pin VCO continues to increase and the frequency keeps decreasing until the lamp ignites. If the lamp ignites successfully, the voltage on pin VCO continues to increase until it internally limits at 6V (V<sub>VCO MAX</sub>). The frequency stops decreasing and stays at the minimum frequency as programmed by an external resistor, RFMIN, on pin FMIN. The minimum frequency should be set below the high-Q resonance frequency of the ballast output stage to ensure that the frequency ramps through resonance for lamp ignition (Figure 4). The desired preheat time can be set by adjusting the slope of the VCO ramp with the external capacitor CVCO.

Fig. 2 Frequency sweep circuitry mode circuitry

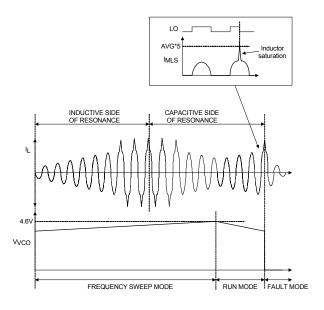

Fig. 3 IR2520D Frequency sweep mode timing diagram.

Fig. 4 Resonant tank Bode plot with lamp operating points.

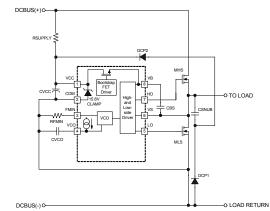

#### Run Mode

The IR2520D enters RUN mode when the voltage on pin VCO exceeds 4.8V (VVCO\_RUN). The lamp has ignited and the ballast output stage becomes a low-Q, series-L, parallel-RC circuit. Also, the VS sensing and fault logic blocks (Figure 5) both become enabled for protection against non-ZVS and over-current fault conditions. The voltage on the VCO pin continues to increase and the frequency deceases further until the VCO pin voltage limits at 6V (VVCO\_MAX) and the minimum frequency is reached. The resonant inductor, resonant capacitor, DC bus voltage and minimum frequency determine the running lamp power. The IC stays at this minimum frequency unless non-ZVS occurs at the VS pin, a crest factor over-current condition is detected at the VS pin, or VCC decreases below the UVLO- threshold (see State Diagram).

Fig. 5 IR2520D Run mode circuitry.

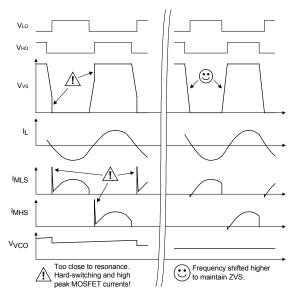

#### Non Zero-Voltage Switching (ZVS) Protection

During run mode, if the voltage at the VS pin has not slewed entirely to COM during the dead-time such that there is voltage between the drain and source of the external low-side half-bridge MOSFET when LO turns-on, then the system is operating too close to, or, on the capacitive side of, resonance. The result is non-ZVS capacitive-mode switching that causes high peak currents to flow in the half-bridge MOSFETs that can damage or destroy them (Figure 6). This can occur due to a lamp filament failure(s),

lamp removal (open circuit), a dropping DC bus during a mains brown-out or mains interrupt, lamp variations over time, or component variations. To protect against this, an internal high-voltage MOSFET is turned on at the turn-off of HO and the VS-sensing circuit measures VS at each rising edge of LO. If the VS voltage is non-zero, a pulse of current is sinked from the VCO pin (Figures 5 and 6) to slightly discharge the external capacitor, CVCO, causing the frequency to increase slightly. The VCO capacitor then charges up during the rest of the cycle slowly due to the internal current source.

Fig. 6 IR2520D non-ZVS protection timing diagram.

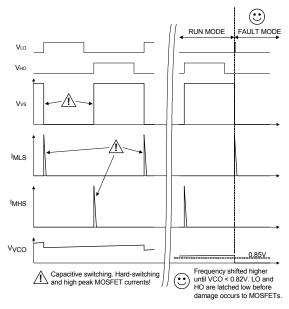

The frequency is trying to decrease towards resonance by charging the VCO capacitor and the adaptive ZVS circuit "nudges" the frequency back up slightly above resonance each time non-ZVS is detected at the turn-on of LO. The internal high-voltage MOSFET is then turned off at the turn-off of LO and it withstands the high-voltage when VS slews up to the DC bus potential. The circuit then remains in this closed-loop adaptive ZVS mode during running and maintains ZVS operation with changing line conditions, component tolerance variations and lamp/load variations. During a lamp removal or filament failure, the lamp resonant tank will be interrupted causing the half-bridge output to go

open circuit (Figure 7). This will cause capacitive switching (hard-switching) resulting in high peak MOSFET currents that can damage them. The IR2520D will increase the frequency in attempt to satisfy ZVS until the VCO pin decreases below 0.82V ( $V_{VCOSD}$ ). The IC will enter Fault Mode and latch the LO and HO gate driver outputs 'low' for turning the half-bridge off safely before any damage can occur to the MOSFETs.

Fig. 7 Lamp removal or open filament fault condition timing diagram

#### Crest Factor Over-current Protection

During normal lamp ignition, the frequency sweeps through resonance and the output voltage increases across the resonant capacitor and lamp until the lamp ignites. If the lamp fails to ignite, the resonant capacitor voltage, the inductor voltage and inductor current will continue to increase until the inductor saturates or the output voltage exceeds the maximum voltage rating of the resonant capacitor or inductor. The ballast must shutdown before damage occurs. To protect against a lamp non-strike fault condition, the IR2520D uses the VS-sensing circuitry (Figure 5) to also measure the low-side half-bridge MOSFET current for detecting an

over-current fault. By using the RDSon of the external lowside MOSFET for current sensing and the VS-sensing circuitry, the IR2520D eliminates the need for an additional current sensing resistor, filter and current-sensing pin. To cancel changes in the RDSon value due to temperature and MOSFET variations, the IR2520D performs a crest factor measurement that detects when the peak current exceeds the average current by a factor of 5 (CSCF). Measuring the crest factor is ideal for detecting when the inductor saturates due to excessive current that occurs in the resonant tank when the frequency sweeps through resonance and the lamp does not ignite. When the VCO voltage ramps up for the first time from zero, the resonant tank current and voltages increase as the frequency decreases towards resonance (Figure 8). If the lamp does not ignite, the inductor current will eventually saturate but the crest factor fault protection is not active until the VCO voltage exceeds 4.8V (V<sub>VCO RUN</sub>) for the first time. The frequency will continue decreasing to the capacitive side of resonance towards the minimum frequency setting and the resonant tank current and voltages will decrease again. When the VCO voltage exceeds 4.8V (V<sub>VCO RUN</sub>), the IC enters Run Mode and the non-ZVS protection and crest factor protection are both enabled. The non-ZVS protection will increase the frequency again cycle-by-cycle towards resonance from the capacitive side. The resonant tank current will increase again as the frequency nears resonance until the inductor saturates again.

The crest factor protection is now enabled and measures the instantaneous voltage at the VS pin only during the time when LO is 'high' and after an initial 1us blank time from the rising edge of LO. The blank time is necessary to prevent the crest factor protection circuit from reacting to a non-ZVS condition. An internal averaging circuit averages the instantaneous voltage at the VS pin over 10 to 20 switching cycles of LO. During Run Mode, the first time the inductor saturates when LO is 'high' (after the 1us blank time) and the peak current exceeds the average by 5 (CSCF), the IR2520D will enter Fault Mode and both LO and HO outputs will be latched 'low'. The half-bridge will be safely disabled before any damage can occur to the ballast components.

The crest factor peak-to-average fault factor varies as a function of the internal average (Figure 20). The maximum internal average should be below 3.0 volts. Should the average exceed this amount, the multiplied average voltage can exceed the maximum limit of the VS sensing circuit and the VS sensing circuit will no longer detect crest factor

faults. This can occur when a half-bridge MOSFET is selected that has an RDSon that is too large for the application causing the internal average to exceed the maximum limit.

#### **FAULT MODE**

During Run Mode, should the VCO voltage decrease below  $0.82V~(V_{VCOSD})$  or a crest factor fault occur, the IR2520D will enter Fault Mode (see State Diagram). The LO and HO gate driver outputs are both latched 'low' so that the half-bridge is disabled. The VCO pin is pulled low to COM and the FMIN pin decreases from 5V to COM. VCC draws micro-power current (ICCFLT) so that VCC stays at the clamp voltage and the IC remains in Fault Mode without the need for the charge-pump auxiliary supply. To exit Fault Mode and return to Frequency Sweep Mode, VCC must be cycled below the UVLO- threshold and back above the UVLO+ threshold.

Fig. 8 Crest factor protection timing diagram

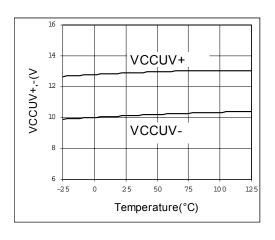

Fig. 9 VCCUV+/- vs TEMP

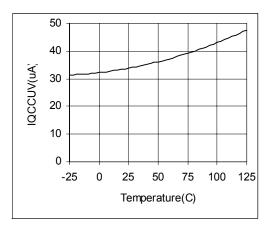

Fig. 10 IQCCUV vs TEMP VCC=10V, VCO=0V

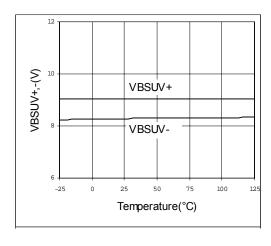

Fig. 11 VBSUV+/- vs TEMP

Fig. 12 IQBSUV vs TEMP

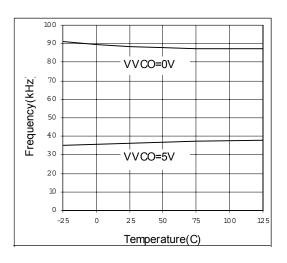

Fig. 13 Frequency vs TEMP REMIN=82K

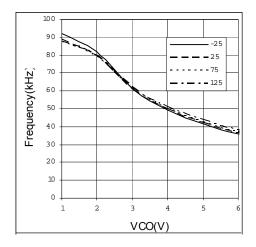

Fig. 15 FREQ VS VVCO vs TEMP VCC=14V

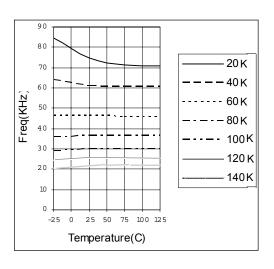

Fig. 14 Frequency vs RFMIN vs TEMP VVCO=6V

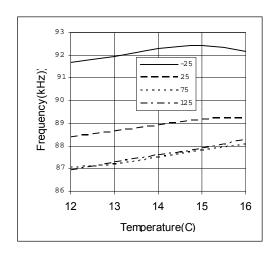

Fig. 16 FREQ VS VCC vs TEMP VVCO=0V

Fig. 17 DTHO, DTLO vs TEMP VCO=0V

Fig. 18 IVCO\_FS vs TEMP

Fig. 19 VVCOMAX vs TEMP

Fig. 20 CSCF vs OFFSET

1.5 1.25 1.075 0.75 0.5 0.25 0.25 0.25 50 75 100 125 Temperature (°C)

Fig. 21 CSCF vs TEMP VS\_OFFSET=0.5V

Fig. 22 VVCO\_SD vs TEMP

Fig. 23 VFMIN vs TEMP VCO=0V, RFMIN=82K

Fig. 24 IBS1 vs TEMP

Fig. 26 IBS2 vs TEMP

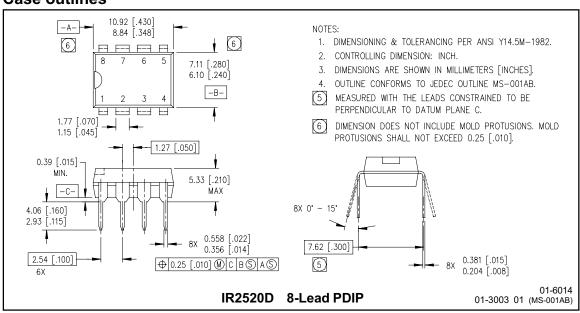

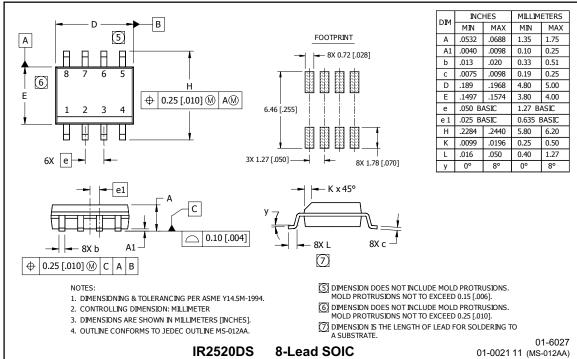

#### **Case outlines**

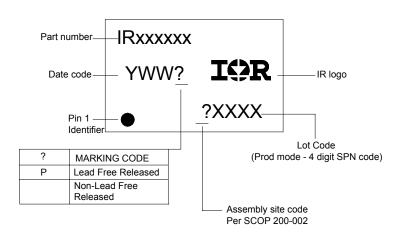

### LEADFREE PART MARKING INFORMATION

#### ORDER INFORMATION

### **Basic Part (Non-Lead Free)**

8-Lead PDIP IR2520D order IR2520D 8-Lead SOIC IR2520DS order IR2520DS

#### **Leadfree Part**

8-Lead PDIP IR2520D order IR2520DPbF 8-Lead SOIC IR2520DS order IR2520DSPbF

International

TOR Rectifier

IR WORLD HEADQUARTERS: 233 Kansas St., El Segundo, California 90245 Tel: (310) 252-7105

This product has been qualified per industrial level MSL-3

Data and specifications subject to change without notice. 3/1/2005