### **TABLE OF CONTENTS**

| Features 1                                   |

|----------------------------------------------|

| Applications1                                |

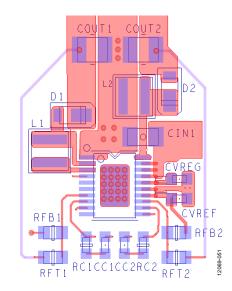

| Typical Application Circuit 1                |

| General Description                          |

| Revision History 2                           |

| Specifications                               |

| Absolute Maximum Ratings 5                   |

| Thermal Resistance                           |

| ESD Caution 5                                |

| Pin Configurations and Function Descriptions |

| Typical Performance Characteristics          |

| Theory of Operation14                        |

| PWM Mode14                                   |

| PSM Mode14                                   |

| Undervoltage Lockout (UVLO)14                |

| Oscillator and Synchronization14             |

| Internal Regulators14                        |

| Precision Enabling15                         |

#### **REVISION HISTORY**

| 7/ <b>2019—Rev. D to Rev. E</b><br>Replaced Figure 7   |

|--------------------------------------------------------|

| <b>3/2019—Rev. C to Rev. D</b><br>Changes to Figure 48 |

| 6/2018—Rev. B to Rev. C                                |

| Changes to Figure 34, Figure 35, and Figure 36 13      |

| 7/2017—Rev. A to Rev. B                                |

| Changes to Table 10 and Table 11                       |

| Updated Outline Dimensions                             |

| Changes to Ordering Guide                              |

| 6/2015—Rev. 0 to Rev. A                                |

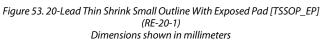

Added 20-Lead TSSOP ......Universal

|   | Soft Start                         | 15 |

|---|------------------------------------|----|

|   | Slew Rate Control                  | 15 |

|   | Current-Limit Protection           | 15 |

|   | Overvoltage Protection             | 15 |

|   | Thermal Shutdown                   | 15 |

|   | Start-Up Sequence                  | 15 |

| A | pplications Information            | 17 |

|   | ADIsimPower Design Tool            | 17 |

|   | Component Selection                | 17 |

|   | Loop Compensation                  | 20 |

|   | Common Applications                | 22 |

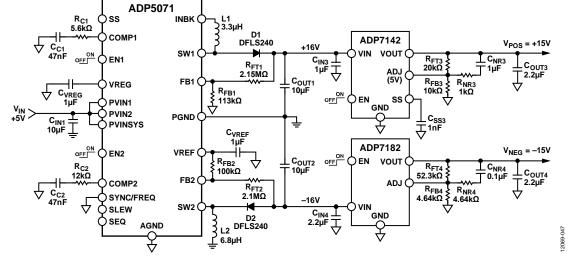

|   | Super Low Noise With Optional LDOs | 24 |

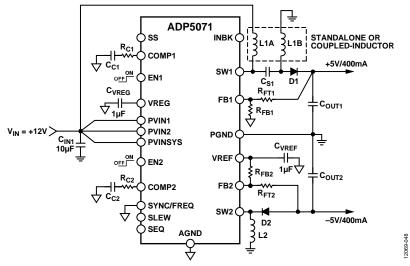

|   | SEPIC Step-Up/Step-Down Operation  | 25 |

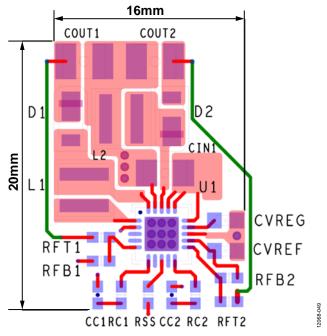

|   | Layout Considerations              | 26 |

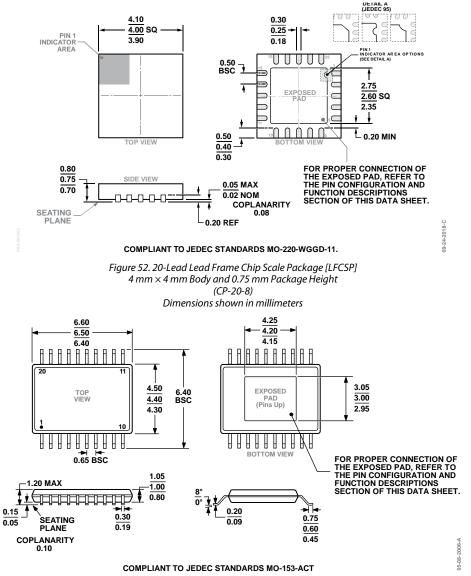

| С | Outline Dimensions                 | 27 |

|   | Ordering Guide                     | 27 |

| Change to Pull-Down Resistance Parameter, Table 23                 |

|--------------------------------------------------------------------|

| Changes to Table 3 and Table 45                                    |

| Added Figure 3, Renumbered Sequentially6                           |

| Changes to Figure 37 Caption to Figure 39 Caption 13               |

| Changes to Internal Regulators Section 14                          |

| Change to Soft Start Section 15                                    |

| Changes to Component Selection Section                             |

| Changes to Output Capacitors Section, Soft Start Resistor Section, |

| and Diodes Section                                                 |

| Changes to Figure 52 Caption                                       |

| Added Figure 53                                                    |

| Updated Outline Dimensions                                         |

| Changes to Ordering Guide                                          |

#### 2/2015—Revision 0: Initial Version

### **SPECIFICATIONS**

PVIN1 = PVIN2 = PVINSYS = 2.85 V to 15 V,  $V_{POS} = 15 V$ ,  $V_{NEG} = -15 V$ ,  $f_{SW} = 1200 \text{ kHz}$ ,  $T_J = -40^{\circ}\text{C}$  to  $+125^{\circ}\text{C}$  for minimum/maximum specifications, and  $T_A = 25^{\circ}\text{C}$  for typical specifications, unless otherwise noted.

| Parameter                              | Symbol                     | Min   | Тур    | Max   | Unit | <b>Test Conditions/Comments</b>                                                |

|----------------------------------------|----------------------------|-------|--------|-------|------|--------------------------------------------------------------------------------|

| INPUT SUPPLY VOLTAGE RANGE             | V <sub>IN</sub>            | 2.85  |        | 15    | V    | PVIN1, PVIN2, PVINSYS                                                          |

| QUIESCENT CURRENT                      |                            |       |        |       |      |                                                                                |

| Operating Quiescent Current            |                            |       |        |       |      |                                                                                |

| PVIN1, PVIN2, PVINSYS (Total)          | lq                         |       | 3.5    | 4.0   | mA   | No switching, EN1 = EN2 = high,<br>PVIN1 = PVIN2 = PVINSYS = 5 V               |

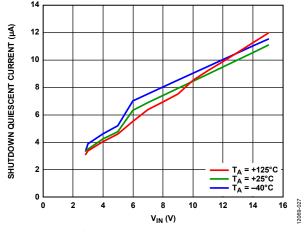

| Shutdown Current                       | Ishdn                      |       | 5      | 10    | μΑ   | No switching, EN1 = EN2 = low,<br>PVIN1 = PVIN2 = PVINSYS = 5 V                |

| UVLO                                   |                            |       |        |       |      |                                                                                |

| System UVLO Threshold                  |                            |       |        |       |      | PVINSYS                                                                        |

| Rising                                 | VUVLO_RISING               |       | 2.8    | 2.85  | V    |                                                                                |

| Falling                                | VUVLO_FALLING              | 2.5   | 2.55   |       | V    |                                                                                |

| Hysteresis                             | V <sub>HYS_1</sub>         |       | 0.25   |       | V    |                                                                                |

| OSCILLATOR CIRCUIT                     |                            |       |        |       |      |                                                                                |

| Switching Frequency                    | fsw                        | 1.130 | 1.200  | 1.270 | MHz  | SYNC/FREQ = low                                                                |

|                                        |                            | 2.240 | 2.400  | 2.560 | MHz  | SYNC/FREQ = high (connect to<br>VREG)                                          |

| SYNC/FREQ Input                        |                            |       |        |       |      |                                                                                |

| Input Clock Range                      | <b>f</b> <sub>SYNC</sub>   | 1.000 |        | 2.600 | MHz  |                                                                                |

| Input Clock Minimum On Pulse Width     | t <sub>sync_min_on</sub>   | 100   |        |       | ns   |                                                                                |

| Input Clock Minimum Off Pulse Width    | t <sub>SYNC_MIN_OFF</sub>  | 100   |        |       | ns   |                                                                                |

| Input Clock High Logic                 | V <sub>H (SYNC)</sub>      |       |        | 1.3   | V    |                                                                                |

| Input Clock Low Logic                  | V <sub>L (SYNC)</sub>      | 0.4   |        |       | V    |                                                                                |

| PRECISION ENABLING (EN1, EN2)          |                            |       |        |       |      |                                                                                |

| High Level Threshold                   | V <sub>TH_H</sub>          | 1.125 | 1.15   | 1.175 | V    |                                                                                |

| Low Level Threshold                    | V <sub>TH_L</sub>          | 1.025 | 1.05   | 1.075 | V    |                                                                                |

| Shutdown Mode                          | V <sub>TH_S</sub>          | 0.4   |        |       | V    | Internal circuitry disabled to achieve ISHDN                                   |

| Pull-Down Resistance                   | R <sub>EN</sub>            |       | 1.48   |       | MΩ   |                                                                                |

| INTERNAL REGULATOR                     |                            |       |        |       |      |                                                                                |

| VREG Output Voltage                    | V <sub>REG</sub>           |       | 4.25   |       | V    |                                                                                |

| BOOST REGULATOR                        |                            |       |        |       |      |                                                                                |

| Feedback Voltage                       | V <sub>FB1</sub>           |       | 0.8    |       | V    |                                                                                |

| Feedback Voltage Accuracy              |                            | -0.5  |        | +0.5  | %    | $T_J = 25^{\circ}C$                                                            |

|                                        |                            | -1.5  |        | +1.5  | %    | $T_{J} = -40^{\circ}C \text{ to } +125^{\circ}C$                               |

| Feedback Bias Current                  | I <sub>FB1</sub>           |       |        | 0.1   | μΑ   |                                                                                |

| Overvoltage Protection Threshold       | V <sub>OV1</sub>           |       | 0.86   |       | V    | At FB1 pin                                                                     |

| Load Regulation                        | $\Delta V_{FB1}/I_{LOAD1}$ |       | 0.0003 |       | %/mA | $I_{LOAD1}^{1} = 5 \text{ mA to } 150 \text{ mA}$                              |

| Line Regulation                        | $\Delta V_{FB1}/V_{PVIN1}$ |       | 0.002  |       | %/V  | V <sub>PVIN1</sub> = 2.85 V to 14.5 V, I <sub>LOAD1</sub> <sup>1</sup> = 50 mA |

| Error Amplifier (EA) Transconductance  | <b>9</b> м1                | 270   | 300    | 330   | μA/V |                                                                                |

| Power FET On Resistance                | R <sub>DS</sub> (ON) BOOST |       | 175    |       | mΩ   |                                                                                |

| Power FET Maximum Drain Source Voltage | Vds (max) boost            |       | 39     |       | V    |                                                                                |

| Input Disconnect Switch On Resistance  | Rds (ON) INBK              |       | 210    |       | mΩ   |                                                                                |

| Current-Limit Threshold                | ILIM (BOOST)               | 2.0   | 2.2    | 2.4   | А    |                                                                                |

| Minimum On Time                        |                            |       | 50     |       | ns   |                                                                                |

| Minimum Off Time                       |                            |       | 25     |       | ns   |                                                                                |

| Parameter                                              | Symbol                                                           | Min  | Тур               | Max  | Unit | <b>Test Conditions/Comments</b>                                                |

|--------------------------------------------------------|------------------------------------------------------------------|------|-------------------|------|------|--------------------------------------------------------------------------------|

| INVERTING REGULATOR                                    |                                                                  |      |                   |      |      |                                                                                |

| Reference Voltage                                      | VREF                                                             |      | 1.60              |      | V    |                                                                                |

| Reference Voltage Accuracy                             |                                                                  | -0.5 |                   | +0.5 | %    | T」 = 25°C                                                                      |

|                                                        |                                                                  | -1.5 |                   | +1.5 | %    | $T_{J} = -40^{\circ}C \text{ to } +125^{\circ}C$                               |

| Feedback Voltage                                       | $V_{\text{REF}}-V_{\text{FB2}}$                                  |      | 0.8               |      | V    |                                                                                |

| Feedback Voltage Accuracy                              |                                                                  | -0.5 |                   | +0.5 | %    | T」 = 25°C                                                                      |

|                                                        |                                                                  | -1.5 |                   | +1.5 | %    | $T_{J} = -40^{\circ}C \text{ to } +125^{\circ}C$                               |

| Feedback Bias Current                                  | I <sub>FB2</sub>                                                 |      |                   | 0.1  | μA   |                                                                                |

| Overvoltage Protection Threshold                       | V <sub>OV2</sub>                                                 |      | 0.74              |      | V    | At FB2 pin after soft start has<br>completed                                   |

| Load Regulation                                        | $\frac{\Delta(V_{\text{REF}}-V_{\text{FB2}})}{I_{\text{LOAD2}}}$ |      | 0.0004            |      | %/mA | $I_{LOAD2}^1 = 5 \text{ mA to } 75 \text{ mA}$                                 |

| Line Regulation                                        | $\Delta (V_{REF} - V_{FB2})/V_{PVIN2}$                           |      | 0.003             |      | %/V  | V <sub>PVIN2</sub> = 2.85 V to 14.5 V, I <sub>LOAD2</sub> <sup>1</sup> = 25 mA |

| EA Transconductance                                    | <b>9</b> м2                                                      | 270  | 300               | 330  | μA/V |                                                                                |

| Power FET On Resistance                                | Rds (ON) INVERTER                                                |      | 350               |      | mΩ   |                                                                                |

| Power FET Maximum Drain Source Voltage                 | V <sub>DS (MAX)</sub> INVERTER                                   |      | 39                |      | V    |                                                                                |

| Current-Limit Threshold                                | ILIM (INVERTER)                                                  | 1200 | 1320              | 1440 | mA   |                                                                                |

| Minimum On Time                                        |                                                                  |      | 60                |      | ns   |                                                                                |

| Minimum Off Time                                       |                                                                  |      | 50                |      | ns   |                                                                                |

| SOFT START                                             |                                                                  |      |                   |      |      |                                                                                |

| Soft Start Timer for Boost and Inverting<br>Regulators | tss                                                              |      | 4                 |      | ms   | SS = open                                                                      |

|                                                        |                                                                  |      | 32                |      | ms   | SS resistor = 50 k $\Omega$ to GND                                             |

| Hiccup Time                                            | <b>t</b> HICCUP                                                  |      | $8 \times t_{ss}$ |      | ms   |                                                                                |

| THERMAL SHUTDOWN                                       |                                                                  |      |                   |      |      |                                                                                |

| Threshold                                              | T <sub>SHDN</sub>                                                |      | 150               |      | °C   |                                                                                |

| Hysteresis                                             | T <sub>HYS</sub>                                                 |      | 15                |      | °C   |                                                                                |

<sup>1</sup> I<sub>LOADx</sub> is the current through a resistive load connected across the output capacitor (where x is 1 for the boost regulator load and 2 for the inverting regulator load).

### **ABSOLUTE MAXIMUM RATINGS**

#### Table 3.

| 10010 01                      |                               |

|-------------------------------|-------------------------------|

| Parameter                     | Rating                        |

| PVIN1, PVIN2, PVINSYS         | –0.3 V to +18 V               |

| INBK                          | –0.3 V to PVIN1 + 0.3 V       |

| SW1                           | –0.3 V to +40 V               |

| SW2                           | PVIN2 - 40 V to PVIN2 + 0.3 V |

| PGND, AGND                    | –0.3 V to +0.3 V              |

| VREG                          | –0.3 V to lower of PVINSYS +  |

|                               | 0.3 V or +6 V                 |

| EN1, EN2, FB1, FB2, SYNC/FREQ | –0.3 V to +6 V                |

| COMP1, COMP2, SLEW, SS,       | –0.3 V to VREG + 0.3 V        |

| SEQ, VREF                     |                               |

| Operating Junction            | -40°C to +125°C               |

| Temperature Range             |                               |

| Storage Temperature Range     | –65°C to +150°C               |

| Soldering Conditions          | JEDEC J-STD-020               |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### THERMAL RESISTANCE

$\begin{array}{l} \theta_{JA} \mbox{ and } \Psi_{JT} \mbox{ are based on a 4-layer printed circuit board (PCB)} \\ (two signal and two power planes) with nine thermal vias connecting the exposed pad to the ground plane as recommended in the Layout Considerations section. \\ \theta_{JC} \mbox{ is measured at the top} \\ of the package and is independent of the PCB. The \Psi_{JT} value is more appropriate for calculating junction to case temperature in the application. \end{array}$

#### Table 4. Thermal Resistance

| Package Type  | θ」Α  | οıc  | Ψл   | Unit |

|---------------|------|------|------|------|

| 20-Lead LFCSP | 60.2 | 36.5 | 0.63 | °C/W |

| 20-Lead TSSOP | 58.5 | 35.0 | 0.60 | °C/W |

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.** Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

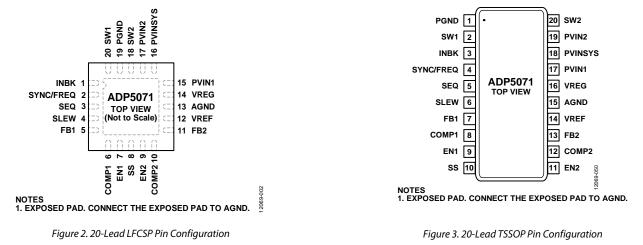

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

#### Table 5. Pin Function Descriptions

| Pin No. |       |           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LFCSP   | TSSOP | Mnemonic  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1       | 3     | INBK      | Input Disconnect Switch Output for the Boost Regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2       | 4     | SYNC/FREQ | Frequency Setting and Synchronization Input. To set the switching frequency to 2.4 MHz, pull the SYNC/FREQ pin high. To set the switching frequency to 1.2 MHz, pull the SYNC/FREQ pin low. To synchronize the switching frequency, connect the SYNC/FREQ pin to an external clock.                                                                                                                                                                                                                                      |

| 3       | 5     | SEQ       | Start-Up Sequence Control. For manual V <sub>POS</sub> /V <sub>NEG</sub> startup using an individual precision enabling pin, leave the SEQ pin open. For simultaneous V <sub>POS</sub> /V <sub>NEG</sub> startup when the EN2 pin rises, connect the SEQ pin to VREG (the EN1 pin can be used to enable the internal references early, if required). For a sequenced startup, pull the SEQ pin low. Either EN1 or EN2 can be used, and the corresponding supply is the first in sequence; hold the other enable pin low. |

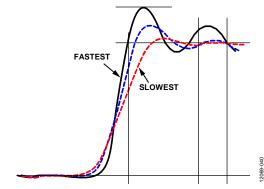

| 4       | 6     | SLEW      | Driver Stage Slew Rate Control. The SLEW pin sets the slew rate for the SW1 and SW2 drivers. For the fastest slew rate (best efficiency), leave the SLEW pin open. For normal slew rate, connect the SLEW pin to VREG. For the slowest slew rate (best noise performance), connect the SLEW pin to AGND.                                                                                                                                                                                                                 |

| 5       | 7     | FB1       | Feedback Input for the Boost Regulator. Connect a resistor divider between the positive side of the boost regulator output capacitor and AGND to program the output voltage.                                                                                                                                                                                                                                                                                                                                             |

| 6       | 8     | COMP1     | Error Amplifier Compensation for the Boost Regulator. Connect the compensation network between this pin and AGND.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 7       | 9     | EN1       | Boost Regulator Precision Enable. The EN1 pin is compared to an internal precision reference to enable the boost regulator output.                                                                                                                                                                                                                                                                                                                                                                                       |

| 8       | 10    | SS        | Soft Start Programming. Leave the SS pin open to obtain the fastest soft start time. To program a slower soft start time, connect a resistor between the SS pin and AGND.                                                                                                                                                                                                                                                                                                                                                |

| 9       | 11    | EN2       | Inverting Regulator Precision Enable. The EN2 pin is compared to an internal precision reference to enable the inverting regulator output.                                                                                                                                                                                                                                                                                                                                                                               |

| 10      | 12    | COMP2     | Error Amplifier Compensation for the Inverting Regulator. Connect the compensation network between this pin and AGND.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11      | 13    | FB2       | Feedback Input for the Inverting Regulator. Connect a resistor divider between the negative side of the inverting regulator output capacitor and VREF to program the output voltage.                                                                                                                                                                                                                                                                                                                                     |

| 12      | 14    | VREF      | Inverting Regulator Reference Output. Connect a 1.0 $\mu F$ ceramic filter capacitor between the VREF pin and AGND.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 13      | 15    | AGND      | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 14      | 16    | VREG      | Internal Regulator Output. Connect a 1.0 µF ceramic filter capacitor between the VREG pin and AGND.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 15      | 17    | PVIN1     | Power Input for the Boost Regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16      | 18    | PVINSYS   | System Power Supply for the ADP5071.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17      | 19    | PVIN2     | Power Input for the Inverting Regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# **Data Sheet**

| Pin No. |       |          |                                                      |  |

|---------|-------|----------|------------------------------------------------------|--|

| LFCSP   | TSSOP | Mnemonic | Description                                          |  |

| 18      | 20    | SW2      | Switching Node for the Inverting Regulator.          |  |

| 19      | 1     | PGND     | Power Ground for the Boost and Inverting Regulators. |  |

| 20      | 2     | SW1      | Switching Node for the Boost Regulator.              |  |

|         |       | EPAD     | Exposed Pad. Connect the exposed pad to AGND.        |  |

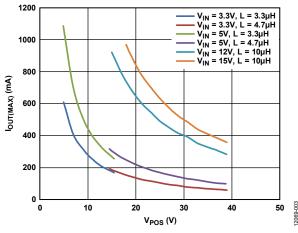

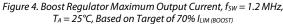

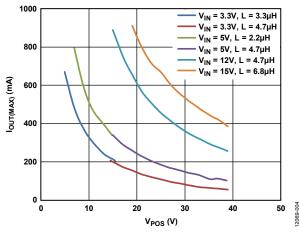

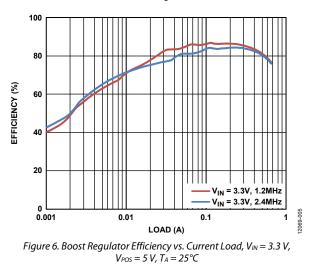

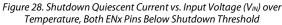

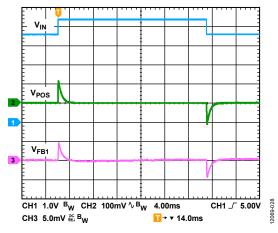

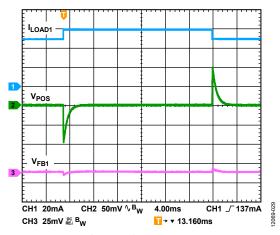

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Typical performance characteristics are generated using the standard bill of materials for each input/output combination listed in Table 9, Table 10, and Table 11.

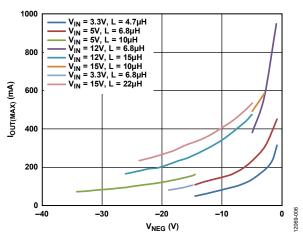

Figure 5. Boost Regulator Maximum Output Current,  $f_{SW} = 2.4$  MHz,  $T_A = 25^{\circ}$ C, Based on Target of 70%  $I_{LIM(BOOST)}$

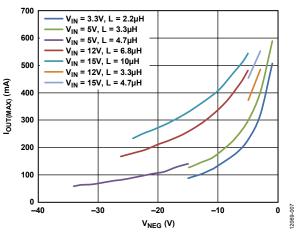

Figure 7. Inverting Regulator Maximum Output Current,  $f_{SW} = 1.2$  MHz,  $T_A = 25^{\circ}$ C, Based on Target of 70%  $I_{LIM}$  (INVERTER)

Figure 8. Inverting Regulator Maximum Output Current,  $f_{SW} = 2.4$  MHz,  $T_A = 25^{\circ}$ C, Based on Target of 70%  $I_{LIM}$  (INVERTER)

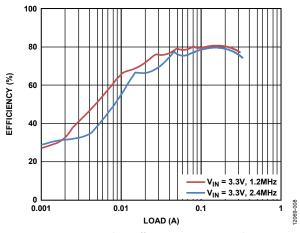

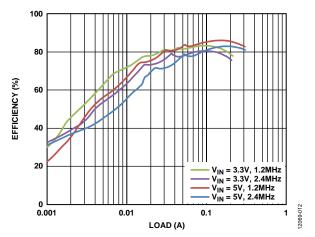

Figure 9. Inverting Regulator Efficiency vs. Current Load,  $V_{IN} = 3.3 V$ ,  $V_{NEG} = -5 V$ ,  $T_A = 25^{\circ}C$

Rev. E | Page 8 of 27

### **Data Sheet**

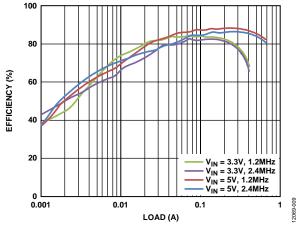

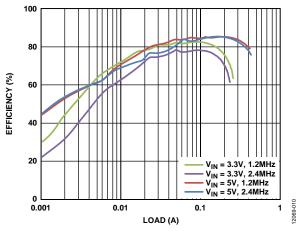

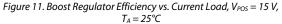

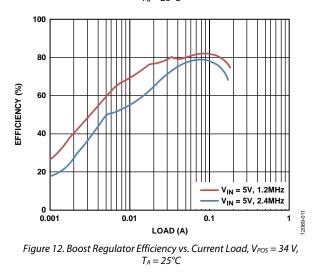

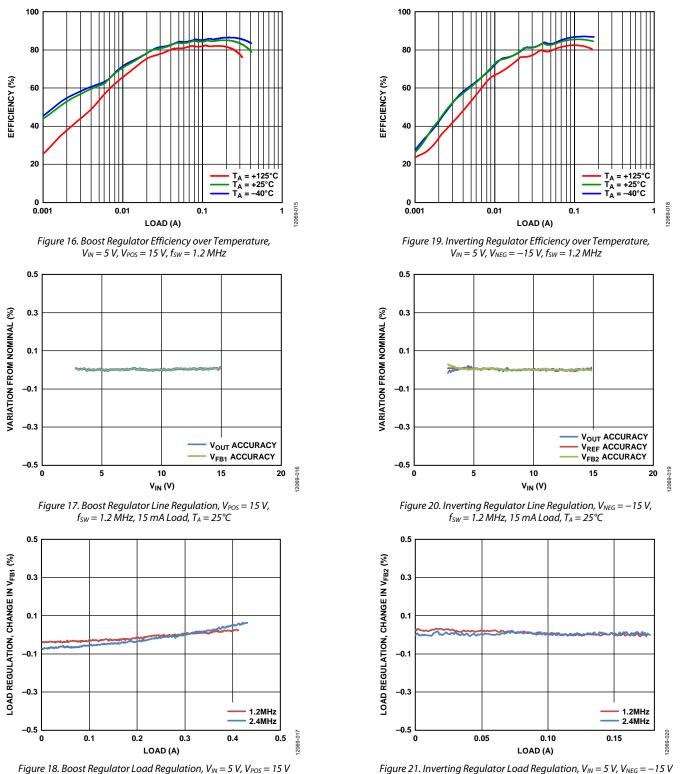

Figure 10. Boost Regulator Efficiency vs. Current Load,  $V_{POS} = 9 V$ ,  $T_A = 25 ^{\circ}C$

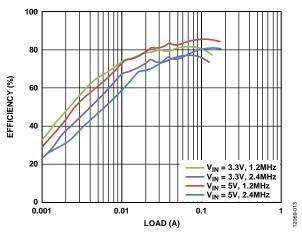

Figure 13. Inverting Regulator Efficiency vs. Current Load,  $V_{\text{NEG}} = -9$  V,  $T_A = 25\,^\circ\text{C}$

Figure 14. Inverting Regulator Efficiency vs. Current Load,  $V_{\text{NEG}} = -15 V$ ,  $T_A = 25^{\circ}\text{C}$

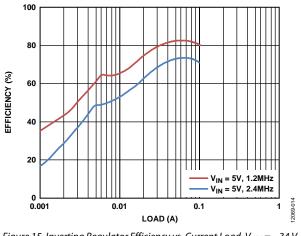

Figure 15. Inverting Regulator Efficiency vs. Current Load,  $V_{\text{NEG}} = -34$  V,  $T_A = 25^{\circ}\text{C}$

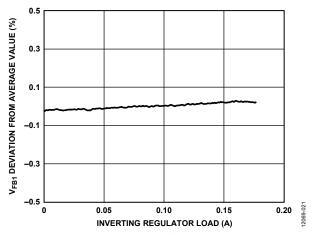

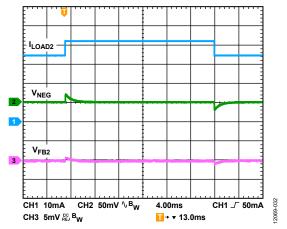

Figure 21. Inverting Regulator Load Regulation,  $V_{IN} = 5 V$ ,  $V_{NEG} = -15 V$

### **Data Sheet**

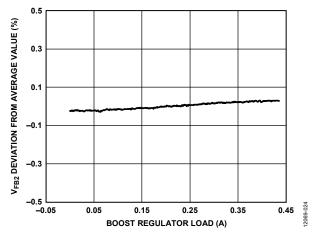

Figure 22. Cross Regulation, Boost Regulator  $V_{FB1}$  Regulation over Inverting Regulator Current Load,  $V_{IN} = 5 V$ ,  $V_{POS} = 15 V$ ,  $V_{NEG} = -15 V$ ,  $f_{SW} = 2.4 \text{ MHz}$ ,  $T_A = 25^{\circ}$ C, Boost Regulator Run in Continuous Conduction Mode with Fixed Load for Test

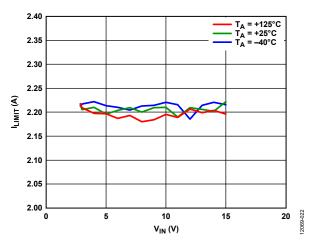

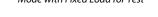

Figure 23. Boost Regulator Current Limit (ILIMIT) vs. Input Voltage (VIN) over Temperature

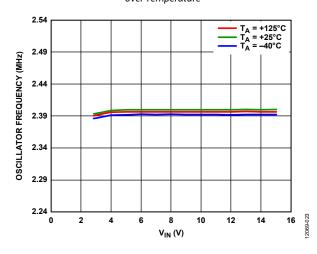

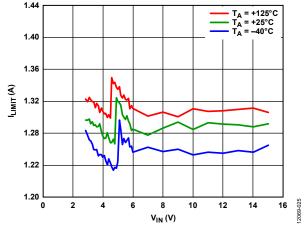

Figure 24. Oscillator Frequency vs. Input Voltage ( $V_{IN}$ ) over Temperature, SYNC/FREQ Pin = High

Figure 25. Cross Regulation, Inverting Regulator  $V_{FB2}$  Regulation over Boost Regulator Current Load,  $V_{IN} = 5 V$ ,  $V_{POS} = 15 V$ ,  $V_{NEG} = -15 V$ ,  $f_{SW} = 2.4 \text{ MHz}$ ,  $T_A = 25^{\circ}$ C, Inverting Regulator Run in Continuous Conduction Mode with Fixed Load for Test

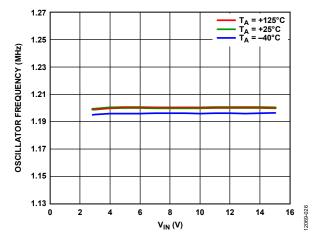

Figure 26. Inverting Regulator Current Limit (ILIMIT) vs. Input Voltage (VIN) over Temperature

Figure 27. Oscillator Frequency vs. Input Voltage ( $V_{IN}$ ) over Temperature, SYNC/FREQ Pin = Low

Figure 29. Boost Regulator Line Transient,  $V_{IN} = 4.5$  V to 5.5 V Step,  $V_{POS} = 15$  V,  $R_{LOAD1} = 300 \Omega$ ,  $f_{SW} = 2.4$  MHz,  $T_A = 25^{\circ}$ C

Figure 30. Boost Regulator Load Transient,  $V_{IN} = 5 V$  Step,  $V_{POS} = 15 V$ ,  $I_{LOAD1} = 120 \text{ mA to } 150 \text{ mA Step}$ ,  $f_{SW} = 2.4 \text{ MHz}$ ,  $T_A = 25^{\circ}\text{C}$

Figure 31. Operating Quiescent Current vs. Input Voltage (V<sub>IN</sub>) over Temperature, Both ENx Pins On

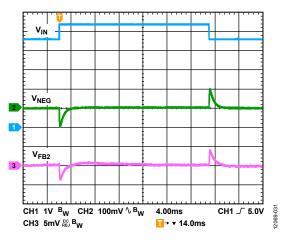

Figure 32. Inverting Regulator Line Transient,  $V_{IN} = 4.5$  V to 5.5 V Step,  $V_{NEG} = -15$  V,  $R_{LOAD2} = 300 \Omega$ ,  $f_{SW} = 2.4$  MHz,  $T_A = 25^{\circ}$ C

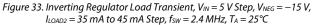

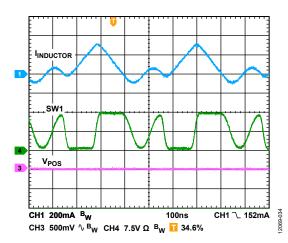

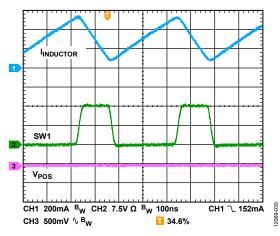

Figure 34. Boost Regulator Skip Mode Operation Showing Inductor Current ( $I_{INDUCTOR}$ ), Switch Node Voltage, and Output Ripple,  $V_{IN} = 12 V$ ,  $V_{POS} = 15 V$ ,  $I_{LOAD1} = 4 mA$ ,  $f_{SW} = 2.4 MHz$ ,  $T_A = 25^{\circ}C$

Figure 35. Boost Regulator Discontinuous Conduction Mode Operation Showing Inductor Current ( $I_{INDUCTOR}$ ), Switch Node Voltage, and Output Ripple,  $V_{IN} = 5 V$ ,  $V_{POS} = 15 V$ ,  $I_{LOAD1} = 20 \text{ mA}$ ,  $f_{SW} = 2.4 \text{ MHz}$ ,  $T_A = 25^{\circ}\text{C}$

Figure 36. Boost Regulator Continuous Conduction Mode Operation Showing Inductor Current ( $I_{INDUCTOR}$ ), Switch Node Voltage, and Output Ripple,  $V_{IN} = 5 V$ ,  $V_{POS} = 15 V$ ,  $I_{LOAD1} = 90 \text{ mA}$ ,  $f_{SW} = 2.4 \text{ MHz}$ ,  $T_A = 25^{\circ}\text{C}$

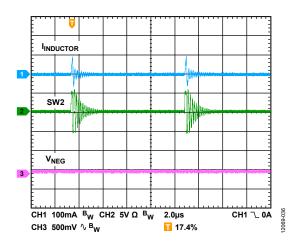

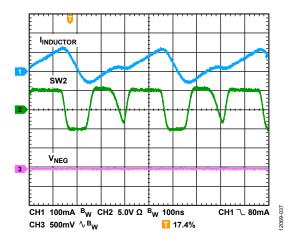

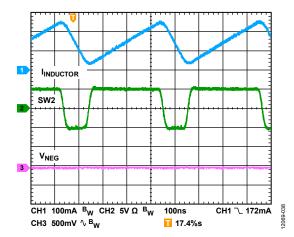

Figure 37. Inverting Regulator Skip Mode Operation Showing Inductor Current ( $I_{INDUCTOR}$ ), Switch Node Voltage, and Output Ripple,  $V_{IN} = 5 V$ ,  $V_{NEG} = -5 V$ ,  $I_{LOAD2} = 1 \text{ mA}$ ,  $f_{SW} = 2.4 \text{ MHz}$ ,  $T_A = 25^{\circ}\text{C}$

Figure 38. Inverting Regulator Discontinuous Conduction Mode Operation Showing Inductor Current ( $I_{INDUCTOR}$ ), Switch Node Voltage, and Output Ripple,  $V_{IN} = 5 V$ ,  $V_{NEG} = -5 V$ ,  $I_{LOAD2} = 6 \text{ mA}$ ,  $f_{SW} = 2.4 \text{ MHz}$ ,  $T_A = 25^{\circ}\text{C}$

Figure 39. Inverting Regulator Continuous Conduction Mode Operation Showing Inductor Current ( $I_{INDUCTOR}$ ), Switch Node Voltage, and Output Ripple,  $V_{IN} = 5$  V,  $V_{NEG} = -5$  V,  $I_{LOAD2} = 35$  mA,  $f_{SW} = 2.4$  MHz,  $T_A = 25$  °C

THEORY OF OPERATION

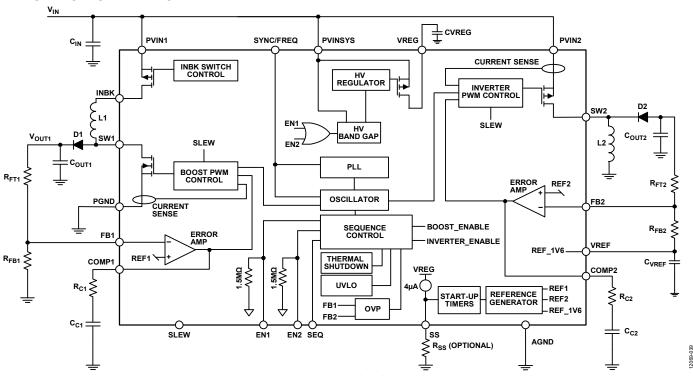

Figure 40. Functional Block Diagram

#### **PWM MODE**

The boost and inverting regulators in the ADP5071 operate at a fixed frequency set by an internal oscillator. At the start of each oscillator cycle, the MOSFET switch turns on, applying a positive voltage across the inductor. The inductor current increases until the current sense signal crosses the peak inductor current threshold that turns off the MOSFET switch; this threshold is set by the error amplifier output. During the MOSFET off time, the inductor current declines through the external diode until the next oscillator clock pulse starts a new cycle. It regulates the output voltage by adjusting the peak inductor current threshold.

#### **PSM MODE**

During light load operation, the regulators can skip pulses to maintain output voltage regulation. Skipping pulses increases the device efficiency.

#### **UNDERVOLTAGE LOCKOUT (UVLO)**

The undervoltage lockout circuitry monitors the PVINSYS pin voltage level. If the input voltage drops below the  $V_{UVLO\_FALLING}$  threshold, both regulators turn off. After the PVINSYS pin voltage rises above the  $V_{UVLO\_RISING}$  threshold, the soft start period initiates, and the regulators are enabled.

#### **OSCILLATOR AND SYNCHRONIZATION**

The ADP5071 initiates the drive of the boost regulator SW1 pin and the inverting regulator SW2 pin 180° out of phase to reduce peak current consumption and noise. A phase-locked loop (PLL)-based oscillator generates the internal clock and offers a choice of two internally generated frequency options or external clock synchronization. The switching frequency is configured using the SYNC/FREQ pin options shown in Table 6.

For external synchronization, connect the SYNC/FREQ pin to a suitable clock source. The PLL locks to an input clock within the range specified by  $f_{SYNC}$ .

#### Table 6. SYNC/FREQ Pin Options

| SYNC/FREQ Pin  | Switching Frequency               |

|----------------|-----------------------------------|

| High           | 2.4 MHz                           |

| Low            | 1.2 MHz                           |

| External Clock | $1 \times \text{clock frequency}$ |

#### **INTERNAL REGULATORS**

The internal VREG regulator in the ADP5071 provides a stable power supply for the internal circuitry. The VREG supply can be used to provide a logic high signal for device configuration pins but must not be used to supply external circuitry.

The VREF regulator provides a reference voltage for the inverting regulator feedback network to ensure a positive feedback voltage on the FB2 pin.

A current-limit circuit is included for both regulators to protect the circuit from accidental loading.

#### **PRECISION ENABLING**

The ADP5071 has an individual enable pin for the boost and inverting regulators: EN1 and EN2. The enable pins feature a precision enable circuit with an accurate reference voltage. This reference allows the ADP5071 to be sequenced easily from other supplies. It can also be used as a programmable UVLO input by using a resistor divider.

The enable pins have an internal pull-down resistor that defaults each regulator to off when the pin is floating.

When the voltage at the enable pins is greater than the  $V_{\rm TH\_H}$  reference level, the regulator is enabled.

#### SOFT START

Each regulator in the ADP5071 includes soft start circuitry that ramps the output voltage in a controlled manner during startup, thereby limiting the inrush current. The soft start time is internally set to the fastest rate when the SS pin is open.

Connecting a resistor between SS and AGND allows the adjustment of the soft start delay. The delay length is common to both regulators.

#### **SLEW RATE CONTROL**

The ADP5071 employs programmable output driver slew rate control circuitry. This circuitry reduces the slew rate of the switching node as shown in Figure 41, resulting in reduced ringing and lower EMI. To program the slew rate, connect the SLEW pin to the VREG pin for normal mode, to the AGND pin for slow mode, or leave it open for fast mode. This configuration allows the use of an open-drain output from a noise sensitive device to switch the slew rate from fast to slow, for example, during analog-to-digital converter (ADC) sampling.

Note that slew rate control causes a trade-off between efficiency and low EMI.

Figure 41. Switching Node at Various Slew Rate Settings

#### **CURRENT-LIMIT PROTECTION**

The boost and inverting regulators in the ADP5071 include current-limit protection circuitry to limit the amount of forward current through the MOSFET switch.

When the peak inductor current exceeds the overcurrent limit threshold for a number of clock cycles during an overload or short-circuit condition, the regulator enters hiccup mode. The regulator stops switching and then restarts with a new soft start cycle after  $t_{\rm HICCUP}$  and repeats until the overcurrent condition is removed.

#### **OVERVOLTAGE PROTECTION**

An overvoltage protection mechanism is present on the FB1 and FB2 pins for the boost and inverting regulators.

On the boost regulator, when the voltage on the FB1 pin exceeds the  $V_{\rm OV1}$  threshold, the switching on SW1 stops until the voltage falls below the threshold again. This functionality is permanently enabled on this regulator.

On the inverting regulator, when the voltage on the FB2 pin drops below the  $V_{OV2}$  threshold, the switching stops until the voltage rises above the threshold. This functionality is enabled after the soft start period has elapsed.

#### THERMAL SHUTDOWN

In the event that the ADP5071 junction temperature rises above  $T_{SHDN}$ , the thermal shutdown circuit turns off the IC. Extreme junction temperatures can be the result of prolonged high current operation, poor circuit board design, and/or high ambient temperature. Hysteresis is included so that when thermal shutdown occurs, the ADP5071 does not return to operation until the on-chip temperature drops below  $T_{SHDN}$  minus  $T_{HYS}$ . When resuming from thermal shutdown, a soft start is performed on each enabled channel.

#### **START-UP SEQUENCE**

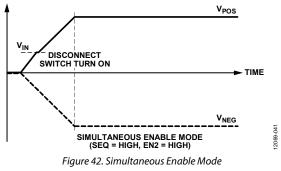

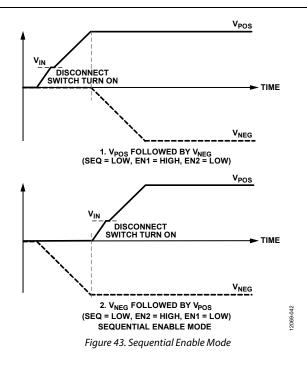

The ADP5071 implements a flexible start-up sequence to meet different system requirements. Three different enabling modes can be implemented via the SEQ pin, as explained in Table 7.

| Table 7. SEQ Pin Settings     |                        |  |  |  |

|-------------------------------|------------------------|--|--|--|

| SEQ Pin                       | EQ Pin Description     |  |  |  |

| Open                          | Manual enable mode     |  |  |  |

| VREG Simultaneous enable mode |                        |  |  |  |

| Low                           | Sequential enable mode |  |  |  |

To configure the manual enable mode, leave the SEQ pin open. The boost and inverting regulators are controlled separately from their respective precision enable pins.

To configure the simultaneous enable mode, connect the SEQ pin to the VREG pin. Both regulators power up simultaneously when the EN2 pin is taken high. The EN1 pin enable can be used to enable the internal references ahead of enabling the outputs, if desired. The simultaneous enable mode timing is shown in Figure 42.

To configure the sequential enable mode, pull the SEQ pin low. In this mode, either  $V_{POS}$  or  $V_{NEG}$  can be enabled first by using the respective EN1 pin or EN2 pin. Keep the other pin low. The secondary supply is enabled when the primary supply completes soft start and its feedback voltage reaches approximately 85% of the target value. The sequential enable mode timing is shown in Figure 43.

### APPLICATIONS INFORMATION ADIsimPOWER DESIGN TOOL

The ADP5071 is supported by the ADIsimPower design toolset. ADIsimPower is a collection of tools that produce complete power designs optimized to a specific design goal. These tools allow the user to generate a full schematic, bill of materials, and calculate performance in minutes. ADIsimPower can optimize designs for cost, area, efficiency, and parts count while taking into consideration the operating conditions and limitations of the IC and all real external components. The ADIsimPower tool can be found at www.analog.com/adisimpower, and the user can request an unpopulated board through the tool.

#### **COMPONENT SELECTION**

#### Feedback Resistors

The ADP5071 provides an adjustable output voltage for both boost and inverting regulators. An external resistor divider sets the output voltage where the divider output must equal the appropriate feedback reference voltage,  $V_{FB1}$  or  $V_{FB2}$ . To limit the output voltage accuracy degradation due to feedback bias current, ensure that the current through the divider is at least 10 times  $I_{FB1}$  or  $I_{FB2}$ . Set the positive output for the boost regulator by

$$V_{POS} = V_{FBI} \times \left(1 + \frac{R_{FTI}}{R_{FBI}}\right)$$

where:

$V_{POS}$  is the positive output voltage.  $V_{FB1}$  is the FB1 reference voltage.  $R_{FT1}$  is the feedback resistor from  $V_{POS}$  to FB1.  $R_{FB1}$  is the feedback resistor from FB1 to AGND.

Set the negative output for the inverting regulator by

$$V_{NEG} = V_{FB2} - \frac{R_{FT2}}{R_{FB2}} \left( V_{REF} - V_{FB2} \right)$$

where:

$V_{NEG}$  is the negative output voltage.  $V_{FB2}$  is the FB2 reference voltage.  $R_{FT2}$  is the feedback resistor from  $V_{NEG}$  to FB2.  $R_{FB2}$  is the feedback resistor from FB2 to VREF.  $V_{REF}$  is the VREF pin reference voltage.

|                               |                       | Boost/SEPI            | C Regulator                      |                       | Inverting Regulator   |                                  |  |  |

|-------------------------------|-----------------------|-----------------------|----------------------------------|-----------------------|-----------------------|----------------------------------|--|--|

| Desired Output<br>Voltage (V) | R <sub>FT1</sub> (ΜΩ) | R <sub>FB1</sub> (kΩ) | Calculated<br>Output Voltage (V) | R <sub>FT2</sub> (ΜΩ) | R <sub>FB2</sub> (kΩ) | Calculated<br>Output Voltage (V) |  |  |

| ±1.8                          | 0.143                 | 115                   | 1.795                            | 0.332                 | 102                   | -1.804                           |  |  |

| ±3                            | 0.316                 | 115                   | 2.998                            | 0.475                 | 100                   | -3.000                           |  |  |

| ±3.3                          | 0.357                 | 115                   | 3.283                            | 0.523                 | 102                   | -3.302                           |  |  |

| ±4.2                          | 0.432                 | 102                   | 4.188                            | 0.715                 | 115                   | -4.174                           |  |  |

| ±5                            | 0.604                 | 115                   | 5.002                            | 1.15                  | 158                   | -5.023                           |  |  |

| ±9                            | 1.24                  | 121                   | 8.998                            | 1.62                  | 133                   | -8.944                           |  |  |

| ±12                           | 1.4                   | 100                   | 12.000                           | 1.15                  | 71.5                  | -12.067                          |  |  |

| ±13                           | 2.1                   | 137                   | 13.063                           | 2.8                   | 162                   | -13.027                          |  |  |

| ±15                           | 2.43                  | 137                   | 14.990                           | 2.32                  | 118                   | -14.929                          |  |  |

| ±18                           | 2.15                  | 100                   | 18.000                           | 2.67                  | 113                   | -18.103                          |  |  |

| ±20                           | 2.55                  | 107                   | 19.865                           | 2.94                  | 113                   | -20.014                          |  |  |

| ±24                           | 3.09                  | 107                   | 23.903                           | 3.16                  | 102                   | -23.984                          |  |  |

| ±30                           | 3.65                  | 100                   | 30.000                           | 4.12                  | 107                   | -30.004                          |  |  |

| ±35                           | 5.9                   | 137                   | 35.253                           | 5.11                  | 115                   | -34.748                          |  |  |

#### Table 8. Recommended Feedback Resistor Values

#### **Output Capacitors**

Higher output capacitor values reduce the output voltage ripple and improve load transient response. When choosing this value, it is also important to account for the loss of capacitance due to the output voltage dc bias.

Ceramic capacitors are manufactured with a variety of dielectrics, each with a different behavior over temperature and applied voltage. Capacitors must have a dielectric adequate to ensure the minimum capacitance over the necessary temperature range and dc bias conditions. X5R or X7R dielectrics with a voltage rating of 25 V or 50 V (depending on output) are recommended for best performance. Y5V and Z5U dielectrics are not recommended for use with any dc-to-dc converter because of their poor temperature and dc bias characteristics.

Calculate the worst-case capacitance accounting for capacitor variation over temperature, component tolerance, and voltage using the following equation:

$C_{EFFECTIVE} = C_{NOMINAL} \times (1 - TEMPCO) \times (1 - DCBIASCO) \times (1 - Tolerance)$

where:

$C_{EFFECTIVE}$  is the effective capacitance at the operating voltage. *C*<sub>NOMINAL</sub> is the nominal data sheet capacitance.

*TEMPCO* is the worst-case capacitor temperature coefficient. *DCBIASCO* is the dc bias derating at the output voltage. *Tolerance* is the worst-case component tolerance.

To guarantee the performance of the device, it is imperative that the effects of dc bias, temperature, and tolerances on the behavior of the capacitors be evaluated for each application.

Capacitors with lower effective series resistance (ESR) and effective series inductance (ESL) are preferred to minimize output voltage ripple.

Note that the use of large output capacitors can require a slower soft start to prevent current limit during startup. A 10  $\mu F$  capacitor is suggested as a good balance between performance and size.

#### Input Capacitor

Higher value input capacitors help to reduce the input voltage ripple and improve transient response.

To minimize supply noise, place the input capacitor as close as possible to the PVINSYS pin, PVIN1 pin, and PVIN2 pin. A low ESR capacitor is recommended.

The effective capacitance needed for stability is a minimum of  $10 \,\mu\text{F}$ . If the power pins are individually decoupled, it is recommended to use an effective minimum of a 5.6  $\mu\text{F}$  capacitor on the PVIN1 and PVIN2 pins and a 3.3  $\mu\text{F}$  capacitor on the PVINSYS pin. The minimum values specified exclude dc bias, temperature, and tolerance effects that are application dependent and must be taken into consideration.

#### **VREG** Capacitor

A 1.0  $\mu F$  ceramic capacitor (C\_{VREG}) is required between the VREG pin and AGND.

#### **VREF** Capacitor

A 1.0  $\mu F$  ceramic capacitor (C\_{VREF}) is required between the VREF pin and AGND.

#### Soft Start Resistor

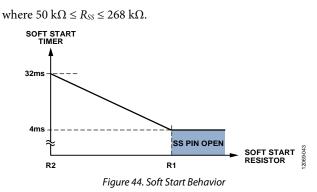

A resistor can be connected between the SS pin and the AGND pin to increase the soft start time. The soft start time can be set by the resistor between 4 ms (268 k $\Omega$ ) and 32 ms (50 k $\Omega$ ). Leaving the SS pin open selects the fastest time of 4 ms. Figure 44 shows the behavior of this operation. Calculate the soft start time using the following formula:

$$t_{SS} = 38.4 \times 10^{-3} - 1.28 \times 10^{-7} \times R_{SS} (\Omega)$$

#### Diodes

A Schottky diode with low junction capacitance is recommended for D1 and D2. At higher output voltages and especially at higher switching frequencies, the junction capacitance is a significant contributor to efficiency. Higher capacitance diodes also generate more switching noise. As a guide, a diode with less than 40 pF junction capacitance is preferred when the output voltage is above 5 V.

#### Inductor Selection for the Boost Regulator

The inductor stores energy during the on time of the power switch, and transfers that energy to the output through the output rectifier during the off time. To balance the tradeoffs between small inductor current ripple and efficiency, inductance values in the range of 1  $\mu$ H to 22  $\mu$ H are recommended. In general, lower inductance values have higher saturation current and lower series resistance for a given physical size. However, lower inductance results in a higher peak current that can lead to reduced efficiency and greater input and/or output ripple and noise. A peak-to-peak inductor ripple current close to 30% of the maximum dc input current for the application typically yields an optimal compromise.

For the inductor ripple current in continuous conduction mode (CCM) operation, the input ( $V_{IN}$ ) and output ( $V_{POS}$ ) voltages determine the switch duty cycle (DUTY<sub>1</sub>) by the following equation:

$$DUTY_{l} = \left(\frac{V_{POS} - V_{IN} + V_{DIODEl}}{V_{POS} + V_{DIODEl}}\right)$$

where  $V_{DIODE1}$  is the forward voltage drop of the Schottky diode (D1).

The dc input current in CCM ( $I_{\rm IN})$  can be determined by the following equation:

$$I_{IN} = \frac{I_{OUT1}}{(1 - DUTY_1)}$$

Using the duty cycle  $(DUTY_1)$  and switching frequency  $(f_{SW})$ , determine the on time  $(t_{ON1})$  using the following equation:

$$t_{ON1} = \frac{DUTY_1}{f_{SW}}$$

The inductor ripple current ( $\Delta I_{L1}$ ) in steady state is calculated by

$$\Delta I_{LI} = \frac{V_{IN} \times t_{ONI}}{LI}$$

Solve for the inductance value (L1) using the following equation:

$$Ll = \frac{V_{\rm IN} \times t_{\rm ONI}}{\Delta I_{\rm Ll}}$$

Assuming an inductor ripple current of 30% of the maximum dc input current results in

$$L1 = \frac{V_{IN} \times t_{ONI} \times (1 - DUTY_l)}{0.3 \times I_{OUT1}}$$

Ensure that the peak inductor current (the maximum input current plus half the inductor ripple current) is below the rated saturation current of the inductor. Likewise, ensure that the maximum rated rms current of the inductor is greater than the maximum dc input current to the regulator.

When the ADP5071 boost regulator is operated in CCM at duty cycles greater than 50%, slope compensation is required to stabilize the current mode loop. This slope compensation is built in to the ADP5071 For stable current mode operation, ensure that the selected inductance is equal to or greater than the minimum calculated inductance, L<sub>MIN1</sub>, for the application parameters in the following equation:

$$L1 > L_{MIN1} = V_{IN} \times \left(\frac{0.13}{(1 - DUTY_1)} - 0.16\right) (\mu H)$$

Table 10 suggests a series of inductors to use with the ADP5071 boost regulator.

#### Inductor Selection for the Inverting Regulator

The inductor stores energy during the on time of the power switch, and transfers that energy to the output through the output rectifier during the off time. To balance the tradeoffs between small inductor current ripple and efficiency, inductance values in the range of 1  $\mu$ H to 22  $\mu$ H are recommended. In general, lower inductance values have higher saturation current and lower series resistance for a given physical size. However, lower inductance results in a higher peak current that can lead to reduced efficiency and greater input and/or output ripple and noise. A peak-to-peak inductor ripple current close to 30% of the maximum dc current in the inductor typically yields an optimal compromise.

For the inductor ripple current in continuous conduction mode (CCM) operation, the input ( $V_{IN}$ ) and output ( $V_{NEG}$ ) voltages determine the switch duty cycle (DUTY<sub>2</sub>) by the following equation:

$$DUTY_{2} = \left(\frac{|V_{NEG}| + V_{DIODE2}}{|V_{IN} + |V_{NEG}| + |V_{DIODE2}|}\right)$$

where  $V_{DIODE2}$  is the forward voltage drop of the Schottky diode (D2).

The dc current in the inductor in CCM  $(I_{L2})$  can be determined by the following equation:

$$I_{L2} = \frac{I_{OUT2}}{(1 - DUTY_2)}$$

Using the duty cycle  $(DUTY_2)$  and switching frequency  $(f_{SW})$ , determine the on time  $(t_{ON2})$  by the following equation:

$$t_{\rm ON2} = \frac{DUTY_2}{f_{\rm SW}}$$

The inductor ripple current ( $\Delta I_{L2}$ ) in steady state is calculated by

$$\Delta I_{L2} = \frac{V_{IN} \times t_{ON2}}{L2}$$

Solve for the inductance value (L2) by the following equation:

$$L2 = \frac{V_{IN} \times t_{ON2}}{\Delta I_{L2}}$$

Assuming an inductor ripple current of 30% of the maximum dc current in the inductor results in

$$L2 = \frac{V_{IN} \times t_{ON2} \times (1 - DUTY_2)}{0.3 \times I_{OUT2}}$$

Ensure that the peak inductor current (the maximum input current plus half the inductor ripple current) is below the rated saturation current of the inductor. Likewise, ensure that the maximum rated rms current of the inductor is greater than the maximum dc input current to the regulator.

When the ADP5071 inverting regulator is operated in CCM at duty cycles greater than 50%, slope compensation is required to stabilize the current mode loop. For stable current mode operation, ensure that the selected inductance is equal to or greater than the minimum calculated inductance,  $L_{MIN2}$ , for the application parameters in the following equation:

$$L2 > L_{MIN2} = V_{IN} \times \left(\frac{0.13}{(1 - DUTY_2)} - 0.16\right) (\mu H)$$

Table 11 suggests a series of inductors to use with the ADP5071 inverting regulator.

#### LOOP COMPENSATION

The ADP5071 uses external components to compensate the regulator loop, allowing the optimization of the loop dynamics for a given application. It is recommended to use the ADIsimPower tool to calculate compensation components.

#### **Boost Regulator**

The boost converter produces an undesirable right half plane zero in the regulation feedback loop. This feedback loop requires compensating the regulator such that the crossover frequency occurs well below the frequency of the right half plane zero. The right half plane zero is determined by the following equation:

$$f_{Zl}(RHP) = \frac{R_{LOADI}(1 - DUTY_l)^2}{2\pi \times L1}$$

where:

$f_{Z1}(RHP)$  is the right half plane zero frequency.

$R_{LOAD1}$  is the equivalent load resistance or the output voltage divided by the load current.

$$DUTY_{l} = \left(\frac{V_{POS} - V_{IN} + V_{DIODEl}}{V_{POS} + V_{DIODEl}}\right)$$

where  $V_{DIODE1}$  is the forward voltage drop of the Schottky diode (D1).

To stabilize the regulator, ensure that the regulator crossover frequency is less than or equal to one-tenth of the right half plane zero frequency.

The boost regulator loop gain is

$$A_{VLI} = \frac{V_{FBI}}{V_{POS}} \times \frac{V_{IN}}{V_{POS}} \times G_{MI} \times \left| R_{OUTI} \right| \left| Z_{COMPI} \right| \times G_{CSI} \times \left| Z_{OUTI} \right|$$

where:

$A_{VL1}$  is the loop gain.

$V_{FB1}$  is the feedback regulation voltage

$V_{POS}$  is the regulated positive output voltage.

$V_{IN}$  is the input voltage.

$G_{M1}$  is the error amplifier transconductance gain.

$R_{OUT1}$  is the output impedance of the error amplifier and is 33 M $\Omega$ .  $Z_{COMP1}$  is the impedance of the series RC network from COMP1 to AGND.  $G_{CSI}$  is the current sense transconductance gain (the inductor current divided by the voltage at COMP1), which is internally set by the ADP5071and is 12.5 A/V.

$Z_{OUT1}$  is the impedance of the load in parallel with the output capacitor.

To determine the crossover frequency  $(f_{C1})$ , it is important to note that, at that frequency, the compensation impedance  $(Z_{COMP1})$ is dominated by a resistor  $(R_{C1})$ , and the output impedance  $(Z_{OUT1})$ is dominated by the impedance of an output capacitor  $(C_{OUT1})$ . Therefore, when solving for the crossover frequency, the equation (by definition of the crossover frequency) is simplified to

$$\begin{aligned} \left|A_{VLI}\right| &= \frac{V_{FBI}}{V_{POS}} \times \frac{V_{IN}}{V_{POS}} \times G_{MI} \times R_{CI} \times G_{CSI} \times \\ \frac{1}{2\pi \times f_{CI} \times C_{OUTI}} = 1 \end{aligned}$$

where  $f_{Cl}$  is the crossover frequency.

To solve for  $R_{C1}$ , use the following equation:

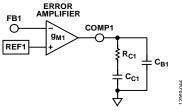

$$R_{CI} = \frac{2\pi \times f_{CI} \times C_{OUTI} \times (V_{POS})^2}{V_{FBI} \times V_{IN} \times G_{MI} \times G_{CSI}}$$

where  $G_{CS1} = 12.5$  A/V.

Using typical values for  $V_{FB1}$  and  $G_{M1}$  results in

$$R_{CI} = \frac{2094 \times f_{CI} \times C_{OUTI} \times (V_{POS})^2}{V_{IN}}$$

For better accuracy, it is recommended to use the value of output capacitance,  $C_{OUT1}$ , expected for the dc bias conditions under which it operates under in the calculation for  $R_{C1}$ .

After the compensation resistor is known, set the zero formed by the compensation capacitor and resistor to one-fourth of the crossover frequency, or

$$C_{CI} = \frac{2}{\pi \times f_{CI} \times R_{CI}}$$

where  $C_{Cl}$  is the compensation capacitor value.

Figure 45. Compensation Components

The capacitor,  $C_{B1}$ , is chosen to cancel the zero introduced by the output capacitor ESR. Solve for  $C_{B1}$  as follows:

$$C_{BI} = \frac{ESR \times C_{OUTI}}{R_{CI}}$$

For low ESR output capacitance such as with a ceramic capacitor,  $C_{B1}$  is optional. For optimal transient performance,  $R_{C1}$  and  $C_{C1}$  may need to be adjusted by observing the load transient response of the ADP5071. For most applications,  $R_{C1}$  must be within the range of 1 k $\Omega$  to 200 k $\Omega$ , and  $C_{C1}$  must be within the range of 1 nF to 68 nF.

#### **Inverting Regulator**

The inverting converter, like the boost converter, produces an undesirable right half plane zero in the regulation feedback loop. This feedback loop requires compensating the regulator such that the crossover frequency occurs well below the frequency of the right half plane zero. The right half plane zero frequency is determined by the following equation:

$$f_{Z2}(RHP) = \frac{R_{LOAD2}(1 - DUTY_2)^2}{2\pi \times L2 \times DUTY_2}$$

where:

$f_{Z2}(RHP)$  is the right half plane zero frequency.  $R_{LOAD2}$  is the equivalent load resistance or the output voltage divided by the load current.

$$DUTY_{2} = \left(\frac{|V_{NEG}| + V_{DIODE2}}{|V_{IN} + |V_{NEG}| + |V_{DIODE2}|}\right)$$

where  $V_{DIODE2}$  is the forward voltage drop of the Schottky diode (D2).

To stabilize the regulator, ensure that the regulator crossover frequency is less than or equal to one-tenth of the right half plane zero frequency.

The inverting regulator loop gain is

$$A_{VL2} = \frac{V_{FB2}}{|V_{NEG}|} \times \frac{V_{IN}}{(V_{IN} + 2 \times |V_{NEG}|)} \times G_{M2} \times$$

$$\left|R_{OUT2}\right|\left|Z_{COMP2}\right| \times G_{CS2} \times \left|Z_{OUT2}\right|$$

where:

$A_{VL2}$  is the loop gain.

$V_{FB2}$  is the feedback regulation voltage.

$V_{NEG}$  is the regulated negative output voltage.

$V_{IN}$  is the input voltage.

$G_{M2}$  is the error amplifier transconductance gain.

$R_{OUT2}$  is the output impedance of the error amplifier and is 33 M $\Omega$ .  $Z_{COMP2}$  is the impedance of the series RC network from COMP2 to AGND.

$G_{CS2}$  is the current sense transconductance gain (the inductor current divided by the voltage at COMP2), which is internally set by the ADP5071 and is 12.5 A/V.

$Z_{OUT2}$  is the impedance of the load in parallel with the output capacitor.

To determine the crossover frequency, it is important to note that, at that frequency, the compensation impedance ( $Z_{COMP2}$ ) is dominated by a resistor,  $R_{C2}$ , and the output impedance ( $Z_{OUT2}$ ) is dominated by the impedance of the output capacitor,  $C_{OUT2}$ . Therefore, when solving for the crossover frequency, the equation (by definition of the crossover frequency) is simplified to

$$\begin{aligned} \left|A_{VL2}\right| &= \frac{V_{FB2}}{\left|V_{NEG}\right|} \times \frac{V_{IN}}{\left(V_{IN} + 2 \times \left|V_{NEG}\right|\right)} \times G_{M2} \times \\ R_{C2} &\times G_{CS} 2 \times \frac{1}{2\pi \times f_{C2} \times C_{OUT2}} = 1 \end{aligned}$$

where  $f_{C2}$  is the crossover frequency.

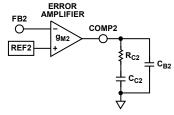

To solve for R<sub>C2</sub>, use the following equation:

$$R_{C2} = \frac{2\pi \times f_{C2} \times C_{OUT2} \times |V_{NEG}| \times (V_{IN} + (2 \times |V_{NEG}|))}{V_{FR2} \times V_{IN} \times G_{M2} \times G_{CS2}}$$

where  $G_{CS2} = 12.5 \text{ A/V}.$

Using typical values for  $V_{FB2}$  and  $G_{M2}$  results in

$$R_{C2} = \frac{2094 \times f_{C2} \times C_{OUT2} \times |V_{NEG}| \times (V_{IN} + (2 \times |V_{NEG}|))}{V_{IN}}$$

For better accuracy, it is recommended to use the value of output capacitance,  $C_{OUT2}$ , expected under the dc bias conditions that it operates under in the calculation for  $R_{C2}$ .

After the compensation resistor is known, set the zero formed by the  $C_{C2}$  and  $R_{C2}$  to one-fourth of the crossover frequency, or

$$C_{C2} = \frac{2}{\pi \times f_{C2} \times R_{C2}}$$

where  $C_{C2}$  is the compensation capacitor.

Figure 46. Compensation Component

The capacitor,  $C_{B2}$ , is chosen to cancel the zero introduced by output capacitance, ESR.

Solve for C<sub>B2</sub> as follows:

$$C_{B2} = \frac{ESR \times C_{OUT2}}{R_{C2}}$$

For low ESR output capacitance, such as with a ceramic capacitor,  $C_{B2}$  is optional. For optimal transient performance,  $R_{C2}$  and  $C_{C2}$  may need to be adjusted by observing the load transient response of the ADP5071. For most applications,  $R_{C2}$  must be within the range of 1 k $\Omega$  to 200 k $\Omega$ , and  $C_{C2}$  must be within the range of 1 nF to 68 nF.

#### **COMMON APPLICATIONS**

Table 9 through Table 11 list a number of common component selections for typical  $V_{\rm IN}$  and  $V_{\rm OUT}$  conditions. These have been bench tested and provide an off the shelf solution. Note that when pairing a boost and inverting regulator bill of materials, choose the same  $V_{\rm IN}$  and switching frequency. To optimize components for an application, it is recommend to use the ADIsimPower toolset.

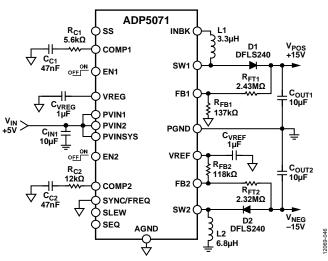

Figure 47 shows the schematic referenced by Table 9 through Table 11 with example component values for +5 V to  $\pm 15$  V generation. Table 9 shows the components common to all of the  $V_{\rm IN}$  and  $V_{\rm OUT}$  conditions.

**Table 9. Recommended Common Components Selections**

| REF               | Value | Part Number        | Manufacturer |

|-------------------|-------|--------------------|--------------|

| C <sub>IN1</sub>  | 10 µF | TMK316B7106KL-TD   | Taiyo Yuden  |

| $C_{\text{VREG}}$ | 1 μF  | GRM188R71A105KA61D | Murata       |

| CVREF             | 1 μF  | GRM188R71A105KA61D | Murata       |

Figure 47. Typical +5 V to  $\pm 15$  V Application

|            |                         |                |            | L1 Manufactur  | er Part Number      |                           |                    | D1,                  |                          |                          |                         |                         |

|------------|-------------------------|----------------|------------|----------------|---------------------|---------------------------|--------------------|----------------------|--------------------------|--------------------------|-------------------------|-------------------------|

| Vıℕ<br>(V) | V <sub>POS</sub><br>(V) | Freq.<br>(MHz) | L1<br>(μΗ) | Coilcraft®     | Wurth<br>Elektronik | C <sub>ουτ1</sub><br>(μF) | Coutt, Murata Part | Diodes,<br>Inc. Part | R <sub>FT1</sub><br>(ΜΩ) | R <sub>FB1</sub><br>(kΩ) | C <sub>C1</sub><br>(nF) | R <sub>C1</sub><br>(kΩ) |

| 3.3        | 5                       | 1.2            | 2.2        | XAL4020-222ME_ | 74438356022         | 10                        | GRM32ER71H106KA12L | DFLS240L             | 0.604                    | 115                      | 47                      | 4.7                     |

| 3.3        | 5                       | 2.4            | 1          | XAL4020-102ME_ | 74438356010         | 10                        | GRM32ER71H106KA12L | DFLS240L             | 0.604                    | 115                      | 47                      | 4.7                     |

| 3.3        | 9                       | 1.2            | 2.2        | XAL4020-222ME_ | 74438356022         | 10                        | GRM32ER71H106KA12L | DFLS240              | 1.24                     | 121                      | 47                      | 3.3                     |

| 3.3        | 9                       | 2.4            | 1.5        | XAL4020-152ME_ | 74438356015         | 10                        | GRM32ER71H106KA12L | DFLS240              | 1.24                     | 121                      | 47                      | 3.3                     |

| 3.3        | 15                      | 1.2            | 3.3        | XAL4030-332ME_ |                     | 10                        | GRM32ER71H106KA12L | DFLS240              | 2.43                     | 137                      | 47                      | 14                      |

| 3.3        | 15                      | 2.4            | 1.5        | XAL4020-152ME_ | 74438356015         | 10                        | GRM32ER71H106KA12L | DFLS240              | 2.43                     | 137                      | 47                      | 14                      |

| 3.3        | 24                      | 1.2            | 3.3        | XAL4030-332ME_ |                     | 10                        | GRM32ER71H106KA12L | DFLS240              | 3.09                     | 107                      | 47                      | 18                      |

| 3.3        | 24                      | 2.4            | 3.3        | XAL4030-332ME_ |                     | 10                        | GRM32ER71H106KA12L | DFLS240              | 3.09                     | 107                      | 47                      | 18                      |

| 3.3        | 34                      | 1.2            | 4.7        | XAL4030-472ME_ | 74438357047         | 10                        | GRM32ER71H106KA12L | DFLS240              | 4.22                     | 102                      | 47                      | 33                      |

| 3.3        | 34                      | 2.4            | 4.7        | XAL4030-472ME_ | 74438357047         | 10                        | GRM32ER71H106KA12L | DFLS240              | 4.22                     | 102                      | 47                      | 33                      |

| 5          | 9                       | 1.2            | 3.3        | XAL4030-332ME_ |                     | 10                        | GRM32ER71H106KA12L | DFLS240              | 1.24                     | 121                      | 47                      | 1.8                     |

| 5          | 9                       | 2.4            | 1.5        | XAL4020-152ME_ | 74438356015         | 10                        | GRM32ER71H106KA12L | DFLS240              | 1.24                     | 121                      | 47                      | 2.2                     |

| 5          | 15                      | 1.2            | 3.3        | XAL4030-332ME_ |                     | 10                        | GRM32ER71H106KA12L | DFLS240              | 2.43                     | 137                      | 47                      | 5.6                     |

| 5          | 15                      | 2.4            | 2.2        | XAL4020-222ME_ | 74438356022         | 10                        | GRM32ER71H106KA12L | DFLS240              | 2.43                     | 137                      | 47                      | 8.2                     |

| 5          | 24                      | 1.2            | 4.7        | XAL4030-472ME_ | 74438357047         | 10                        | GRM32ER71H106KA12L | DFLS240              | 3.09                     | 107                      | 47                      | 10                      |

| 5          | 24                      | 2.4            | 3.3        | XAL4030-332ME_ |                     | 10                        | GRM32ER71H106KA12L | DFLS240              | 3.09                     | 107                      | 47                      | 10                      |

| 5          | 34                      | 1.2            | 4.7        | XAL4030-472ME_ | 74438357047         | 10                        | GRM32ER71H106KA12L | DFLS240              | 4.22                     | 102                      | 47                      | 12                      |

| 5          | 34                      | 2.4            | 4.7        | XAL4030-472ME_ | 74438357047         | 10                        | GRM32ER71H106KA12L | DFLS240              | 4.22                     | 102                      | 47                      | 12                      |

| 12         | 24                      | 1.2            | 6.8        | XAL4030-682ME_ | 74438357068         | 10                        | GRM32ER71H106KA12L | DFLS240              | 3.09                     | 107                      | 47                      | 4.7                     |

| 12         | 24                      | 2.4            | 3.3        | XAL4030-332ME_ |                     | 10                        | GRM32ER71H106KA12L | DFLS240              | 3.09                     | 107                      | 47                      | 4.7                     |

#### Table 10. Recommended Boost Regulator Components

Table 11. Recommended Inverting Regulator Components

|     |      |       |      | L2, Manufacturer Part Number |             | L2, Manufacturer Part Number |                    |           | D2,              |                  |                 |                 |  |

|-----|------|-------|------|------------------------------|-------------|------------------------------|--------------------|-----------|------------------|------------------|-----------------|-----------------|--|

| VIN | VNEG | Freq. | L2   |                              | Wurth       | Cout2                        |                    | Diodes,   | R <sub>FT2</sub> | R <sub>FB2</sub> | C <sub>C2</sub> | R <sub>C2</sub> |  |

| (V) | (V)  | (MHz) | (µH) | Coilcraft                    | Elektronik  | (μF)                         | COUT2, Murata Part | Inc. Part | (MΩ)             | (kΩ)             | (nF)            | (kΩ)            |  |

| 3.3 | -5   | 1.2   | 3.3  | XAL4030-332ME_               |             | 10                           | GRM32ER71H106KA12L | DFLS240L  | 1.15             | 158              | 47              | 8.2             |  |

| 3.3 | -5   | 2.4   | 2.2  | XAL4020-222ME_               | 74438356022 | 10                           | GRM32ER71H106KA12L | DFLS240L  | 1.15             | 158              | 47              | 8.2             |  |

| 3.3 | -9   | 1.2   | 4.7  | XAL4030-472ME_               | 74438357047 | 10                           | GRM32ER71H106KA12L | DFLS240   | 1.62             | 133              | 47              | 10              |  |

| 3.3 | -9   | 2.4   | 2.2  | XAL4020-222ME_               | 74438356022 | 10                           | GRM32ER71H106KA12L | DFLS240   | 1.62             | 133              | 47              | 15              |  |

| 3.3 | -15  | 1.2   | 4.7  | XAL4030-472ME_               | 74438357047 | 10                           | GRM32ER71H106KA12L | DFLS240   | 2.32             | 118              | 47              | 18              |  |