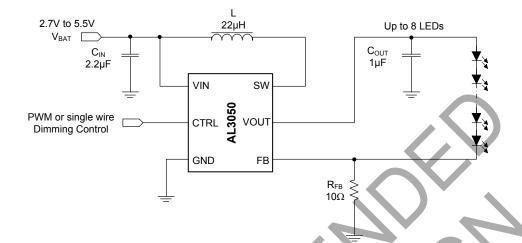

## **Typical Applications Circuit**

## **Pin Descriptions**

| Pin Number | Pin Name    | Function                                                                                                                                            |

|------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | CTRL        | Control pin of the boost converter. It is a multi-functional pin which can be used for enable control, PWM and digital dimming.                     |

| 2          | VIN         | Supply input pin. A capacitor should be connected between the VIN pin and GND pin to keep the DC input voltage constant.                            |

| 3          | VOUT        | Output of the boost converter.                                                                                                                      |

| 4          | FB          | Feedback pin for current. Connect a resistor between this pin and GND to set the current.                                                           |

| 5          | GND         | Ground.                                                                                                                                             |

| 6          | SW          | This is the switching node of the IC. Connect the inductor between the VIN and SW pin.                                                              |

| -          | Thermal Pad | The thermal pad should be soldered to the analog ground plane. If possible, use thermal via to connect to ground plane for ideal power dissipation. |

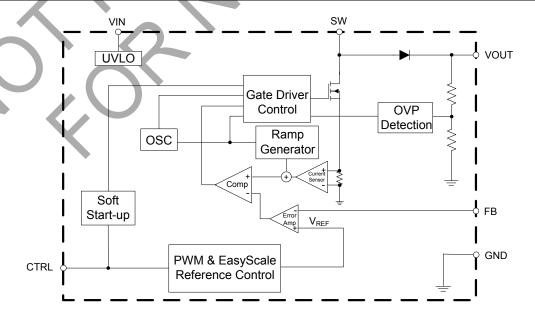

## **Functional Block Diagram**

## Absolute Maximum Ratings (@T<sub>A</sub> = +25°C, unless otherwise specified.) (Note 4)

| Symbol                              | ymbol Parameter                               |                         | Rating      |      |

|-------------------------------------|-----------------------------------------------|-------------------------|-------------|------|

| V <sub>IN</sub>                     | Input Pin Voltage -0.3 to 6                   |                         | V           |      |

| $V_{VOUT}, V_{SW}$                  | VOUT and SW Pin Voltage                       | -0.3 to 32              |             | V    |

| V <sub>FB</sub> , V <sub>CTRL</sub> | FB and CTRL Pin Voltage                       | -0.3 t                  | -0.3 to 6   |      |

| $\theta_{JA}$                       | Thermal Resistance (Junction to Ambient)      | U-DFN2020-6<br>(Type S) | 70.4        | °C/W |

| $T_J$                               | T <sub>J</sub> Operating Junction Temperature |                         | +150        |      |

| T <sub>STG</sub>                    | T <sub>STG</sub> Storage Temperature          |                         | -65 to +150 |      |

| ESD                                 | ESD (Human Body Model)                        | 2000                    |             | V    |

| LSD                                 | ESD (Machine Model)                           | 200                     |             | V    |

Note:

## Recommended Operating Conditions (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol           | Parameter                      |   | Min             | Max  | Unit |

|------------------|--------------------------------|---|-----------------|------|------|

| $V_{IN}$         | Input Voltage                  |   | 2.7             | 5.5  | V    |

| Vo               | Output Voltage                 |   | V <sub>IN</sub> | 30   | V    |

| lo               | Output Current                 |   | -               | 40   | mA   |

| f <sub>PWM</sub> | PWM Dimming Frequency          | \ | 20              | 100  | kHz  |

| T <sub>A</sub>   | Operating Ambient Temperature  |   | -40             | +85  | °C   |

| TJ               | Operating Junction Temperature |   | -40             | +125 | °C   |

<sup>4.</sup> Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to "Absolute Maximum Ratings" for extended periods may affect device reliability.

## **Electrical Characteristics** ( $V_{IN} = 3.6V$ , CTRL = High, $T_A = +25$ °C, unless otherwise specified.)

| Symbol                           | Parameter                             | Condition                                                                     | Min                        | Тур      | Max  | Unit     |

|----------------------------------|---------------------------------------|-------------------------------------------------------------------------------|----------------------------|----------|------|----------|

| SUPPLY VOLTA                     | AGE (VIN PIN)                         |                                                                               |                            |          |      |          |

| $V_{IN}$                         | Input Voltage                         | -                                                                             | 2.7                        | -        | 5.5  | V        |

|                                  | Outropart Comment                     | Device enable, no switching and no load (V <sub>FB</sub> = 0.4V)              | -                          | 0.3      | 0.5  | mA       |

| I <sub>Q</sub> Quiescent Current |                                       | Device enable, switching<br>750kHz and no load (V <sub>FB</sub> = 0V)         |                            | 0.5      | 1.65 |          |

| I <sub>SHDN</sub>                | Shutdown Supply Current               | CRTL = GND                                                                    | -                          | 0.1      | 1    | μΑ       |

| UNDER VOLTA                      | GE LOCKOUT                            |                                                                               |                            |          | )    |          |

|                                  | land IN/I O Threehold                 | V <sub>IN</sub> ramp down                                                     | - /                        | 2.2      | 2.35 | V        |

| $V_{UVLO}$                       | Input UVLO Threshold                  | V <sub>IN</sub> ramp up                                                       | -                          | 2.5      | 2.65 | V        |

| V <sub>HYS</sub>                 | Input UVLO Hysteresis                 | -                                                                             | -                          | 300      | -    | mV       |

| <b>ENABLE CONT</b>               | ROL                                   |                                                                               |                            | <u> </u> |      |          |

| V <sub>CTRL-H</sub>              | CTRL Logic High Voltage               | -                                                                             | 1.2                        |          | -    | V        |

| V <sub>CTRL-L</sub>              | CTRL Logic Low Voltage                | -                                                                             | -                          |          | 0.4  | V        |

| R <sub>CTRL</sub>                | CTRL Pull Down Resistor               | -                                                                             |                            | 300      | -    | kΩ       |

| t <sub>OFF</sub> (Note 5)        | CTRL Pulse With to Shutdown           | CTRL from high to low                                                         | 3.5                        |          | -    | ms       |

|                                  | D REFERENCE (FB PIN)                  |                                                                               |                            |          |      | l        |

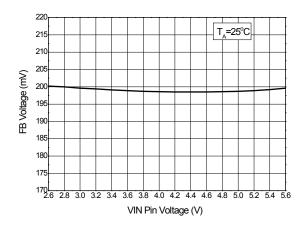

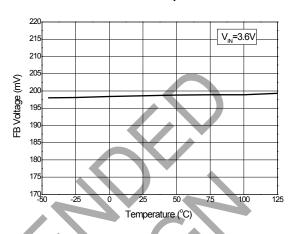

| $V_{REF}$                        | Feedback Reference Voltage            | Duty = 100%                                                                   | 194                        | 200      | 206  | mV       |

| I <sub>FB</sub>                  | Feedback Input Bias Current           | V <sub>FB</sub> = 200mV                                                       | (                          | -        | 2    | μA       |

| t <sub>REF</sub> (Note 5)        | V <sub>REF</sub> Filter Time Constant | - 1                                                                           |                            | 230      | -    | μs       |

| (                                | NCY OSCILLATOR                        |                                                                               |                            |          |      |          |

| f <sub>OSC</sub>                 | Oscillator Frequency                  |                                                                               | 600                        | 750      | 900  | kHz      |

| D <sub>MAX</sub> (Note 5)        | Maximum Duty Cycle                    | V <sub>FB</sub> = 0V, measured on the<br>drive signal of the switch<br>MOSFET | 88                         | 94       | -    | %        |

| POWER SWITC                      | H AND DIODE                           |                                                                               | l                          | I        |      |          |

| R <sub>DS(ON)</sub>              | N-MOSFET On-Resistance                | V <sub>IN</sub> = 3.6V                                                        | -                          | 0.56     | 1    | Ω        |

| VF                               | Power Diode Forward Voltage           | I <sub>DIODE</sub> = 0.2A                                                     | _                          | 0.75     | 1    | V        |

| I <sub>LEAK_SW</sub>             | SW Pin Leakage Current                | V <sub>SW</sub> = 28V                                                         | _                          | 0.1      | 2    | μA       |

| PROTECTION L                     |                                       |                                                                               |                            |          |      | '        |

| I <sub>LIM</sub>                 | N-MOSFET Current Limit                | D = D <sub>MAX</sub>                                                          | 0.6                        | 0.7      | 0.84 | А        |

| ILIM_OPEN                        | LED Open Current Limit                | LED open                                                                      | -                          | 0.3      | -    | A        |

| V <sub>OVP</sub>                 | Open LED Protection Threshold         | Measured on the VOUT pin                                                      | 27                         | 28.2     | 30   | V        |

| T <sub>OTSD</sub> (Note 5)       | Thermal Shutdown Threshold            | -                                                                             | -                          | +160     | -    | °C       |

| T <sub>HYS</sub> (Note 5)        | Thermal Shutdown Hysteresis           | -                                                                             | _                          | +20      | _    | °C       |

|                                  | NG TIMING (Note 5)                    |                                                                               |                            | . 20     |      |          |

| t <sub>1W_DET</sub>              | Digital Dimming Detection Time        | CTRL pin low                                                                  | 450                        | _        | _    | μs       |

|                                  | Digital Dimming Detection Delay       | -                                                                             | 100                        | -        | _    | μs       |

| t <sub>1W_DELAY</sub>            | Digital Dimming Detection Window Time | Measured from CTRL High                                                       | 3.5                        | -        | _    | ms       |

| t <sub>1W_WIN</sub>              | Start Time of Program Stream          | Wedsdred Holli OTTL High                                                      | 3.5                        | -        | -    |          |

| tstart<br>tsco                   | End Time Of Program Stream            | -                                                                             | 3.5                        | -        | 600  | μs<br>μs |

| tuus                             | High Time Low Bit                     | Logic 0                                                                       | 3.5                        | -        | 300  | · ·      |

| t <sub>H_LB</sub>                | Low Time Low Bit                      | Logic 0                                                                       | †                          | -        | 600  | μs       |

| tu up                            | High Time High Bit                    | Logic 0                                                                       | 2×t <sub>H_LB</sub>        |          | 600  | μs       |

| th_HB                            | Low Time High Bit                     | ,                                                                             | 2×t <sub>L_HB</sub><br>3.5 | -        | 300  | μs       |

| t <sub>L_HB</sub>                | Acknowledge Output Voltage Low        | Logic 1 Open Drain, $R_{PULL-UP}$ =15K $\Omega$ to                            | 3.5                        | -        | 0.4  | μs<br>V  |

| V AUKN                           | 3 , 3                                 | VIN                                                                           |                            |          |      |          |

| tval_ackn                        | Acknowledge Valid Time                | -                                                                             | -                          | -        | 3.5  | μs       |

| t <sub>ACKN</sub>                | Duration of Acknowledge Condition     | -                                                                             | -                          | -        | 900  | μs       |

Note: 5. Guaranteed by design.

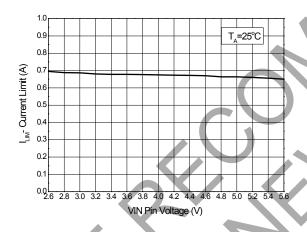

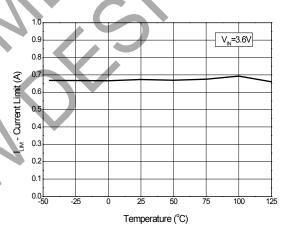

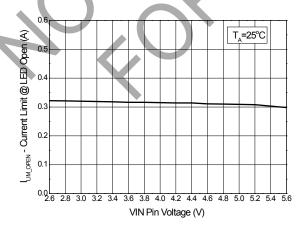

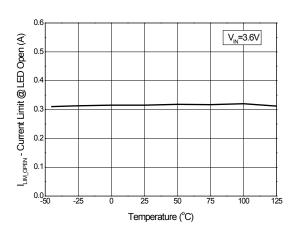

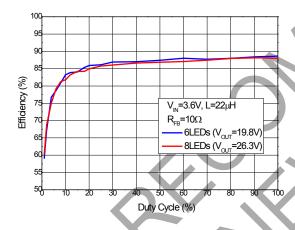

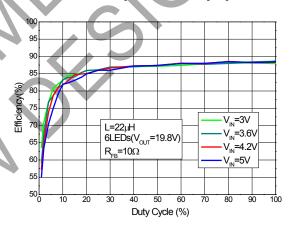

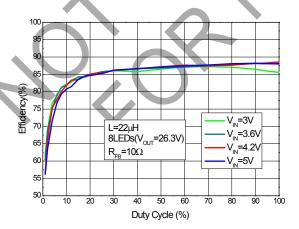

# Performance Characteristics ( $V_{IN}$ = 3.6V, L = 22 $\mu$ H, R<sub>FB</sub> = 10 $\Omega$ , 8 LEDs in series, T<sub>A</sub> = +25°C, unless otherwise specified.)

#### FB vs. VIN Pin Voltage

#### FB vs. Temperature

### **Current Limit vs. VIN Pin Voltage**

**Current Limit vs. Temperature**

### Current Limit @LED Open vs. VIN Pin Voltage

### Current Limit @LED Open vs. Temperature

# $\textbf{Performance Characteristics} \text{ (V}_{\text{IN}} = 3.6 \text{V, L} = 22 \mu\text{H, R}_{\text{FB}} = 10 \underline{\Omega}, 8 \text{ LEDs in series, T}_{\text{A}} = +25 ^{\circ}\text{C, unless otherwise specified.)}$

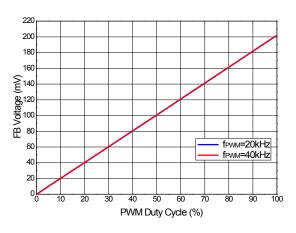

### FB vs. PWM Duty Cycle

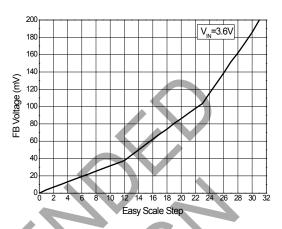

### FB vs. Easy Scale Step

### Efficiency vs. PWM Duty Cycle

Efficiency vs. PWM Duty Cycle

## Efficiency vs. PWM Duty Cycle

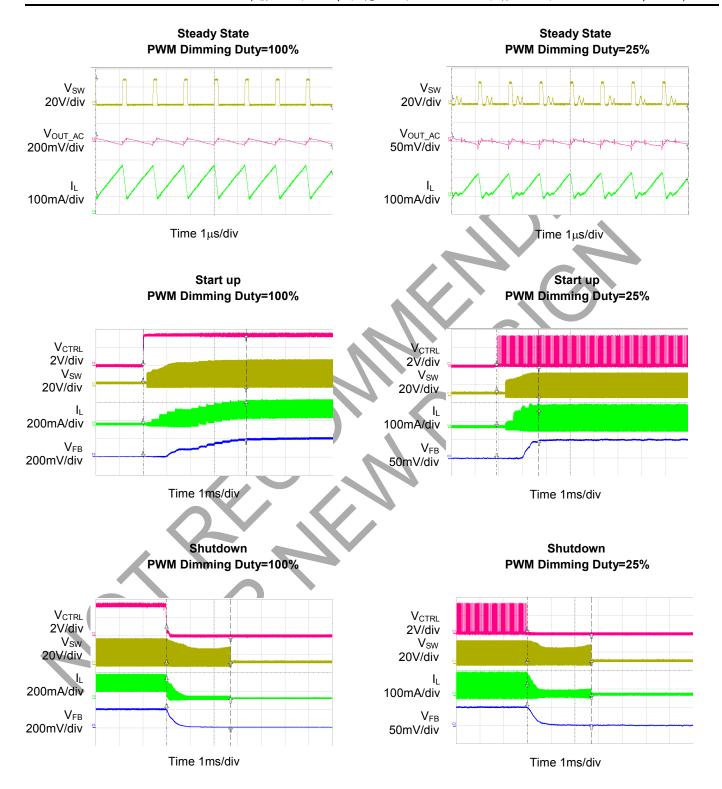

## Performance Characteristics ( $V_{IN} = 3.6V$ , $L = 22\mu H$ , $R_{FB} = 10\Omega$ , 8 LEDs in series, $T_A = +25^{\circ}C$ , unless otherwise specified.)

### **Performance Characteristics** ( $V_{IN} = 3.6V$ , $L = 22\mu H$ , $R_{EB} = 10\Omega$ , 8 LEDs in series, $T_A = +25^{\circ}C$ , unless otherwise specified.)

Time 10µs /div

### Application Information

20V/div

#### 1. General Operation

The AL3050 is a high efficiency boost converter with integrated power diode in a small package size. The device is ideal for driving white LED in series. The serial LED connection provides even illumination by sourcing the same output current through all LEDs, eliminating the need for expensive factory calibration. The device integrates a 30V/0.7A low side switch MOSFET and a 30V power diode, and operates in pulse width modulation (PWM) with 750 kHz fixed switching frequency. For operation see the block diagram. The duty cycle of the converter is set by the error amplifier output and the current signal applied to the PWM control comparator. The control architecture is based on traditional current-mode control; therefore, slope compensation is added to the current signal to allow stable operation for duty cycles larger than 50%. The feedback loop regulates the FB pin to a low reference voltage (200mV typical), reducing the power dissipation in the current sense resistor.

#### 2. Soft Start-up

Soft-start circuitry is integrated into the IC to avoid a high inrush current during start-up. After the device is enabled, the voltage at FB pin ramps up slowly to the reference voltage in 32 steps with each step taking 341µs. This ensures that the output voltage rises slowly to reduce the input current. Additionally, during the start up process, the current limit of the switch is set to half of the normal current limit spec. During this period, the input current is kept below 360mA (typical).

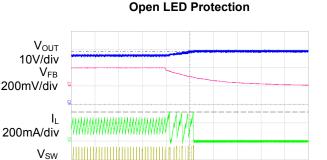

#### 3. Open LED Protection

Open LED protection circuitry prevents IC damage as the result of white LED disconnection. The AL3050 monitors the voltages at the VOUT pin and FB pin. The circuitry turns off the switch MOSFET and shuts down the IC completely if both of the following two conditions are met: 1) the VOUT voltage reaches OVP threshold (28.2V typical), 2) FB voltage is lower than half of its regulation voltage. This means the LED string is open or the FB pin is short to ground. During open LED condition, the cycle by cycle switch current limit is set to be 0.3A typically to protect external devices. As a result, the output voltage falls to the level of the input supply. The device remains in shutdown mode until it is enabled by pulling down the CTRL pin logic low for at least 3.5ms and then pulling it high.

#### 4. Shutdown

The  $\Delta L3050$  enters shutdown mode when the CTRL voltage is logic low for more than 3.5ms. During shutdown, the input supply current for the device is less than 1µA (max). Although the internal MOSFET does not switch in shutdown mode, there is still a DC current path between the input and the LEDs through the inductor and the power diode. The minimum forward voltage of the LED array must exceed the maximum input voltage to ensure that the LEDs remain off in shutdown. In the typical application with two or more LEDs, the forward voltage is large enough to reverse bias the diode and keep leakage current low.

#### 5. Current Setting

The FB voltage is regulated by a low 0.2V reference voltage. The LED current is programmed externally using a current-sense resistor in series with the LED string. The LED current can be calculated by Equation 1:

$$I_{LED} = rac{V_{FB}}{R_{SET}}$$

(1)

Where

$I_{\mathit{LED}}$  = full-scale output current of LEDs

$V_{\it FB}$  = 200mV (regulated voltage of FB)

$R_{\it SET}$  = current sense resistor at FB pin

The output current tolerance depends on the FB accuracy and the current sensor resistor accuracy.

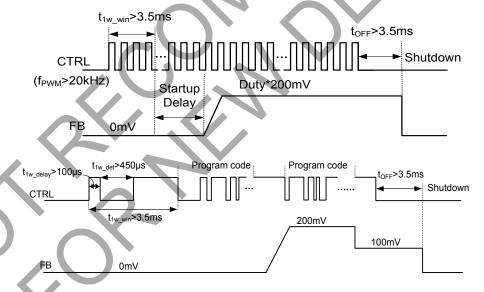

#### 6. LED Brightness Dimming Mode Selection

The CTRL pin is used for the control input for both dimming modes, PWM dimming and single wire dimming. The dimming mode for the AL3050 is selected each time the device is enabled. The default dimming mode is PWM dimming. To enter the single wire mode, the following digital pattern on the CTRL pin must be recognized by the IC every time the IC starts from the shutdown mode.

- 1. Pull CTRL pin high to enable the AL3050, and to start the single wire dimming detection window,

- 2. After the single wire dimming detection delay  $(t_{1W\_DELAY}, 100\mu s)$  expires, drive the CTRL pin low for more than single wire detection time  $(t_{1W\_DET}, 450\mu s)$ ;

- 3. The CTRL pin has to be low for more than  $t_{1w\_DET}$  before the single wire dimming detection window ( $t_{1W\_WIN}$ , 3.5ms) expires. Single wire detection

window starts from the first CTRL pin low to high transition.

If all above three conditions are fulfilled, the IC enters single wire dimming mode, otherwise enters PWM dimming mode. Once the dimming mode is programmed, it can not be changed without another start up. This means the IC needs to be shut down by pulling the CTRL low for 3.5ms and restarts. See the Dimming Mode Detection and Soft Start (Figure 1) for a graphical explanation.

Figure 1. Dimming Mode Detection and Soft Start

#### 7. PWM Dimming Mode

When the CTRL pin is constantly high, the FB voltage is regulated to 200mV typically. However, the CTRL pin allows a PWM signal to reduce this regulation voltage; therefore, it achieves LED brightness dimming. The relationship between the duty cycle and FB voltage is given by Equation 2.

$$V_{FB} = Duty \times 200mV \tag{2}$$

Where

Duty = duty cycle of the PWM signal 200mV = internal reference voltage

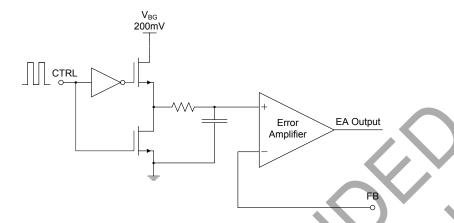

Figure 2. Block Diagram of Programmable FB Voltage in PWM Dimming Mode

As shown in Figure 2, the AL3050 chops up the internal 200mV reference voltage at the duty cycle of the PWM signal. The pulse signal is then filtered by an internal low pass filter. The output of the filter is connected to the error amplifier as the reference voltage for the FB pin regulation. Therefore, although a PWM signal is used for brightness dimming, only the LED DC current is modulated, which is often referred as analog dimming. This eliminates the audible noise which often occurs when the LED current is pulsed in replica of the frequency and duty cycle of PWM control.

For optimum performance, use the PWM dimming frequency in the range of 20kHz to 100kHz. Since the CTRL pin is logic only pin, adding an external RC filter applied to the pin does not work.

The minimum dimming duty cycle the IC can support is 1% within the PWM dimming frequency range 20kHz to 100kHz.

#### 8. Single Wire Digital Dimming Mode

The CTRL pin features a simple digital interface to allow digital brightness control. The digital dimming can save the processor power and battery life as it does not require a PWM signal all the time, and the processor can enter idle mode if available.

The AL3050 adopts a single wire digital protocol for the digital dimming mode control, which can program the FB voltage to any of the 32 steps with single command. The step increment increases with the voltage to produce pseudo logarithmic curve for the brightness step. See the Table 1 for the FB pin voltage steps. The default step is full scale when the device is first enabled (V<sub>FB</sub> = 200mV). The programmed reference voltage is stored in an internal register. A power reset clears the register value and reset it to default.

| -  | FB Voltage (mV) | D4  | D3 | D2 | D1 | D0 |

|----|-----------------|-----|----|----|----|----|

| 0  | 0               | 0   | 0  | 0  | 0  | 0  |

| 1  | 5               | 0   | 0  | 0  | 0  | 1  |

| 2  | 8               | 0   | 0  | 0  | 1  | 0  |

| 3  | 11              | 0   | 0  | 0  | 1  | 1  |

| 4  | 14              | 0   | 0  | 1  | 0  | 0  |

| 5  | 17              | 0   | 0  | 1  | 0  | 1  |

| 6  | 20              | 0   | 0  | 1  | 1  | 0  |

| 7  | 23              | 0   | 0  | 1  | 1  | 1  |

| 8  | 26              | 0   | 1  | 0  | 0  | 0  |

| 9  | 29              | 0   | 1  | 0  | 0  | 1  |

| 10 | 32              | 0   | 1  | 0  | 1  | 0  |

| 11 | 35              | 0   | 1  | 0  | 1  | 1  |

| 12 | 38              | 0   | 1  | 1  | 0  | 0  |

| 13 | 44              | 0   | 1  | 1  | 0  | 1  |

| 14 | 50              | 0   | 1  | 1  | 1  | 0  |

| 15 | 56              | 0   | 1  |    | 1  | 1  |

| 16 | 62              | 1   | 0  | 0  | 0  | 0  |

| 17 | 68              | 1   | 0  | 0  | 0  | 1  |

| 18 | 74              | 1   | 0  | 0  | 1  | 0  |

| 19 | 80              | 1   | 0  | 0  | 1  | 1  |

| 20 | 86              | 1   | 0  | 1  | 0  | 0  |

| 21 | 92              | 1   | 0  | 1  | 0  | 1  |

| 22 | 98              | 1   | 0  | 1  | 1  | 0  |

| 23 | 104             |     | 0  | 1  | 1  | 1  |

| 24 | 116             | . 1 | 1  | 0  | 0  | 0  |

| 25 | 128             | 1   | 1  | 0  | 0  | 1  |

| 26 | 140             | 1   | 1  | 0  | 1  | 0  |

| 27 | 152             | 1   | 1  | 0  | 1  | 1  |

| 28 | 164             | 1   | 1  | 1  | 0  | 0  |

| 29 | 176             | 1   | 1  | 1  | 0  | 1  |

| 30 | 188             | 1   | 1  | 1  | 1  | 0  |

| 31 | 200             | 1   | 1  | 1  | 1  | 1  |

Table 1. 32-Step Digital Dimming Setting

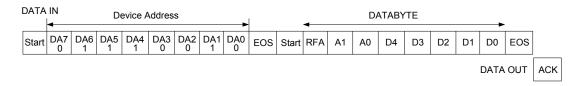

The digital dimming interface is based on a master-slave structure, where the master is typically a microcontroller or application processor. Figure 3 and Table 2 give an overview of the protocol. The protocol consists of a device specific address byte and a data byte. The device specific address byte is fixed to 58 hex. The data byte consists of five bits for information, two address bits ("00"), and the RFA bit. The RFA bit set to high indicates the Request for Acknowledge condition. The Acknowledge condition is only applied if the protocol was received correctly. The advantage of single wire digital dimming compared with other on pin interfaces is that its bit detection is in a large extent independent from the bit transmission rate. It can automatically detect bit rates between 1.1kBit/sec and up to 100kBit/sec.

Figure 3. Single Wire Digital Protocol Overview

| Byte                | Bit Number | Name | Transmission<br>Direction | Description                                                                                                                                                                                                                                                                                                                                  |

|---------------------|------------|------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | 7          | DA7  |                           | 0 (MSB Device Address)                                                                                                                                                                                                                                                                                                                       |

|                     | 6          | DA6  |                           | 1                                                                                                                                                                                                                                                                                                                                            |

|                     | 5          | DA5  |                           | 0                                                                                                                                                                                                                                                                                                                                            |

| Device Address Byte | 4          | DA4  | IN                        | 1                                                                                                                                                                                                                                                                                                                                            |

| 72 Hex              | 3          | DA3  | IIN                       | 1                                                                                                                                                                                                                                                                                                                                            |

|                     | 2          | DA2  |                           | 0                                                                                                                                                                                                                                                                                                                                            |

|                     | 1          | DA1  |                           | 0                                                                                                                                                                                                                                                                                                                                            |

|                     | 0          | DA0  |                           | 0 (LSB Device Address)                                                                                                                                                                                                                                                                                                                       |

|                     | 7 (MSB)    | RFA  |                           | Request for acknowledge. If high, acknowledge is applied by device.                                                                                                                                                                                                                                                                          |

|                     | 6          | A1   |                           | 0 (Address bit A1)                                                                                                                                                                                                                                                                                                                           |

|                     | 5          | A0   |                           | 0 (Address bit A0)                                                                                                                                                                                                                                                                                                                           |

| Data Byte           | 4          | D4   | IN                        | Data bit D4                                                                                                                                                                                                                                                                                                                                  |

| ŕ                   | 3          | D3   | \                         | Data bit D3                                                                                                                                                                                                                                                                                                                                  |

|                     | 2          | D2   |                           | Data bit D2                                                                                                                                                                                                                                                                                                                                  |

|                     | 1          | D1   |                           | Data bit D1                                                                                                                                                                                                                                                                                                                                  |

|                     | 0 (LSB)    | D0   | 11/2                      | Data bit D0                                                                                                                                                                                                                                                                                                                                  |

| -                   | -          | ACK  | OUT                       | Acknowledge condition active 0, this condition will only be applied to case RFA bit is set. Open drain output, line needs to be pulled high by the host with a pullup resistor. This feature can only be used if the master has an open drain output stage. In case of a push pull output stage, acknowledge condition may not be requested! |

Table 2. Single Wire Dimming Bit Description

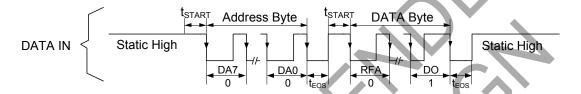

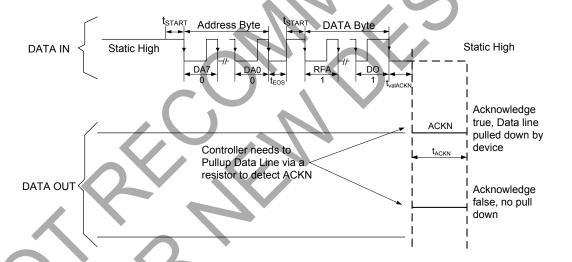

All bits are transmitted MSB first and LSB last. Figure 4 shows the protocol without acknowledge request (Bit RFA = 0), Figure 5 with acknowledge (Bit RFA = 1) request. Prior to both bytes, device address byte and data byte, a start condition must be applied. For this, the CTRL pin must be pulled high for at least  $t_{START}$  (3.5µs) before the bit transmission starts with the falling edge. If the CTRL pin is already at high level, no start condition is needed prior to the device address byte. The transmission of each byte is closed with an End of Stream condition for at least  $t_{EOS}$  (3.5µs).

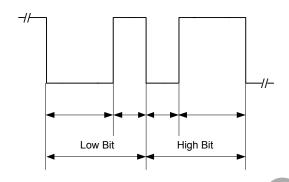

The bit detection is based on a Logic Detection scheme, where the criterion is the relation between  $t_{LOW}$  and  $t_{HIGH}$  (refer to Figure 6). It can be simplified to:

High Bit:  $t_{HIGH} > t_{LOW}$ , but with  $t_{HIGH}$  at least 2x  $t_{LOW}$ . Low Bit:  $t_{HIGH} < t_{LOW}$ , but with  $t_{LOW}$  at least 2x  $t_{HIGH}$ .

The bit detection starts with a falling edge on the CTRL pin and ends with the next falling edge. Depending on the relation between  $t_{HIGH}$  and  $t_{LOW}$ , the logic 0 or 1 is detected.

The acknowledge condition is only applied if:

- · Acknowledge is requested by setting RFA bit to 1.

- The transmitted device address matches with the device address of the device.

- Device address byte and data byte are received correctly.

If above conditions are met, after  $t_{VAL\_ACKN}$  (3.5 $\mu$ s) delay from the moment when the last falling edge of the protocol is detected, an internal ACKN-MOSFET is turned on to pull the CTRL pin low for the time  $t_{ACKN}$  (900 $\mu$ s maximum), then the Acknowledge condition is valid. During the  $t_{VAL\_ACKN}$  delay, the master controller keeps the line low; after the delay, it should release the line by outputting high impedance and then detect the acknowledge condition. If it reads back a logic 0, it means the IC has received the command correctly. The CTRL pin can be used again by the master when the acknowledge condition ends after  $t_{ACKN}$  time.

Note that the acknowledge condition may only be requested in case the master device has an open drain output. For a push-pull output stage, the use a series resistor in the CRTL line to limit the current to 500µA is recommended to for such cases as:

- · an accidentally requested acknowledge, or

- to protect the internal ACKN-MOSFET.

Figure 4. Single Wire Digital Dimming Timing, without Acknowledge RFA=0

Figure 5. Single Wire Digital Dimming Timing, with Acknowledge RFA=1

Figure 6. Single Wire Digital Dimming - Bit Coding

### 9. Under Voltage Lockout

An under voltage lockout prevents operation of the device at input voltages below typical 2.2V. When the input voltage is below the under voltage threshold, the device is shutdown and the internal switch is turned off. If the input voltage rises by under voltage lockout hysteresis, the IC restarts.

#### 10. Thermal Shutdown

An internal thermal shutdown turns off the device when the typical junction temperature of +160°C is exceeded. The device is released from shutdown automatically when the junction temperature decreases by +20°C.

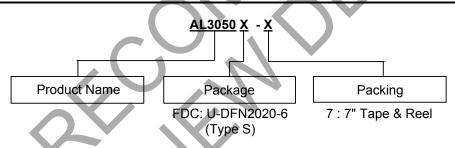

## Ordering Information

| Dord Novelean | Dealessa Code | Deskara              | 7" Tape and Reel |                    |  |

|---------------|---------------|----------------------|------------------|--------------------|--|

| Part Number   | Package Code  | Package              | Quantity         | Part Number Suffix |  |

| AL3050FDC-7   | FDC           | U-DFN2020-6 (Type S) | 3000/Tape & Reel | -7                 |  |

## **Marking Information**

U-DFN2020-6 (Type S)

(Top View)

<u>XX</u> Y<u>W</u>X XX: Identification Code

Y: Year: 0~9

W: Week: A~Z: 1~26 week;

a~z: 27~52 week; z represents

52 and 53 week

X: Internal Code

| Part Number | Package              | Identification Code |  |

|-------------|----------------------|---------------------|--|

| AL3050FDC-7 | U-DFN2020-6 (Type S) | Z9                  |  |

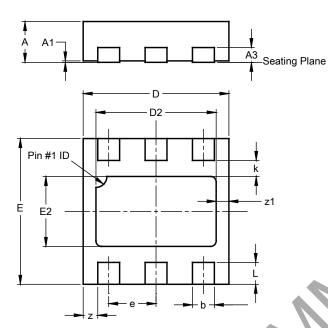

## **Package Outline Dimensions**

Please see http://www.diodes.com/package-outlines.html for the latest version.

## U-DFN2020-6 (Type S)

| U-DFN2020-6<br>(Type S) |      |        |       |  |  |

|-------------------------|------|--------|-------|--|--|

| Dim                     | Min  | Max    | Тур   |  |  |

| Α                       | 0.51 | 0.61   | 0.56  |  |  |

| A1                      | 0.00 | 0.05   | 0.02  |  |  |

| <b>A</b> 3              | 1    | 1      | 0.203 |  |  |

| b                       | 0.25 | 0.35   | 0.30  |  |  |

| D                       | 1.95 | 2.05   | 2.00  |  |  |

| D2                      | 1.55 | 1.75   | 1.65  |  |  |

| E                       | 1.95 | 2.05   | 2.00  |  |  |

| E2                      | 0.86 | 1.06   | 0.96  |  |  |

| е                       | 0.   | 650 BS | S     |  |  |

| k                       | -    | ı      | 0.22  |  |  |

| ٦                       | 0.25 | 0.35   | 0.30  |  |  |

| z                       |      | 1      | 0.20  |  |  |

| z1                      |      |        | 0.175 |  |  |

| All Dimensions in mm    |      |        |       |  |  |

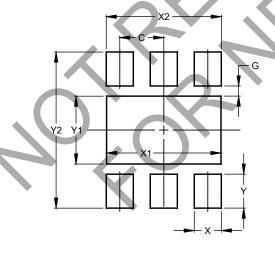

## **Suggested Pad Layout**

Please see http://www.diodes.com/package-outlines.html for the latest version.

# U-DFN2020-6 (Type S)

| Dimensions     | Value   |  |

|----------------|---------|--|

| פווטופווסוטווס | (in mm) |  |

| С              | 0.650   |  |

| G              | 0.150   |  |

| X              | 0.400   |  |

| X1             | 1.690   |  |

| X2             | 1.700   |  |

| Y              | 0.500   |  |

| Y1             | 1.000   |  |

| Y2             | 2.300   |  |

#### **IMPORTANT NOTICE**

- 1. DIODES INCORPORATED AND ITS SUBSIDIARIES ("DIODES") MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

- 2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes products. Diodes products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of the Diodes products for their intended applications, (c) ensuring their applications, which incorporate Diodes products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

- 3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

- 4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

- 5. Diodes products are provided subject to Diodes' Standard Terms and Conditions of Sale (<a href="https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/">https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/</a>) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

- 6. Diodes products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

- 7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

- 8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

Copyright © 2021 Diodes Incorporated

www.diodes.com