## **TABLE OF CONTENTS**

| Features                                                      |

|---------------------------------------------------------------|

| Applications1                                                 |

| Functional Block Diagram                                      |

| General Description                                           |

| Product Highlights                                            |

| Revision History                                              |

| Specifications                                                |

| AD7656-1                                                      |

| AD7657-15                                                     |

| AD7658-17                                                     |

| Timing Specifications                                         |

| Absolute Maximum Ratings10                                    |

| Thermal Resistance                                            |

| ESD Caution10                                                 |

| Pin Configuration and Function Descriptions11                 |

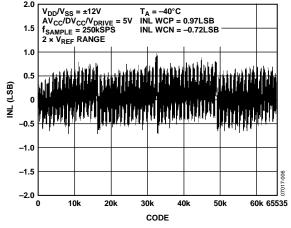

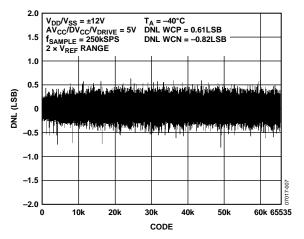

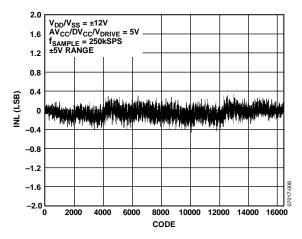

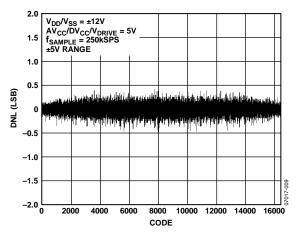

| Typical Performance Characteristics                           |

|                                                               |

| Terminology                                                   |

|                                                               |

| REVISION HISTORY                                              |

|                                                               |

| REVISION HISTORY 3/12—Rev. C to Rev. D Changes to Figure 28   |

| REVISION HISTORY  3/12—Rev. C to Rev. D  Changes to Figure 28 |

| REVISION HISTORY 3/12—Rev. C to Rev. D Changes to Figure 28   |

| REVISION HISTORY  3/12—Rev. C to Rev. D  Changes to Figure 28 |

| REVISION HISTORY  3/12—Rev. C to Rev. D  Changes to Figure 28 |

| REVISION HISTORY  3/12—Rev. C to Rev. D Changes to Figure 28  |

| REVISION HISTORY  3/12—Rev. C to Rev. D  Changes to Figure 28 |

| REVISION HISTORY  3/12—Rev. C to Rev. D Changes to Figure 28  |

| REVISION HISTORY  3/12—Rev. C to Rev. D  Changes to Figure 28 |

| REVISION HISTORY  3/12—Rev. C to Rev. D  Changes to Figure 28 |

| REVISION HISTORY  3/12—Rev. C to Rev. D  Changes to Figure 28 |

| Theory of Operation                                                     | 20 |

|-------------------------------------------------------------------------|----|

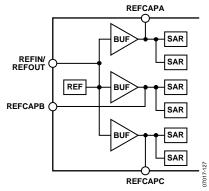

| Converter Details                                                       | 20 |

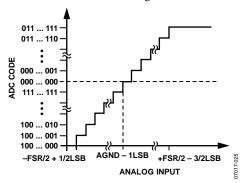

| ADC Transfer Function                                                   | 21 |

| Internal/External Reference                                             | 21 |

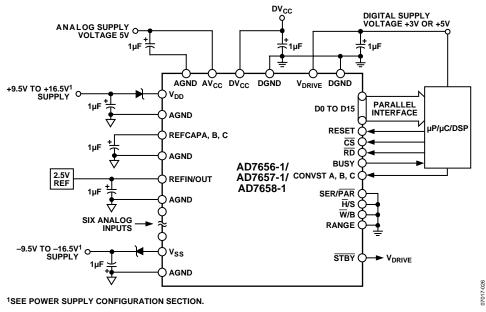

| Typical Connection Diagram                                              | 21 |

| Driving the Analog Inputs                                               | 22 |

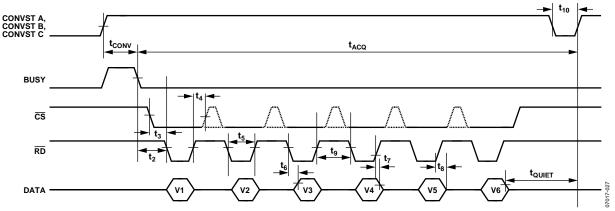

| Interface Options                                                       | 22 |

| Software Selection of ADCs                                              | 24 |

| Changing the Analog Input Range $(\overline{H}/S SEL = 0)$              | 25 |

| Changing the Analog Input Range $(\overline{H}/S SEL = 1)$              | 25 |

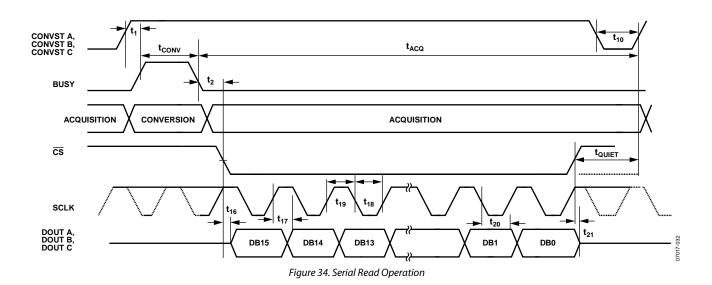

| Serial Read Operation                                                   |    |

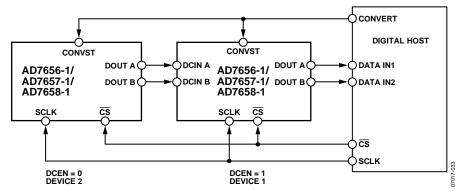

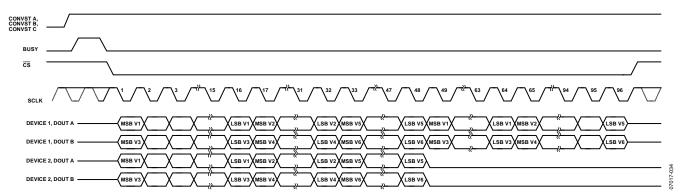

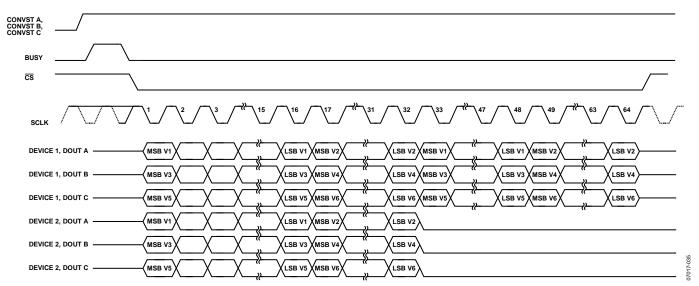

| Daisy-Chain Mode (DCEN = 1, SER/PAR SEL = 1)                            |    |

| Application Hints                                                       | 29 |

| Layout                                                                  | 29 |

| Power Supply Configuration                                              | 29 |

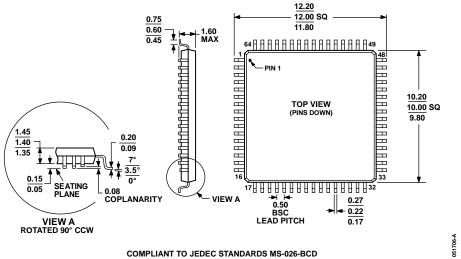

| Outline Dimensions                                                      | 30 |

| Ordering Guide                                                          | 30 |

|                                                                         |    |

|                                                                         |    |

| Changes to Table 3                                                      |    |

| Changes to Table 4                                                      |    |

| Changes to Absolute Maximum Ratings Table                               |    |

| Changes to Pin Functions Description Table                              |    |

| Changes to Figure 9                                                     |    |

| Changes to Converter Details Section                                    |    |

| Changes to Internal/External Reference Section                          |    |

| Changes to Interface Options Section                                    |    |

| Changes to Parallel Interface Section                                   |    |

| Changes to Serial Interface (SER/PAR SEL = 1) Section                   |    |

| Changes to Daisy-Chain Mode (DCEN = 1, $SER/\overline{PAR}$ $SEL = 1$ ) |    |

| Changes to Layout Section                                               |    |

| Undated Outline Dimension                                               | 21 |

7/08—Revision 0: Initial Version

## **SPECIFICATIONS**

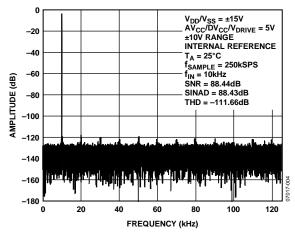

### AD7656-1

$V_{REF} = 2.5 \text{ V internal/external, } AV_{CC} = 4.75 \text{ V to } 5.25 \text{ V, } DV_{CC} = 4.75 \text{ V to } 5.25 \text{ V, } V_{DRIVE} = 2.7 \text{ V to } 5.25 \text{ V; for the } \pm 4 \times V_{REF} \text{ range, } V_{DD} = 10 \text{ V to } 16.5 \text{ V, } V_{SS} = -10 \text{ V to } -16.5 \text{ V; for the } \pm 2 \times V_{REF} \text{ range, } V_{DD} = 5 \text{ V to } 16.5 \text{ V, } V_{SS} = -5 \text{ V to } -16.5 \text{ V; } f_{SAMPLE} = 250 \text{ kSPS, } T_A = T_{MIN} \text{ to } T_{MAX} \text{, unless otherwise noted.}$

Table 1.

| Parameter                                           | Min                   | Тур  | Max                 | Unit                                    | Test Conditions/Comments                                                |

|-----------------------------------------------------|-----------------------|------|---------------------|-----------------------------------------|-------------------------------------------------------------------------|

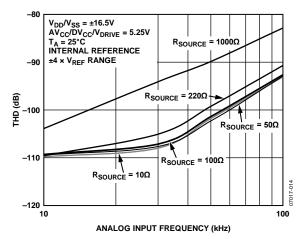

| DYNAMIC PERFORMANCE                                 |                       |      | _                   |                                         | f <sub>IN</sub> = 10 kHz sine wave                                      |

| Signal-to-(Noise + Distortion) (SINAD)1             |                       | 88   |                     | dB                                      |                                                                         |

| Signal-to-Noise Ratio (SNR) <sup>1</sup>            |                       | 88   |                     | dB                                      |                                                                         |

| Total Harmonic Distortion (THD) <sup>1</sup>        |                       |      | -90                 | dB                                      |                                                                         |

|                                                     |                       | -105 |                     | dB                                      | $V_{DD}/V_{SS} = \pm 5 \text{ V to } \pm 16.5 \text{ V}$                |

| Peak Harmonic or Spurious Noise (SFDR) <sup>1</sup> |                       | -100 |                     | dB                                      |                                                                         |

| Intermodulation Distortion (IMD) <sup>1</sup>       |                       |      |                     |                                         | fa = 10.5 kHz, fb = 9.5 kHz                                             |

| Second-Order Terms                                  |                       | -112 |                     | dB                                      |                                                                         |

| Third-Order Terms                                   |                       | -107 |                     | dB                                      |                                                                         |

| Aperture Delay                                      |                       |      | 10                  | ns                                      |                                                                         |

| Aperture Delay Matching                             |                       |      | 4                   | ns                                      |                                                                         |

| Aperture Jitter                                     |                       | 35   |                     | ps                                      |                                                                         |

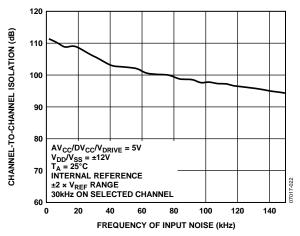

| Channel-to-Channel Isolation <sup>1</sup>           |                       | -100 |                     | dB                                      | f <sub>IN</sub> on unselected channels up to 100 kHz                    |

| Full-Power Bandwidth                                |                       | 4.5  |                     | MHz                                     | @ -3 dB                                                                 |

|                                                     |                       | 2.2  |                     | MHz                                     | @ -0.1 dB                                                               |

| DC ACCURACY                                         |                       |      |                     |                                         |                                                                         |

| Resolution                                          | 16                    |      |                     | Bits                                    |                                                                         |

| No Missing Codes                                    |                       |      |                     |                                         |                                                                         |

| B Version                                           | 15                    |      |                     | Bits                                    |                                                                         |

| Y Version                                           | 14                    |      |                     | Bits                                    |                                                                         |

| Integral Nonlinearity <sup>1</sup>                  |                       |      | ±3                  | LSB                                     |                                                                         |

|                                                     |                       | ±1   |                     | LSB                                     |                                                                         |

| Positive Full-Scale Error <sup>1</sup>              |                       |      | ±0.8                | % FSR                                   | ±0.381% FSR typical                                                     |

| Positive Full-Scale Error Matching <sup>1</sup>     |                       |      | ±0.35               | % FSR                                   |                                                                         |

| Bipolar Zero-Scale Error <sup>1</sup>               |                       |      | _0.55               | 70.0.                                   | ±0.0137% FSR typical                                                    |

| B Version                                           |                       |      | ±0.048              | % FSR                                   |                                                                         |

| Y Version                                           |                       |      | ±0.048              | %F SR                                   |                                                                         |

| Bipolar Zero-Scale Error Matching <sup>1</sup>      |                       |      | ±0.038              | % FSR                                   |                                                                         |

| Negative Full-Scale Error <sup>1</sup>              |                       |      | ±0.8                | % FSR                                   | ±0.381% FSR typical                                                     |

| Negative Full-Scale Error Matching <sup>1</sup>     |                       |      | ±0.35               | % FSR                                   |                                                                         |

| ANALOG INPUT                                        |                       |      |                     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | See Table 8 for minimum V <sub>DD</sub> /V <sub>SS</sub> for each range |

| Input Voltage Ranges                                | $-4 \times V_{REF}$   |      | $+4 \times V_{REF}$ | ٧                                       | RNGx bits or RANGE pin = 0                                              |

| input voltage hanges                                | -2 × V <sub>REF</sub> |      | +2×V <sub>REF</sub> | V                                       | RNGx bits or RANGE pin = 1                                              |

| DC Leakage Current                                  |                       |      | ±1                  | μΑ                                      |                                                                         |

| Input Capacitance <sup>2</sup>                      |                       | 10   |                     | pF                                      | ±4 × V <sub>REF</sub> range when in track                               |

| input capacitance                                   |                       | 14   |                     | pF                                      | $\pm 2 \times V_{REF}$ range when in track                              |

| REFERENCE INPUT/OUTPUT                              |                       |      |                     | F.                                      |                                                                         |

| Reference Input Voltage Range                       | 2.5                   |      | 2.5                 | ٧                                       |                                                                         |

| DC Leakage Current                                  | 2.3                   |      | ±1                  | μΑ                                      |                                                                         |

| Input Capacitance <sup>2</sup>                      |                       | 18.5 |                     | pF                                      | REF <sub>EN/DIS</sub> = 1                                               |

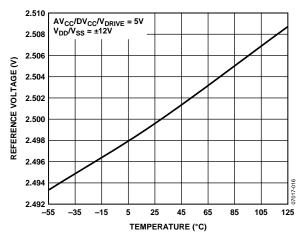

| Reference Output Voltage                            | 2.49                  | 10.5 | 2.51                | V                                       | TIEL ENVOID — I                                                         |

| Long-Term Stability                                 | 2.49                  | 150  | 2.31                | -                                       | 1000 hours                                                              |

| Reference Temperature Coefficient                   |                       | 130  | 25                  | ppm                                     | Tood flours                                                             |

| heierence remperature Coemcient                     |                       | 6    | 25                  | ppm/°C                                  |                                                                         |

|                                                     |                       | 6    |                     | ppm/°C                                  |                                                                         |

| Parameter                                         | Min                      | Тур  | Max                    | Unit | Test Conditions/Comments                                                                                                             |

|---------------------------------------------------|--------------------------|------|------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| LOGIC INPUTS                                      |                          |      |                        |      |                                                                                                                                      |

| Input High Voltage (V <sub>INH</sub> )            | $0.7 \times V_{DRIVE}$   |      |                        | V    |                                                                                                                                      |

| Input Low Voltage (V <sub>INL</sub> )             |                          |      | $0.3 \times V_{DRIVE}$ | V    |                                                                                                                                      |

| Input Current (I <sub>IN</sub> )                  |                          |      | ±10                    | μΑ   | Typically 10 nA, $V_{IN} = 0 \text{ V or } V_{DRIVE}$                                                                                |

| Input Capacitance (C <sub>IN</sub> ) <sup>2</sup> |                          |      | 10                     | pF   |                                                                                                                                      |

| LOGIC OUTPUTS                                     |                          |      |                        | ·    |                                                                                                                                      |

| Output High Voltage (Vон)                         | V <sub>DRIVE</sub> − 0.2 |      |                        | V    | $I_{SOURCE} = 200 \mu\text{A}$                                                                                                       |

| Output Low Voltage (Vol)                          |                          |      | 0.2                    | V    | $I_{SINK} = 200 \mu\text{A}$                                                                                                         |

| Floating-State Leakage Current                    |                          |      | ±10                    | μΑ   | · ·                                                                                                                                  |

| Floating-State Output Capacitance <sup>2</sup>    |                          |      | 10                     | pF   |                                                                                                                                      |

| Output Coding                                     | Two                      | S    |                        |      |                                                                                                                                      |

| , ,                                               | complei                  | ment |                        |      |                                                                                                                                      |

| CONVERSION RATE                                   |                          |      |                        |      |                                                                                                                                      |

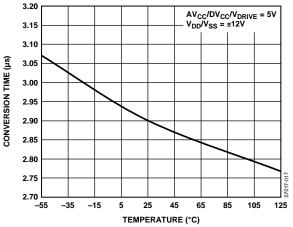

| Conversion Time                                   |                          |      | 3.1                    | μs   |                                                                                                                                      |

| Track-and-Hold Acquisition Time <sup>1,2</sup>    |                          |      | 550                    | ns   |                                                                                                                                      |

| Throughput Rate                                   |                          |      | 250                    | kSPS | Parallel interface mode only                                                                                                         |

| POWER REQUIREMENTS                                |                          |      |                        |      |                                                                                                                                      |

| $V_{DD}$                                          | -5                       |      | +16.5                  | V    | For the $4 \times V_{REF}$ range, $V_{DD} = 10 \text{ V}$ to 16.5 V                                                                  |

| $V_{SS}$                                          | -5                       |      | -16.5                  | V    | For the $4 \times V_{REF}$ range, $V_{SS} = -10 \text{ V}$ to $-16.5 \text{ V}$                                                      |

| $AV_{CC}$                                         | 4.75                     |      | 5.25                   | V    |                                                                                                                                      |

| $DV_CC$                                           | 4.75                     |      | 5.25                   | V    |                                                                                                                                      |

| $V_{DRIVE}$                                       | 2.7                      |      | 5.25                   | V    |                                                                                                                                      |

| I <sub>TOTAL</sub> <sup>3</sup>                   |                          |      |                        |      | Digital inputs = 0 V or V <sub>DRIVE</sub>                                                                                           |

| Normal Mode—Static                                |                          |      | 18                     | mA   | $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$                                |

| Normal Mode—Operational                           |                          |      | 26                     | mA   | $f_{SAMPLE} = 250 \text{ kSPS}, AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$ |

| Iss (Operational)                                 |                          |      | 0.25                   | mA   | $V_{SS} = -16.5 \text{ V}, f_{SAMPLE} = 250 \text{ kSPS}$                                                                            |

| IDD (Operational)                                 |                          |      | 0.25                   | mA   | $V_{DD} = +16.5 \text{ V}, f_{SAMPLE} = 250 \text{ kSPS}$                                                                            |

| Partial Power-Down Mode                           |                          |      | 7                      | mA   | $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$                                |

| Full Power-Down Mode (STBY Pin)                   |                          |      | 60                     | μΑ   | SCLK on or off, $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V},$<br>$V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$           |

| Power Dissipation                                 |                          |      |                        |      | $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$                                |

| Normal Mode—Static                                |                          |      | 94                     | mW   |                                                                                                                                      |

| Normal Mode—Operational                           |                          |      | 140                    | mW   | f <sub>SAMPLE</sub> = 250 kSPS                                                                                                       |

| Partial Power-Down Mode                           |                          |      | 40                     | mW   |                                                                                                                                      |

| Full Power-Down Mode (STBY Pin)                   |                          |      | 315                    | μW   |                                                                                                                                      |

<sup>&</sup>lt;sup>1</sup> See the Terminology section. <sup>2</sup> Sample tested during initial release to ensure compliance. <sup>3</sup> Includes I<sub>AVCC</sub>, I<sub>VDD</sub>, I<sub>VSS</sub>, I<sub>VDRIVE</sub>, and I<sub>DVCC</sub>.

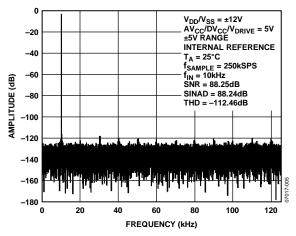

### AD7657-1

$V_{REF} = 2.5 \text{ V internal/external, } AV_{CC} = 4.75 \text{ V to } 5.25 \text{ V, } DV_{CC} = 4.75 \text{ V to } 5.25 \text{ V, } DV_{CC} = 2.7 \text{ V to } 5.25 \text{ V; } for the \pm 4 \times V_{REF} \, range, V_{DD} = 10 \text{ V to } 16.5 \text{ V; } V_{SS} = -10 \text{ V to } -16.5 \text{ V; } for the \pm 2 \times V_{REF} \, range, V_{DD} = 5 \text{ V to } 16.5 \text{ V; } V_{SS} = -5 \text{ V to } -16.5 \text{ V; } f_{SAMPLE} = 250 \text{ kSPS, } T_A = T_{MIN} \, to T_{MAX}, \, unless \, otherwise \, noted.$

Table 2.

| Parameter                                              | Min                    | Тур  | Max                    | Unit   | Test Conditions/Comments                                                |

|--------------------------------------------------------|------------------------|------|------------------------|--------|-------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                                    |                        |      |                        |        | f <sub>IN</sub> = 10 kHz sine wave                                      |

| Signal-to-(Noise + Distortion)<br>(SINAD) <sup>1</sup> |                        | 82.5 |                        | dB     |                                                                         |

| Signal-to-Noise Ratio (SNR) <sup>1</sup>               |                        | 83.5 |                        | dB     |                                                                         |

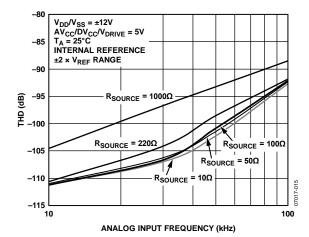

| Total Harmonic Distortion (THD)1                       |                        |      | -90                    | dB     |                                                                         |

|                                                        |                        | -105 |                        | dB     |                                                                         |

| Peak Harmonic or Spurious Noise (SFDR) <sup>1</sup>    |                        | -100 |                        | dB     |                                                                         |

| Intermodulation Distortion (IMD) <sup>1</sup>          |                        |      |                        |        | fa = 10.5 kHz, fb = 9.5 kHz                                             |

| Second-Order Terms                                     |                        | -109 |                        | dB     |                                                                         |

| Third-Order Terms                                      |                        | -104 |                        | dB     |                                                                         |

| Aperture Delay                                         |                        |      | 10                     | ns     |                                                                         |

| Aperture Delay Matching                                |                        |      | 4                      | ns     |                                                                         |

| Aperture Jitter                                        |                        | 35   |                        | ps     |                                                                         |

| Channel-to-Channel Isolation <sup>1</sup>              |                        | -100 |                        | dB     | f <sub>IN</sub> on unselected channels up to 100 kHz                    |

| Full-Power Bandwidth                                   |                        | 4.5  |                        | MHz    | @ -3 dB                                                                 |

|                                                        |                        | 2.2  |                        | MHz    | @ -0.1 dB                                                               |

| DC ACCURACY                                            |                        | -    |                        |        |                                                                         |

| Resolution                                             | 14                     |      |                        | Bits   |                                                                         |

| No Missing Codes                                       | 14                     |      |                        | Bits   |                                                                         |

| Integral Nonlinearity <sup>1</sup>                     |                        |      | ±1                     | LSB    |                                                                         |

| eg.aeay                                                |                        | ±1   |                        |        |                                                                         |

| Positive Full-Scale Error <sup>1</sup>                 |                        |      | ±0.95                  | % FSR  | ±0.27% FSR typical                                                      |

| Positive Full-Scale Error Matching <sup>1</sup>        |                        |      | ±0.366                 | % FSR  |                                                                         |

| Bipolar Zero-Scale Error <sup>1</sup>                  |                        |      | ±0.04                  | % FSR  | ±0.016% FSR typical                                                     |

| Bipolar Zero-Scale Error Matching <sup>1</sup>         |                        |      | ±0.0427                | % FSR  | ±0.010701 Sh typical                                                    |

| Negative Full-Scale Error <sup>1</sup>                 |                        |      | ±0.0427                | % FSR  | ±0.27% FSR typical                                                      |

| Negative Full-Scale Error Matching <sup>1</sup>        |                        |      | ±0.366                 | % FSR  | ±0.27 /01 Sit typical                                                   |

| ANALOG INPUT                                           |                        |      | ±0.500                 | 701311 | See Table 8 for minimum V <sub>DD</sub> /V <sub>SS</sub> for each range |

| Input Voltage Ranges                                   | -4×V <sub>REE</sub>    |      | $+4 \times V_{REF}$    | V      | RNGx bits or RANGE pin = 0                                              |

| input voltage hanges                                   | -2 × V <sub>REF</sub>  |      | $+2 \times V_{REF}$    | V      | RNGx bits or RANGE pin = 1                                              |

| DC Leakage Current                                     | -Z × V REF             |      | ±1                     | μA     | MINOX BITS OF MAINGE PILL = 1                                           |

| Input Capacitance <sup>2</sup>                         |                        | 10   | エリ                     | pF     | ±4 × V <sub>REF</sub> range when in track                               |

| input Capacitance                                      |                        | 14   |                        | -      |                                                                         |

| REFERENCE INPUT/OUTPUT                                 |                        | 14   |                        | pF     | ±2 × V <sub>REF</sub> range when in track                               |

|                                                        | 2.5                    |      | 2.5                    | V      |                                                                         |

| Reference Input Voltage Range                          | 2.5                    |      |                        | -      |                                                                         |

| DC Leakage Current                                     |                        | 10.5 | ±1                     | μΑ     | DES 4                                                                   |

| Input Capacitance <sup>2</sup>                         |                        | 18.5 |                        | pF     | REF <sub>EN/DIS</sub> = 1                                               |

| Reference Output Voltage                               | 2.49                   |      | 2.51                   | V      |                                                                         |

| Long-Term Stability                                    |                        | 150  |                        | ppm    | 1000 hours                                                              |

| Reference Temperature Coefficient                      |                        |      | 25                     | ppm/°C |                                                                         |

|                                                        |                        | 6    |                        | ppm/°C |                                                                         |

| LOGIC INPUTS                                           |                        |      |                        |        |                                                                         |

| Input High Voltage (V <sub>INH</sub> )                 | $0.7 \times V_{DRIVE}$ |      |                        | V      |                                                                         |

| Input Low Voltage (V <sub>INL</sub> )                  |                        |      | $0.3 \times V_{DRIVE}$ | V      |                                                                         |

| Input Current (I <sub>IN</sub> )                       |                        |      | ±10                    | μΑ     | Typically 10 nA, $V_{IN} = 0 \text{ V or } V_{DRIVE}$                   |

| Input Capacitance (C <sub>IN</sub> ) <sup>2</sup>      |                        |      | 10                     | pF     |                                                                         |

| Parameter                                      | Min                      | Тур  | Max   | Unit | Test Conditions/Comments                                                                                                             |

|------------------------------------------------|--------------------------|------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS                                  |                          |      |       |      |                                                                                                                                      |

| Output High Voltage (V <sub>OH</sub> )         | V <sub>DRIVE</sub> - 0.2 |      |       | V    | $I_{SOURCE} = 200 \mu\text{A}$                                                                                                       |

| Output Low Voltage (Vol)                       |                          |      | 0.2   | V    | $I_{SINK} = 200 \mu\text{A}$                                                                                                         |

| Floating-State Leakage Current                 |                          |      | ±10   | μΑ   |                                                                                                                                      |

| Floating-State Output Capacitance <sup>2</sup> |                          |      | 10    | рF   |                                                                                                                                      |

| Output Coding                                  | Two                      | S    |       |      |                                                                                                                                      |

|                                                | complei                  | ment |       |      |                                                                                                                                      |

| CONVERSION RATE                                |                          |      |       |      |                                                                                                                                      |

| Conversion Time                                |                          |      | 3.1   | μs   |                                                                                                                                      |

| Track-and-Hold Acquisition Time <sup>1,2</sup> |                          |      | 550   | ns   |                                                                                                                                      |

| Throughput Rate                                |                          |      | 250   | kSPS | Parallel interface mode only                                                                                                         |

| POWER REQUIREMENTS                             |                          |      |       |      |                                                                                                                                      |

| $V_{DD}$                                       | -5                       |      | +16.5 | V    | For the $4 \times V_{REF}$ range, $V_{DD} = 10 \text{ V}$ to $16.5 \text{ V}$                                                        |

| $V_{SS}$                                       | -5                       |      | -16.5 | V    | For the $4 \times V_{REF}$ range, $V_{SS} = -10 \text{ V}$ to $-16.5 \text{ V}$                                                      |

| <b>AV</b> cc                                   | 4.75                     |      | 5.25  | V    |                                                                                                                                      |

| $DV_CC$                                        | 4.75                     |      | 5.25  | V    |                                                                                                                                      |

| $V_{DRIVE}$                                    | 2.7                      |      | 5.25  | V    |                                                                                                                                      |

| I <sub>TOTAL</sub> <sup>3</sup>                |                          |      |       |      | Digital inputs = 0 V or V <sub>DRIVE</sub>                                                                                           |

| Normal Mode—Static                             |                          |      | 18    | mA   | $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$                                |

| Normal Mode—Operational                        |                          |      | 26    | mA   | $f_{SAMPLE} = 250 \text{ kSPS}, AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$ |

| Iss (Operational)                              |                          |      | 0.25  | mA   | $V_{SS} = -16.5 \text{ V}, f_{SAMPLE} = 250 \text{ kSPS}$                                                                            |

| IDD (Operational)                              |                          |      | 0.25  | mA   | $V_{DD} = 16.5 \text{ V}, f_{SAMPLE} = 250 \text{ kSPS}$                                                                             |

| Partial Power-Down Mode                        |                          |      | 7     | mA   | $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$                                |

| Full Power-Down Mode (STBY Pin)                |                          |      | 60    | μΑ   | SCLK on or off, $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V},$<br>$V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$           |

| Power Dissipation                              |                          |      |       |      | $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$                                |

| Normal Mode—Static                             |                          |      | 94    | mW   |                                                                                                                                      |

| Normal Mode—Operational                        |                          |      | 140   | mW   | f <sub>SAMPLE</sub> = 250 kSPS                                                                                                       |

| Partial Power-Down Mode                        |                          |      | 40    | mW   |                                                                                                                                      |

| Fu <u>ll Pow</u> er-Down Mode<br>(STBY Pin)    |                          |      | 315   | μW   |                                                                                                                                      |

<sup>&</sup>lt;sup>1</sup> See the Terminology section. <sup>2</sup> Sample tested during initial release to ensure compliance. <sup>3</sup> Includes I<sub>AVCC</sub>, I<sub>VDD</sub>, I<sub>VSS</sub>, I<sub>VDRIVE</sub>, and I<sub>DVCC</sub>.

### AD7658-1

$V_{REF} = 2.5 \text{ V internal/external}, AV_{CC} = 4.75 \text{ V to } 5.25 \text{ V}, DV_{CC} = 4.75 \text{ V to } 5.25 \text{ V}, V_{DRIVE} = 2.7 \text{ V to } 5.25 \text{ V}; \text{ for } \pm 4 \times V_{REF} \text{ range}, V_{DD} = 10 \text{ V to } 16.5 \text{ V}, V_{SS} = -10 \text{ V to } -16.5 \text{ V}; \text{ for } \pm 2 \times V_{REF} \text{ range}, V_{DD} = 5 \text{ V to } 16.5 \text{ V}, V_{SS} = -5 \text{ V to } -16.5 \text{ V}; f_{SAMPLE} = 250 \text{ kSPS}, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted}.$

Table 3.

| Parameter                                              | Min                    | Тур  | Max                    | Unit     | Test Conditions/Comments                                                |

|--------------------------------------------------------|------------------------|------|------------------------|----------|-------------------------------------------------------------------------|

| DYNAMIC PERFORMANCE                                    |                        |      |                        |          | f <sub>IN</sub> = 10 kHz sine wave                                      |

| Signal-to-(Noise + Distortion)<br>(SINAD) <sup>1</sup> |                        | 73.5 |                        | dB       |                                                                         |

|                                                        |                        | 73.5 |                        | dB       |                                                                         |

| Total Harmonic Distortion (THD) <sup>1</sup>           |                        |      | -88                    | dB       |                                                                         |

|                                                        |                        | -100 |                        | dB       |                                                                         |

| Peak Harmonic or Spurious Noise<br>(SFDR) <sup>1</sup> |                        | -97  |                        | dB       |                                                                         |

| Intermodulation Distortion (IMD) <sup>1</sup>          |                        |      |                        |          | fa = 10.5 kHz, fb = 9.5 kHz                                             |

| Second-Order Terms                                     |                        | -106 |                        | dB       |                                                                         |

| Third-Order Terms                                      |                        | -101 |                        | dB       |                                                                         |

| Aperture Delay                                         |                        |      | 10                     | ns       |                                                                         |

| Aperture Delay Matching                                |                        |      | 4                      | ns       |                                                                         |

| Aperture Jitter                                        |                        | 35   |                        | ps       |                                                                         |

| Channel-to-Channel Isolation <sup>1</sup>              |                        | -100 |                        | dB       | f <sub>IN</sub> on unselected channels up to 100 kHz                    |

| Full-Power Bandwidth                                   |                        | 4.5  |                        | MHz      | @ -3 dB                                                                 |

|                                                        |                        | 2.2  |                        | MHz      | @ -0.1 dB                                                               |

| DC ACCURACY                                            |                        | -    |                        |          |                                                                         |

| Resolution                                             | 12                     |      |                        | Bits     |                                                                         |

| No Missing Codes                                       | 12                     |      |                        | Bits     |                                                                         |

| Differential Nonlinearity                              |                        |      | ±0.7                   | LSB      |                                                                         |

| Integral Nonlinearity <sup>1</sup>                     |                        |      | ±0.5                   | LSB      |                                                                         |

| Positive Full-Scale Error <sup>1</sup>                 |                        |      | ±0.95                  | % FSR    | ±0.317% FSR typical                                                     |

| Positive Full-Scale Error Matching <sup>1</sup>        |                        |      | ±0.366                 | % FSR    | ±0.517 /01 5ht typical                                                  |

| Bipolar Zero-Scale Error <sup>1</sup>                  |                        |      | ±0.500<br>±2           | LSB      | ±0.0125% FSR typical                                                    |

| Bipolar Zero-Scale Error Matching <sup>1</sup>         |                        |      | ±2                     | LSB      | ±0.0125 /01 511 typical                                                 |

| Negative Full-Scale Error <sup>1</sup>                 |                        |      | ±0.95                  | % FSR    | ±0.317% FSR typical                                                     |

| Negative Full-Scale Error Matching <sup>1</sup>        |                        |      | ±0.95<br>±0.366        | % FSR    | ±0.317% F3N typical                                                     |

| ANALOG INPUT                                           |                        |      | ±0.300                 | 70 1 311 | See Table 8 for minimum V <sub>DD</sub> /V <sub>SS</sub> for each range |

|                                                        | $-4 \times V_{REF}$    |      | $+4 \times V_{REF}$    | V        | RNGx bits or RANGE pin = 0                                              |

| Input Voltage Ranges                                   |                        |      |                        |          | ·                                                                       |

| DC Lastra Comment                                      | $-2 \times V_{REF}$    |      | $+2 \times V_{REF}$    | V        | RNGx bits or RANGE pin = 1                                              |

| DC Leakage Current                                     |                        | 10   | ±1                     | μΑ       | LAW LAW L                                                               |

| Input Capacitance <sup>2</sup>                         |                        | 10   |                        | _        | ±4 × V <sub>REF</sub> range when in track                               |

|                                                        |                        | 14   |                        | pF       | ±2 × V <sub>REF</sub> range when in track                               |

| REFERENCE INPUT/OUTPUT                                 |                        |      |                        |          |                                                                         |

| Reference Input Voltage Range                          | 2.5                    |      | 2.5                    | V        |                                                                         |

| DC Leakage Current                                     |                        |      | ±1                     | μΑ       |                                                                         |

| Input Capacitance <sup>2</sup>                         |                        | 18.5 |                        | pF       | $REF_{EN/\overline{DIS}} = 1$                                           |

| Reference Output Voltage                               | 2.49                   |      | 2.51                   | V        |                                                                         |

| Long-Term Stability                                    |                        | 150  |                        | ppm      | 1000 hours                                                              |

| Reference Temperature Coefficient                      |                        |      | 25                     | ppm/°C   |                                                                         |

|                                                        |                        | 6    |                        | ppm/°C   |                                                                         |

| LOGIC INPUTS                                           |                        |      |                        |          |                                                                         |

| Input High Voltage (V <sub>INH</sub> )                 | $0.7 \times V_{DRIVE}$ |      |                        | V        |                                                                         |

| Input Low Voltage (V <sub>INL</sub> )                  |                        |      | $0.3 \times V_{DRIVE}$ | V        |                                                                         |

| Input Current (I <sub>IN</sub> )                       |                        |      | ±10                    | μΑ       | Typically 10 nA, $V_{IN} = 0 \text{ V or } V_{DRIVE}$                   |

| Input Capacitance (C <sub>IN</sub> ) <sup>2</sup>      |                        |      | 10                     | pF       |                                                                         |

| Parameter                                         | Min                      | Тур | Max   | Unit | Test Conditions/Comments                                                                                                             |

|---------------------------------------------------|--------------------------|-----|-------|------|--------------------------------------------------------------------------------------------------------------------------------------|

| LOGIC OUTPUTS                                     |                          |     |       |      |                                                                                                                                      |

| Output High Voltage (Vон)                         | V <sub>DRIVE</sub> - 0.2 |     |       | V    | $I_{SOURCE} = 200 \mu\text{A}$                                                                                                       |

| Output Low Voltage (Vol)                          |                          |     | 0.2   | V    | $I_{SINK} = 200 \mu A$                                                                                                               |

| Floating-State Leakage Current                    |                          |     | ±10   | μΑ   |                                                                                                                                      |

| Floating-State Output<br>Capacitance <sup>2</sup> |                          |     | 10    | pF   |                                                                                                                                      |

| Output Coding                                     | Two<br>comple            |     |       |      |                                                                                                                                      |

| CONVERSION RATE                                   |                          |     |       |      |                                                                                                                                      |

| Conversion Time                                   |                          |     | 3.1   | μs   |                                                                                                                                      |

| Track-and-Hold Acquisition Time <sup>1,2</sup>    |                          |     | 550   | ns   |                                                                                                                                      |

| Throughput Rate                                   |                          |     | 250   | kSPS | Parallel interface mode only                                                                                                         |

| POWER REQUIREMENTS                                |                          |     |       |      |                                                                                                                                      |

| $V_{DD}$                                          | -5                       |     | +16.5 | V    | For the $4 \times V_{REF}$ range, $V_{DD} = 10 \text{ V}$ to $16.5 \text{ V}$                                                        |

| $V_{SS}$                                          | -5                       |     | -16.5 | V    | For the $4 \times V_{REF}$ range, $V_{SS} = -10 \text{ V}$ to $-16.5 \text{ V}$                                                      |

| <b>AV</b> cc                                      | 4.75                     |     | 5.25  | V    |                                                                                                                                      |

| $DV_CC$                                           | 4.75                     |     | 5.25  | V    |                                                                                                                                      |

| V <sub>DRIVE</sub>                                | 2.7                      |     | 5.25  | V    |                                                                                                                                      |

| I <sub>TOTAL</sub> <sup>3</sup>                   |                          |     |       |      | Digital inputs = 0 V or V <sub>DRIVE</sub>                                                                                           |

| Normal Mode—Static                                |                          |     | 18    | mA   | $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$                                |

| Normal Mode—Operational                           |                          |     | 26    | mA   | $f_{SAMPLE} = 250 \text{ kSPS}, AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$ |

| Iss (Operational)                                 |                          |     | 0.25  | mA   | $V_{SS} = -16.5 \text{ V}, f_{SAMPLE} = 250 \text{ kSPS}$                                                                            |

| I <sub>DD</sub> (Operational)                     |                          |     | 0.25  | mA   | $V_{DD} = 16.5 \text{ V}, f_{SAMPLE} = 250 \text{ kSPS}$                                                                             |

| Partial Power-Down Mode                           |                          |     | 7     | mA   | $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$                                |

| Full Power-Down Mode (STBY Pin)                   |                          |     | 60    | μΑ   | SCLK on or off, $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V},$<br>$V_{DD} = +16.5 \text{ V}, V_{SS} = -16.5 \text{ V}$           |

| Power Dissipation                                 |                          |     |       |      | $AV_{CC} = DV_{CC} = V_{DRIVE} = +5.25 \text{ V}, V_{DD} = +16.5 \text{ V},$<br>$V_{SS} = -16.5 \text{ V}$                           |

| Normal Mode—Static                                |                          |     | 94    | mW   |                                                                                                                                      |

| Normal Mode—Operational                           |                          |     | 140   | mW   | f <sub>SAMPLE</sub> = 250 kSPS                                                                                                       |

| Partial Power-Down Mode                           |                          |     | 40    | mW   |                                                                                                                                      |

| Full <u>Pow</u> er-Down Mode<br>(STBY Pin)        |                          |     | 315   | μW   |                                                                                                                                      |

<sup>&</sup>lt;sup>1</sup> See the Terminology section. <sup>2</sup> Sample tested during initial release to ensure compliance. <sup>3</sup> Includes I<sub>AVCC</sub>, I<sub>VDD</sub>, I<sub>VSS</sub>, I<sub>VDRIVE</sub>, and I<sub>DVCC</sub>.

### **TIMING SPECIFICATIONS**

$AV_{CC}$  and  $DV_{CC} = 4.75 \text{ V}$  to 5.25 V,  $V_{DD} = 5 \text{ V}$  to 16.5 V,  $V_{SS} = -5 \text{ V}$  to -16.5 V,  $V_{DRIVE} = 2.7 \text{ V}$  to 5.25 V,  $V_{REF} = 2.5 \text{ V}$  internal/external,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 4.

|                              | Limit at t <sub>MIN</sub> , t <sub>MAX</sub> |                                         |         |                                                                                 |

|------------------------------|----------------------------------------------|-----------------------------------------|---------|---------------------------------------------------------------------------------|

| Parameter <sup>1</sup>       | $V_{DRIVE}$ < 4.75 $V$                       | $V_{DRIVE} = 4.75 V \text{ to } 5.25 V$ | Unit    | Description                                                                     |

| PARALLEL INTERFACE           |                                              |                                         |         |                                                                                 |

| tconvert                     | 3                                            | 3                                       | μs typ  | Conversion time, internal clock                                                 |

| t <sub>QUIET</sub>           | 150                                          | 150                                     | ns min  | Minimum quiet time required between bus relinquish and start of next conversion |

| t <sub>ACQ</sub>             | 550                                          | 550                                     | ns min  | Acquisition time                                                                |

| t <sub>10</sub>              | 25                                           | 25                                      | ns min  | Minimum CONVST low pulse                                                        |

| $t_1$                        | 60                                           | 60                                      | ns max  | CONVST high to BUSY high                                                        |

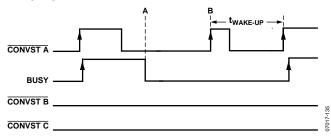

| t <sub>wake-up</sub>         | 2                                            | 2                                       | ms max  | STBY rising edge to CONVST rising edge                                          |

|                              | 25                                           | 25                                      | μs max  | Partial power-down mode                                                         |

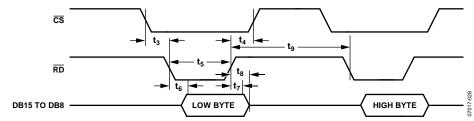

| PARALLEL READ OPERATION      |                                              |                                         |         |                                                                                 |

| $t_2$                        | 0                                            | 0                                       | ns min  | BUSY to RD delay                                                                |

| $t_3$                        | 0                                            | 0                                       | ns min  | CS to RD setup time                                                             |

| t <sub>4</sub>               | 0                                            | 0                                       | ns min  | CS to RD hold time                                                              |

| <b>t</b> 5                   | 45                                           | 36                                      | ns min  | RD pulse width                                                                  |

| t <sub>6</sub>               | 45                                           | 36                                      | ns max  | Data access time after RD falling edge                                          |

| $t_7$                        | 10                                           | 10                                      | ns min  | Data hold time after RD rising edge                                             |

| t <sub>8</sub>               | 12                                           | 12                                      | ns max  | Bus relinquish time after RD rising edge                                        |

| <b>t</b> <sub>9</sub>        | 6                                            | 6                                       | ns min  | Minimum time between reads                                                      |

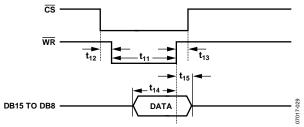

| PARALLEL WRITE OPERATION     |                                              |                                         |         |                                                                                 |

| t <sub>11</sub>              | 15                                           | 15                                      | ns min  | WR pulse width                                                                  |

| t <sub>12</sub>              | 0                                            | 0                                       | ns min  | CS to WR setup time                                                             |

| <b>t</b> <sub>13</sub>       | 5                                            | 5                                       | ns min  | CS to WR hold time                                                              |

| t <sub>14</sub>              | 5                                            | 5                                       | ns min  | Data setup time before WR rising edge                                           |

| t <sub>15</sub>              | 5                                            | 5                                       | ns min  | Data hold after WR rising edge                                                  |

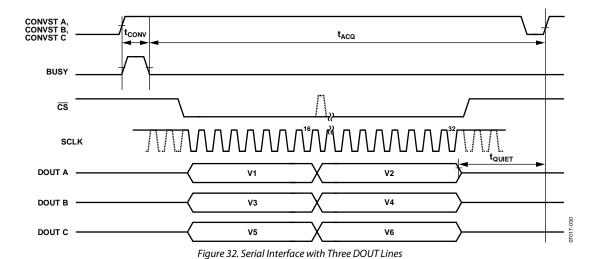

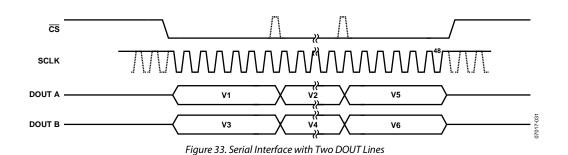

| SERIAL INTERFACE             |                                              |                                         |         |                                                                                 |

| f <sub>SCLK</sub>            | 18                                           | 18                                      | MHz max | Frequency of serial read clock                                                  |

| t <sub>16</sub>              | 12                                           | 12                                      | ns max  | Delay from CS until DOUTx three-state disabled                                  |

| t <sub>17</sub> <sup>2</sup> | 22                                           | 22                                      | ns max  | Data access time after SCLK rising edge/CS falling edge                         |

| t <sub>18</sub>              | $0.4 \times t_{SCLK}$                        | $0.4 \times t_{SCLK}$                   | ns min  | SCLK low pulse width                                                            |

| <b>t</b> <sub>19</sub>       | $0.4 \times t_{SCLK}$                        | 0.4 × t <sub>SCLK</sub>                 | ns min  | SCLK high pulse width                                                           |

| t <sub>20</sub>              | 10                                           | 10                                      | ns min  | SCLK to data valid hold time after SCLK falling edge                            |

| t <sub>21</sub>              | 18                                           | 18                                      | ns max  | CS rising edge to DOUTx high impedance                                          |

$<sup>^{1}</sup>$  Sample tested during initial release to ensure compliance. All input signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of 1.6 V.

<sup>&</sup>lt;sup>2</sup> A buffer is used on the DOUTx pins (Pin 5 to Pin 7) for this measurement.

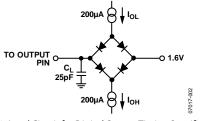

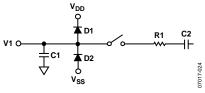

Figure 2. Load Circuit for Digital Output Timing Specifications

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 5.

| 1 abic 5.                                 |                                                     |

|-------------------------------------------|-----------------------------------------------------|

| Parameter                                 | Rating                                              |

| V <sub>DD</sub> to AGND, DGND             | -0.3 V to +16.5 V                                   |

| V <sub>SS</sub> to AGND, DGND             | +0.3 V to -16.5 V                                   |

| V <sub>DD</sub> to AV <sub>CC</sub>       | $V_{CC} - 0.3 \text{ V to} + 16.5 \text{ V}$        |

| AVcc to AGND, DGND                        | −0.3 V to +7 V                                      |

| DV <sub>cc</sub> to AV <sub>cc</sub>      | $-0.3 \text{ V to AV}_{CC} + 0.3 \text{ V}$         |

| DV <sub>cc</sub> to DGND, AGND            | −0.3 V to +7 V                                      |

| AGND to DGND                              | -0.3 V to +0.3 V                                    |

| V <sub>DRIVE</sub> to DGND                | $-0.3 \text{ V to DV}_{CC} + 0.3 \text{ V}$         |

| Analog Input Voltage to AGND <sup>1</sup> | $V_{SS} - 0.3 \text{ V to } V_{DD} + 0.3 \text{ V}$ |

| Digital Input Voltage to DGND             | $-0.3 \text{ V to V}_{DRIVE} + 0.3 \text{ V}$       |

| Digital Output Voltage to DGND            | $-0.3 \text{ V}$ to $V_{DRIVE} + 0.3 \text{ V}$     |

| REFIN/REFOUT to AGND                      | $-0.3 \text{ V to AV}_{CC} + 0.3 \text{ V}$         |

| Input Current to Any Pin Except           |                                                     |

| Supplies <sup>2</sup>                     | ±10 mA                                              |

| Operating Temperature Range               |                                                     |

| B Version                                 | −40°C to +85°C                                      |

| Y Version                                 | −40°C to +125°C                                     |

| Storage Temperature Range                 | −65°C to +150°C                                     |

| Junction Temperature                      | 150°C                                               |

| Pb/Sn Temperature, Soldering              |                                                     |

| Reflow (10 sec to 30 sec)                 | 240(+0)°C                                           |

| Pb-Free Temperature, Soldering Reflow     | 260(+0)°C                                           |

| ESD                                       | 1.5 kV                                              |

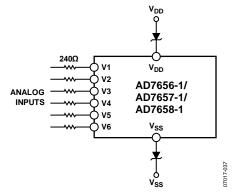

$<sup>^1</sup>$  If the analog inputs are driven from alternative  $V_{DD}$  and  $V_{SS}$  supply circuitry, a  $240\,\Omega$  series resistor should be placed on the analog inputs and Schottky diodes should be placed in series with the  $V_{DD}$  and  $V_{SS}$  supplies of the AD7656-1/AD7657-1/AD7658-1.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages. These specifications apply to a 4-layer board.

**Table 6. Thermal Resistance**

| Package Type | θ <sub>JA</sub> | θις | Unit |

|--------------|-----------------|-----|------|

| 64-Lead LQFP | 45              | 11  | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

<sup>&</sup>lt;sup>2</sup> Transient currents of up to 100 mA do not cause SCR latch-up.

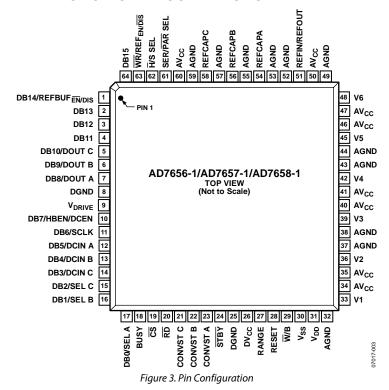

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

**Table 7. Pin Function Descriptions**

| Pin No.                                          | Mnemonic                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 54, 56, 58                                       | REFCAPA, REFCAPB,<br>REFCAPC    | Reference Capacitor A, Reference Capacitor B, and Reference Capacitor C. Decoupling capacitors are connected to these pins to decouple the reference buffer for each ADC pair. Decouple each REFCAP pin to AGND using a 1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                                                                                                                              |

| 33, 36, 39,<br>42, 45, 48                        | V1 to V6                        | Analog Input 1 to Analog Input 6. These pins are single-ended analog inputs. In hardware mode, the analog input range of these channels is determined by the RANGE pin. In software mode, it is determined by the RNGC to RNGA bits of the control register (see Table 11).                                                                                                                                                                                                                                                                                                                                               |

| 32, 37, 38, 43,<br>44, 49, 52, 53,<br>55, 57, 59 | AGND                            | Analog Ground. This pin is the ground reference point for all analog circuitry on the AD7656-1/AD7657-1/AD7658-1. Refer all analog input signals and external reference signals to this pin.  Connect all AGND pins to the AGND plane of the system. The AGND and DGND voltages should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis.                                                                                                                                                                                                                                 |

| 26                                               | DV <sub>cc</sub>                | Digital Power, 4.75 V to 5.25 V. The DV <sub>CC</sub> and AV <sub>CC</sub> voltages should ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis. Decouple this supply to DGND by placing a 1 $\mu$ F decoupling capacitor on the DV <sub>CC</sub> pin.                                                                                                                                                                                                                                                                                                                       |