Figure 1. Z84013/015 Version

Figure 2. Z84C13/C15 Version

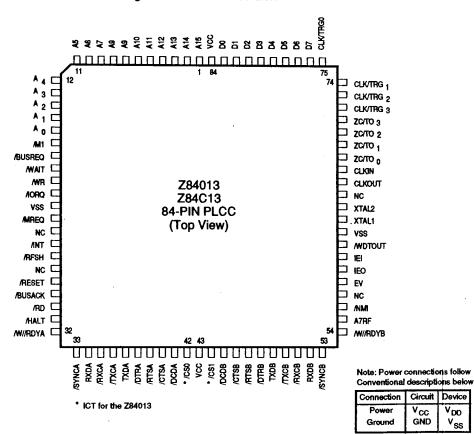

Figure 3. Z84013/Z84C13 Pin-out Assignments

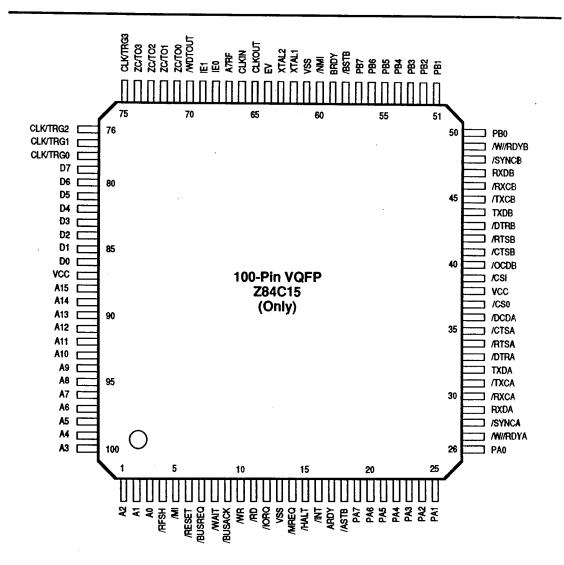

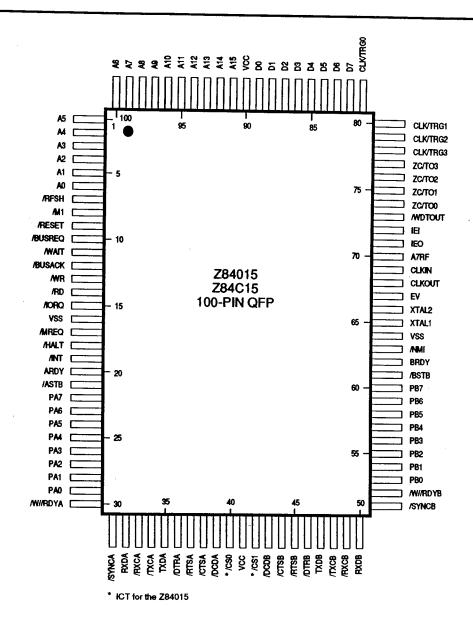

**Z84C15 Pin-out Assignments**

Figure 4. Z84015/Z84C15 Pin-out Assignments

# **PIN DEFINITIONS**

The pin assignment for each device is shown in Figures 3 and 4. Following is the description on each pin. For the description and the pin number, if stated as "x13" or "x15",

that applies to both Z84C13/Z84013 or Z84C15/Z84015. Otherwise, C13 for Z84C13, C15 for Z84C15, 013 for Z84013 and 015 for Z84015.

# **CPU SIGNALS**

| Pin Name   | Pin Number                     | Input/Output, 3-State | Function                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------|--------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A15     | 16-1(x13),<br>6-1, 100-91(x15) | I/O                   | 16-bit address bus. Specifies I/O and memory addresses to be accessed. During the refresh period, addresses for refreshing are output. The bus is an input when the external master is accessing the on-chip peripherals.                                                                                                                                                                                                         |

| D0-D7      | 83-76(x13),<br>89-82(x15)      | I/O                   | 8-bit bidirectional data bus. When the on-chip CPU is accessing on-chip peripherals, these lines are set to output and hold the data to/from on-chip peripherals.                                                                                                                                                                                                                                                                 |

| /RD        | 30(x13), 14(x15)               | I/O                   | Read signal. CPU read signal for accepting data from memory or I/O devices. When an external master is accessing the on-chip peripherals, it is an input signal.                                                                                                                                                                                                                                                                  |

| <b>W</b> Ŕ | 20(x13), 13(x15)               | I/O                   | Write Signal. This signal is output when data, to be stored in a specified memory or peripheral LSI, is on the MPU data bus. When an external master is accessing the on-chip peripherals, it is an input signal.                                                                                                                                                                                                                 |

| /MREQ      | 23(x13), 17(x15)               | I/O, 3-State          | Memory request signal. When an effective address for memory access is on the address bus, "0" is output. When an external master is accessing the on-chip peripherals, it is an tristate signal.                                                                                                                                                                                                                                  |

| /IORQ      | 21(x13), 15(x15)               | 1/O                   | I/O request signal. When addresses for I/O are on the lower 8 bits (A7-A0) of the address bus in the I/O operation, "0" is output. In addition, the /IORO signal is output with the /M1 signal at the time of interrupt acknowledge cycle to inform peripheral LSI of the state of the interrupt response vector is when put on the data bus. When an external master is accessing the onchip peripherals, it is an input signal. |

| /M1        | 17(×13), 8(×15)                | I/O                   | Machine cycle "1". /MREQ and "0" are putput together in the operation code fetch cycle. /M1 is output for every opcode fetch when a two byte opcode is executed. In the maskable interrupt acknowledge cycle, this signal is output together with /IORQ. It is 3-stated in EV mode.                                                                                                                                               |

| CPU SIGNALS | (Continued) |

|-------------|-------------|

|-------------|-------------|

| Pin Name          | Pin Number                    | Input/Output, 3-State                      | Function                                                                                                                                                                                                                                                                                                                                             |

|-------------------|-------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /RFSH             | 26(x13), 7(x15)               | Out, 3-State                               | The refresh signal. When the dynamic memory refresh address is on the low order byte of the address bus, /RFSH is active along with /MREQ signal. This pin is 3-stated in EV mode.                                                                                                                                                                   |

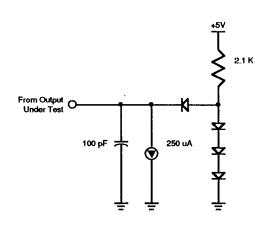

| /INT              | 25(x13), 19(x15)              | Open drain                                 | Maskable interrupt request signal. Interrupt is generated by peripheral LSI. This signal is accepted if the interrupt enable Flip-Flop (IFF) is set to "1". The /INT signal of on-chip peripherals is internally wired - OR without pull-up resistors and requires external pull-up. Also, interrupts from on-chip peripherals go out from this pin. |

| /NMI              | 56(x13), 63(x15)              | ln ·                                       | Non-maskable interrupt request signal. This interrupt request has a higher priority than the maskable interrupt request and does not rely upon the state of the interrupt enable Flip-Flop (IFF).                                                                                                                                                    |

| /HALT             | 31(x13), 81(x15)              | Out, 3-State                               | Halt signal. Indicates that the CPU has executed a HALT instruction. This signal is 3-stated in EV mode.                                                                                                                                                                                                                                             |

| /BUSREQ           | 18(x13), 10(x15)              | In .                                       | BUS request signal. /BUSREQ requests placement of the address bus, data bus, /MREQ. /IORQ, /RD and /WR signals into the high impedance state. /BUSREQ is normally wired-OR and a pull-up resistor is externally connected.                                                                                                                           |

| /BUSACK           | 29(x13), 12(x15)              | Out (013/015),<br>Out/3-State<br>(C13/C15) | Bus Acknowledge signal. In response to /BUSREQ signal, /BUSACK informs a peripheral LSI that the address bus, data bus, /MREQ, /IORQ, /RD and /WR signals have been placed in the high impedance state.                                                                                                                                              |

| Note: For the Z84 | 4013/015 the /BUSACK signal v | rill not be 3-stated during EV mode. Fo    | or the Z84C13/C15 the /BUSACK will be 3-stated during EV mode.                                                                                                                                                                                                                                                                                       |

| /WAIT             | 19(x13), 11(x15)              | In(013/015),<br>I/O(C13/C15)               | Wait signal. /WAIT informs the CPU that specified memory or peripheral is not ready for data transfer. As long as /WAIT signal is adlive, MPU is continuously kept in the wait state.                                                                                                                                                                |

Note: For the Z84C13/C15, the /WAIT pin becomes an output to bring out on-chip wait state generator during the EV mode.

# **CPU SIGNALS** (Continued)

| Pin Name | Pin Number       | Input/Output, 3-State | Function                                                                                                                                                                                                                                                                 |

|----------|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A7RF     | 55(x13), 70(x15) | Out                   | 1-bit auxiliary address bus. Output is the same as bit-7 (A7) of the address bus. However, during a refresh cycle, this pin outputs the address which is the most significant bit of the 8-bit refresh address signal linked to the low order 7 bits of the address bus. |

# CTC SIGNALS

| Pin Name               | Pin Number             | Input/Output, 3-State | Function                                                                                                                                                                                                                                                                                                     |  |

|------------------------|------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

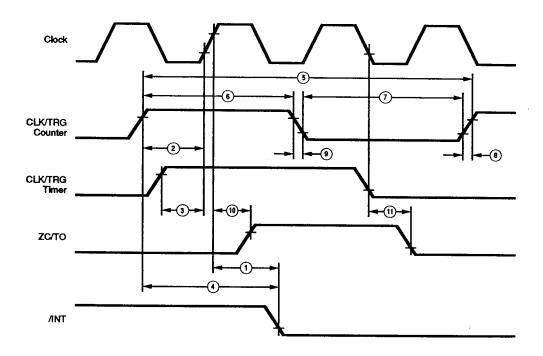

| CLK/TRG0 -<br>CLK/TRG3 | 75-72(x13), 81-78(x15) | In                    | External clock/trigger input. These four CLK/TRG pins correspond to four Counter/Timer Channels. In the counter mode, each active edge will cause the downcounter to decreme by one. In timer mode, an active edge will stathe timer. It is program selectable whether the active edge is rising or falling. |  |

| ZC/TO0 -<br>ZC/TO3     | 68-71(x13), 74-77(x15) | Out                   | Zero count/timer out signal. In either timer or counter mode, pulses are output when the down-counter has reached zero.                                                                                                                                                                                      |  |

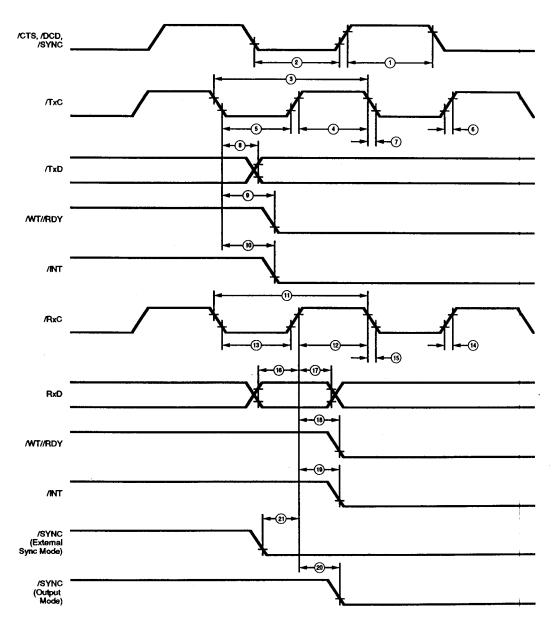

# SIO SIGNALS

| Pin Name              | Pin Number             | Input/Output, 3-State | Function                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-----------------------|------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| /W//RDYA,<br>/W//RDYB | 32,54(×13), 30,52(×15) | Out                   | Wait/Ready signal A and Wait/Ready signal B. Used as MAIT or /READY depending upon SIO programming. When programmed as /WA they go active at "0", alerting the CPU that addressed memory or I/O devices are not read by requesting the CPU to wait. When programmed as /READY, they are active at "0" which determines when a peripheral device associated with a DMA port is for read/write data. |  |

| /SYNCA,<br>/SYNCB     | 33,53(x13), 31,51(x15) | I/O                   | Synchronous signals. In asynchronous receive mode, they act as /CTS and /CDC. In external sync mode, these signals act as inputs. In internal sync mode, they act as outputs.                                                                                                                                                                                                                      |  |

| RxDA, RxDB            | 34,52(x13), 32,50(x15) | In                    | Serial receive data signal.                                                                                                                                                                                                                                                                                                                                                                        |  |

# SIO SIGNALS (Continued)

| Pin Name        | Pin Number             | Input/Output, 3-State | Function                                                                                                                                                                                                                                                         |

|-----------------|------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /RxCA, /RxCB    | 35,51(x13), 33,49(x15) | In                    | Receive clock signal. In the asynchronous mode, the receive clocks can be 1, 16, 32, or 64 times the data transfer rate.                                                                                                                                         |

| /TxCA, /TxCB    | 36,50(x13), 34,48(x15) | In                    | Transmitter clock signal. In the asynchronous mode, the transmitter clocks can be 1, 16, 32, or 64 times the data transfer rate.                                                                                                                                 |

| TxDA, TxDB      | 37,49(x13), 35,47(x15) | Out                   | Serial transmit data signal.                                                                                                                                                                                                                                     |

| /DTRA, /DTRB    | 38,48(x13), 36,46(x15) | Out                   | Data terminal ready signal. When ready, these signals go active to enable the terminal transmitter. When not ready they go inactive to disable the transfer from the terminal.                                                                                   |

| /RTSA, /RTSB    | 39,47(x13), 37,45(x15) | Out                   | Request to send signal. "0" when transmitting serial data. They are active when enabling their receivers to transmit data.                                                                                                                                       |

| /CTSA, /CTSB    | 40,46(x13), 38,44(x15) | In                    | Clear to send signal. When "0", after transmitting these signals the modem is ready to receive serial data. When ready, these signals go active to enable terminal transmitter. When not ready, these signals go inactive to disable transfer from the terminal. |

| /DCDA,<br>/DCDB | 41,45(x13), 39,43(x15) | In                    | Data carrier detect signal. When "0", serial data can be received. These signals are active to enable receivers to transmit.                                                                                                                                     |

# SYSTEM CONTROL SIGNALS

| Pin Name               | Pin Number       | Input/Output, 3-State | Function                                                                                                                                                                                                                                                                 |

|------------------------|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

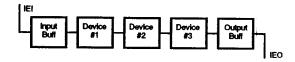

| IEI                    | 60(x13), 72(x15) | In .                  | Interrupt enable input signal. IEI is used with the IEO to form a priority daisy chain when there is more than one interrupt-driven peripheral.                                                                                                                          |

| IEO                    | 59(x13), 71(x15) | Out                   | The interrupt enable output signal. In the daisy chain interrupt control, IEO controls the interrupt of external peripherals. IEO is active when IEI is "1" and the CPU is not servicing an interrupt from the on-chip peripherals.                                      |

| /CS0<br>(C13/C15 only) | 42(C13), 40(C15) | Out                   | Chip Select 0. Used to access external memory or I/O devices. This pin has been assigned to "ICT" pin on Z84013/015. This signal is decoded only from A15-A12 without control signals. Refer to "Functional Description" on-chip select signals for further explanation. |

300

# **SYSTEM CONTROL SIGNALS (Continued)**

| Pin Name                                    | Pin Number       | Input/Output, 3-State                            | Function                                                                                                                                                                                                                                                                |  |

|---------------------------------------------|------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| /CS1 40(x13), 42(x15) Out<br>(C13/C15 only) |                  | Out                                              | Chip Select 1. Used to access external memory or I/O devices. This pin has been assigned to "ICT" pin on Z84013/015. This signal is decoded only from A15-A12 without control signals. Refer to "Functional Description on-chip select signals for further explanation. |  |

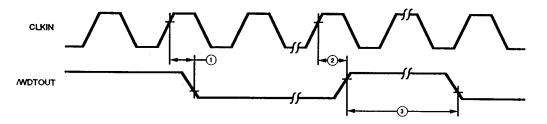

| MDTOUT                                      | 61(x13), 73(x15) | Out(013/015),<br>Open Drain(C13/C15)             | Watch Dog Timer Output signal. Output pulse width depends on the externally connected pin.                                                                                                                                                                              |  |

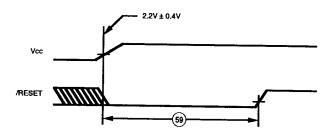

| /RESET                                      | 28(x13), 9(x15)  | Input(013/015),<br>I/O (Open Drain)<br>(C13/C15) | Reset signal. /RESET signal is used for initializing MPU and other devices in the system. Also used to return from the steady state in the STOP or IDLE modes.                                                                                                          |  |

Note: For the Z84013/Z84015 the /RESET must be kept in active state for a period of at least three system clock cycles.

Note: For the Z84C13/Z84C15, during the power-up sequence, the /RESET becomes an Open drain output and the Z84C13/C15 will drive this pin to "0" for 25 to 75 msec after the power supply passes through approx. 2.2V and then reverts to input. If it receives the /RESET signal after power-on sequence, it will drive /RESET pin for 16-processor clock cycles depending on the status of Reset Output Disable bit in Misc Control Register. If this Reset output is disabled, it must be kept in active state for a period of at least three system clock cycles. Note, that if using Z84C13/C15 in a Z84013/015 socket, modification may be required on the reset circuit since this pin is "pure input pin" on the Z84013/015. Also, the /RESET pin doesn't have internal pull-up resistors and therefore requires external pull-ups. For more details on the device, please refer to "Functional Description."

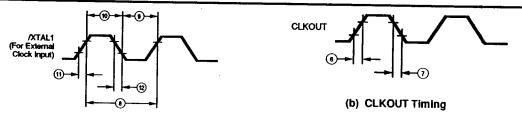

| XTAL1  | 63(x13), 65(x15) | In   | Crystal oscillator connecting terminal. A parallel resonant crystal is recommended. If external clock source is used as an input to the OGC unit, supply clock goes into this terminal. If external clock is supply to CLKIN pin (without CGC unit), this terminal must be connected to "0" or "1". |

|--------|------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTAL2  | 63(x13), 66(x15) | Out  | Crystal oscillator connecting terminal.                                                                                                                                                                                                                                                             |

| CLKIN  | 67(x13), 69(x15) | , In | Single-phase System Clock Input.                                                                                                                                                                                                                                                                    |

| CLKOUT | 66(x13), 68(x15) | Out  | Single-phase clock output from on-chip Clock<br>Generator/Controller.                                                                                                                                                                                                                               |

| EV     | 58(x13), 67(x15) | In , | Evaluator signal. When "1" is applied to this pin, IPC is put in Evaluation mode.                                                                                                                                                                                                                   |

Note: For the Z84013/015, together with /BUSREO, the EV signal puts the IPC into the evaluation mode. When this signal becomes active, the status of /M1, /HALT and /RFSH change to input. When using Z84013/015 as an evaluator chip, the CPU is electrically disconnected after one machine cycle is executed with the EV signal "1" and the /BUSREO signal "0". It follows the instructions from the other CPU (of ICE). Upon receiving /BUSREO; A15-A0, /MREO, /IORO, /RD and /WR are changed to input and D7-D0 changes its direction. /BUSACK is NOT 3-stated so it should be disconnected by an externally connected circuit. For details, please refer to "Functional Description" on EV mode.

# SYSTEM CONTROL SIGNALS (Continued)

Note: For the Z84C13/C15, to access on-chip resources from the CPU (e.g., ICE CPU), the CPU is electrically disconnected; A15-A0, MREQ, /IORQ, /RD and /MR are changed to input; D7-D0 changes its direction; /M1, /HALT and /RFSH are put into the high impedance state when the EV pin is set to "1". Also, /BUSACK is 3-stated. For details, please refer to "Functional Description" on EV mode.

| Pin Number                                  | Input/Output, 3-State                                                                                      | Function                                                                                                          |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 42,44(013), 40,42(015),<br>Not with C13/C15 | Out                                                                                                        | Test pins. Used in the open state.                                                                                |

| 24,27,57,65(x13),<br>Not with x15           |                                                                                                            | Not connected.                                                                                                    |

| 43,84(x13), 41,90(x15)                      | Power Supply                                                                                               | +5 Volts                                                                                                          |

| 22, 62(x13), 16,64(x15)                     | Power Supply                                                                                               | 0 Volts                                                                                                           |

|                                             | 42,44(013), 40,42(015),<br>Not with C13/C15<br>24,27,57,65(x13),<br>Not with x15<br>43,84(x13), 41,90(x15) | 42,44(013), 40,42(015), Out Not with C13/C15  24,27,57,65(x13), Not with x15  43,84(x13), 41,90(x15) Power Supply |

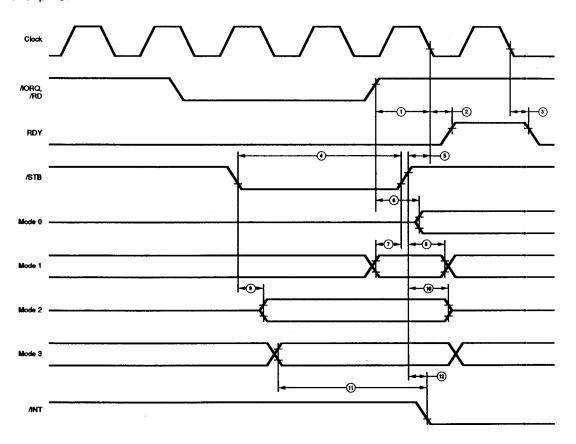

# PIO SIGNALS (for the Z84x15 only)

| Pin Name | Pin Number | Input/Output, 3-State | Function                                                                                                                                                                                                                            |

|----------|------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| /ASTB    | 21(x15)    | In ·                  | Port A strobe pulse from a peripheral device. The signal is used as the handshake between Port A and external circuits. The meaning of this signal depends on the mode of operation selected for Port A (see "PIO Basic Timing").   |

| /BSTB    | 61(x15)    | In                    | Port B strobe pulse from a peripheral device. This signal is used as the handshake between Port B and external circuits. The meaning of this signal is the same as /ASTB, except when Port A is in mode 2 (see "PIO Basic Timing"). |

| ARDY     | 20(x15)    | Out                   | Register A ready signal. Used as the handshake between Port A and external circuits. The meaning of this signal depends on the mode of operation selected for Port A (see *PIO Basic Timing*).                                      |

| BRDY     | 62(x15)    | Out                   | Register B ready signal. Used as the handshake between Port B and external circuits. The meaning of this signal is the same as ARDY except when Port A is in mode 2 (see "PIO Basic Timing").                                       |

| PA7-PA0  | 22-29(x15) | I/O, 3-State          | Port A data signals. Used for data transfer between Port A and external circuits.                                                                                                                                                   |

| PB7-PB0  | 53-60(x15) | I/O, 3-State          | Port B data signals. Used for transfer between Port B and external circuits.                                                                                                                                                        |

# The following pins have different functions between 013/015 and C13/C15

| Pin Name                     | Pin # X13      | Pin # X15      | Function                                                         |

|------------------------------|----------------|----------------|------------------------------------------------------------------|

| /RESET                       | 28             | 9              | Functionality is different.                                      |

| /WAIT                        | 19             | 15             | Functionality is different.                                      |

| EV                           | 58             | 67             | Functionality is different.                                      |

| MDTOUT                       | 61             | 73             | Push-pull output on Z84013/015, Open drain on Z84 C13/C15        |

| ICT                          | 40, 42         | 42, 40         | (Test pin) on Z84013/015; /CS0 and /CS1 on Z84C13/15.            |

| TxCA, TxCB,<br>RxCA and RxCB | 35, 36, 50, 51 | 33, 34, 48, 49 | On Z84C13/15; these signals have Schmitt-triggered inputs.       |

| /BUSACK                      | 29             | 12             | In EV mode, 3-stated on Z84C13/15; remains active on Z84013/015. |

### **FUNCTIONAL DESCRIPTION**

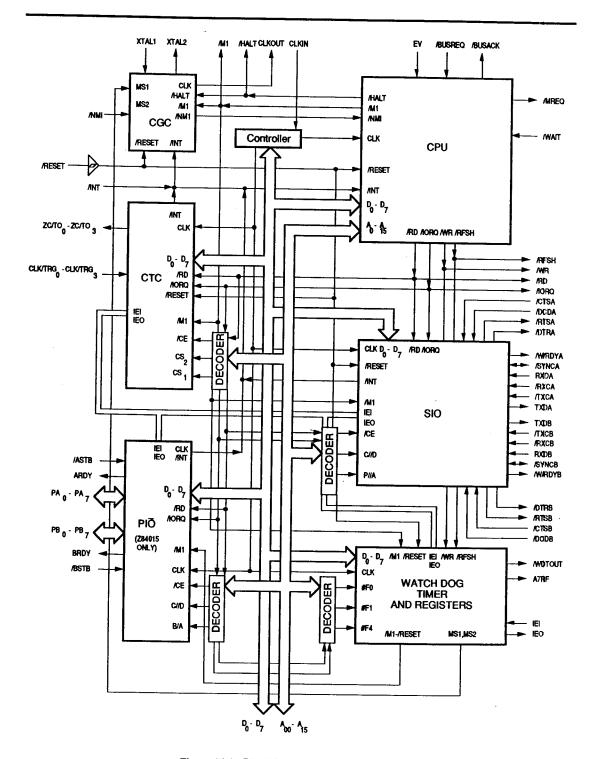

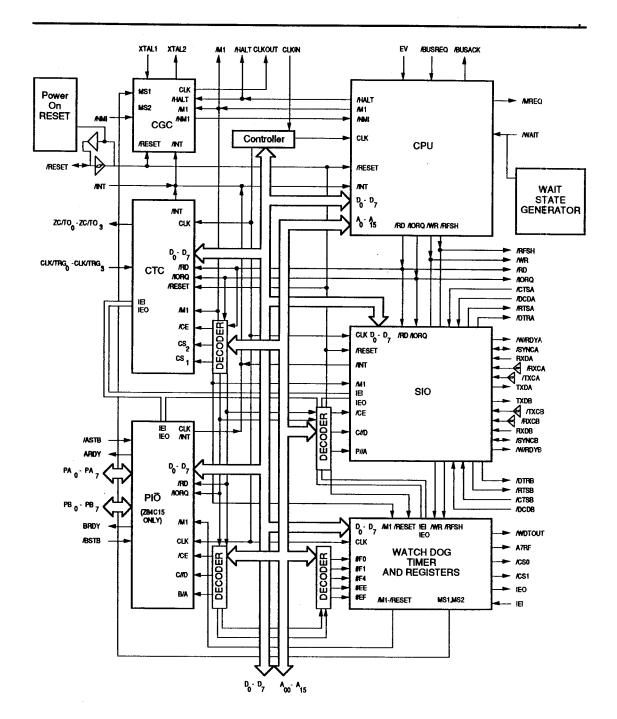

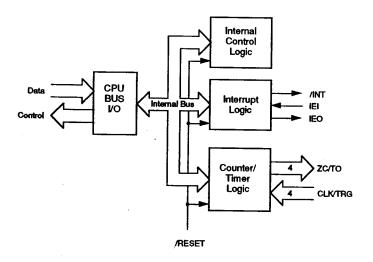

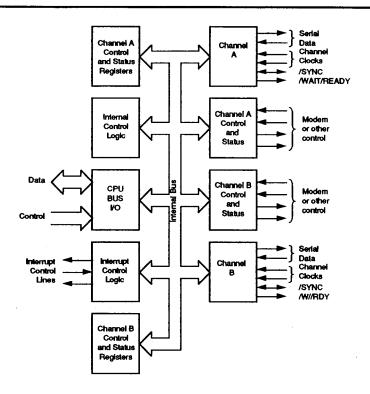

Figure 5(a) shows the functional block diagram of the Z84013/015 and Figure 5(b) shows the functional block diagram of the Z84C13/C15. As described earlier, the only difference between the Z84x13 and the Z84x15 is the PIO not being available on the Z84x13.

Functionally, the on-chip SIO, PIO (not available on Z84x13), CTC, and the Z80 CPU are the same as the discrete devices. Therefore, for detailed description of each individual unit, refer to the Product Specification/Technical Manual of each discrete product.

The following subsections describe each individual functional unit of the IPC.

#### Z84C00/01 Logic Unit

The CPU provides all the capabilities and pins of the Zilog Z80 CPU. This allows 100% software compatibility with existing Z80 software. In addition, it has the pin called "A7RF" to extend DRAM refresh address to 8-bits. Refer to "Z84C01 Z80 CPU with CGC" Product Specification.

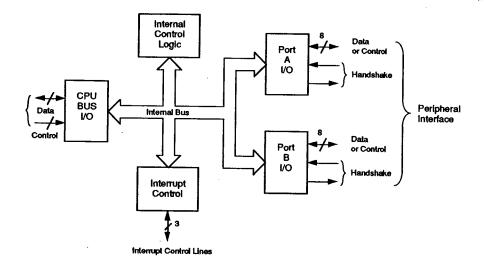

# Z84C20 Parallel Input/Output Logic Unit (Z84x15 Only)

This logic unit provides both TTL- and CMOS- compatible interfaces between peripheral devices and a CPU through the use of two 8-bit parallel ports (Figure 6). The CPU configures the logic to interface to a wide range of peripheral devices with no external logic. Typical devices that are compatible with this interface are keyboards, printers, and EPROM/PAL programmers.

The parallel ports (designated Port A and Port B) are byte wide and completely compatible with the Z84C20 PIO.

These two ports have several modes of operation; input, output, bi-directional, or bit control mode. Each port has two handshake signals (RDY and /STB) which are used to control data transfers. The RDY (ready) indicates that the port is ready for data transfer while /STB (strobe) is an input to the port that indicates when data transfer has occurred. Each of the ports can be programmed to interrupt the CPU upon the occurrence of specified status conditions, and generate unique interrupt vectors when the CPU responds (for more information on the operation of this portion of the logic, please refer to the Z84C20 PIO Product Specification and Technical Manual).

#### Z84C30 Counter/Timer Logic Unit

This logic unit provides the user with four individual 8-bit Counter/Timer Channels that are compatible with the Z84C30 CTC (Figure 7). The Counter/Timers can be programmed by the CPU for a broad range of counting and timing applications. Typical applications include event counting, interrupt and interval counting, and serial baud rate clock generation.

Each of the Counter/Timer Channels, designated Channels 0-3, have an 8-bit prescaler (when used in timer mode) and its own 8-bit counter to provide a wide range of count resolution. Each of the channels have their own Clock/Trigger input to quantify the counting process and an output to indicate zero crossing/timeout conditions. With only one interrupt vector programmed into the logic unit, each channel can generate a unique interrupt vector in response to the interrupt acknowledge cycle.

Figure 5(a). Block Diagram for 84013/015 IPC

Figure 5(b). Block Diagram for 84C13/C15 IPC

Figure 6. PiO Block Diagram

Figure 7. CTC Block Diagram

# Z84C4x Serial VO Logic Unit

This logic unit provides the user with two separate multiprotocol serial I/O channels that are completely compatible with the Z84C4x SIO. Their basic functions as serial-toparallel and parallel-to-serial converters can be programmed by a CPU for a broad range of serial communications applications. Each channel, designated Channel A and Channel B, is capable of supporting all common

asynchronous and synchronous protocols (Monosync, Bisync, and SDLC/HDLC, byte or bit oriented - Figure 8).

**Z84C13/C15 Only.** As an enhancement to the Z84013/015, the Z84C13/C15 can handle a 32-bit CRC on Channel A and Schmitt-trigger inputs on the /TxC and /RxC pins of both channels.

Figure 8. SIO Block Diagram

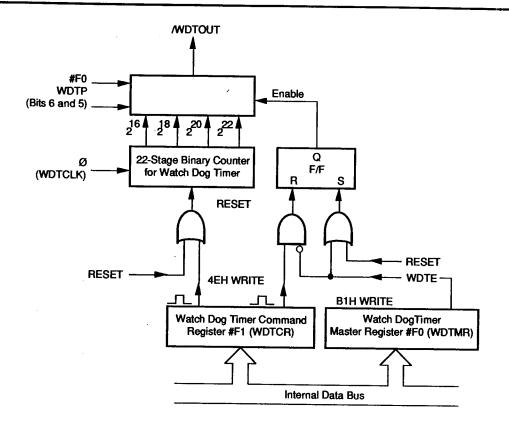

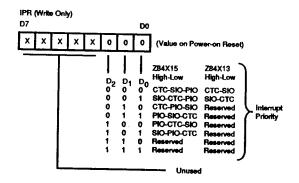

#### Watch Dog Timer (WDT) Logic Unit

This logic unit has been superintegrated into the IPC. It detects an operation error, caused by the program runaway, and returns to normal operation. Figure 9, shows the block diagram of the WDT. Upon Power-On Reset, this unit is enabled. If WDT is not required, but /WDTOUT is connected to /RESET or any other circuit, it has to be disabled. During the power-down mode of operation (either IDLE1/2 or Stop), the Watch Dog Timer is halted.

WDT Output (/WDTOUT pin). When the WDT is used, the "0" level signal is output from the /WDTOUT pin after a duration of time specified in the WDTP or in the WDTMR. The output pulse width is one of the following, depending on the /WDTOUT pin connection.

- The /WDTOUT is connected to the /RESET pin: The "0" level is pulsed for 5TcC (System clock cycles).

- The /WDTOUT is connected to a pin other than the /RESET pin: The "0" level is kept until the Watch Dog timer is cleared by software, or reset by /RESET pin.

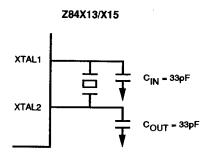

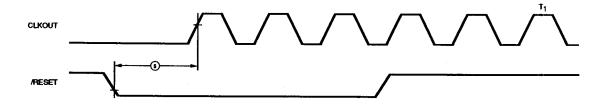

CGC Logic Unit. The IPC has CGC (Clock Generator/Controller) unit. This unit is identical to the one with the Z84C01 and the Z84C50, and supports power-down modes of operation. The output from this unit is on the pln called CLKOUT, and is not connected to the system clock internally. The CLKIN pin is the system clock input. The user can connect CLKOUT to CLKIN to utilize this CGC unit, or supply external clock from CLKIN pin.

The CGC unit allows crystal input (XTAL1, XTAL2) or External Clock input on the XTAL1 pin. It has clock divide-by-two circuits and generates a half-speed clock to the input.

**Z84C13/C15.** The power-down modes of the IPC vary depending upon whether the system clock is fed from the CGC unit (tie CLKOUT to CLKIN) or the external clock source on the CLKIN pin. They also have divide-by-one Mode. If the clock is supplied by this CGC unit, all of the modes in "halt" state are available. When external clock is provided on the CLKIN pin, XTAL1 is not left open (tied to "0" or "1") to avoid meta-stable conditions to minimize power consumption.

Figure 9. Block Diagram of Watch Dog Timer

**Z84013/015 Only.** If the system clock is provided on the CLKIN pin, none of the power-down mode (except RUN mode) is supported.

**Z84C13/C15 Only.** If the system clock is provided on the CLKIN pin, only the IDLE2 mode is applicable. In this mode, if the HALT instruction is executed, internal clock to the CTC is kept on "Continue", but the clock to the other components (CPU, PIO, SIO and Watch Dog Timer) are stopped. The divide-by-two circuit of the CGC unit can be skipped by programming bit D4 of the WDTMR (see "Programming" section). Upon Power-on Reset, it comes up in divide by two mode.

# System Clock Generation

The IPC has a built-in oscillator circuit and the required clock can be easily generated by connecting a crystal to the external terminals (XTAL1, XTAL2). Clock output is the same frequency as half the speed of the crystal frequency. Example of oscillator connections are shown in Figure 10.

**Z84C13/C15.** Clock output is the same, or half, of the external frequency.

Figure 10. Circuit Configuration For Crystal

Recommended characteristics of the crystal and the values for the capacitor are as follows (the values will change with crystal frequency).

- Type of crystal: Fundamental, parallel type crystal (AT cut is recommended).

- Frequency tolerance: Application dependent.

- CL, Load capacitance: Approximately 22pf (acceptable range is 20-30pf).

- Rs, equivalent-series resistance: ≤ 150 ohms.

- Drive level: 10mW (for ≤ 10MHz crystal); 5mW (for ≥ 10MHz crystal).

- $C_N = C_{OUT} = 33pF.$

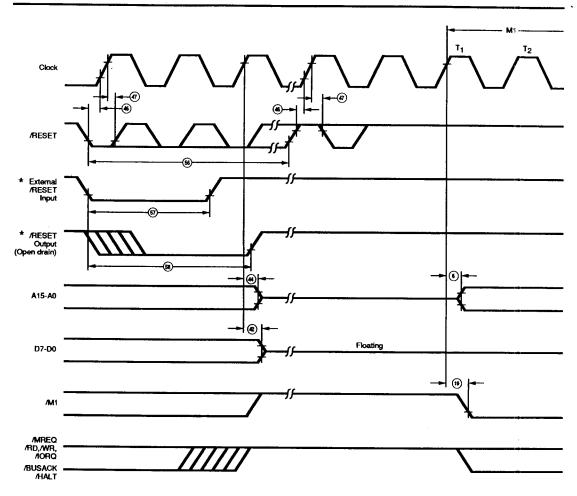

# Power-On Reset Logic Unit (Z84C13/C15 Only)

The Z84C13/C15 has the enhanced feature of a Power-on Reset Circuit. During the power-up sequence, the opendrain gate of the on-chip power-on Reset circuit drives /RESET pin to "0" for 25 to 75 msec after the power supply passes through approx. 2.2V. After the termination of the "Power-on Reset" cycle, the open-drain gate of the on-chip Power-on Reset circuit stops to drive the /RESET pin. It is required to have external pull-up register on the /RESET pin.

If it receives /RESET input from outside after the power-on sequence and while the Reset Output Disable bit in Misc Control Register is cleared to "0", it will drive the /RESET pin for 16-processor clock cycles from the falling edge of the external /RESET input. Otherwise, the /RESET pin must be kept in the active state for a period of at least 3 system clock cycles.

If there are power-on reset circuits outside of this device, drive this pin with OPEN-DRAIN type gates with pull-up resisters because /RESET signal is driven low for the period mentioned above during the Power-on sequence. If the external Power-on Reset circuit has push-pull type drivers and they drive the /RESET pin to "1" during that period, it may cause damage. In particular, when using Z84C13/C15 in the Z84013/015 socket, modification may be required on the external reset circuit.

### Wait State Generator Unit (Z84C13/C15 Only)

The Z84C13/C15 has the enhanced feature of a Wait State Generator circuit. It is capable of generating /WAIT signals to the CPU internally. The status of the External /WAIT input line is sampled after the insertion of software wait states, except for the wait state's insertion of Interrupt Daisy Chain Wait (for this cycle, insertion of a wait state is not simple).

The Wait State Control Register can be programmed to generate multiple Wait states during different CPU cycles listed as follows.

Memory Wait and Opcode wait. The Wait State Generator can put 0 to 3 wait states in memory accesses. Additionally, one added wait state can be inserted during an /M1 (Opcode fetch) cycle, because /M1 cycle's timing requirement is tighter than memory Read/Write cycles. It generates wait states to the Memory Access in a specified address range, which is programmed in the Memory Wait Boundary Register.

I/O Wait. The Wait State generator can put 0, 2, 4 or 6 wait states in I/O accesses. Regardless of the programming of this field, no I/O wait states are inserted for accesses to on-chip peripherals.

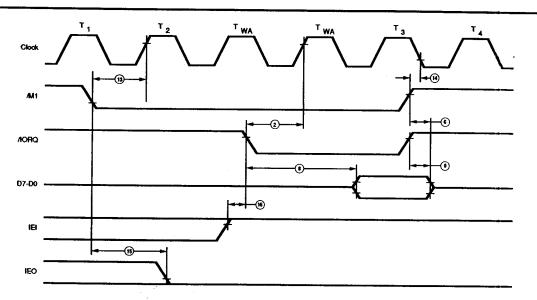

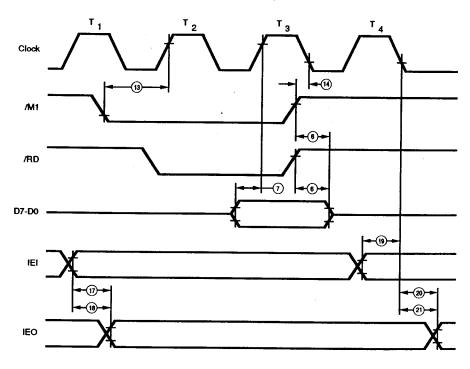

Interrupt Vector Wait. During Interrupt acknowledge cycle, the Wait State Generator can insert one wait state after /IORQ goes active, to extend the time between /IORQ fall to vector fetch by CPU. It allows a slow vector response device.

Interrupt Daisy Chain Wait and RETI sequence extension. During Interrupt acknowledge cycle, the Wait State Generator can insert 0, 2, 4 or 6 wait states between/M1 falling to /IORQ falling edge, to extend the time required to settle daisy chain. This allows a longer daisy chain. Also, this field controls the number of wait states inserted during RETI (Return From Interrupt) cycle. If specified to insert 4 or 6 wait states during Interrupt Acknowledge cycle, Wait State Generator also inserts wait states during RETI fetch sequence. This sequence is generated with two op-code fetch cycles (Op-code is EDh followed by 4Dh). It inserts 2 or 4 wait states, respectively, if op-code followed by EDh is 4Dh. One wait state if the following op-code is not 4Dh.

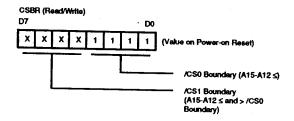

#### Chip Select Signals (Z84C13/C15 Only)

The Z84C13/C15 has an enhanced feature of adding two chip select (/CS0, /CS1) pins. Both signals are originally IC test pins (ICT) on the Z84013/015. The boundary value for each Chip Select Signal is 4 bits wide, and compare with A15-A12 of the address. Each Chip Select Signal goes active when:

/CS0: (D3-D0 of CSBR) ≥ A15-A12 ≥ 0 /CS1: (D7-D4 of CSBR) ≥ A15-A12 > (D3-D0 of CSBR)

(Where CSBR is the contents of Chip Select Boundary Register.)

There is also a separate /CS enable bit. /CS0 is enabled on power-up with a boundary value of "F" causing /CS0 to go active for all memory accesses. /CS1 is disabled on

power-up, and boundary address is undefined. These features are controlled via the I/O control registers located at I/O address EEh and EFh. Note that a glitch may be observed on these pins because address decode logic is decoding only A15-A12, without any control signals. For more detail, please refer to the "Programming section."

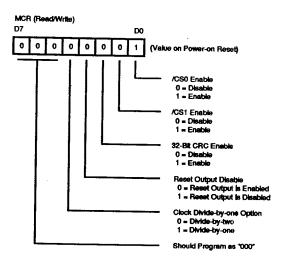

# Other functional features (Z84C13/C15 Only)

For more system design flexibility, the Z84C13/C15 has the following unique features. These features are controlled by MCR (Misc. Control Register) which is indirectly accessed via the System Control Register Pointer (SCRP, I/O address EEh), and System Control Data Port (SCDP, I/O address EFh). For more details, please refer to the "Programming" section.

- Clock Divide-by-one option

- Reset Output Disable

- 32-bit CRC Generation/Checking

Clock Divide-by-One Option. This feature is programmed through Bit D4 of MCR. Upon Power-On reset, the Clock from on-chip CGC is passed through a divide-by-two circuit. By setting this bit to one, the divide-by-two circuit is bypassed so the clock on the CLKOUT pin is equal to X'tal input. If the clock is applied to the CLKIN pin from external clock source, the status of this bit is ignored. Upon Power-on Reset, it is cleared to 0. For details, please refer to "Programming" section.

Reset Output Disable. This feature is programmed by Bit D3 of MCR. If this bit is cleared to "0", The /RESET pin becomes "Open-drain output" and is driven to "0" for 16-clock cycles from the falling edge of /RESET input. This feature is for the cases where /RESET is used to get out from the "HALT" state. If this bit is set to one, the on-chip reset circuit will not drive /RESET pin.

**32-bit CRC Generation/Checking.** This feature is programmed by Bit D2 of MCR. By setting this bit to one, Channel A of SIO is set to use the 32-bit CRC generator/checker instead of the original 16-bit CRC generator/checker in synchronous communication modes. The polynomial to be used in this mode is the one for the protocols

such as V.42, and is (X32 + X26 + X23 + X22 + X16 + X12 + X11 + X10 + X8 + X7 + X5 + X4 + X2 + X + 1). Upon Poweron Reset, this bit is cleared to 0.

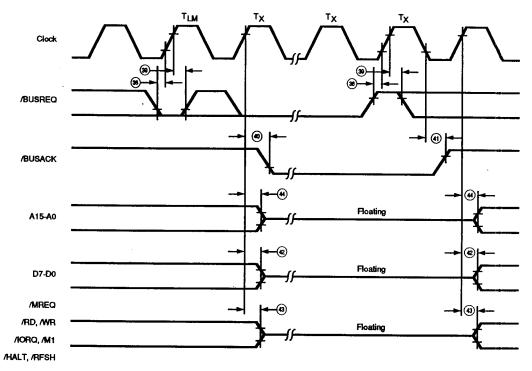

#### **Evaluation Mode**

The IPC has a built evaluation (or development) mode feature which allows the users to utilize standard Z80 development systems conveniently. This mode virtually replaces the on-chip Z80 CPU with the external CPU. In this mode, the on-chip CPU is electrically disconnected from internal bus and all 3-state signals (A15-0, D7-0, MREQ, /IORQ, /RD, MR, /HALT, /M1 and /RFSH; for C13/ C15, /BUSREQ as well) are tri-stated, or changed to input. This allows the development system CPU to take over and use the internal I/O registers of the IPC exactly as if the CPU was on-chip.

**Z84013/015 Only.** When this signal is active,the /M1, /HALT and /RFSH pins are put in the high-impedance state. In using the Z84013/015 as an evaluator chip, the CPU is electrically disconnected (put in high-impedance state) after one machine cycle is executed with the EV signal being "1" and the /BUSREQ signal being "0". Then, on-chip resources can be accessed from the cutside. /BUSACK is disconnected by an externally connected circuit.

Z84C13/C15 Only. If the EV pin is tied to Vcc on Power-up, the Z84C13/C15 enters into an evaluation mode. In this mode, the internal CPU is immediately disconnected from the internal bus and all 3-state signals mentioned above are tri-stated, or changed to input. Note that the MNAIT pin became the OUTPUT pin in EV mode, and the Wait State Generator generates wait states only as programmed. If the target application board has a separate wait state generator, modification of the target may be required. /BUSACK is 3-stated in this mode.

The Z84C13/C15 behaves similarly to the situation where in regular operation, the /BUSREQ signal is asserted by an external master causing all 3-state signals to be tri-stated by the Z84C13/C15 during T1 of the following machine cycle. The /BUSREQ approach was not used for the evaluation mode to avoid significant external circuitry to work around the time period before the external CPU uses the bus for Z84C13/C15 accesses.

### **PROGRAMMING**

# I/O address assignment

The IPC 's on-chip peripherals' I/O addresses are listed in Table 1. They are fully decoded from A7-A0 and have no image. The registers with Z84C13/C15 located at I/O Ad-

dress EEh and EFh are the registers to control enhanced features to Z84013/015, and not assigned on Z84C013/015.

| Address | Device               | Channel  | Register                                           |

|---------|----------------------|----------|----------------------------------------------------|

| 10h     | СТС                  | Ch 0     | Control Register                                   |

| 11h     | CTC                  | Ch 1     | Control Register                                   |

| 12h     | CTC                  | Ch 2     | Control Register                                   |

| 13h     | СТС                  | Ch 3     | Control Register                                   |

| 18h     | SIO                  | Ch. A    | Data Register                                      |

| 19h     | SIO                  | Ch. A    | Control Register                                   |

| 1Ah     | SIO                  | Ch. B    | Data Register                                      |

| 1Bh     | SIO                  | Ch. B    | Control Register                                   |

| 1Ch     | PIO                  | Port A   | Data Register (Not with Z84x13)                    |

| 1Dh     | PIO                  | Port A   | Command Register (Not with Z84x13)                 |

| 1Eh     | PIO                  | Port B   | Data Register (Not with Z84x13)                    |

| 1Fh     | PIO                  | Port B   | Command Register (Not with Z84x13)                 |

| F0h     | Watch-Dog Time       |          | Master Register (WDTMR)                            |

| F1h     | Watch-Dog Time       |          | Control Register (WDTCR)                           |

| F4h     | Interrupt Priority F | Register | ,                                                  |

| EEh     |                      |          | System Control Register Pointer (SCRP)             |

|         |                      |          | (Not with Z84013/015)                              |

| EFh     |                      |          | System Control Data Port (SCDP) (Not               |

|         |                      |          | with Z84013/015)                                   |

|         | Through SCRP ar      | nd SCDP  | Control Register 00 - Wait State Control           |

|         |                      | •        | register (WCR)                                     |

|         |                      |          | Control Register 01 - Memory Wait state            |

|         |                      |          | Boundary Register (MWBR)                           |

|         |                      |          | Control Register 02 - Chip Select Boundary         |

|         |                      |          | Register (CSBR)                                    |

|         |                      |          | Control Register 03 - Misc. Control Register (MCR) |

# **PIO REGISTERS**

For more detailed information, please refer to the PIO Technical Manual. These registers are not in the Z84x13.

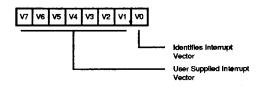

# Interrupt Vector Word

The PIO logic unit is designed to work with the Z80 CPU in interrupt Mode 2. The interrupt word must be programmed if interrupts are used. Bit D0 must be a zero (Figure 11).

Figure 11. PIO Interrupt Vector Word

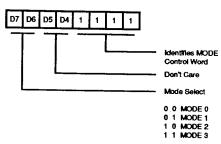

#### Mode Control Word

Selects the port operating mode. This word is required and is written at any time (Figure 12).

Figure 12. PIO Mode Control Word

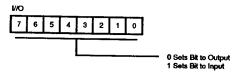

### I/O Register Control Word

When Mode 3 is selected, the Mode Control Word is followed by the I/O Register Control Word. This word configures the I/O register, which defines which port lines are inputs or outputs. A "1" indicates input while a "0" indicates output. This word is required when in Mode 3 (Figure 13).

Figure 13. I/O Register Control Word

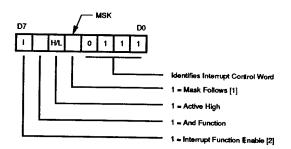

#### Interrupt Control Word

In Mode 3 operation, handshake signals are not used. Interrupts are generated as a logic function of the input signal levels. The Interrupt Control Word sets the logic conditions and the logic levels required for generating an interrupt. Two logic conditions or functions are available: AND (if all input bits change to the active level, an interrupt is triggered), OR (if any one of the input bits change to the active logic level, an interrupt is triggered). The user can program which input bits are to be considered as part of

this logic function. Bit D6 sets the logic function, bit D5 sets the logic level, and bit D4 specifies a mask control word to follow (Figure 14).

- [1] Regardless of the operating mode, setting Bit D4 = 1 pending interrupts to be cleared.

[2] The port interrupt is not enabled until the interrupt fur

Figure 14. Interrupt Control Word

#### Mask Control Word

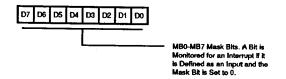

This word sets the mask control register, thus allowing any unused bits to be masked off. If any bits are to be masked, then bit D4 of the interrupt Control Word is set. When bit D4 of the interrupt Control Word is set, then the next word programmed is the Mask Control Word. To mask an input bit, the corresponding Mask Control Word bit is a "1" (Figure 15).

Figure 15. Mask Control Word

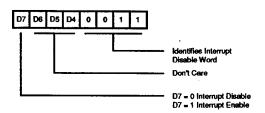

#### Interrupt Disable Word

This word can be used to enable or disable a port's interrupts without changing the rest of the port's interrupt conditions (Figure 16).

Figure 16. Interrupt Disable Word

### **CTC CONTROL REGISTERS**

For more detailed information, refer to the CTC Technical Manual.

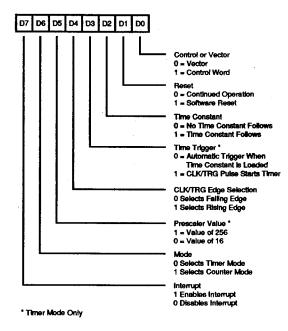

#### **Channel Control Word**

This word sets the operating modes and parameters as described below. Bit D0 is a "1" to indicate that this is a Control Word (Figure 17).

Figure 17. CTC Channel Control Word

Bit D7. Interrupt Enable. This bit enables the interrupt logic so that an internal INT can be generated at zero count. Interrupts are programmed in either mode and may be enabled or disabled at any time.

Bit D6. Mode Bit. This bit selects either Timer Mode or Counter Mode.

**Bit D5.** Prescalor Factor. This bit selects the prescalor factor for use in the timer mode. Either divide-by-16 or divide-by-256 is available.

**Bit D4.** Clock/Trigger Edge Selector. This bit selects the active edge of the CLK/TRG input pulses.

Bit D3. Timer Trigger. This bit selects the trigger mode for timer operation. Either automatic or external trigger may be selected.

Bit D2. Time Constant. This bit indicates that the next word programmed is time constant data for the downcounter.

**Bit D1.** Software Reset. Writing 1 to this bit indicates a software reset operation, which stops counting activities until another time constant word is written.

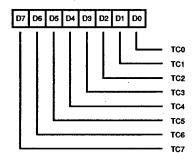

### Time Constant Word

Before a channel starts counting, it must receive a time constant word. The time constant value is anywhere between 1 and 256, with "0" being accepted as a count of 256 (Figure 18).

Figure 18. CTC Time Constant Word

#### Interrupt Vector Word

If one or more of the CTC channels have interrupt enabled, then the Interrupt Vector Word must be programmed. Only the five most significant bits of this word are programmed, and bit D0 must be "0". Bits D2-D1 are automatically modified by the CTC channels when it responds with an interrupt vector (Figure 19).

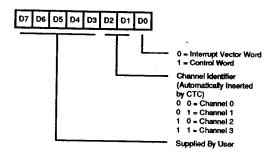

Figure 19. CTC Interrupt Vector Word

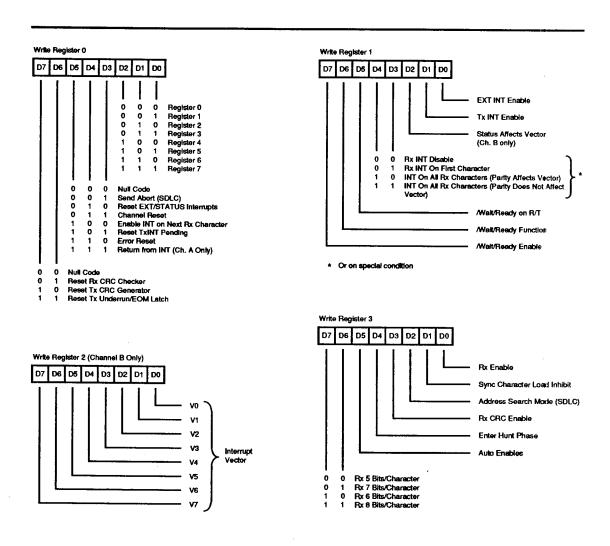

#### SIO REGISTERS

For more detailed information, refer to the SIO Technical Manual.

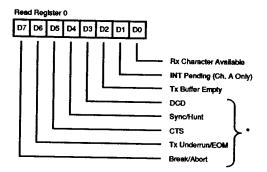

Read Registers. The SIO channel B contains three read registers while channel A contains only two that are read to obtain status information. To read the contents of a register (rather than RR0), the program must first write a pointer to WR0 in exactly the same manner as a write operation. The next I/O read cycle will place the contents of the selected read registers onto the data bus (Figure 20a, b, c).

\* Used With "External/Status Interrupt" Modes

Figure 20a. SIO Read Register 0

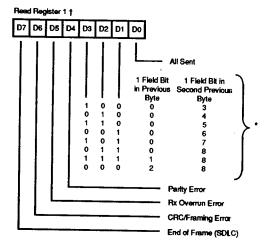

- Residue data for eight Px bits/character programmed

- † Used with special receive condition mode

Figure 20b. SIO Read Register 1

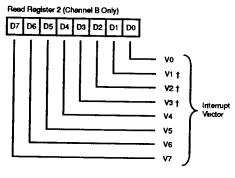

† Variable if "Status Affects Vector" is programmed

Figure 20c. SIO Read Register 2

Write Registers. The SIO Channel B contains eight write registers while Channel A contains only seven that are programmed to configure the operating mode characteristics of each channel. With the exception of WRO, programming the write registers is a two step operation. The first operation is a pointer written to WRO which points to the selected register. The second operation is the actual control word that is written into the register to configure the SIO channel (Figure 21).

Figure 21. SIO Write Registers

Figure 21. SIO Write Registers (Continued)

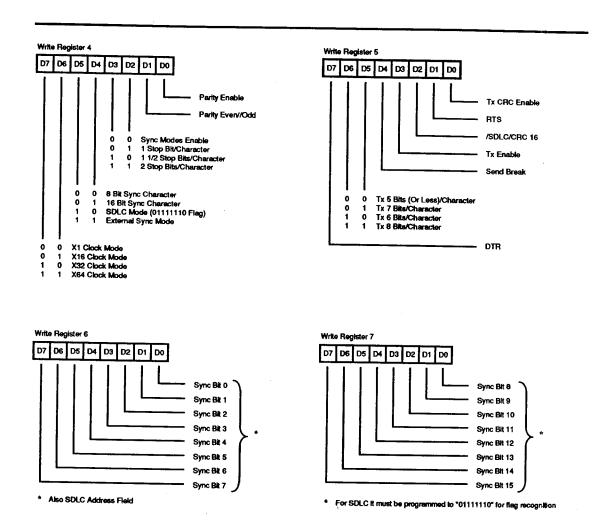

# **WATCH DOG CONTROL REGISTERS**

There are two registers to control Watch Dog Timer operations. These are Watch Dog Timer Master Register (WDTMR; I/O Address F0h) and the WDT Command Register (WDTCR; I/O Address F1h). Watch Dog Timer Logic has a "double key" structure to prevent the WDT disabling error, which may lead to the WDT operation to stop due to program runaway. Programming the WDT follows this procedure. Also, these registers program the power-down mode of operation. The "Second key" is needed when turning off the Watch Dog Timer.

**Enabling the WDT.** The WDT is enabled by setting the WDT Enable Bit (D7:WDTE) to "1" and the WDT Periodic field (D5,D6:WDTP) to the desired time period. These command bits are in the Watch Dog Timer Master Register (WDTMR; I/O Address F0h).

**Disabling the WDT.** The WDT is disabled by clearing WDT Enable bit (WDTE) in the WDTMR to "0" followed by writing "B1h" to the WDT Command Register (WDTCR; I/O Address F1h).

Clearing the WDT. The WDT can be cleared by writing "4Eh" into the WDTCR.

Watch Dog Timer Master Register (WDTMR;I/O address F0h). This register controls the activities of the Watch Dog Timer and selects power-down mode of operation (Figure 22).

Figure 22. Watch Dog Timer Master Register

Bit D7. Watch Dog Timer Enable (WDTE). This bit controls the activities of Watch Dog Timer. The WDT can be enabled by setting this bit to "1". To disable WDT, write "0" to this bit followed by writing "B1h" in the WDT Command Register. Watch Dog Timer Logic has a "double key" structure to prevent the WDT disabling error, which may lead to the WDT operation to stop, due to program runaway. Upon Power-on reset, this bit is set to "1" and the WDT is enabled.

Bit D6-D5. WDT Periodic field (WDTP). This two bit field determines the desired time period. Upon Power-on reset, this field sets to "11".

```

00 - Period is (TcC * 2<sup>16</sup>)

01 - Period is (TcC * 2<sup>18</sup>)

10 - Period is (TcC * 2<sup>20</sup>)

11 - Period is (TcC * 2<sup>22</sup>)

```

Bit D4-D3. HALT mode (HALTM). This two bit field specifies one of four power-down modes. To change this field, write "DBh" to the WDT command register, followed by a write to this register. For detailed descriptions of this field, please refer to the section "Mode of operations." Upon Power-on Reset, this field is set to 11, which specifies "RUN mode."

00 - IDLE 1 Mode 01 - IDLE 2 Mode 10 - STOP Mode 11 - RUN Mode

Power-down mode.

Bit D2-D0. Reserved. These three bits are reserved and should always be programmed as "011". A read to these bit returns "011".

Watch Dog Timer Command Register (WDTCR; VO address F1h). In conjunction with the WDTMR, this register works as a "Second key" for the Watch Dog Timer. This register is write only (Figure 23).

Write B1h after clearing WDTE to "0" - Disable WDT. Write 4Eh - Clear WDT. Write DBh followed by a write to HALTM - Change

###

Figure 23. Watch Dog Timer Command Register

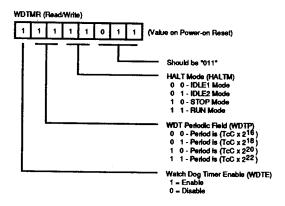

# INTERRUPT PRIORITY REGISTER (INTPR; I/O address F4h)

This register (write only) is provided to determine the interrupt priority for the CTC, SIO and the PIO (Figure 24).

Figure 24. Interrupt Priority Register

Bit D7-D3. Unused

Bit D2-D0. This field specifies the order of the interrupt daisy chain. Upon Power-on Reset, this field is set to "000".

|     | Z84C15<br>High - Low | Z84C13<br>High - Low |  |

|-----|----------------------|----------------------|--|

| 000 | CTC-SIO-PIO          | CTC-SIO              |  |

| 001 | SIO-CTC-PIO          | SIO-CTC              |  |

| 010 | CTC-PIO-SIO          | Reserved             |  |

| 011 | PIO-SIO-CTC          | Reserved             |  |

| 100 | PIO-CTC-SIO          | Reserved             |  |

| 101 | SIO-PIO-CTC          | Reserved             |  |

| 110 | Reserved             | Reserved             |  |

| 111 | Reserved             | Reserved             |  |

# REGISTERS FOR SYSTEM CONFIGURATION

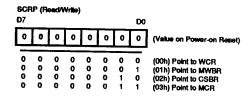

(The following registers are not available on Z84013/015.) There are four indirectly accessible registers to determine System configuration with the Z84C13/C15. These indirectly accessible registers are: Wait State Control Register (WCR, Control Register O0h), Memory Wait Boundary Register (MWBR, Control Register 01h), Chip Select Boundary Register (CSBR, Control Register 02h) and Misc. Control Register (MCR, Control Register 03h). To access these registers, Z84C13/C15 writes "register number to be accessed" to the System Control Register Pointer (SCRP,

I/O address EEh), and then accesses the target register through the System Control Data Port (SCDP, I/O address EFh). The pointer which writes into SCRP is kept until modified.

System Control Register Pointer (SCRP, I/O address EEh) This register stores the pointer to access System Control Registers (WCR, MWBR, CSBR and MCR). This register is Read/Write and it holds the pointer value until modified. Upon Power-on Reset, all bits are cleared to zero. The pointer value, other than 00h to 03h is reserved and is not written. Upon Power-on Reset, this register is set to "00h" (Figure 25).

Figure 25. System Control Register Pointer

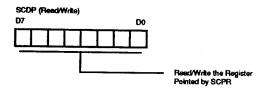

System Control Data Port (SCDP, I/O address EFh)

This register is to access WCR, MWBR, CSBR and MCR (Figure 26).

Figure 26. System Control Data Port

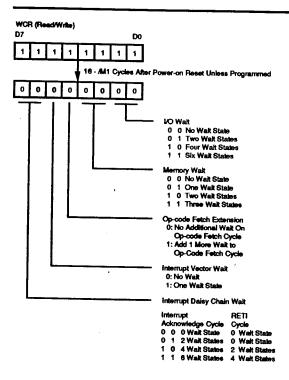

Wait State Control Register (WCR, Control Register 00h) This register can be accessed through SCDP with the pointer value 00h in SCRP (Figure 27). To maintain compatibility with the Z84013/015, the Z84C13/C15 inserts the maximum number of wait states (set all bits of this register to one) for fifteen /M1 cycles after Power-on Reset. It automatically clears the contents of this register (move to no-wait state insertion) on the trailing edge of the 16th /M1 signal unless software has programmed a value. If automatic wait state insertion is needed, the wait state is programmed within this time period. A read to WCR during this period will return FFh, unless programmed.

Figure 27. Wait State Control Register

This register has the following fields:

Bit 7-6. Interrupt Daisy Chain Wait. This 2-bit field specifies the number of wait states to be inserted during an Interrupt Daisy Chain settle period of the Interrupt Acknowledge cycle, which is/IORQ falls after the settling period from /M1 going active "0". Also, this field controls the number of wait states inserted during the RETI (Return From Interrupt) cycle. If specified to insert 4 or 6 wait states during Interrupt Acknowledge cycle, the Wait state generator also inserts wait states during RETI fetch sequence. This sequence is formed with two op-code fetch cycles (Op-code is EDh followed by 4Dh). It inserts 1 wait state if op-code followed by EDh is NOT 4Dh, and inserts 2 or 4 wait states, respectively, if the following op-code is 4Dh.

| Interrupt Acknowledge | RETI cycle     |

|-----------------------|----------------|

| 00 - No Wait states   | No Wait states |

| 01 - 2 Wait states    | No Wait states |

| 10 - 4 Wait states    | 2 Wait states  |

| 11 - 6 Wait states    | 4 Wait states  |

For fifteen /M1 cycles from Power-on Reset, bits 7-6 are set to "11". They clear to "00" on the trailing edge of the 16th /M1 signal unless programmed.

Bit 5. Interrupt Vector Wait. While this bit is set to one, the wait state generator inserts one wait state after the /IORQ signal goes active during the Interrupt acknowledge cycle. This gives more time for the vector read cycle. While this bit is cleared to zero, no wait state is inserted (standard timing). For fifteen /M1 cycles from Power-on Reset, this bit is set to "1", then cleared to "0" on the trailing edge of the 16th /M1 signal, unless programmed.

Bit 4. Opcode Fetch Extension. If this bit is set to "1", one additional wait state is inserted during the Op-code fetch cycle in addition to the number of wait states programmed in the Memory Wait field. For fifteen /M1 cycles from Poweron Reset, this bit is set to "1", then cleared to "0" on the trailing edge of the 16th /M1 signal, unless programmed.

**Bit 3-2.** *Memory Wait States.* This 2-bit field specifies the number of wait states to be inserted during memory Read/Write transactions.

00 - No Wait states

01 - 1 Wait states

10 - 2 Wait states

11 - 3 Wait states

For fifteen /M1 cycles from Power-on Reset, these bits are set to "11", then cleared to "00" on the trailing edge of the 16th /M1 signal, unless programmed.

Bit 1-0. I/O Wait states. This 2-bit field specifies the number of wait states to be inserted during I/O transactions.

00 - No Wait states

01 - 2 Wait states

10 - 4 Wait states

11 - 6 Wait states

For fifteen /M1 cycles from Power-on Reset, these bits are set to "11", then cleared to "00" on the trailing adde of the 16th /M1 signal, unless programmed. For the accesses to the on-chip I/O registers, no Wait states are inserted regardless of the programming of this field.

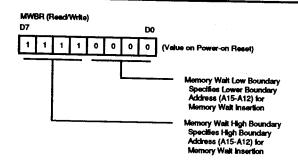

# Memory Wait Boundary Register (MWBR, Control Register 01h)

This register specifies the address range to insert memory wait states. When accessed memory addresses are within this range, the Memory Wait State generator inserts Memory Wait States specified in the Memory Wait field of WCR (Figure 28).

Figure 28. Memory Wait Boundary Register

Bit D7-D4. Memory Wait High Boundary. This field specifies A15-A12 of the upper address boundary for Memory Wait.

Bit D3-D0. Memory Wait Low Boundary. This field specifies A15-12 of the lower address boundary for Memory Wait.

Memory Wait states are inserted for the address range:

(D7-D4 of MWBR) ≥ A15-A12 ≥ (D3-D0 of MWBR)

This register is set to "F0h" on Power-on Reset, which specifies the address range for Memory Wait as "0000h to FFFFh".

# Chip Select Boundary Register (CSBR, Control Register 02h)

This register specifies the address range for each chip select signal. When accessed memory addresses are within this range, chip select signals are active (Figure 29).

Figure 29. Chip Select Boundary Register

D7-D4. /CS1 Boundary Address. These bits specify the boundary address range for /CS1. The bit values are ignored on power-up as the /CS1 enable bit is off. The /CS1 is asserted if the address lines A15-12 have an address value greater than the programmed value for /CS0, and less than or equal to the programmed value in these bits.

D3-D0. /CSO Boundary Address. These bits specify the boundary address range for /CSO. /CSO is asserted if the address lines A15-12 have an address value less than or equal to the programmed boundary value. The /CSO enable bit in the MCR must be set to 1. Upon Power-up reset, these bits come up as all 1's so that /CSO is asserted for all addresses.

Chip Select signals are active for the address range:

/CS0: (D3-D0 of CSBR) ≥ A15-A12 ≥ 0 /CS1: (D7-D4 of CSBR) ≥ A15-A12 > (D3-D0 of CSBR)

This register is set to "xxxx1111b" on Power-on Reset, which specifies the address range of /CS0 for "0000h to FFFFh" (all Memory location) and /CS1 "undefined."

Misc Control Register (MCR, Control Register 03h)

This register specifies miscellaneous options on this device (Figure 30).

Figure 30. Misc Control Register

**Bit D7-D5.** Reserved. These three bits are reserved and are always programmed as "000".

Bit D4. Clock Divide-by-one option. "0"-Disable, "1"-enable. On-chip CGC unit has divide-by-two circuit. By setting this bit to one, this circuit is bypassed and CLKOUT is equal to X'tal oscillator frequency (or external clock input on the XTAL1 pin). This bit has no effect when the on-chip CGC unit is not in use and the external system clock is fed from CLKIN pin. Upon Power-on Reset, this bit is cleared to 0 and the clock is divided by two.

Bit D3. Reset Output Disable. "0"-Reset output is enabled, "1"-Reset output is disabled. This bit controls the /RESET signal and is driven out when reset input is used to take the Z84C13/C15 out of the "Halt" state. The reset pulse is driven out for 16-clock cycles from the falling edge of /RESET input, unless this bit is set. Upon Power-on reset, this bit is cleared to 0.

Bit D2. 32-Bit CRC enable. "0"-Normal mode (16-bit CRC) "1"-32-bit CRC generation/Checking is enabled on SIO Channel A. This bit determines if the 32-bit CRC feature is enabled on Channel A of the SIO. If this bit is 0, the SIO is in a normal mode of operation. If this bit is set to 1, a normal CRC generator/checker is replaced with a 32-bit CRC generator/checker. Upon Power-on Reset, this bit is clear to "0".

Bit D1. /CS1 Enable. "0"-Disable, "1"-Enable. This bit enables /CS1 output. While this bit is "0", /CS1 is forced to "1". While this bit is "1", /CS1 carries the address range specified in the CSBR. Upon Power-on Reset, this bit is cleared to "0".

Bit Do. /CSO Enable. "O"-Disable, "1"-Enable. This bit enables /CSO output. While this bit is "O", /CS1 pin is forced

to "1". While this bit is "1", the /CSO carries address range specified in the CSBR. Upon Power-on Reset, this bit is set to "1".

#### Operation modes

There are four kinds of operation modes available for the IPC in connection with clock generation; RUN Mode, IDLE1/2 Modes and STOP Mode.

The Operation mode is effective when the HALT instruction is executed. Restart of the MPU from the stopped state under IDLE 1/2 Mode or STOP mode is affected by inputting either /RESET or interrupt (/NMI or /INT). The mode selection of these power-down modes is made by programming the HALTM field (Bit D4-3) of WDTMR.

#### **Setting Halt Mode**

Duplicate control is provided to prevent the stopping of the WDT operation caused by the halt mode setting an error due to program runaway. As described in the programming section, changing the Halt Mode field of WDTMR is in two steps. First, write "DBh" to WDTCR followed by a write to the WDTMR with the value in HALTM. Table 2 has descriptions of each mode, and Table 3 has device status in the Halt state.

**Table 2. Power-down Modes**(When using on-chip CGC unit; CLKOUT and CLKIN are tied together)

| Operation Mode | WDTMR<br>Bit D4 | Bit D3 | Description at HALT State                                                                                                                                                                                                                                                               |

|----------------|-----------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RUN Mode       | 1               | 1      | The IPC continues the operation and continuously supplies a clock to the outside.                                                                                                                                                                                                       |

| IDLE1 Mode     | 0               | . 0    | The internal oscillator's operation is continued. Clock output (CLKOUT) as well as internal clock to the CPU, PIO, SIO, CTC and the Watch Dog Timer is stopped at "0" level of T4 state in the halt instruction operation code fetch cycle.                                             |

| IDLE2 Mode     | 0               | 1      | The internal oscillator and the CTC's operation continues and supplies clock to the outside on the CLKOUT pin continuously. But the internal clock to the CPU, PIO, SIO and the Watch Dog Timer is stopped at "0" level of T4 state in the halt instruction operation code fetch cycle. |

| STOP Mode      | 1               | 0      | All operations of the internal oscillator, clock (CLK) output, internal clock to the CPU, PIO, CTC, SIO and the Watch Dog Timer are stopped at "0" level of T4 state in the halt instruction operation code fetch cycle.                                                                |

Table 3. Device status in Halt state

(When using on-chip CGC unit; CLKOUT and CLKIN are tied together)

| Mode  | CGC | CPU | стс | PIO | SIO | WDT | CLKOUT |

|-------|-----|-----|-----|-----|-----|-----|--------|

| IDLE1 | 0   | Х   | X   | X   | Х   | X   | X      |

| IDLE2 | 0   | X   | 0   | X   | X   | X   | 0      |

| STOP  | X   | X   | X   | X   | Х   | Х   | X      |

| RUN   | 0   | 0   | Ο.  | 0   | 0   | 0   | 0      |

O: Operating

X: Stop

All of the operating modes listed here are valid with crystal input (Crystal connected between XTAL1/2 or external clock input on XTAL1). For the external clock on the CLKIN pin, only the IDLE2 and RUN modes are applicable.

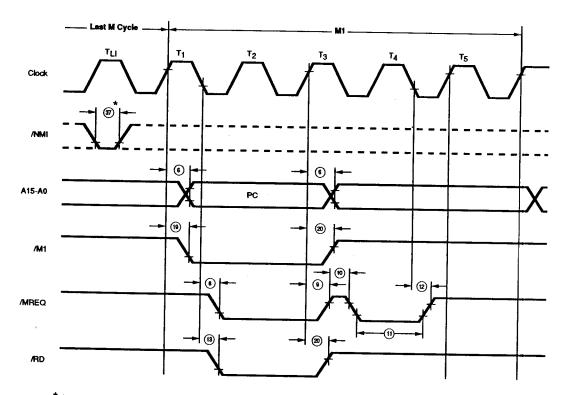

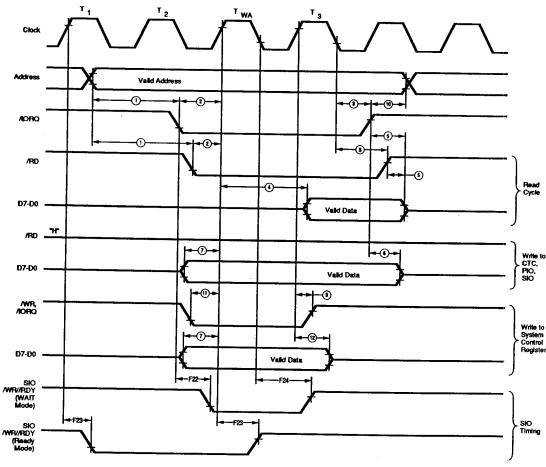

### TIMING

#### **Basic Timing**

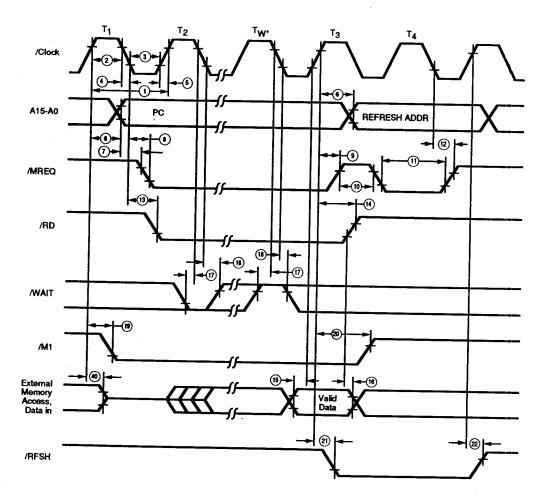

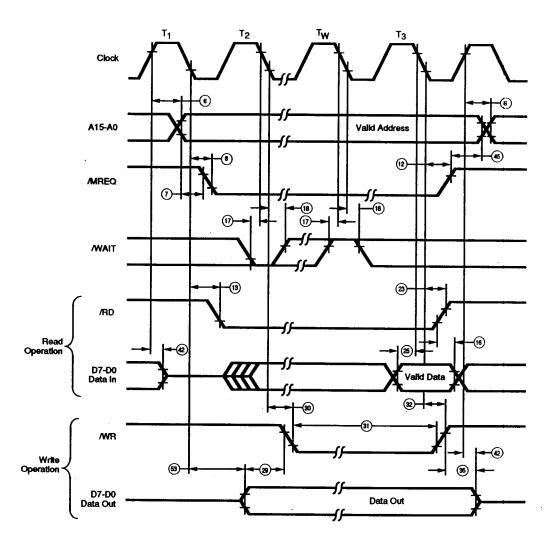

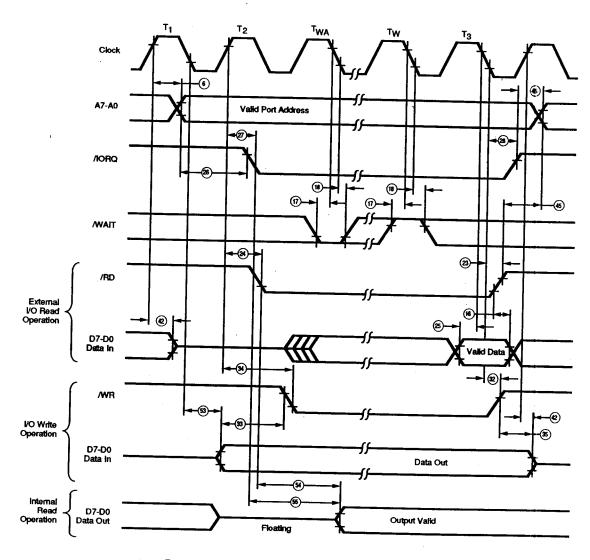

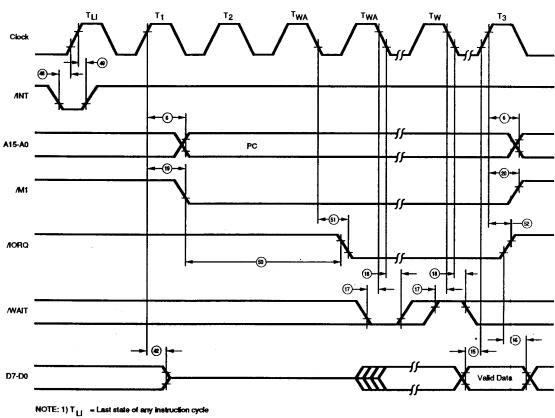

The basic timing is explained here with emphasis placed on the halt function relative to the clock generator. The following items are identical to those for the Z84C00. Refer to the data sheet for the Z84C00.

- Operation code fetch cycle

- Memory Read/Write operation

- Input/Output operation

- Bus request/acknowledge operation

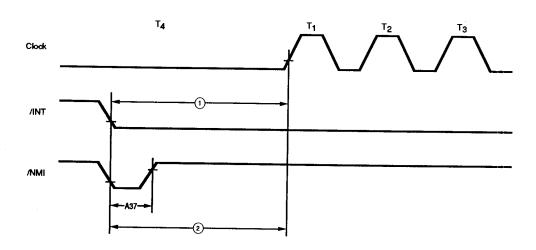

- Maskable interrupt request operation

- Non-Maskable interrupt request operation

- Reset Operation

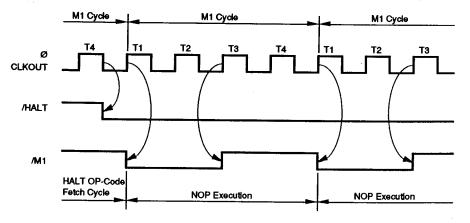

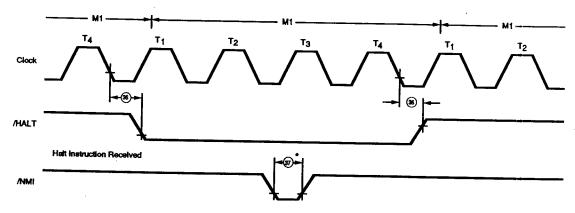

Operation When HALT Instruction is Executed. When the CPU fetches a halt instruction in the operation code fetch cycle, /HALT goes active (Low) in synch with the falling edge of T4 state before the peripheral LSI and CPU stops the operation. After this, the system clock generation differs depending upon the operation mode (RUN Mode, IDLE1/2 Mode or STOP Mode). If the internal system clock is running, the CPU continues to execute NOP instruction even in the halt state.

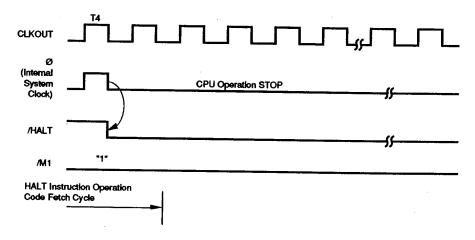

RUN Mode (HALTM = 11). Shown in Figure 31 is the basic timing when the halt instruction is executed in RUN Mode.

Figure 31. Timing of RUN Mode (at Halt Instruction Command Execution)

In RUN Mode, output from the CGC unit (CLKOUT) is not stopped and the internal system clock ( $\emptyset$ ) continues even after the halt instruction is executed. Therefore, until the halt state is released by the interrupt signal (/NMI or /INT)

or /RESET signal, MPU continues to execute HALT instructions (internally executing NOP instructions).

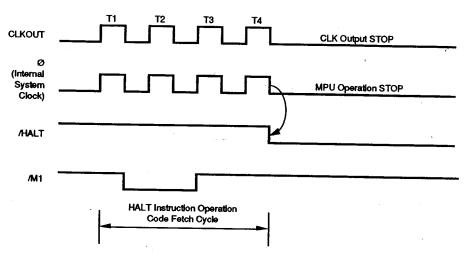

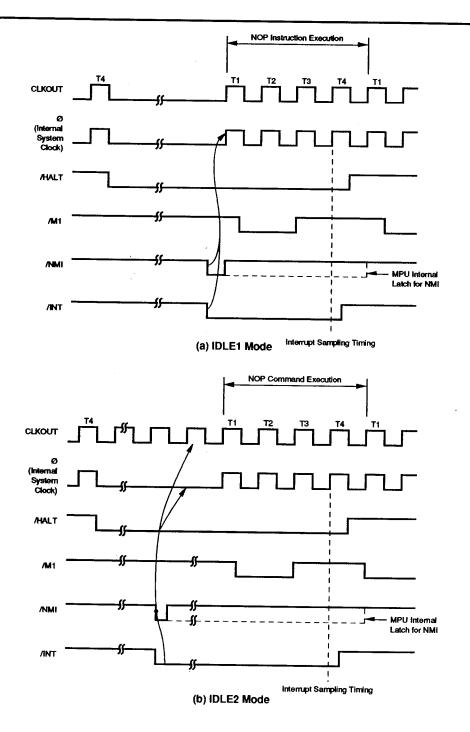

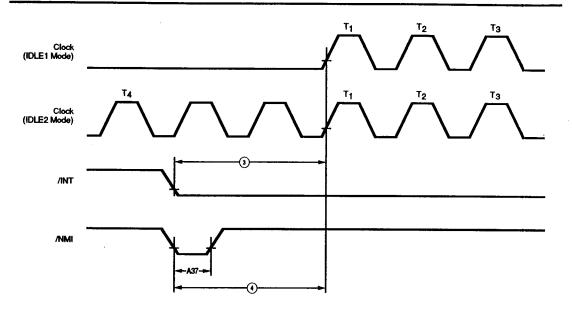

IDLE1 Mode (HALTM=00). Shown in Figure 32 is the basic timing when the halt instruction is executed in IDLE1 Mode.

Figure 32. IDLE1 Mode Timing (At Halt Instruction Execution)

In IDLE1 Mode, the internal oscillator continues to operate, but clock output (CLKOUT) is stopped at T4 Low state of HALT instruction execution. Then all components in the MPU stop their operation. This mode is not supported

when the CGC unit is inactive and the external clock is fed from CLKIN pin; CLKOUT should be connected to CLKIN.

IDLE2 Mode (HALTM=01). Shown in Figure 33 is the basic timing when the halt instruction is executed in IDLE2 Mode.

Figure 33. IDLE2 Mode Timing (At Halt Instruction Execution)

In IDLE2 Mode, the internal oscillator and clock output (CLKOUT) continue to operate. The internal system clock, fed from CLKIN to the components other than CTC is stopped at the T4 Low state of HALT instruction execution.

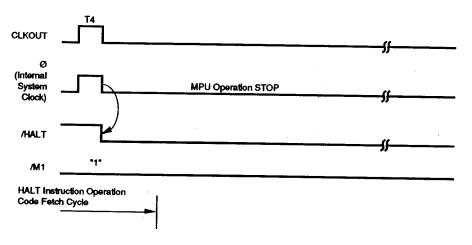

STOP Mode (HALTM=10). Shown in Figure 34 is the basic timing when the halt instruction is executed in STOP Mode.

Figure 34. STOP Mode Timing (At Halt Instruction Execution)

In STOP Mode, the on-chip CGC unit is stopped at T4 Low state of HALT instruction execution. Therefore, clock output (CLKOUT), operation of Watch Dog Timer, CPU, PIO, CTC, SIO are stopped.

Release from Halt State. The halt state of the CPU is released when "0" is input to the /RESET signal and the MPU is reset or an interrupt request is accepted. An interrupt request signal is sampled at the leading edge of the last clock cycle (T4 state) of NOP instruction. In case of the maskable interrupt, interrupt will be accepted by an active /INT signal ("0" level). Also, the interrupt enable flip-

flop is set to "1". The accepted interrupt process is started from the next cycle.

Further, when the internal system clock is stopped (IDLE1/2 Mode, STOP Mode), it is necessary first to restart the internal system clock. The internal system clock is restarted when /RESET or interrupt signal (/NMI or /INT) is asserted.

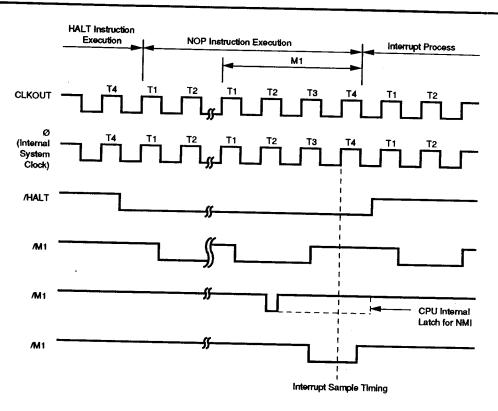

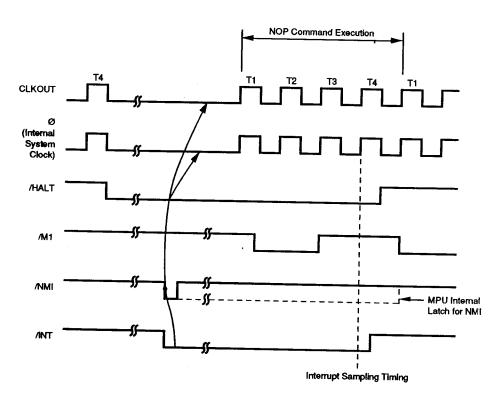

RUN Mode (HALTM=11). The halt release operation is enabled by interrupt request in RUN Mode (Figure 35).

Figure 35. Halt Release Operation Timing By Interrupt Request Signal in RUN Mode

In RUN Mode the internal system clock is not stopped. If the interrupt signal is recognized on the rising clock edge of T4 of the continued NOP instruction, CPU will execute the interrupt process from the next cycle.

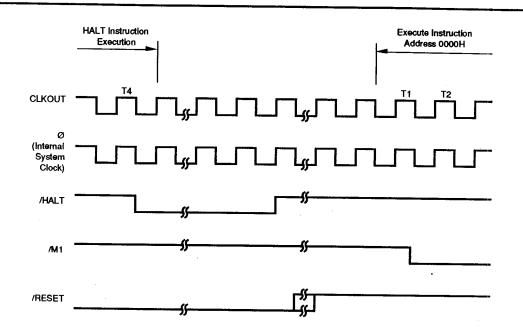

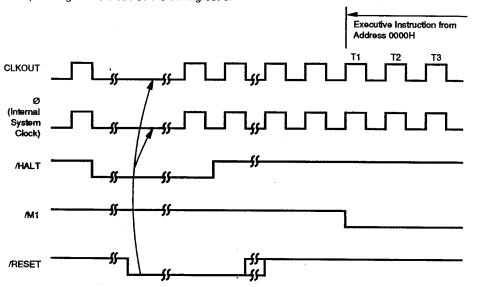

The halt release resets CPU in RUN Mode (Figure 36). After reset, CPU will execute an instruction starting from address 0000H. However, in order to reset the CPU it is

necessary to keep /RESET signal at "0" for at least 3 system clock cycles. (For Z84C13/C15: 3 clock cycles if Reset output is disabled.) In addition, if /RESET signal becomes "1", after the dummy cycle for at least two T states, CPU executes an instruction from address 0000H.

Figure 36. Halt Release Operation Timing By Reset in RUN Mode

IDLE1 Mode (HALTM=00), IDLE2 Mode (HALTM=01). The halt release operation by interrupt signal in IDLE1 Mode is shown in Figure 37 (a) and in IDLE2 Mode in Figure 37 (b).

Figure 37. Halt Release Operation Timing By Interrupt Request Signal in IDLE1/2 Mode

When receiving /NMI or /INT signals, the stopped internal system clock starts to feed. In IDLE1 Mode, the IPC starts clock output on CLKOUT at the same time.

The operation stop of CPU in IDLE2 mode is taking place at "0" level during T4 state in the halt instruction op-code fetch cycle. Therefore, after being restarted by the interrupt signal, CPU executes one NOP instruction and samples an interrupt signal at the rise of T4 state during the execution of this NOP instruction, and executes the interrupt process from next cycle.

If no interrupt signal is accepted during the execution of the first NOP instruction after the internal system clock is restarted, CPU is not released from the halt state. It is placed in IDLE1/2 Mode again at "0" level during T4 state of the NOP instruction, stopping the internal system clock. If /INT signal is not at "0" level at the rise of T4 state, no interrupt request is accepted.

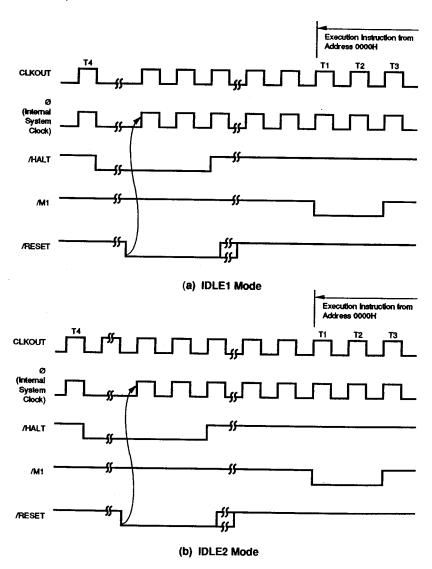

The halt release operation resets the IPC in IDLE1 Mode (Figure 38a) and in IDLE2 Mode (Figure 38b).

Figure 38. Halt Release Operation Timing By Reset in IDLE1/2 Mode