## **Ordering Information**

| Part Number | Package                             | Configuration                | Lead Finish |  |

|-------------|-------------------------------------|------------------------------|-------------|--|

| MIC4123YME  | EPAD 8-Lead SOIC                    | D 8-Lead SOIC Dual Inverting |             |  |

| MIC4123YML  | 8-Lead MLF                          | Lead MLF Dual Inverting      |             |  |

| MIC4124YME  | EPAD 8-Lead SOIC                    | Dual Non-Inverting           | Pb-Free     |  |

| MIC4124YML  | 8-Lead MLF                          | Dual Non-Inverting           | Pb-Free     |  |

| MIC4125YME  | C4125YME EPAD 8-Lead SOIC Inverting |                              | Pb-Free     |  |

| MIC4125YML  | 8-Lead MLF                          | Inverting + Non-Inverting    | Pb-Free     |  |

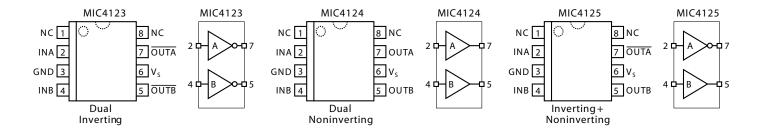

# **Pin & Driver Configuration**

# **Pin Description**

| Pin Number | Pin Name       | Function                                                           |

|------------|----------------|--------------------------------------------------------------------|

| 2/4        | INA / B        | Control Input                                                      |

| 3          | GND            | Ground: Duplicate pins must be externally connected together       |

| 6          | V <sub>s</sub> | Supply Input: Duplicate pins must be externally connected together |

| 7 / 5      | OUTA / B       | Output: Duplicate pins must be externally connected together       |

| 1, 8       | NC             | Not connected                                                      |

| EP         | GND            | Ground: Backside Pad                                               |

## **Absolute Maximum Ratings (Note 1)**

ESD Susceptability, Note 3

# Supply Voltage +24V Input Voltage V<sub>s</sub> + 0.3V to GND – 5V Junction Temperature 150°C Storage Temperature Range -65°C to 150°C Lead Temperature (10 sec.) 300°C

## **Operating Ratings (Note 2)**

| Supply Voltage (V <sub>s</sub> ) | +4.5V to +20V |

|----------------------------------|---------------|

| Junction Temperature Range       | 40°C to 125°C |

| Package Thermal Resistance       |               |

| 4mm X 4mm MLF $\theta_{1A}$      | 45°C/W        |

| EPAD SOIC-8L θ <sub>JA</sub>     |               |

## MIC4123/4124/4125 Electrical Characteristics (Note 4)

$4.5\text{V} \le \text{V}_{\text{S}} \le 20\text{V}$ ;  $\text{T}_{\text{A}} = 25^{\circ}\text{C}$ , **bold** values indicate  $-40^{\circ}\text{C} \le \text{T}_{\text{J}} \le +125^{\circ}\text{C}$ ; unless noted. Input Voltage slew rate >2.5V/ $\mu$ s.

| Symbol              | Parameter                                     | Conditions                                    | Min                   | Тур  | Max                | Units    |

|---------------------|-----------------------------------------------|-----------------------------------------------|-----------------------|------|--------------------|----------|

| Input               |                                               |                                               |                       |      |                    |          |

| $V_{\text{IH}}$     | Logic 1 Input Voltage                         |                                               | 2.4                   | 1.5  |                    | V        |

| $V_{IL}$            | Logic 0 Input Voltage                         |                                               |                       | 1.3  | 0.8                | V        |

| I <sub>IN</sub>     | Input Current                                 | $0V \le V_{IN} \le V_{S}$                     | -1<br><b>-10</b>      |      | 1<br>10            | μA<br>μA |

| Output              | •                                             | •                                             |                       |      | •                  |          |

| $V_{OH}$            | High Output Voltage                           | I <sub>OUT</sub> = 100μA                      | V <sub>s</sub> -0.025 |      |                    | V        |

| $\overline{V}_{OL}$ | Low Output Voltage                            | I <sub>OUT</sub> = -100μA                     |                       |      | 0.025              | V        |

| V <sub>OL</sub> Lo  | Output Resistance HI State                    | I <sub>OUT</sub> = 10mA, V <sub>S</sub> = 20V |                       | 2.3  | 5                  | Ω        |

|                     |                                               |                                               |                       |      | 8                  | Ω        |

|                     | Output Resistance LO State                    | I <sub>OUT</sub> = 10mA, V <sub>S</sub> = 20V |                       | 2.2  | 5                  | Ω        |

|                     |                                               |                                               |                       |      | 8                  | Ω        |

| I <sub>PK</sub>     | Peak Output Current                           |                                               |                       | 3    |                    | Α        |

| I                   | Latch-Up Protection Withstand Reverse Current |                                               | >200                  |      |                    | mA       |

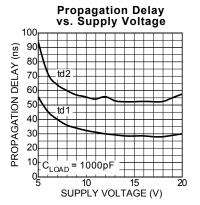

| Switching '         | Time                                          | <u>'</u>                                      |                       |      | •                  |          |

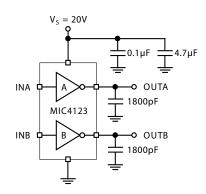

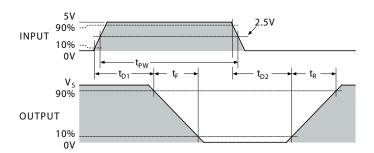

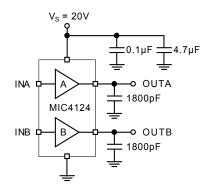

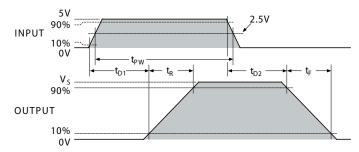

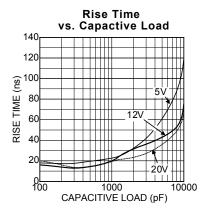

| t <sub>R</sub>      | Rise Time                                     | test Figure 1, C <sub>L</sub> = 1800pF        |                       | 11   | 35<br><b>60</b>    | ns<br>ns |

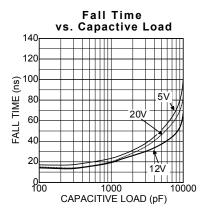

| t <sub>F</sub>      | Fall Time                                     | test Figure 1, C <sub>L</sub> = 1800pF        |                       | 11   | 35<br><b>60</b>    | ns<br>ns |

| $\overline{t}_{D1}$ | Delay Time                                    | test Ffigure 1, C <sub>L</sub> = 1800pF       |                       | 44   | 75<br><b>100</b>   | ns<br>ns |

| $\overline{t}_{D2}$ | Delay Time                                    | test Figure 1, C <sub>L</sub> = 1800pF        |                       | 59   | 75<br><b>100</b>   | ns<br>ns |

| Power Sup           | ply                                           | •                                             | ı                     |      |                    |          |

| I <sub>s</sub>      | Power Supply Current                          | V <sub>IN</sub> = 3.0V (both inputs)          |                       | 1.5  | 2.5<br><b>3.5</b>  | mA<br>mA |

| I <sub>s</sub>      | Power Supply Current                          | V <sub>IN</sub> = 0.0V (both inputs)          |                       | 0.15 | 0.25<br><b>0.3</b> | mA<br>mA |

- Note 1. Exceeding the absolute maximum rating may damage the device.

- Note 2. The device is not guaranteed to function outside its operating rating.

- Note 3. Devices are ESD sensitive. Handling precautions recommended. ESD tested to human body model, 1.5k in series with 100pF.

- Note 4. Specification for packaged product only.

## **Test Circuit**

Figure 1a. Inverting Driver Switching Time

Figure 1b. Non-inverting Driver Switching Time

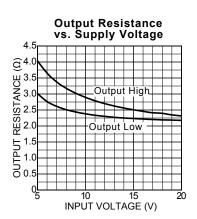

# **Typical Characteristic Curves**

### **Application Information**

Although the MIC4123/24/25 drivers have been specifically constructed to operate reliably under any practical circumstances, there are nonetheless details of usage which will provide better operation of the device.

#### **Supply Bypassing**

Charging and discharging large capacitive loads quickly requires large currents. For example, charging 2000pF from 0 to 15 volts in 20ns requires a constant current of 1.5A. In practice, the charging current is not constant, and will usually peak at around 3A. In order to charge the capacitor, the driver must be capable of drawing this much current, this quickly, from the system power supply. In turn, this means that as far as the driver is concerned, the system power supply, as seen by the driver, must have a **VERY** low impedance.

As a practical matter, this means that the power supply bus must be capacitively bypassed at the driver with at least 100X the load capacitance in order to achieve optimum driving speed. It also implies that the bypassing capacitor must have very low internal inductance and resistance at all frequencies of interest. Generally, this means using two capacitors, one a high-performance low ESR film, the other a low internal resistance ceramic, as together the valleys in their two impedance curves allow adequate performance over a broad enough band to get the job done. PLEASE NOTE that many film capacitors can be sufficiently inductive as to be useless for this service. Likewise, many multilayer ceramic capacitors have unacceptably high internal resistance. Use capacitors intended for high pulse current service (in-house we use WIMA™ film capacitors and AVX Ramguard™ ceramics; several other manufacturers of equivalent devices also exist). The high pulse current demands of capacitive drivers also mean that the bypass capacitors must be mounted very close to the driver in order to prevent the effects of lead inductance or PCB land inductance from nullifying what you are trying to accomplish. For optimum results the sum of the lengths of the leads and the lands from the capacitor body to the driver body should total 2.5cm or less.

Bypass capacitance, and its close mounting to the driver serves two purposes. Not only does it allow optimum performance from the driver, it minimizes the amount of lead length radiating at high frequency during switching, (due to the large  $\Delta$  I) thus minimizing the amount of EMI later available for system disruption and subsequent cleanup. It should also be noted that the actual frequency of the EMI produced by a driver is not the clock frequency at which it is driven, but is related to the highest rate of change of current produced during switching, a frequency generally one or two orders of magnitude higher, and thus more difficult to filter if you let it permeate your system. Good bypassing practice is essential to proper operation of high speed driver ICs.

#### Grounding

Both proper bypassing and proper grounding are necessary for optimum driver operation. Bypassing capacitance only allows a driver to turn the load ON. Eventually (except in rare circumstances) it is also necessary to turn the load OFF. This requires attention to the ground path. Two things other than the driver affect the rate at which it is possible to turn a load off: The adequacy of the grounding available for the driver, and the inductance of the leads from the driver to the load. The latter will be discussed in a separate section.

The E-Pad and MLF packages have an exposed pad under the package. It's important for good thermal performance that this pad is connected to a ground plane.

Best practice for a ground path is obviously a well laid out ground plane. However, this is not always practical, and a poorly-laid out ground plane can be worse than none. Attention to the paths taken by return currents even in a ground plane is essential. In general, the leads from the driver to its load, the driver to the power supply, and the driver to whatever is driving it should all be as low in resistance and inductance as possible. Of the three paths, the ground lead from the driver to the logic driving it is most sensitive to resistance or inductance, and ground current from the load are what is most likely to cause disruption. Thus, these ground paths should be arranged so that they never share a land, or do so for as short a distance as is practical.

To illustrate what can happen, consider the following: The inductance of a 2cm long land, 1.59mm (0.062") wide on a PCB with no ground plane is approximately 45nH. Assuming a dl/dt of 0.3A/ns (which will allow a current of 3A to flow after 10ns, and is thus slightly slow for our purposes) a voltage of 13.5 Volts will develop along this land in response to our postulated  $\Delta I$ . For a 1cm land, (approximately 15nH) 4.5 Volts is developed. Either way, anyone using TTL-level input signals to the driver will find that the response of their driver has been seriously degraded by a common ground path for input to and output from the driver of the given dimensions. Note that this is before accounting for any resistive drops in the circuit. The resistive drop in a 1.59mm (0.062") land of 2oz. Copper carrying 3A will be about 4mV/cm (10mV/in) at DC, and the resistance will increase with frequency as skin effect comes into play.

The problem is most obvious in inverting drivers where the input and output currents are in phase so that any attempt to raise the driver's input voltage (in order to turn the driver's load off) is countered by the voltage developed on the common ground path as the driver attempts to do what it was supposed to. It takes very little common ground path, under these circumstances, to alter circuit operation drastically.

#### **Output Lead Inductance**

The same descriptions just given for PCB land inductance apply equally well for the output leads from a driver to its load, except that commonly the load is located much further away from the driver than the driver's ground bus.

Generally, the best way to treat the output lead inductance problem, when distances greater than 4cm (2") are involved, requires treating the output leads as a transmission line. Unfortunately, as both the output impedance of the driver and the input impedance of the MOSFET gate are at least an order of magnitude lower than the impedance of common coax, using coax is seldom a cost-effective solution. A twisted pair works about as well, is generally lower in cost, and allows use of a

wider variety of connectors. The second wire of the twisted pair should carry common from as close as possible to the ground pin of the driver directly to the ground terminal of the load. Do not use a twisted pair where the second wire in the pair is the output of the other driver, as this will not provide a complete current path for either driver. Likewise, do not use a twisted triad with two outputs and a common return unless both of the loads to be driver are mounted extremely close to each other, and you can guarantee that they will never be switching at the same time.

For output leads on a printed circuit, the general rule is to make them as short and as wide as possible. The lands should also be treated as transmission lines: i.e., minimize sharp bends, or narrowings in the land, as these will cause ringing. For a rough estimate, on a 1.59mm (0.062") thick G-10 PCB a pair of opposing lands each 2.36mm (0.093") wide translates to a characteristic impedance of about  $50\Omega$ . Half that width suffices on a 0.787mm (0.031") thick board. For accurate impedance matching with a MIC4123/24/25 driver, on a 1.59mm (0.062") board a land width of 42.75mm (1.683") would be required, due to the low impedance of the driver and (usually) its load. This is obviously impractical under most circumstances. Generally the tradeoff point between lands and wires comes when lands narrower than 3.18mm (0.125") would be required on a 1.59mm (0.062") board.

To obtain minimum delay between the driver and the load, it is considered best to locate the driver as close as possible to the load (using adequate bypassing). Using matching transformers at both ends of a piece of coax, or several matched lengths of coax between the driver and the load, works in theory, but is not optimum.

#### **Driving at Controlled Rates**

Occasionally there are situations where a controlled rise or fall time (which may be considerably longer than the normal rise or fall time of the driver's output) is desired for a load. In such cases it is still prudent to employ best possible practice in terms of bypassing, grounding and PCB layout, and then reduce the switching speed of the load (NOT the driver) by adding a noninductive series resistor of appropriate value between the output of the driver and the load. For situations where only rise or only fall should be slowed, the resistor can be paralleled with a fast diode so that switching in the other direction remains fast. Due to the Schmitt-trigger action of the driver's input it is not possible to slow the rate of rise (or fall) of the driver's input signal to achieve slowing of the output.

#### Input Stage

The input stage of the MIC4123/24/25 consists of a single-MOSFET class A stage with an input capacitance of <8pF. This capacitance represents the maximum load from the driver that will be seen by its controlling logic. The drain load on the input MOSFET is a –2mA current source. Thus, the quiescent current drawn by the driver varies, depending upon the logic state of the input.

Following the input stage is a buffer stage which provides ~400mV of hysteresis for the input, to prevent oscillations when slowly-changing input signals are used or when noise

is present on the input. Input voltage switching threshold is approximately 1.5V which makes the driver directly compatible with TTL signals, or with CMOS powered from any supply voltage between 3V and 15V.

The MIC4123/24/25 drivers can also be driven directly by the MIC9130, MIC3808, MIC38C42, and similar switch mode power supply ICs. By relocating the main switch drive function into the driver rather than using the somewhat limited drive capabilities of a PWM IC. The PWM IC runs cooler, which generally improves its performance and longevity, and the main switches switch faster, which reduces switching losses and increase system efficiency.

The input protection circuitry of the MIC4123/24/25, in addition to providing 2kV or more of ESD protection, also works to prevent latchup or logic upset due to ringing or voltage spiking on the logic input terminal. In most CMOS devices when the logic input rises above the power supply terminal, or descends below the ground terminal, the device can be destroyed or rendered inoperable until the power supply is cycled OFF and ON. The MIC4123/24/25 drivers have been designed to prevent this. Input voltages excursions as great as 5V below ground will not alter the operation of the device. Input excursions above the power supply voltage will result in the excess voltage being conducted to the power supply terminal of the IC. Because the excess voltage is simply conducted to the power terminal, if the input to the driver is left in a high state when the power supply to the driver is turned off, currents as high as 30mA can be conducted through the driver from the input terminal to its power supply terminal. This may overload the output of whatever is driving the driver, and may cause other devices that share the driver's power supply, as well as the driver, to operate when they are assumed to be off, but it will not harm the driver itself. Excessive input voltage will also slow the driver down, and result in much longer internal propagation delays within the drivers. T<sub>D2</sub>, for example, may increase to several hundred nanoseconds. In general, while the driver will accept this sort of misuse without damage, proper termination of the line feeding the driver so that line spiking and ringing are minimized, will always result in faster and more reliable operation of the device, leave less EMI to be filtered elsewhere, be less stressful to other components in the circuit, and leave less chance of unintended modes of operation.

#### **Power Dissipation**

CMOS circuits usually permit the user to ignore power dissipation. Logic families such as 4000 series and 74Cxxx have outputs which can only source or sink a few milliamps of current, and even shorting the output of the device to ground or  $V_{\rm CC}$  may not damage the device. CMOS drivers, on the other hand, are intended to source or sink several Amps of current. This is necessary in order to drive large capacitive loads at frequencies into the megahertz range. Package power dissipation of driver ICs can easily be exceeded when driving large loads at high frequencies. Care must therefore be paid to device dissipation when operating in this domain.

The Supply Current vs Frequency and Supply Current vs Load characteristic curves furnished with this data sheet aid in estimating power dissipation in the driver. Operating frequency, power supply voltage, and load all affect power dissipation.

Given the power dissipation in the device, and the thermal resistance of the package, junction operating temperature for any ambient is easy to calculate. For example, the thermal resistance of the 8-pin E-Pas SOIC package, from the datasheet, is 58°C/W. In a 25°C ambient, then, using a maximum junction temperature of 150°C, this package will dissipate 2.16W.

Accurate power dissipation numbers can be obtained by summing the three sources of power dissipation in the device:

- Load power dissipation (P<sub>1</sub>)

- Quiescent power dissipation (P<sub>o</sub>)

- Transition power dissipation  $(P_{\tau})$

Calculation of load power dissipation differs depending upon whether the load is capacitive, resistive or inductive.

#### Resistive Load Power Dissipation

Dissipation caused by a resistive load can be calculated as:

$$P_L = I^2 R_O D$$

where:

I = the current drawn by the load

$R_0$  = the output resistance of the driver when the output is high, at the power supply voltage used (See characteristic curves)

D = fraction of time the load is conducting (duty cycle)

#### Capacitive Load Power Dissipation

Dissipation caused by a capacitive load is simply the energy placed in, or removed from, the load capacitance by the driver. The energy stored in a capacitor is described by the equation:

$$E = 1/2 C V^2$$

As this energy is lost in the driver each time the load is charged or discharged, for power dissipation calculations the 1/2 is removed. This equation also shows that it is good practice not to place more voltage in the capacitor than is necessary, as dissipation increases as the square of the voltage applied to the capacitor. For a driver with a capacitive load:

$$P_{1} = f C (V_{s})^{2}$$

where:

f = Operating Frequency

C = Load Capacitance

V<sub>s</sub> = Driver Supply Voltage

#### Inductive Load Power Dissipation

For inductive loads the situation is more complicated. For the part of the cycle in which the driver is actively forcing current into the inductor, the situation is the same as it is in the resistive case:

$$P_{11} = I^2 R_0 D$$

However, in this instance the R<sub>o</sub> required may be either the on resistance of the driver when its output is in the high state, or its on resistance when the driver is in the low state, depending upon how the inductor is connected, and this is still only half the story. For the part of the cycle when the inductor is forcing current through the driver, dissipation is best described as

$$P_{L2} = I V_{D} (1 - D)$$

where  $V_{D}$  is the forward drop of the clamp diode in the driver (generally around 0.7V). The two parts of the load dissipation must be summed in to produce P,

$$P_{L} = P_{L1} + P_{L2}$$

#### **Quiescent Power Dissipation**

Quiescent power dissipation (PQ, as described in the input section) depends on whether the input is high or low. A low input will result in a maximum current drain (per driver) of ≤0.2mA; a logic high will result in a current drain of ≤2.0mA. Quiescent power can therefore be found from:

$$P_0 = V_s [D I_H + (1 - D) I_I]$$

where:

$I_{H}$  = quiescent current with input high  $I_{I}$  = quiescent current with input low

D = fraction of time input is high (duty cycle)

V<sub>s</sub> = power supply voltage

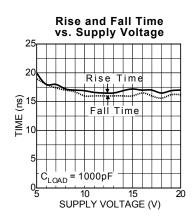

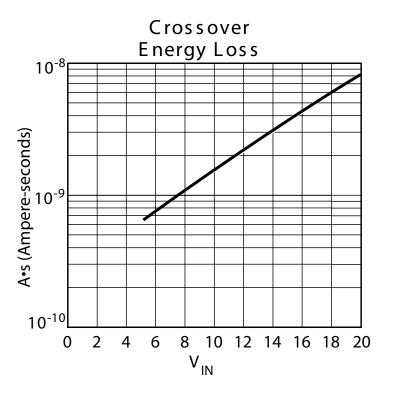

#### **Transition Power Dissipation**

Transition power is dissipated in the driver each time its output changes state, because during the transition, for a very brief interval, both the N- and P-channel MOSFETs in the output totem-pole are ON simultaneously, and a current is conducted through them from V<sub>s</sub> to ground. The transition power dissipation is approximately:

$$P_{\tau} = f V_{s} (A \cdot s)$$

where (A•s) is a time-current factor derived from Figure 2.

Total power (PD) then, as previously described is just

$$P_D = P_L + P_D + P_T$$

Examples show the relative magnitude for each term.

EXAMPLE 1: A MIC4123 operating on a 12V supply driving two capacitive loads of 3000pF each, operating at 250kHz, with a duty cycle of 50%, in a maximum ambient of 60°C.

First calculate load power loss:

$$P_L = f x C x (V_S)^2$$

$P_L = 250,000 x (3 x 10^{-9} + 3 x 10^{-9}) x 12^2$

$= 0.2160W$

Then transition power loss:

$$P_T = f x V_S x (A \cdot s)$$

= 250,000 • 12 • 2.2 x 10<sup>-9</sup> = 6.6mW

Then guiescent power loss:

$$P_Q = V_S \times [D \times I_H + (1 - D) \times I_L]$$

= 12 \times [(0.5 \times 0.0035) + (0.5 \times 0.0003)]

= 0.0228W

Total power dissipation, then, is:

$$P_D = 0.2160 + 0.0066 + 0.0228$$

= 0.2454W

Assuming an E-Pad SOIC package, with an  $\theta_{JA}$  of 58°C/W, this will result in the junction running at:

$$0.2454 \times 58 = 14.2$$

°C

above ambient, which, given a maximum ambient temperature of 60°C, will result in a maximum junction temperature of 89.4°C.

EXAMPLE 2: A MIC4124 operating on a 15V input, with one driver driving a  $50\Omega$  resistive load at 1MHz, with a duty cycle of 67%, and the other driver quiescent, in a maximum ambient temperature of 40°C:

$$P_L = I^2 \times R_O \times D$$

First,  $I_{\cap}$  must be determined.

$$I_o = V_s / (R_o + R_{LOAD})$$

Given R<sub>o</sub> from the characteristic curves then,

$$I_0 = 15 / (3.3 + 50)$$

$I_0 = 0.281A$

and:

$$P_L = (0.281)^2 \times 3.3 \times 0.67$$

= 0.174W

$P_T = F \times V_S \times (A \cdot s)/2$

(because only one side is operating)

=

$$(1,000,000 \times 15 \times 3.3 \times 10^{-9}) / 2$$

=  $0.025 \text{ W}$

and:

$$P_Q = 15 \times [(0.67 \times 0.00125) + (0.33 \times 0.000125) + (1 \times 0.000125)]$$

(this assumes that the unused side of the driver has its input grounded, which is more efficient)

= 0.015W

then:

$$P_D = 0.174 + 0.025 + 0.0150$$

= 0.213W

In a MLF with an  $\theta_{JA}$  of 60°C/W, this amount of power results in a junction temperature given the maximum 40°C ambient of:

$$(0.213 \times 100) + 40 = 52.8$$

°C

The actual junction temperature will be lower than calculated both because duty cycle is less than 100% and because the graph lists  $R_{\rm DS(on)}$  at a  $T_{\rm J}$  of 125°C and the  $R_{\rm DS(on)}$  at 52.8°C  $T_{\rm J}$  will be somewhat lower.

#### **Definitions**

C<sub>1</sub> = Load Capacitance in Farads.

D = Duty Cycle expressed as the fraction of time the input to the driver is high.

f = Operating Frequency of the driver in Hertz.

I<sub>H</sub> = Power supply current drawn by a driver when both inputs are high and neither output is loaded.

I<sub>L</sub> = Power supply current drawn by a driver when both inputs are low and neither output is loaded.

$I_p$  = Output current from a driver in Amps.

P<sub>D</sub> = Total power dissipated in a driver in Watts.

P<sub>L</sub> = Power dissipated in the driver due to the driver's load in Watts.

P<sub>o</sub> = Power dissipated in a quiescent driver in Watts.

P<sub>T</sub> = Power dissipated in a driver when the output changes states ("shoot-through current") in Watts. NOTE: The "shoot-through" current from a dual transition (once up, once down) for both drivers is stated in the graph on the following page in amperenanoseconds. This figure must be multiplied by the number of repetitions per second (frequency to find

$R_0$  = Output resistance of a driver in Ohms.

$V_s$  = Power supply voltage to the IC in Volts.

**NOTE:** THE VALUES ON THIS GRAPH REPRESENT THE LOSS SEEN BY BOTH DRIVERS IN A PACKAGE DURING ONE COMPLETE CYCLE. FOR A SINGLE DRIVER DIVIDE THE STATED VALUES BY 2. FOR A SINGLE TRANSITION OF A SINGLE DRIVER, DIVIDE THE STATED VALUE BY 4.

Figure 2.

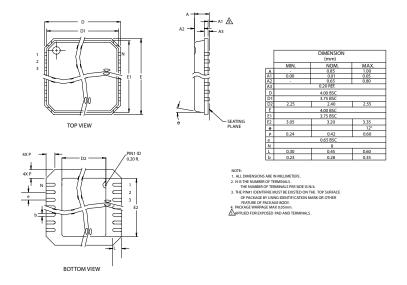

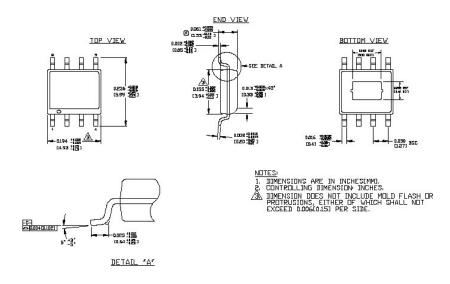

## **Package Information**

8-Pin 4x4 MLF (ML)

8-Pin Exposed Pad SOIC (ME)

#### MICREL INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

This information furnished by Micrel in this data sheet is believed to be accurate and reliable. However no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2004 Micrel Incorporated