# Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

#### **Absolute Maximum Ratings**

| V <sub>CC</sub> , ENABLE, ENABLE, IN      | 0.3V to +6V                      |

|-------------------------------------------|----------------------------------|

| OUT, OUT (push-pull)                      | 0.3V to (V <sub>CC</sub> + 0.3V) |

| OUT, OUT (open-drain)                     |                                  |

| CDELAY                                    | 0.3V to (V <sub>CC</sub> + 0.3V) |

| Output Current (all pins)                 | ±20mA                            |

| Continuous Power Dissipation ( $T_A = +7$ | 70°C)                            |

|                                           |                                  |

6-Pin μDFN (derate 2.1mW/°C above +70°C) .........167.7mW 6-Pin Thin SOT23 (derate 9.1mW/°C above +70°C)....727.3mW

| Operating Temperature Range       | -40°C to +125°C |

|-----------------------------------|-----------------|

| Storage Temperature Range         | -65°C to +150°C |

| Junction Temperature              | +150°C          |

| Lead Temperature (soldering, 10s) | +300°C          |

| Soldering Temperature (reflow)    | +260°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Package Thermal Characteristics (Note 1)

μDFN

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......477°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......122C/W

Thin SOT23

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......110°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......50°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four layer board. For detailed information on package thermal considerations refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

(V<sub>CC</sub> = 1.5V to 5.5V,  $T_A$  = -40°C to +125°C, unless otherwise specified. Typical values are at V<sub>CC</sub> = 3.3V and  $T_A$  = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                      | SYMBOL              | CONDITIONS                                            | MIN   | TYP  | MAX   | UNITS |

|--------------------------------|---------------------|-------------------------------------------------------|-------|------|-------|-------|

| SUPPLY                         |                     |                                                       |       |      |       |       |

| Operating Voltage Range        | V <sub>CC</sub>     |                                                       | 1.5   |      | 5.5   | V     |

| Undervoltage Lockout (Note 3)  | UVLO                | V <sub>CC</sub> falling                               | 1.20  |      | 1.35  | V     |

| V <sub>CC</sub> Supply Current | Icc                 | V <sub>CC</sub> = 3.3V, no load                       |       | 10   | 20    | μA    |

| IN                             |                     | -<br>-                                                |       |      |       |       |

| Threshold Voltage              | V <sub>TH</sub>     | V <sub>IN</sub> rising, 1.5V < V <sub>CC</sub> < 5.5V | 0.491 | 0.5  | 0.509 | V     |

| Hysteresis                     | V <sub>HYST</sub>   | V <sub>IN</sub> falling                               |       | 5    |       | mV    |

| Input Current (Note 4)         | I <sub>IN</sub>     | V <sub>IN</sub> = 0V or V <sub>CC</sub>               | -15   |      | +15   | nA    |

| CDELAY                         |                     |                                                       |       |      |       |       |

| Delay Charge Current           | I <sub>CD</sub>     |                                                       | 200   | 250  | 300   | nA    |

| Delay Threshold                | V <sub>TCD</sub>    | CDELAY rising                                         | 0.95  | 1.00 | 1.05  | V     |

| CDELAY Pulldown Resistance     | R <sub>CDELAY</sub> |                                                       |       | 130  | 500   | Ω     |

| ENABLE/ENABLE                  |                     |                                                       |       |      |       |       |

| Input Low Voltage              | VIL                 |                                                       |       |      | 0.4   | V     |

| Input High Voltage             | VIH                 |                                                       | 1.4   |      |       | V     |

| Input Leakage Current          | I <sub>LEAK</sub>   | ENABLE, ENABLE = V <sub>CC</sub> or GND               | -100  |      | +100  | nA    |

# Ultra-Small, Adjustable Sequencing/ **Supervisory Circuits**

#### **Electrical Characteristics (continued)**

(V<sub>CC</sub> = 1.5V to 5.5V,  $T_A$  = -40°C to +125°C, unless otherwise specified. Typical values are at V<sub>CC</sub> = 3.3V and  $T_A$  = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                                  | SYMBOL             | CONDITIONS                                                                        |                       | TIONS                         | MIN                      | TYP | MAX | UNITS |

|--------------------------------------------|--------------------|-----------------------------------------------------------------------------------|-----------------------|-------------------------------|--------------------------|-----|-----|-------|

| OUT/OUT                                    |                    |                                                                                   |                       |                               |                          |     |     |       |

| Output Low Voltage (Open-Drain             |                    | V <sub>CC</sub> ≥ 1.2V, I <sub>SINK</sub> = 90µA,<br>MAX6895/MAX6897/MAX6899 only |                       |                               |                          | 0.3 |     |       |

| or Push-Pull)                              | V <sub>OL</sub>    | V <sub>CC</sub> ≥ 2.25V,                                                          | I <sub>SINK</sub> = 0 | .5mA                          |                          |     | 0.3 | V     |

|                                            |                    | V <sub>CC</sub> ≥ 4.5V, Ig                                                        | SINK = 1n             | nA                            |                          |     | 0.4 |       |

| Output High Voltage (Bush Bull)            | Mari               | V <sub>CC</sub> ≥ 2.25V,                                                          | ISOURCE               | _ = 500μA                     | 0.8 x<br>V <sub>CC</sub> |     |     |       |

| Output High Voltage (Push-Pull)            | V <sub>OH</sub>    | V <sub>CC</sub> ≥ 4.5V, I                                                         | SOURCE                | = 800µA                       | 0.8 x<br>V <sub>CC</sub> |     |     |       |

| Output Open-Drain Leakage<br>Current       | I <sub>LKG</sub>   | Output high impedance, V <sub>OUT</sub> = 28V                                     |                       |                               |                          | 1   | μA  |       |

| TIMING                                     |                    |                                                                                   |                       |                               |                          |     |     |       |

|                                            | <sup>t</sup> DELAY | V <sub>IN</sub> rising                                                            | C <sub>CDELA</sub>    | <sub>.Υ</sub> = 0μF           |                          | 40  |     | μs    |

| IN to OUT/OUT Propagation Delay            |                    | C <sub>CDELAY</sub> = 0.047µF                                                     |                       |                               | 190                      |     | ms  |       |

|                                            | t <sub>DL</sub>    | V <sub>IN</sub> falling                                                           |                       |                               |                          | 16  |     | μs    |

| Startup Delay (Note 5)                     |                    |                                                                                   |                       |                               |                          | 2   |     | ms    |

| ENABLE/ENABLE Minimum<br>Input Pulse Width | t <sub>PW</sub>    |                                                                                   |                       |                               | 1                        |     |     | μs    |

| ENABLE/ENABLE Glitch<br>Rejection          |                    |                                                                                   |                       |                               |                          | 100 |     | ns    |

| ENABLE/ENABLE to OUT/OUT<br>Delay          | tOFF               | From device enabled to device disabled                                            |                       |                               | 150                      |     | ns  |       |

|                                            | t <sub>PROPP</sub> | From device c<br>(P version)                                                      | disabled t            | o device enabled              |                          | 150 |     | ns    |

| ENABLE/ENABLE to OUT/OUT                   |                    | From device disabled                                                              | disabled              | C <sub>CDELAY</sub> = 0µF     |                          | 20  |     | μs    |

| Delay                                      | t <sub>PROPA</sub> | to device enabled<br>(A version)                                                  |                       | C <sub>CDELAY</sub> = 0.047µF |                          | 190 |     | ms    |

Note 2: All devices are production tested at T<sub>A</sub> = +25°C. Limits over temperature are guaranteed by design.

Note 3: When V<sub>CC</sub> falls below the UVLO threshold, the outputs will deassert (OUT goes low, OUT goes high). When V<sub>CC</sub> falls below 1.2V, the out cannot be determined.

Note 4: Guaranteed by design.

Note 5: During the initial power-up, V<sub>CC</sub> must exceed 1.5V for at least 2ms before the output is guaranteed to be in the correct state.

### Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

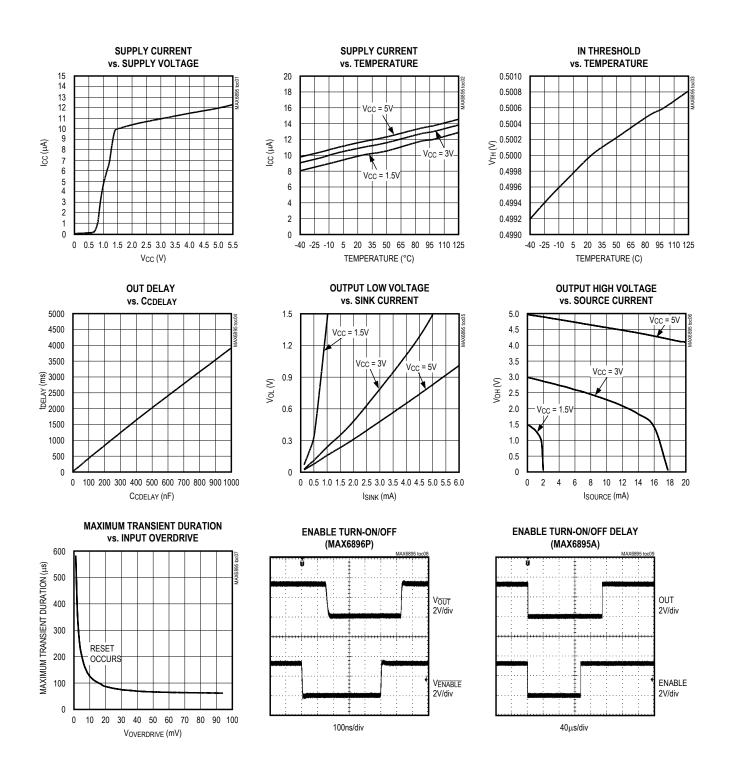

### **Typical Operating Characteristics**

(V<sub>CC</sub> = 3.3V and T<sub>A</sub> = +25°C, unless otherwise noted.)

# Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

### **Pin Description**

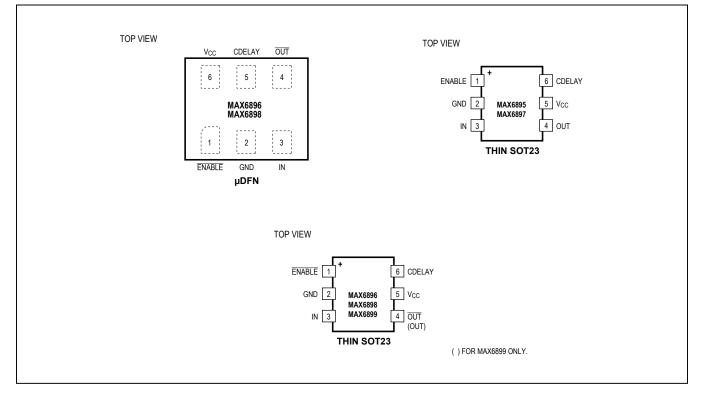

|      |                | Р    | IN            |      |               |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------|----------------|------|---------------|------|---------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 6895/<br>(6897 |      | 6896/<br>6898 | МАХ  | 6899          | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| μDFN | THIN<br>SOT23  | μDFN | THIN<br>SOT23 | μDFN | THIN<br>SOT23 |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1    | 1              |      |               |      |               | ENABLE          | Active-High Logic-Enable Input. Drive ENABLE low to immediately deassert the output to its false state (OUT = low or OUT = high) independent of $V_{IN}$ . With $V_{IN}$ above $V_{TH}$ , drive ENABLE high to assert the output to its true state (OUT = high or OUT = low) after the adjustable delay period (MAX689_A) or a 150ns propagation delay (MAX689_P).                                                                                                                                                                                                                          |

| _    | _              | 1    | 1             | 1    | 1             | ENABLE          | Active-Low Logic-Enable Input. Drive $\overline{\text{ENABLE}}$ high to<br>immediately deassert the output to its false state (OUT =<br>low or $\overline{\text{OUT}}$ = high) independent of V <sub>IN</sub> . With V <sub>IN</sub> above<br>V <sub>TH</sub> , drive $\overline{\text{ENABLE}}$ low to assert the output to its true<br>state (OUT = high or $\overline{\text{OUT}}$ = low) after the adjustable<br>delay period (MAX689_A) or a 150ns propagation delay<br>(MAX689_P).                                                                                                    |

| 2    | 2              | 2    | 2             | 2    | 2             | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 3    | 3              | 3    | 3             | 3    | 3             | IN              | High-Impedance Monitor Input. Connect IN to an external resistive divider to set the desired monitored threshold. The output changes state when V <sub>IN</sub> rises above 0.5V and when V <sub>IN</sub> falls below 0.495V.                                                                                                                                                                                                                                                                                                                                                               |

| 4    | 4              | _    | _             | 4    | 4             | OUT             | Active-High Sequencer/Monitor Output, Push-Pull (MAX6895/MAX6899) or Open-Drain (MAX6897). OUT is asserted to its true state (OUT = high) when $V_{IN}$ is above $V_{TH}$ and the enable input is in its true state (ENABLE = high or ENABLE = low) for the capacitor-adjusted delay period. OUT is deasserted to its false state (OUT = low) immediately after $V_{IN}$ drops below $V_{TH}$ - 5mV or the enable input is in its false state (ENABLE = low or ENABLE = high). The open-drain version requires an external pullup resistor.                                                 |

| _    | _              | 4    | 4             | _    | _             | Ουτ             | Active-Low Sequencer/Monitor Output, Push-Pull (MAX6896) or Open-Drain (MAX6898). OUT is asserted to its true state ( $\overline{OUT}$ = low) when V <sub>IN</sub> is above V <sub>TH</sub> and the enable input is in its true state (ENABLE = high or ENABLE = low) after the CDELAY adjusted timeout period. OUT is deasserted to its false state ( $\overline{OUT}$ = high) immediately after V <sub>IN</sub> drops below V <sub>TH</sub> - 5mV or the enable input is in its false state (ENABLE = low or ENABLE = high). The open-drain version requires an external pullup resistor. |

| 5    | 6              | 5    | 6             | 5    | 6             | CDELAY          | Capacitor-Adjustable Delay. Connect an external capacitor ( $C_{CDELAY}$ ) from CDELAY to GND to set the IN to OUT (and ENABLE to OUT or ENABLE to OUT for A version devices) delay period. t <sub>DELAY</sub> = ( $C_{CDELAY}$ x 4.0 x 10 <sup>6</sup> ) + 40µs. There is a fixed short delay (40µs, typ) for the output deasserting when V <sub>IN</sub> falls below V <sub>TH</sub> .                                                                                                                                                                                                    |

| 6    | 5              | 6    | 5             | 6    | 5             | V <sub>CC</sub> | Supply Voltage Input. Connect a 1.5V to 5.5V supply to $V_{CC}$ to power the device. For noisy systems, bypass with a 0.1 $\mu F$ ceramic capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

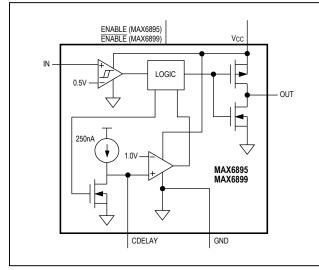

Figure 1. MAX6895/MAX6899 Functional Diagram

#### **Detailed Description**

The MAX6895–MAX6899 is a family of ultra-small, lowpower, sequencing/supervisory circuits. These devices provide adjustable voltage monitoring for inputs down to 0.5V. They are ideal for use in power-supply sequencing, reset sequencing, and power-switching applications. Multiple devices can be cascaded for complex sequencing applications.

Voltage monitoring is performed through a high-impedance input (IN) with an internally fixed 0.5V threshold. When the voltage at IN falls below 0.5V or when the enable input is deasserted (ENABLE = low or  $\overline{\text{ENABLE}}$  = high), the output deasserts (OUT goes low or  $\overline{\text{OUT}}$  goes high). When VIN rises above 0.5V and the enable input is asserted (ENABLE = high or  $\overline{\text{ENABLE}}$  = low), the output asserts (OUT goes high or OUT goes low) after a capacitor-programmable time delay.

With VIN above 0.5V, the enable input can be used to turn the output on or off. After the enable input is asserted, the output turns on with a capacitor-programmable delay period (A version) or with a 150ns propagation delay (P version). Tables 1, 2, and 3 detail the output state depending on the various input and enable conditions.

| IN                                | ENABLE | OUT                                  |

|-----------------------------------|--------|--------------------------------------|

| V <sub>IN</sub> < V <sub>TH</sub> | Low    | Low                                  |

| $V_{IN} < V_{TH}$                 | High   | Low                                  |

| $V_{IN} > V_{TH}$                 | Low    | Low                                  |

|                                   |        | OUT = V <sub>CC</sub><br>(MAX6895)   |

| $V_{IN} > V_{TH}$                 | High   | OUT = high<br>Impedance<br>(MAX6897) |

#### Table 1. MAX6895/MAX6897 Output

#### Table 2. MAX6896/MAX6898 Output

| IN                                | ENABLE | OUT                                                 |                                   |

|-----------------------------------|--------|-----------------------------------------------------|-----------------------------------|

|                                   |        | $\overline{OUT} = V_{CC} (MAX6896)$                 |                                   |

| V <sub>IN</sub> < V <sub>TH</sub> | Low    | OUT = high impedance<br>(MAX6898)                   |                                   |

|                                   |        | $\overline{\text{OUT}}$ = V <sub>CC</sub> (MAX6896) |                                   |

| V <sub>IN</sub> < V <sub>TH</sub> | High   | High                                                | OUT = high impedance<br>(MAX6898) |

| V <sub>IN</sub> > V <sub>TH</sub> | Low    | Low                                                 |                                   |

|                                   |        | $\overline{\text{OUT}}$ = V <sub>CC</sub> (MAX6896) |                                   |

| V <sub>IN</sub> > V <sub>TH</sub> | High   | OUT = high impedance<br>(MAX6898)                   |                                   |

#### Table 3. MAX6899 Output

| IN                                | ENABLE | OUT  |

|-----------------------------------|--------|------|

| V <sub>IN</sub> < V <sub>TH</sub> | Low    | Low  |

| V <sub>IN</sub> < V <sub>TH</sub> | High   | Low  |

| V <sub>IN</sub> > V <sub>TH</sub> | Low    | High |

| V <sub>IN</sub> > V <sub>TH</sub> | High   | Low  |

#### Supply Input (V<sub>CC</sub>)

The device operates with a V<sub>CC</sub> supply voltage from 1.5V to 5.5V. To maintain a 1.8% accurate threshold, VCC must be above 1.5V. When V<sub>CC</sub> falls below the UVLO threshold, the output deasserts. When V<sub>CC</sub> falls below 1.2V the output state cannot be determined. For noisy systems, connect a 0.1µF ceramic capacitor from V<sub>CC</sub> to GND as close to the device as possible. For the push-pull active-high output option, a 100k $\Omega$  external pulldown resistor to ground ensures the correct logic state for V<sub>CC</sub> down to 0.

### Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

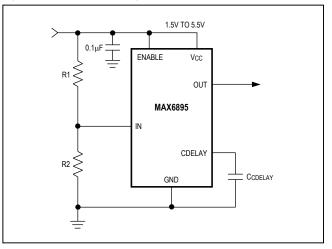

#### Monitor Input (IN)

Connect the center point of a resistive divider to IN to monitor external voltages (see R1 and R2 of the *Typical Operating Circuit*). IN has a rising threshold of V<sub>TH</sub> = 0.5V and a falling threshold of 0.495V (5mV hysteresis). When V<sub>IN</sub> rises above V<sub>TH</sub> and ENABLE is high (or ENABLE is low) OUT goes high (OUT goes low) after the programmed t<sub>DELAY</sub> period. When V<sub>IN</sub> falls below 0.495V, OUT goes low (OUT goes high) after a 16µs delay. IN has a maximum input current of 15nA so large-value resistors are permitted without adding significant error to the resistive divider.

#### Adjustable Delay (CDELAY)

When  $V_{IN}$  rises above  $V_{TH}$  with ENABLE high (ENABLE low), the internal 250nA current source begins charging an external capacitor connected from CDELAY to GND. When the voltage at CDELAY reaches 1V, the output

asserts (OUT goes high or  $\overline{\text{OUT}}$  goes low). When the output asserts, C<sub>CDELAY</sub> is immediately discharged. Adjust the delay (t<sub>DELAY</sub>) from when V<sub>IN</sub> rises above V<sub>TH</sub> (with ENABLE high or ENABLE low) to OUT going high ( $\overline{\text{OUT}}$  going low) according to the equation:

where  $\mathsf{C}_{\mathsf{CDELAY}}$  is the external capacitor from CDELAY to GND.

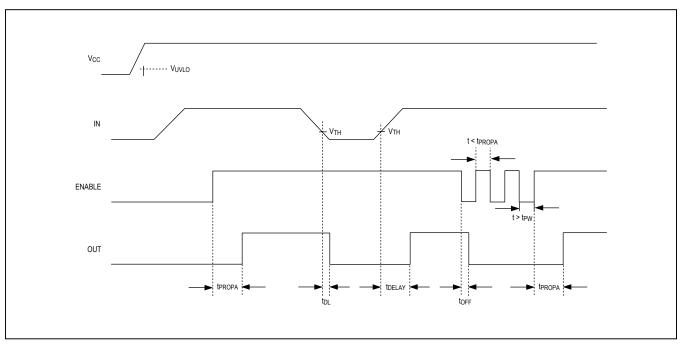

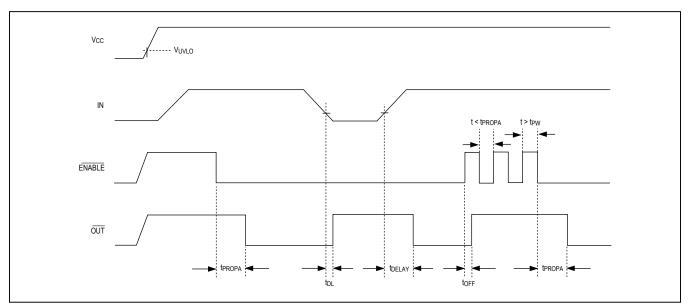

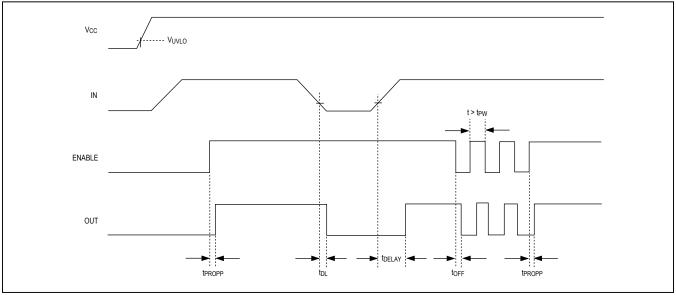

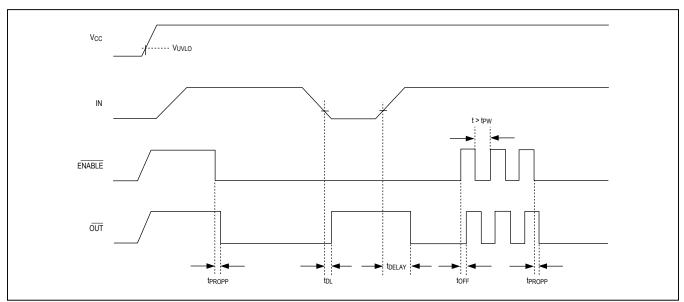

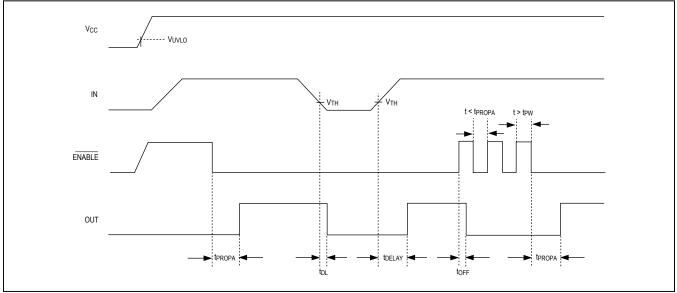

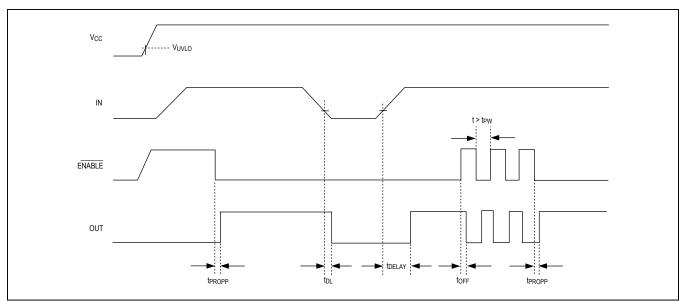

For adjustable delay devices (A version), when  $V_{IN} > 0.5V$  and ENABLE goes from low to high (ENABLE goes from high to low) the output asserts after a  $t_{DELAY}$  period. For nonadjustable delay devices (P version) there is a 1µs propagation delay from when the enable input is asserted to when the output asserts. Figures 2 through 5 show the timing diagrams for the adjustable and fixed delay versions, respectively.

Figure 2. MAX6895A/MAX6897A Timing Diagram

# Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

Figure 3. MAX6896A/MAX6898A Timing Diagram

Figure 4. MAX6895P/MAX6897P Timing Diagram

# Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

Figure 5. MAX6896P/MAX6898P Timing Diagram

Figure 6. MAX6899A Timing Diagram

### Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

Figure 7. MAX6899P Timing Diagram

#### Enable Input (ENABLE or ENABLE)

The MAX6895/MAX6897 offer an active-high enable input (ENABLE), while the MAX6896/MAX6898/MAX6899 offer an active-low enable input (ENABLE). With V<sub>IN</sub> above V<sub>TH</sub>, drive ENABLE high (ENABLE low) to force OUT high (OUT low) after the adjustable delay time (A versions). For P version devices, when V<sub>IN</sub> > 0.5V and enable is asserted, the output asserts after typically 150ns.

The enable input has logic-high and logic-low voltage thresholds of 1.4V and 0.4V, respectively. For both versions, when  $V_{IN} > 0.5V$ , drive ENABLE low (ENABLE high) to force OUT low (OUT high) within 150ns typ.

#### Output (OUT or OUT)

The MAX6895/MAX6899 offer an active-high, push-pull output (OUT), and the MAX6896 offers an active-low push-pull output ( $\overline{OUT}$ ). The MAX6897 offers an active-high open-drain output (OUT), and the MAX6898 offers an active-low open-drain output ( $\overline{OUT}$ ).

Push-pull output devices are referenced to  $V_{CC}$ . Opendrain outputs can be pulled up to 28V.

#### **Applications Information**

#### Input Threshold

The MAX6895–MAX6899 monitor the voltage on IN with an external resistive divider (see R1 and R2 in the *Typical Operating Circuit*). Connect R1 and R2 as close to IN as possible. R1 and R2 can have very high values to minimize current consumption due to low IN leakage currents ( $\pm$ 15nA max). Set R2 to some conveniently high value (1M $\Omega$ , for example) and calculate R1 based on the desired monitored voltage using the following formula:

$$R1 = R2 \times \left[\frac{V_{MONITOR}}{V_{IN}} - 1\right] *$$

where  $V_{MONITOR}$  is the desired monitored voltage and  $V_{IN}$  is the detector input threshold (0.5V).

### Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

# Pullup Resistor Values (MAX6897/MAX6898)

The exact value of the pullup resistors for the open-drain outputs is not critical, but some consideration should be made to ensure the proper logic levels when the device is sinking current. For example, if  $V_{CC} = 2.25V$  and the pullup voltage is 28V, you would try to keep the sink current less than 0.5mA as shown in the *Electrical Characteristics* table. As a result, the pullup resistor should be greater than 56k $\Omega$ . For a 12V pullup, the resistor should be larger than 24k $\Omega$ . It should be noted that the ability to sink current is dependent on the V<sub>CC</sub> supply voltage.

#### **Typical Application Circuits**

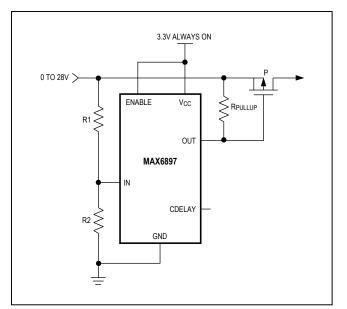

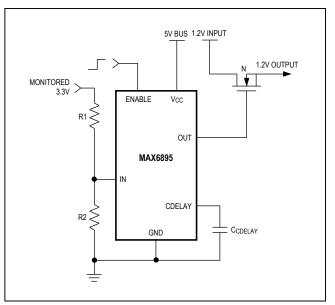

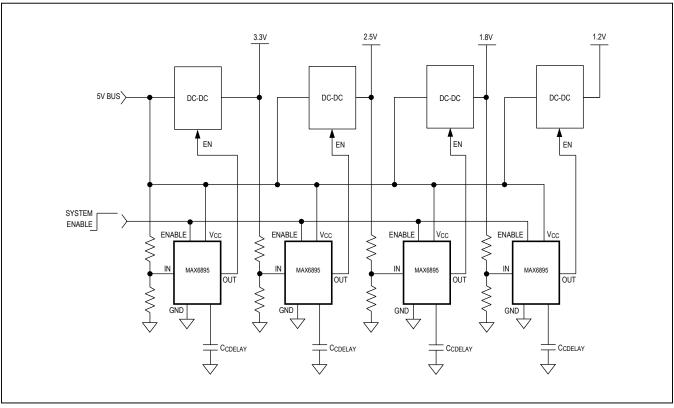

Figures 8, 9, 10 show typical applications for the MAX6895–MAX6899. Figure 8 shows the MAX6895

used with a p-channel MOSFET in an overvoltage protection circuit. Figure 9 shows the MAX6895 in a lowvoltage sequencing application using an n-channel MOSFET. Figure 10 shows the MAX6895 used in a multiple-output sequencing application.

#### Using an n-Channel Device for Sequencing

In higher power applications, using an n-channel device reduces the loss across the MOSFETs as it offers a lower drain-to-source on-resistance. However, an nchannel MOSFET requires a sufficient VGS voltage to fully enhance it for a low RDS\_ON. The application in Figure 9 shows the MAX6895 in a switch sequencing application using an n-channel MOSFET.

Similarly, if a higher voltage is present in the system, the open-drain version can be used in the same manner.

Figure 8. Overvoltage Protection

Figure 9. Low-Voltage Sequencing Using an n-Channel MOSFET

# Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

Figure 10. Multiple-Output Sequencing

#### **Ordering Information**

| PART            | PIN-PACKAGE  | TOP MARK |

|-----------------|--------------|----------|

| MAX6895AALT+    | 6 µDFN       | +AW      |

| MAX6895AAZT+    | 6 Thin SOT23 | +AADK    |

| MAX6895AAZT/V+T | 6 Thin SOT23 | +AATF    |

| MAX6895PALT+T   | 6 µDFN       | +AX      |

| MAX6895PAZT+    | 6 Thin SOT23 | +AADL    |

| MAX6896AALT+    | 6 µDFN       | +AY      |

| MAX6896AAZT+    | 6 Thin SOT23 | +AADO    |

| MAX6896AAZT/V+T | 6 Thin SOT23 | +AATA    |

| MAX6896PALT+T   | 6 µDFN       | +AZ      |

| MAX6896PAZT+    | 6 Thin SOT23 | +AADP    |

| MAX6897AALT+    | 6 µDFN       | +BA      |

| MAX6897AAZT+    | 6 Thin SOT23 | +AADQ    |

| MAX6897AAZT/V+  | 6 Thin SOT23 | +AADX    |

| MAX6897AAZT/V+T | 6 Thin SOT23 | +AADX    |

| MAX6897PALT+T   | 6 µDFN       | +BB      |

| MAX6897PAZT+    | 6 Thin SOT23 | +AADR    |

| MAX6898AALT+    | 6 µDFN       | +BD      |

| PART             | PIN-PACKAGE  | TOP MARK |

|------------------|--------------|----------|

| MAX6898AAZT+     | 6 Thin SOT23 | +AADS    |

| MAX6898AAZT/V+*  | 6 Thin SOT23 | —        |

| MAX6898AAZT/V+T* | 6 Thin SOT23 | —        |

| MAX6898PALT+T    | 6 µDFN       | +BC      |

| MAX6898PAZT+     | 6 Thin SOT23 | +AADT    |

| MAX6899AALT+     | 6 µDFN       | +LO      |

| MAX6899AAZT+     | 6 Thin SOT23 | +AADM    |

| MAX6899PALT+T    | 6 µDFN       | +LP      |

| MAX6899PAZT+     | 6 Thin SOT23 | +AADN    |

**Note:** All devices are specified over the -40°C to +125°C operating temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package. /V denotes an automotive qualified part; T = Tape and reel. \*Future product—Contact factory for availability.

# Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

#### **Selector Guide**

| PART          | ENABLE INPUT | OUTPUT                  | INPUT (IN) DELAY     | ENABLE DELAY         |

|---------------|--------------|-------------------------|----------------------|----------------------|

| MAX6895AALT+T | Active-High  | Active-High, Push-Pull  | Capacitor Adjustable | Capacitor Adjustable |

| MAX6895AAZT+T | Active-High  | Active-High, Push-Pull  | Capacitor Adjustable | Capacitor Adjustable |

| MAX6895PALT+T | Active-High  | Active-High, Push-Pull  | Capacitor Adjustable | 150ns Delay          |

| MAX6895PAZT+T | Active-High  | Active-High, Push-Pull  | Capacitor Adjustable | 150ns Delay          |

| MAX6896AALT+T | Active-Low   | Active-Low, Push-Pull   | Capacitor Adjustable | Capacitor Adjustable |

| MAX6896AAZT+T | Active-Low   | Active-Low, Push-Pull   | Capacitor Adjustable | Capacitor Adjustable |

| MAX6896PALT+T | Active-Low   | Active-Low, Push-Pull   | Capacitor Adjustable | 150ns Delay          |

| MAX6896PAZT+T | Active-Low   | Active-Low, Push-Pull   | Capacitor Adjustable | 150ns Delay          |

| MAX6897AALT+T | Active-High  | Active-High, Open-Drain | Capacitor Adjustable | Capacitor Adjustable |

| MAX6897AAZT+T | Active-High  | Active-High, Open-Drain | Capacitor Adjustable | Capacitor Adjustable |

| MAX6897PALT+T | Active-High  | Active-High, Open-Drain | Capacitor Adjustable | 150ns Delay          |

| MAX6897PAZT+T | Active-High  | Active-High, Open-Drain | Capacitor Adjustable | 150ns Delay          |

| MAX6898AALT+T | Active-Low   | Active-Low, Open-Drain  | Capacitor Adjustable | Capacitor Adjustable |

| MAX6898AAZT+T | Active-Low   | Active-Low, Open-Drain  | Capacitor Adjustable | Capacitor Adjustable |

| MAX6898PALT+T | Active-Low   | Active-Low, Open-Drain  | Capacitor Adjustable | 150ns Delay          |

| MAX6898PAZT+T | Active-Low   | Active-Low, Open-Drain  | Capacitor Adjustable | 150ns Delay          |

| MAX6899AALT+T | Active-Low   | Active-High, Push-Pull  | Capacitor Adjustable | Capacitor Adjustable |

| MAX6899AAZT+T | Active-Low   | Active-High, Push-Pull  | Capacitor Adjustable | Capacitor Adjustable |

| MAX6899PALT+T | Active-Low   | Active-High, Push-Pull  | Capacitor Adjustable | 150ns Delay          |

| MAX6899PAZT+T | Active-Low   | Active-High, Push-Pull  | Capacitor Adjustable | 150ns Delay          |

# **Typical Operating Circuit**

# Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

### **Pin Configurations (continued)**

### **Chip Information**

PROCESS: BICMOS

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE NO.    | LAND<br>PATTERN NO. |

|-----------------|-----------------|----------------|---------------------|

| 6 µDFN          | L611+1          | <u>21-0147</u> | <u>90-0080</u>      |

| 6 Thin SOT23    | Z6+1, Z6+1A     | <u>21-0114</u> | <u>90-0242</u>      |

# Ultra-Small, Adjustable Sequencing/ Supervisory Circuits

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                     | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------|------------------|

| 5                  | 10/07            | —                                                                                                                               | 1, 13, 18        |

| 6                  | 11/09            | Corrected Absolute Maximum Ratings and made style corrections to Electrical Characteristics and TOC8 and TOC9                   | 2–5              |

| 7                  | 7/10             | Revised Figures 3, 4, and 6                                                                                                     | 7–9              |

| 8                  | 7/11             | Added automotive packages for MAX6896A and MAX6896P; added top mark to MAX6896AAZT/V+1 in the <i>Ordering Information</i> table | 1                |

| 9                  | 12/13            | Added automotive packages for MAX6897 in the Ordering Information table                                                         | 13               |

| 10                 | 3/14             | Added automotive packages for MAX6898 in the Ordering Information table                                                         | 13               |

| 11                 | 12/17            | Added AEC statement and updated Ordering Information table                                                                      | 1, 12            |

| 12                 | 3/18             | Updated Ordering Information table                                                                                              | 12               |

| 13                 | 8/18             | Updated Ordering Information table                                                                                              | 12               |

| 14                 | 9/18             | Updated Features section                                                                                                        | 1                |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated and the Maxim Integrated logo are trademarks of Maxim Integrated Products, Inc. © 2018 Maxim Integrated Products, Inc. | 15