# Microprocessor Supervisory Reset Circuits with Edge-Triggered, One-Shot Manual Reset

## **Absolute Maximum Ratings**

| V <sub>CC</sub> to GND          | 0.3V to +6.0V                    |

|---------------------------------|----------------------------------|

| RESET to GND                    |                                  |

| Open-Drain                      | -0.3V to +6.0V                   |

| Push-Pull                       | 0.3V to (V <sub>CC</sub> + 0.3V) |

| MR to GND                       | 0.3V to (V <sub>CC</sub> + 0.3V) |

| Input/Output Current (all pins) | 20mA                             |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |

|-------------------------------------------------------|

| 4-Pin SC70 (derate 3.1mW/°C above +70°C)245mW         |

| 4-Pin SOT143 (derate 4mW/°C above +70vC)320mW         |

| Operating Temperature Range40°C to +125°C             |

| Storage Temperature Range65°C to +150°C               |

| Junction Temperature+150°C                            |

| Lead Temperature (soldering, 10s)+300°C               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Electrical Characteristics**

(V<sub>CC</sub> = +1.2V to +5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                                          | SYMBOL           | CONDITIONS                                                                  | MIN                   | TYP                   | MAX   | UNITS |  |

|--------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------|-----------------------|-----------------------|-------|-------|--|

| Operating Voltage Pange                                            | V <sub>CC</sub>  | $T_A = 0^{\circ}C$ to +125°C                                                | 1.0                   |                       | 5.5   | — V   |  |

| Operating Voltage Range                                            |                  | $T_A = -40^{\circ}C$ to $0^{\circ}C$                                        | 1.2                   |                       | 5.5   |       |  |

|                                                                    |                  | V <sub>CC</sub> = +5.5V, no load                                            |                       | 7                     | 13    | μΑ    |  |

| Summer Current                                                     |                  | V <sub>CC</sub> = +3.6V, no load                                            |                       | 6                     | 11    |       |  |

| Supply Current                                                     | Icc              | $V_{CC}$ = +2.5V, no load                                                   |                       | 4                     | 8     |       |  |

|                                                                    |                  | V <sub>CC</sub> = +1.8V, no load                                            |                       | 3                     | 7.5   |       |  |

|                                                                    |                  | T <sub>A</sub> = +25°C                                                      | -1.5%                 | V <sub>TH</sub>       | +1.5% |       |  |

| V <sub>CC</sub> Reset Threshold<br>(See the Reset Threshold Table) | V <sub>TH</sub>  | $T_A = -40^{\circ}C$ to $+85^{\circ}C$                                      | -2.5%                 |                       | +2.5% | V     |  |

| ()                                                                 |                  | T <sub>A</sub> = +85°C to +125°C                                            | -3%                   |                       | +3%   |       |  |

| V <sub>CC</sub> Reset Delay                                        | t <sub>RD</sub>  | $V_{CC}$ falling at 10mV/µs from $V_{TH}$ + 100mV to $V_{TH}$ - 100mV       |                       | 35                    |       | μs    |  |

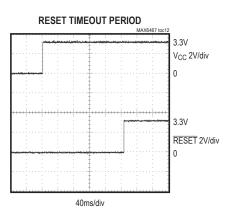

|                                                                    |                  | D3 option                                                                   | 150                   | 225                   | 300   | ms    |  |

| V <sub>CC</sub> Reset Timeout Period                               | t <sub>RP</sub>  | D7 option                                                                   | 1200                  | 1800                  | 2400  |       |  |

| MR Timeout Period                                                  | t <sub>MRP</sub> | D3 and D7 options                                                           | 150                   | 225                   | 300   | ms    |  |

| MR Rising Debounce Period (Note 2)                                 | t <sub>DEB</sub> | D3 and D7 options                                                           | 150                   | 225                   | 300   | ms    |  |

|                                                                    | VIL              |                                                                             | 0.3 x V <sub>CC</sub> |                       |       | V     |  |

|                                                                    | VIH              | V <sub>TH</sub> < +4V                                                       | 0.7 x V <sub>CC</sub> |                       |       |       |  |

| MR Input Voltage                                                   | VIL              |                                                                             |                       |                       | 0.8   | v     |  |

|                                                                    | VIH              | $-V_{TH} \ge +4V$                                                           |                       |                       |       |       |  |

| MR Minimum Input Pulse                                             |                  |                                                                             | 1                     |                       |       | μs    |  |

| MR Glitch Rejection                                                |                  |                                                                             |                       | 100                   |       | ns    |  |

| MR to RESET Delay                                                  |                  |                                                                             |                       | 200                   |       | ns    |  |

| MR Pullup Resistance                                               |                  | MR to V <sub>CC</sub>                                                       | 500                   | 1560                  | 3000  | Ω     |  |

| RESET Output High                                                  | Mari             | V <sub>CC</sub> ≥ +2.5V, I <sub>SOURCE</sub> = 500µA, RESET<br>not asserted | 0.8 x V <sub>CC</sub> |                       |       |       |  |

| (MAX6468 Only)                                                     | Voh              | V <sub>CC</sub> ≥ +4.5V, I <sub>SOURCE</sub> = 800µA, RESET<br>not asserted | 0.8 x V <sub>C</sub>  | ).8 x V <sub>CC</sub> |       | V     |  |

# Microprocessor Supervisory Reset Circuits with Edge-Triggered, One-Shot Manual Reset

#### **Electrical Characteristics**

(V<sub>CC</sub> = +1.2V to +5.5V,  $T_A$  = -40°C to +125°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.) (Note 1)

| PARAMETER                                      | SYMBOL           | CONDITIONS                                                            | MIN | TYP   | MAX | UNITS |

|------------------------------------------------|------------------|-----------------------------------------------------------------------|-----|-------|-----|-------|

|                                                |                  | V <sub>CC</sub> ≥ +1V, I <sub>SINK</sub> = 80µA, RESET asserted       |     |       | 0.3 |       |

| RESET Output Low                               | V <sub>OL</sub>  | V <sub>CC</sub> ≥ +2.5V, I <sub>SINK</sub> = 1.2mA, RESET<br>asserted |     | 0.3 V |     | V     |

|                                                |                  | V <sub>CC</sub> ≥ +4.5V, I <sub>SINK</sub> = 3.2mA, RESET<br>asserted |     |       | 0.3 |       |

| RESET Output Leakage Current<br>(MAX6467 Only) | I <sub>LKG</sub> | RESET not asserted                                                    |     |       | 1   | μA    |

**Note 1:** Specifications over temperature are guaranteed by design. Production testing at  $T_A = +25^{\circ}C$  only. **Note 2:** The MR input ignores falling edges that occur within the MR rising debounce period ( $t_{DEB}$ ) after MR first rises from low to high (after a valid MR reset assertion). This prevents invalid reset assertion due to switch bounce.

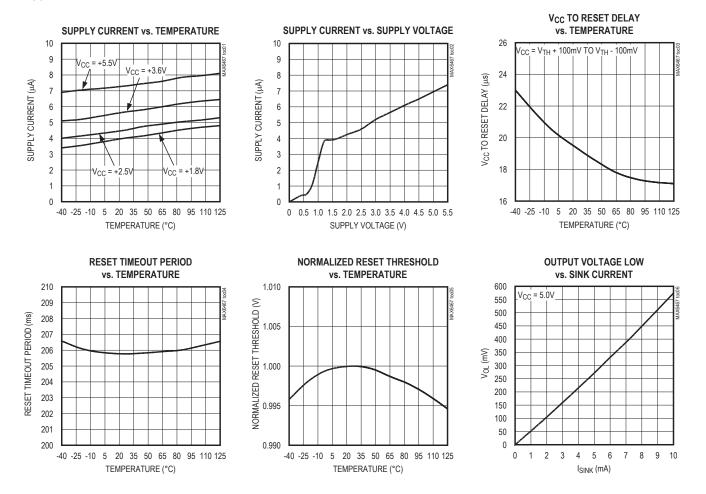

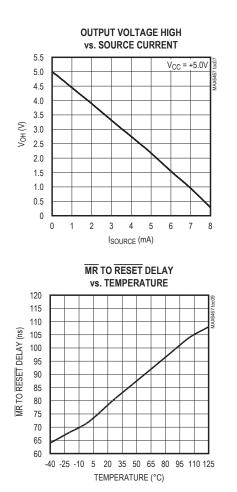

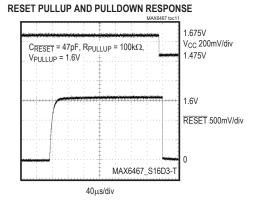

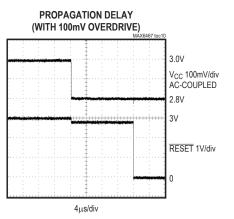

### **Typical Operating Characteristics**

(V<sub>CC</sub> = +5V, MAX6468US29D3 device, T<sub>A</sub> = +25°C, unless otherwise noted.)

# Microprocessor Supervisory Reset Circuits with Edge-Triggered, One-Shot Manual Reset

### **Typical Operating Characteristics**

(V<sub>CC</sub> = +5V, MAX6468US29D3 device,  $T_A$  = +25°C, unless otherwise noted.)

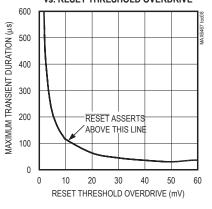

MAXIMUM TRANSIENT DURATION vs. RESET THRESHOLD OVERDRIVE

www.analog.com

# Microprocessor Supervisory Reset Circuits with Edge-Triggered, One-Shot Manual Reset

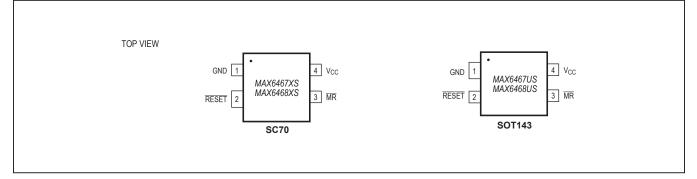

# **Pin Configurations**

#### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2   | RESET           | Reset Output. $\overrightarrow{\text{RESET}}$ is an active-low open-drain (MAX6467) or push-pull (MAX6468) output. $\overrightarrow{\text{RESET}}$ asserts low when V <sub>CC</sub> drops below the selected threshold and remains low for the V <sub>CC</sub> reset timeout period after V <sub>CC</sub> rises above the threshold. The RESET one-shot asserts low for a fixed MR reset timeout period on the falling edge of the manual reset input. The open-drain output requires an external pullup resistor. |

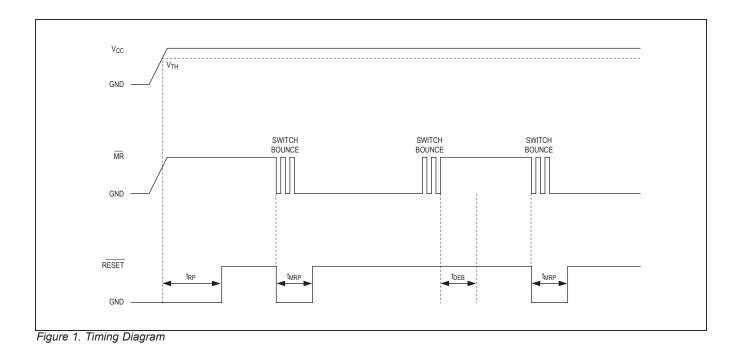

| 3   | MR              | Manual <u>Reset Input</u> . Drive <u>MR</u> low to initiate a reset output. <u>MR</u> controls an edge-triggered one-shot that asserts <u>RESET</u> low for a fixed <u>MR</u> timeout period when <u>MR</u> is driven low. Internal timing circuitry ignores switch close and open bounce to ensure proper one-shot reset timing.                                                                                                                                                                                  |

| 4   | V <sub>CC</sub> | Power-Supply Input. V <sub>CC</sub> provides power to the device and is also a monitored voltage. When V <sub>CC</sub> drops below the selected threshold, RESET asserts low and remains low for the reset timeout period after V <sub>CC</sub> rises above the threshold. For better noise immunity, bypass V <sub>CC</sub> to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                  |

# Microprocessor Supervisory Reset Circuits with Edge-Triggered, One-Shot Manual Reset

#### **Detailed Description**

#### **Reset Output**

The MAX6467 provides an active-low open-drain RESET output. The MAX6468 provides an active-low push-pull RESET output. RESET asserts low if V<sub>CC</sub> drops below the selected threshold or if a falling edge occurs on MR. RESET remains low for the V<sub>CC</sub> reset timeout period after V<sub>CC</sub> increases above the threshold voltage or is one-shot pulsed low for the MR timeout period after a falling edge on MR.

#### **Manual Reset Input**

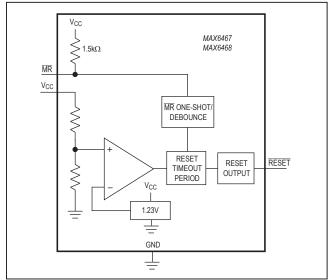

Many  $\mu$ P-based products require manual reset capability, allowing the operator, a test technician, or external logic circuitry to initiate a reset. A falling edge on  $\overline{MR}$  asserts

**RESET** low. **RESET** is one-shot pulsed low for the  $\overline{\text{MR}}$  timeout period after a falling edge on  $\overline{\text{MR}}$ . An internal 1.5k $\Omega$  pullup resistor to V<sub>CC</sub> allows MR to be left unconnected if not used. MR can be driven with TTL or CMOS-logic levels, or with open-drain/collector outputs. Connect a normally open momentary pushbutton switch from  $\overline{\text{MR}}$  to GND to realize a manual reset function. External debounce circuitry is not required, as the MAX6467/MAX6468 respond to the first falling edge on  $\overline{\text{MR}}$  and ignore subsequent falling edges within the reset timeout period and during the  $\overline{\text{MR}}$  debounce period (see Figure 1). After  $\overline{\text{MR}}$  goes high for 150ms (t<sub>DEB</sub>), the manual reset one-shot is ready to trigger a reset on the next  $\overline{\text{MR}}$  falling edge. Connect a 0.1µF capacitor from  $\overline{\text{MR}}$  to GND when using long cables to provide additional noise immunity.

# Microprocessor Supervisory Reset Circuits with Edge-Triggered, One-Shot Manual Reset

#### **Reset Timeout Delay\***

| RESET TIMEOUT SUFFIX | V <sub>CC</sub> RESET TIMEOUT PERIOD<br>(min/max) (ms) | MR TIMEOUT PERIOD<br>(min/max) (ms) | MR RISING DEBOUNCE PERIOD<br>(min/max) (ms) |

|----------------------|--------------------------------------------------------|-------------------------------------|---------------------------------------------|

| D3                   | 150/300                                                | 150/300                             | 150/300                                     |

| D7                   | 1200/2400                                              | 150/300                             | 150/300                                     |

\*Additional reset timeout options may be available. Contact factory for availability.

#### **Applications Information**

#### Falling V<sub>CC</sub> Transients

In addition to issuing a reset to the  $\mu$ P during power-up, power-down, and brownout conditions, the MAX6467/ MAX6468 are relatively immune to short-duration falling V<sub>CC</sub> transients (glitches). The Typical Operating Characteristics section shows the Maximum Transient Duration vs. V<sub>CC</sub> Overdrive for which the MAX6467/ MAX6468 do not generate a reset pulse. This graph was generated using a falling pulse applied to V<sub>CC</sub> starting above the actual reset threshold and ending below the threshold by the magnitude indicated (V<sub>CC</sub> Overdrive). The graph indicates the typical maximum pulse width a falling V<sub>CC</sub> transient can have without initiating a reset pulse. As the magnitude of the transient increases (goes farther below the reset threshold), the maximum allowable pulse width decreases. A  $0.1\mu$ F bypass capacitor from V<sub>CC</sub> to GND provides additional transient immunity.

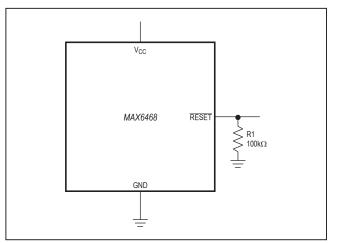

# Ensuring a Valid RESET Output Down to $V_{CC} = 0V$

The MAX6467/MAX6468 guarantee proper operation down to V<sub>CC</sub> = +1V. In applications that require valid reset levels down to V<sub>CC</sub> = 0V, a pulldown resistor to active-low outputs (MAX6468 only, Figure 3) ensures that RESET remains valid while the RESET output can no longer sink current. This scheme does not work with the open-drain outputs of the MAX6467. Ensure that the resistor value used does not overload the RESET output when V<sub>CC</sub> is above the reset threshold. For most applications, use 100k $\Omega$  to 1M $\Omega$ .

Figure 2. Functional Diagram

Figure 3.  $\overline{RESET}$  Valid to  $V_{CC} = 0V$

Chip Information TRANSISTOR COUNT: 748 PROCESS: BICMOS

# Microprocessor Supervisory Reset Circuits with Edge-Triggered, One-Shot Manual Reset

## **Standard Versions**

| PART          | TOP MARK |

|---------------|----------|

| MAX6467XS16D3 | AGL      |

| MAX6467XS22D3 | AGM      |

| MAX6467XS26D3 | AGN      |

| MAX6467XS29D3 | AGO      |

| MAX6467XS46D3 | AGP      |

| MAX6467US16D3 | KAFN     |

| MAX6467US22D3 | KAFO     |

| MAX6467US26D3 | KAFP     |

| MAX6467US29D3 | KAFQ     |

| MAX6467US46D3 | KAFR     |

| MAX6468XS16D3 | AGQ      |

| MAX6468XS22D3 | AGR      |

| MAX6468XS26D3 | AGS      |

| MAX6468XS29D3 | AGC      |

| MAX6468XS46D3 | AGB      |

| MAX6468US16D3 | KAFS     |

| MAX6468US22D3 | KAFT     |

| MAX6468US26D3 | KAFU     |

| MAX6468US29D3 | KAEW     |

| MAX6468US46D3 | KAFV     |

| SUFFIX | V <sub>TH</sub> (min) | V <sub>TH</sub> (typ) | V <sub>TH</sub> (max) |

|--------|-----------------------|-----------------------|-----------------------|

|        |                       |                       |                       |

| 46     | 4.509                 | 4.625                 | 4.741                 |

| 45     | 4.388                 | 4.500                 | 4.613                 |

| 44     | 4.266                 | 4.375                 | 4.484                 |

| 43     | 4.193                 | 4.300                 | 4.408                 |

| 42     | 4.095                 | 4.200                 | 4.305                 |

| 41     | 3.998                 | 4.100                 | 4.203                 |

| 40     | 3.900                 | 4.000                 | 4.100                 |

| 39     | 3.803                 | 3.900                 | 3.998                 |

| 38     | 3.705                 | 3.800                 | 3.895                 |

| 37     | 3.608                 | 3.700                 | 3.793                 |

| 36     | 3.510                 | 3.600                 | 3.690                 |

| 35     | 3.413                 | 3.500                 | 3.588                 |

| 34     | 3.315                 | 3.400                 | 3.485                 |

| 33     | 3.218                 | 3.300                 | 3.383                 |

| 32     | 3.120                 | 3.200                 | 3.280                 |

| 31     | 2.998                 | 3.075                 | 3.152                 |

| 30     | 2.925                 | 3.000                 | 3.075                 |

| 29     | 2.852                 | 2.925                 | 2.998                 |

| 28     | 2.730                 | 2.800                 | 2.870                 |

| 27     | 2.633                 | 2.700                 | 2.768                 |

| 26     | 2.559                 | 2.625                 | 2.691                 |

| 25     | 2.438                 | 2.500                 | 2.563                 |

| 24     | 2.340                 | 2.400                 | 2.460                 |

| 23     | 2.255                 | 2.313                 | 2.370                 |

| 22     | 2.133                 | 2.188                 | 2.242                 |

| 21     | 2.048                 | 2.100                 | 2.153                 |

| 20     | 1.950                 | 2.000                 | 2.050                 |

| 19     | 1.853                 | 1.900                 | 1.948                 |

| 18     | 1.755                 | 1.800                 | 1.845                 |

| 17     | 1.623                 | 1.665                 | 1.707                 |

| 16     | 1.536                 | 1.575                 | 1.614                 |

# Reset Threshold (-40°C to +85°C)

# Microprocessor Supervisory Reset Circuits with Edge-Triggered, One-Shot Manual Reset

#### **Ordering Information**

| PART              | TEMP RANGE      | PIN-<br>PACKAGE |

|-------------------|-----------------|-----------------|

| MAX6467XSDT       | -40°C to +125°C | 4 SC70-4        |

| MAX6467XSD_/V+T*  | -40°C to +125°C | 4 SC70-4        |

| MAX6467XS29D3/V+T | -40°C to +125°C | 4 SC70-4        |

| MAX6467XS32D3/V+T | -40°C to +125°C | 4 SC70-4        |

| MAX6467XS16D3/V+T | -40°C to +125°C | 4 SC70-4        |

| MAX6467USDT       | -40°C to +125°C | 4 SOT143-4      |

| MAX6468XSDT       | -40°C to +125°C | 4 SC70-4        |

| MAX6468USDT       | -40°C to +125°C | 4 SOT143-4      |

**Note:** Insert reset threshold suffix (see Reset Threshold table) after XS or US. Insert reset timeout delay (see Reset Timeout Delay table) after D to complete the part number. Sample stock is generally held on standard versions only (see Standard Versions table). Standard versions have an order increment requirement of 2500 pieces. Nonstandard versions have an order increment requirement of 10,000 pieces. Contact factory for availability. Devices are available in both leaded and leadfree packaging. Specify lead-free by replacing "T" with "+T" when ordering.

T = Tape and reel.

N denotes an automotive qualified part. +Denotes a lead(Pb)-free/RoHS-compliant package. \*Future product—contact factory for availability.

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN<br>NO. |

|-----------------|-----------------|----------------|------------------------|

| 4 SC70          | X4+1            | <u>21-0098</u> | <u>90-0187</u>         |

| 4 SOT143        | U4+1            | <u>21-0052</u> | <u>90-0183</u>         |

# Microprocessor Supervisory Reset Circuits with Edge-Triggered, One-Shot Manual Reset

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                  | PAGES<br>CHANGED |

|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2                  | 3/14             | Added /V OPNs                                                                                                                | 1                |

|                    | 4/14             | Removed automotive reference from Applications section                                                                       | 1                |

| 3                  | 6/14             | Reversed 4/14 change and added automotive reference back to <i>Applications</i> section                                      | 1                |

| 4                  | 10/14            | Fixed typo in Package Information section                                                                                    | 9                |

| 5                  | 10/15            | Fixed MR Pullup Resistance specification in <i>Electrical Characteristics</i> table                                          | 2                |

| 6                  | 3/18             | Updated Benefits and Features and Ordering Information table                                                                 | 1, 9             |

| 6.1                |                  | Reformatted Standard Versions table                                                                                          | 8                |

| 7                  | 3/20             | Updated Features, Absolute Maximum Ratings, Detailed Description,<br>Applications Information, and Package Information table | 1, 2, 6, 7, 9    |

| 8                  | 7/21             | Updated Ordering information table                                                                                           | 9                |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implicationor otherwise under any patent or patent rights of Analog Devices. Trademarks andregistered trademarks are the property of their respective owners.