# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to GND0.3V to +                       | -30V  |

|-------------------------------------------------------|-------|

| REG to GND0.3V to the lower of +22V or ( $V_{CC}$ + 0 | ).3V) |

| DRV to PGND0.3V to +                                  | -22V  |

| IN0.3V to +                                           | -22V  |

| FB/SET to GND0.3V to                                  | +6V   |

| P_OUT to DRV22V to +                                  |       |

| N_OUT to PGND0.3V to +                                | -22V  |

| OUT1, OUT2 to PGND0.3V to (V <sub>DRV</sub> + 0       | ).3V) |

| PGND to GND0.3V to +                                  | 0.3V  |

| P_OUT, N_OUT Continuous Source/Sink Current* 20       | 0mA   |

| OUT1, OUT2 Continuous Source/Sink Current*20          | 0mA   |

|                                                       |       |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) | )              |

|-------------------------------------------------------|----------------|

| 10-Pin TDFN, Single-Layer Board                       |                |

| (derate 18.5mW/°C above +70°C)                        | 1481.5mW       |

| 10-Pin TDFN, Multilayer Board                         |                |

| (derate 24.4mW/°C above +70°C)                        | 1951.2mW       |

| Operating Temperature Range                           | 40°C to +125°C |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

|                                                       |                |

<sup>\*</sup>Continuous output current is limited by the power dissipation of the package.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL CHARACTERISTICS (Note 1)

10 TDEN

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="http://www.maxim-ic.com/thermal-tutorial">http://www.maxim-ic.com/thermal-tutorial</a>.

#### **MAX15024 ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{DRV} = V_{REG} = 10V, FB/SET = GND, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = T_J = +25^{\circ}C$ ). (Note 2)

| PARAMETER                                          | SYMBOL                       | CONDITIONS                                                                       |                                          | MIN | TYP | MAX                                   | UNITS |

|----------------------------------------------------|------------------------------|----------------------------------------------------------------------------------|------------------------------------------|-----|-----|---------------------------------------|-------|

| SYSTEM SPECIFICATIONS                              | •                            |                                                                                  |                                          |     |     |                                       |       |

|                                                    |                              | V <sub>CC</sub> powered only, V <sub>REG</sub> = V <sub>DRV</sub> decoupled with | MAX15024B                                | 6.5 |     | 28.0                                  |       |

| Input Voltage Range                                | V <sub>CC</sub>              | minimum 1µF to GND                                                               | MAX15024A                                | 4.5 |     | 28.0                                  | V     |

|                                                    |                              | VCC = VREG = VDRV (MAX15                                                         | 5024B)                                   | 6.5 |     | 18.0                                  |       |

|                                                    |                              | V <sub>CC</sub> = V <sub>REG</sub> = V <sub>DRV</sub> (MAX15                     | 5024A)                                   | 4.5 |     | 18.0                                  |       |

| V <sub>DRV</sub> Turn-On Voltage                   | V <sub>DRV</sub> ON          | $V_{CC} = V_{REG} = 10V, IN+ = V_{REG}$                                          | CC, IN- = GND                            |     | 1.7 | 2.3                                   | V     |

| Quiescent Supply Current                           |                              | IN_ = V <sub>CC</sub> or GND                                                     |                                          |     | 700 | 1350                                  | μΑ    |

| Quiescent Supply Current<br>Under UVLO Condition   |                              | IN_ = V <sub>CC</sub> or GND                                                     |                                          |     | 250 |                                       | μΑ    |

| Switching Supply Current                           |                              | Switching at 250kHz, C <sub>L</sub> = 0                                          | Switching at 250kHz, C <sub>L</sub> = 0F |     | 1.5 | 3.0                                   | mA    |

| V <sub>CC</sub> Undervoltage Lockout               | UVLO_VCC                     | V <sub>CC</sub> rising                                                           |                                          | 3.0 | 3.4 | 3.8                                   | V     |

| V <sub>CC</sub> Undervoltage-Lockout<br>Hysteresis |                              |                                                                                  |                                          |     | 300 |                                       | mV    |

| V <sub>CC</sub> Undervoltage Lockout to            |                              | V <sub>CC</sub> rising                                                           |                                          |     | 100 |                                       |       |

| Output Delay                                       |                              | V <sub>CC</sub> falling                                                          |                                          |     | 2   |                                       | μs    |

| REG REGULATOR (V <sub>CC</sub> = 12V               | , REG = V <sub>DRV</sub> , ( | $C_L = 1\mu F$ , FB/SET = GND)                                                   |                                          |     |     |                                       |       |

| Output Voltage                                     | V <sub>REG</sub>             | 12V < V <sub>CC</sub> < 28V, 0 < I <sub>LOAD</sub>                               | ) < 10mA                                 | 9   | 10  | 11                                    | V     |

| Dropout Voltage                                    | Vp. 50                       | V <sub>CC</sub> = 6.5V, I <sub>LOAD</sub> = 100mA                                |                                          |     | 0.4 | 0.9                                   | V     |

| Dropout voltage                                    | V <sub>R_DO</sub>            | $V_{CC} = 4.5V$ , $I_{LOAD} = 50$ mA                                             | 0mA 0.2 0.5                              |     | 0.5 | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |       |

| Load Regulation                                    |                              | $V_{CC} = 12V$ , $I_{LOAD} = 0$ to 100                                           | )mA                                      |     | 1   |                                       | %     |

| Line Regulation                                    |                              | 12V < V <sub>CC</sub> < 28V                                                      |                                          |     | 10  |                                       | mV    |

## Single/Dual, 16ns, High Sink/Source **Current Gate Drivers**

#### MAX15024 ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = V_{DRV} = V_{REG} = 10V, FB/SET = GND, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = T_J = +25^{\circ}C$ ). (Note 2)

| PARAMETER                                                                    | SYMBOL                  | CONDITIONS                                                    |                         | MIN     | TYP      | MAX     | UNITS |

|------------------------------------------------------------------------------|-------------------------|---------------------------------------------------------------|-------------------------|---------|----------|---------|-------|

| DRIVER OUTPUT (SINK)                                                         |                         |                                                               |                         | ·       |          |         | •     |

|                                                                              |                         | V <sub>CC</sub> = V <sub>REG</sub> = V <sub>DRV</sub> = 10V,  | T <sub>A</sub> = +25°C  |         | 0.45     | 0.60    |       |

|                                                                              |                         | sinking 100mA                                                 | $T_A = +125^{\circ}C$   |         | 0.625    | 0.850   |       |

| Driver Output Resistance                                                     | R <sub>ON-N</sub>       | $V_{CC} = V_{REG} = V_{DRV} = 4.5V,$                          | T <sub>A</sub> = +25°C  |         | 0.50     | 0.65    | Ω     |

|                                                                              |                         | sinking 100mA<br>(MAX15024A)                                  | T <sub>A</sub> = +125°C |         | 0.7      | 0.9     |       |

| Peak Output Current                                                          | I <sub>PK-N</sub>       | V <sub>N_OUT</sub> = 10V                                      |                         |         | 8        |         | А     |

| Maximum Load Capacitance                                                     |                         | SOA condition: $C_L \times V_{DRV}^2 \le$ for $V_{DRV} = 10V$ | 20μJ,                   |         | 200      |         | nF    |

| Latchup Robustness                                                           |                         |                                                               |                         |         | 500      |         | mA    |

| DRIVER OUTPUT (SOURCE)                                                       |                         |                                                               |                         | I.      |          |         |       |

|                                                                              |                         | V <sub>CC</sub> = V <sub>REG</sub> = V <sub>DRV</sub> = 10V,  | $T_A = +25^{\circ}C$    |         | 0.875    | 1.500   |       |

|                                                                              |                         | sourcing 100mA                                                | $T_A = +125^{\circ}C$   |         | 1.2      | 2.0     |       |

| Driver Output Resistance                                                     | R <sub>ON-P</sub>       | $V_{CC} = V_{REG} = V_{DRV} = 4.5V,$                          | T <sub>A</sub> = +25°C  |         | 0.95     | 1.65    | Ω     |

|                                                                              |                         | sourcing 100mA<br>(MAX15024A)                                 | T <sub>A</sub> = +125°C |         | 1.25     | 2.20    | 20    |

| Peak Output Current                                                          | I <sub>PK-P</sub>       | VP_OUT = 0V                                                   |                         |         | 4        |         | А     |

| Latchup Robustness                                                           |                         |                                                               |                         |         | 500      |         | mA    |

| LOGIC INPUTS                                                                 |                         |                                                               |                         |         |          |         |       |

| Logic 1 Input Voltage                                                        | VIH                     | MAX15024A                                                     |                         | 2.0     |          |         | V     |

| Logic 1 input voltage                                                        | VIH                     | MAX15024B                                                     |                         | 4.25    |          |         | V     |

| Logic 0 Input Voltage                                                        | V <sub>IL</sub>         | MAX15024A                                                     |                         |         |          | 0.8     | V     |

| Logic o input voltage                                                        | V IL                    | MAX15024B                                                     |                         |         |          | 2       | v     |

| Logic Input Hysteresis                                                       |                         | MAX15024A                                                     |                         |         | 0.4      |         | V     |

| Logio input i iyotoroolo                                                     |                         | MAX15024B                                                     |                         |         | 1        |         | •     |

| Logic Input Current Leakage                                                  |                         | V <sub>IN</sub> = 18V or V <sub>GND</sub>                     |                         | -75     | 0.01     | +75     | μΑ    |

| Input Capacitance                                                            |                         |                                                               |                         |         | 10       |         | рF    |

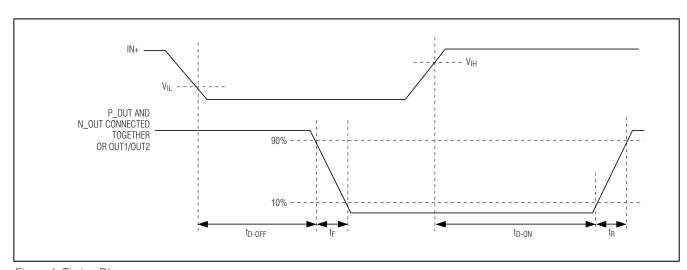

| SWITCHING CHARACTERISTIC (see Figure 1)                                      | S FOR V <sub>CC</sub> = | $V_{DRV} = V_{REG} = 10V, P_{OUT}$                            | AND N_OUT AR            | E CONNE | ECTED TO | DGETHER | 3     |

| (See Figure 1)                                                               |                         | C <sub>LOAD</sub> = 1nF                                       |                         |         | 3        |         |       |

| Rise Time                                                                    | t <sub>R</sub>          | $C_{LOAD} = 5nF$                                              |                         |         | 12       |         | ns    |

| The Time                                                                     | 41                      | $C_{LOAD} = 10nF$                                             |                         |         | 24       |         | 110   |

|                                                                              |                         | C <sub>LOAD</sub> = 1nF                                       |                         |         | 3        |         |       |

| Fall Time                                                                    | tF                      | CLOAD = 5nF                                                   |                         |         | 8        |         | ns    |

|                                                                              | ,                       | CLOAD = 10nF                                                  |                         |         | 16       |         |       |

| Turn-On Delay Time                                                           | t <sub>D-ON</sub>       | C <sub>LOAD</sub> = 1nF (Note 3)                              |                         | 8       | 16       | 32      | ns    |

| Turn-Off Delay Time                                                          | t <sub>D-OFF</sub>      | C <sub>LOAD</sub> = 1nF (Note 3)                              |                         | 8       | 16       | 32      | ns    |

| Mismatch Propagation Delays from Inverting and Noninverting Inputs to Output |                         | C <sub>LOAD</sub> = 1nF (Note 3)                              |                         | -9      | 1        | +9      | ns    |

# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

#### **MAX15024 ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = V_{DRV} = V_{REG} = 10V, FB/SET = GND, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = T_J = +25^{\circ}C$ ). (Note 2)

| PARAMETER                                                                                                             | SYMBOL             | CONDITIONS               | MIN | TYP  | MAX | UNITS |  |  |

|-----------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------|-----|------|-----|-------|--|--|

| SWITCHING CHARACTERISTICS FOR V <sub>CC</sub> = V <sub>DRV</sub> = V <sub>REG</sub> = 4.5V (see Figure 1) (MAX15024A) |                    |                          |     |      |     |       |  |  |

|                                                                                                                       |                    | C <sub>LOAD</sub> = 1nF  | 3   |      |     |       |  |  |

| Rise Time                                                                                                             | t <sub>R</sub>     | C <sub>LOAD</sub> = 5nF  |     | 11   |     | ns    |  |  |

|                                                                                                                       |                    | C <sub>LOAD</sub> = 10nF |     | 22   |     |       |  |  |

|                                                                                                                       |                    | C <sub>LOAD</sub> = 1nF  |     | 2.5  |     |       |  |  |

| Fall Time                                                                                                             | tϝ                 | C <sub>LOAD</sub> = 5nF  |     | 8    |     | ns    |  |  |

|                                                                                                                       |                    | C <sub>LOAD</sub> = 10nF | 16  |      |     |       |  |  |

| Turn-On Delay Time                                                                                                    | t <sub>D-ON</sub>  | C <sub>LOAD</sub> = 1nF  |     | 18   |     | ns    |  |  |

| Turn-Off Delay Time                                                                                                   | t <sub>D-OFF</sub> | C <sub>LOAD</sub> = 1nF  |     | 18   |     | ns    |  |  |

| Mismatch Propagation Delays from Inverting and Noninverting Inputs to Output                                          |                    | C <sub>LOAD</sub> = 1nF  |     | 2    |     | ns    |  |  |

| Minimum Input Pulse Width that Changes the Output                                                                     | tpw                |                          |     | 15   |     | ns    |  |  |

| THERMAL CHARACTERISTICS                                                                                               |                    |                          |     |      |     |       |  |  |

| Thermal-Shutdown Temperature                                                                                          |                    | Temperature rising       |     | +160 |     | °C    |  |  |

| Thermal-Shutdown Temperature Hysteresis                                                                               |                    |                          |     | 15   |     | °C    |  |  |

#### **MAX15025 ELECTRICAL CHARACTERISTICS**

$(V_{CC} = V_{DRV} = V_{REG} = 10V, FB/SET = GND, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = T_J = +25^{\circ}C$ ). (Note 2)

| PARAMETER                                        | SYMBOL              | CONDITIONS                                                                     |                                                                                                                                   | MIN | TYP | MAX  | UNITS |

|--------------------------------------------------|---------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|-------|

| SYSTEM SPECIFICATIONS                            |                     |                                                                                |                                                                                                                                   |     |     |      |       |

|                                                  |                     | V <sub>CC</sub> powered only,<br>V <sub>REG</sub> = V <sub>DRV</sub> decoupled | MAX15025B/D                                                                                                                       |     | 6.5 | 28   |       |

| Input Voltage Range                              | Vcc                 | with minimum 1µF                                                               | MAX15025A/C                                                                                                                       |     | 4.5 | 28   | V     |

|                                                  |                     | VCC = VREG = VDRV (MAX                                                         | 15025B/D)                                                                                                                         | 6.5 |     | 18.0 |       |

|                                                  |                     | V <sub>CC</sub> = V <sub>REG</sub> = V <sub>DRV</sub> (MAX15025A/C)            |                                                                                                                                   | 4.5 |     | 18.0 |       |

| V <sub>DRV</sub> Turn-On Voltage                 | V <sub>DRV</sub> ON |                                                                                | V <sub>CC</sub> = V <sub>REG</sub> = 10V, IN1 = V <sub>CC</sub> , IN2 = V <sub>CC</sub><br>(MAX15025A/B) or GND for (MAX15025C/D) |     | 1.7 | 2.3  | V     |

| Quiescent Supply Current                         |                     | IN_ = V <sub>CC</sub> or GND                                                   |                                                                                                                                   |     | 700 | 1350 | μΑ    |

| Quiescent Supply Current<br>Under UVLO Condition |                     | IN_ = V <sub>CC</sub> or GND                                                   |                                                                                                                                   |     | 250 |      | μA    |

| Switching Supply Current                         |                     | Switching at 250kHz, C <sub>L</sub> = 0F                                       |                                                                                                                                   |     | 1.5 | 3.0  | mA    |

| V <sub>CC</sub> Undervoltage Lockout             | UVLO_VCC            | V <sub>CC</sub> rising                                                         | <u> </u>                                                                                                                          | 3.0 | 3.4 | 3.8  | V     |

# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

#### MAX15025 ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = V_{DRV} = V_{REG} = 10V, FB/SET = GND, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = T_J = +25^{\circ}C$ ). (Note 2)

| PARAMETER                                          | SYMBOL                                | CONDITIONS                                                         |                         | MIN  | TYP   | MAX  | UNITS          |

|----------------------------------------------------|---------------------------------------|--------------------------------------------------------------------|-------------------------|------|-------|------|----------------|

| V <sub>CC</sub> Undervoltage-Lockout<br>Hysteresis |                                       |                                                                    |                         |      | 300   |      | mV             |

| V <sub>CC</sub> Undervoltage Lockout to            |                                       | V <sub>CC</sub> rising                                             |                         |      | 100   |      |                |

| Output Delay                                       |                                       | V <sub>CC</sub> falling                                            |                         |      | 2     |      | μs             |

| REG REGULATOR (V <sub>CC</sub> = 12V               | , V <sub>REG</sub> = V <sub>DRV</sub> | , $C_L = 1\mu F$ , FB/SET = GND)                                   |                         |      |       |      |                |

| Output Voltage                                     | VREG                                  | 12V < V <sub>CC</sub> < 28V, 0 < I <sub>LOAD</sub>                 | < 10mA                  | 9    | 10    | 11   | V              |

| Dropout Voltage                                    | Vp. p.c                               | $V_{CC} = 6.5V$ , $I_{LOAD} = 100$ mA                              |                         |      | 0.4   | 0.9  | V              |

| Dropout voltage                                    | V <sub>R_DO</sub>                     | $V_{CC} = 4.5V, I_{LOAD} = 50mA$                                   |                         |      | 0.2   | 0.5  | V              |

| Load Regulation                                    |                                       | $V_{CC} = 12V$ , $I_{LOAD} = 0$ to 100                             | mA                      |      | 1     |      | %              |

| Line Regulation                                    |                                       | 12V < V <sub>CC</sub> < 28V                                        |                         |      | 10    |      | mV             |

| FB/SET Reference Voltage                           |                                       | External resistive divider con FB/SET                              | nected at               | 1.10 | 1.23  | 1.35 | ٧              |

| FB/SET Threshold                                   |                                       | V <sub>FB</sub> rising                                             |                         |      | 220   |      | mV             |

| FB/SET Input Leakage Current                       |                                       | V <sub>FB</sub> = 4.5V                                             |                         | -125 |       | +125 | nA             |

| DRIVER OUTPUT SINK                                 | •                                     |                                                                    |                         |      |       |      |                |

|                                                    |                                       | VCC = VREG = VDRV = 10V,                                           | $T_A = +25^{\circ}C$    |      | 1.0   | 1.6  |                |

|                                                    |                                       | sinking 100mA                                                      | $T_A = +125^{\circ}C$   |      | 1.25  | 2.10 | 2.10<br>1.65 Ω |

| Driver Output Resistance                           | Ron-n                                 | $V_{CC} = V_{REG} = V_{DRV} = 4.5V,$                               | $T_A = +25^{\circ}C$    |      | 1.10  | 1.65 |                |

|                                                    |                                       | sinking 100mA<br>(MAX15025A/C)                                     | T <sub>A</sub> = +125°C |      | 1.5   | 2.2  |                |

| Peak Output Current                                | I <sub>PK-N</sub>                     | V <sub>OUT</sub> _ = 10V                                           |                         |      | 4     |      | Α              |

| Maximum Load Capacitance                           |                                       | SOA condition: $C_L \times V_{DRV}^2 \le$ for $V_{DRV} = 10V$      | 20μJ,                   |      | 100   |      | nF             |

| Latchup Robustness                                 |                                       |                                                                    |                         |      | 500   |      | mA             |

| DRIVER OUTPUT SOURCE                               | <u> </u>                              | 1                                                                  |                         |      |       |      |                |

|                                                    |                                       | VCC = V <sub>REG</sub> = V <sub>DRV</sub> = 10V,<br>sourcing 100mA | T <sub>A</sub> = +25°C  |      | 1.75  | 2.50 |                |

|                                                    |                                       |                                                                    | $T_A = +125^{\circ}C$   |      | 2.25  | 3.50 | Ω              |

| Driver Output Resistance                           | Ron-P                                 | $V_{CC} = V_{REG} = V_{DRV} = 4.5V,$                               | T <sub>A</sub> = +25°C  |      | 1.85  | 2.60 |                |

|                                                    |                                       | sourcing 100mA<br>(MAX15025A/C)                                    | T <sub>A</sub> = +125°C |      | 2.50  | 3.75 |                |

| Peak Output Current                                | I <sub>PK-P</sub>                     | V <sub>OUT</sub> _ = 0V                                            |                         |      | 2     |      | А              |

| Latchup Robustness                                 |                                       |                                                                    |                         |      | 500   |      | mA             |

| LOGIC INPUTS                                       |                                       |                                                                    |                         |      |       |      |                |

| Lania d Inn. AValtana                              |                                       | MAX15025A/C                                                        |                         | 2.0  |       |      |                |

| Logic 1 Input Voltage                              | VIH                                   | MAX15025B/D                                                        |                         | 4.25 |       |      | V              |

| Lagia O lagut Valtaga                              | \/                                    | MAX15025A/C                                                        |                         |      |       | 0.8  | V              |

| Logic 0 Input Voltage                              | VIL                                   | MAX15025B/D                                                        |                         |      |       | 2    | v              |

| Logio Input Hyotorosia                             |                                       | MAX15025A/C                                                        |                         |      | 0.4   |      | \/             |

| Logic Input Hysteresis                             |                                       | MAX15025B/D                                                        |                         |      | 1     |      | V              |

| Logic Input Current Leakage                        |                                       | V <sub>IN</sub> = 18V or V <sub>GND</sub>                          |                         | -75  | +0.01 | +75  | μΑ             |

| Input Capacitance                                  |                                       |                                                                    |                         |      | 10    |      | рF             |

# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

#### MAX15025 ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = V_{DRV} = V_{REG} = 10V, FB/SET = GND, T_A = T_J = -40^{\circ}C$  to  $+125^{\circ}C$ , unless otherwise noted. Typical values are at  $T_A = T_J = +25^{\circ}C$ ). (Note 2)

| PARAMETER                                         | SYMBOL                  | CONDITIONS                                                    | MIN         | TYP           | MAX | UNITS |

|---------------------------------------------------|-------------------------|---------------------------------------------------------------|-------------|---------------|-----|-------|

| SWITCHING CHARACTERISTIC                          | S FOR V <sub>CC</sub> = | V <sub>DRV</sub> = V <sub>REG</sub> = 10V (see Figure 1)      | •           |               |     |       |

|                                                   |                         | C <sub>LOAD</sub> = 1nF                                       |             | 6             |     |       |

| Rise Time                                         | t <sub>R</sub>          | C <sub>LOAD</sub> = 5nF                                       |             | 24            |     | ns    |

|                                                   |                         | $C_{LOAD} = 10nF$                                             |             | 48            |     |       |

|                                                   |                         | C <sub>LOAD</sub> = 1nF                                       |             | 5             |     |       |

| Fall Time                                         | tϝ                      | $C_{LOAD} = 5nF$                                              |             | 16            |     | ns    |

|                                                   |                         | C <sub>LOAD</sub> = 10nF                                      |             | 32            |     |       |

| Turn-On Delay Time                                | t <sub>D-ON</sub>       | C <sub>LOAD</sub> = 1nF (Note 3)                              | 8           | 16            | 32  | ns    |

| Turn-Off Delay Time                               | t <sub>D-OFF</sub>      | C <sub>LOAD</sub> = 1nF (Note 3)                              | 8           | 16            | 32  | ns    |

| Mismatch Propagation Delays<br>Between 2 Channels |                         | C <sub>LOAD</sub> = 1nF (Note 3)                              | -9          | 1             | +9  | ns    |

| SWITCHING CHARACTERISTIC                          | S FOR V <sub>CC</sub> = | V <sub>DRV</sub> = V <sub>REG</sub> = 4.5V (see Figure 1) (MA | AX15025A/C) |               |     | •     |

|                                                   |                         | C <sub>LOAD</sub> = 1nF                                       |             | 5<br>20<br>42 |     | ns    |

| Rise Time                                         | t <sub>R</sub>          | C <sub>LOAD</sub> = 5nF                                       |             |               |     |       |

|                                                   |                         | $C_{LOAD} = 10nF$                                             |             |               |     |       |

|                                                   |                         | C <sub>LOAD</sub> = 1nF                                       |             | 4<br>15<br>30 |     | ns    |

| Fall Time                                         | tϝ                      | $C_{LOAD} = 5nF$                                              |             |               |     |       |

|                                                   |                         | $C_{LOAD} = 10nF$                                             |             |               |     |       |

| Turn-On Delay Time                                | t <sub>D-ON</sub>       | C <sub>LOAD</sub> = 1nF                                       |             | 18            |     | ns    |

| Turn-Off Delay Time                               | t <sub>D-OFF</sub>      | C <sub>LOAD</sub> = 1nF                                       |             | 18            |     | ns    |

| Mismatch Propagation Delays<br>Between 2 Channels |                         | C <sub>LOAD</sub> = 1nF                                       |             | 2             |     | ns    |

| Minimum Input Pulse Width that Changes the Output | t <sub>PW</sub>         |                                                               |             | 15            |     | ns    |

| THERMAL CHARACTERISTICS                           |                         | •                                                             |             |               |     | •     |

| Thermal-Shutdown Temperature                      |                         | Temperature rising                                            |             | +160          |     | °C    |

| Thermal-Shutdown Temperature Hysteresis           |                         |                                                               |             | 15            |     | °C    |

Note 2: All devices are 100% production tested at  $T_A = +25$ °C. Limits over temperature are guaranteed by design.

Note 3: Design guaranteed by bench characterization. Limits are not production tested.

# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

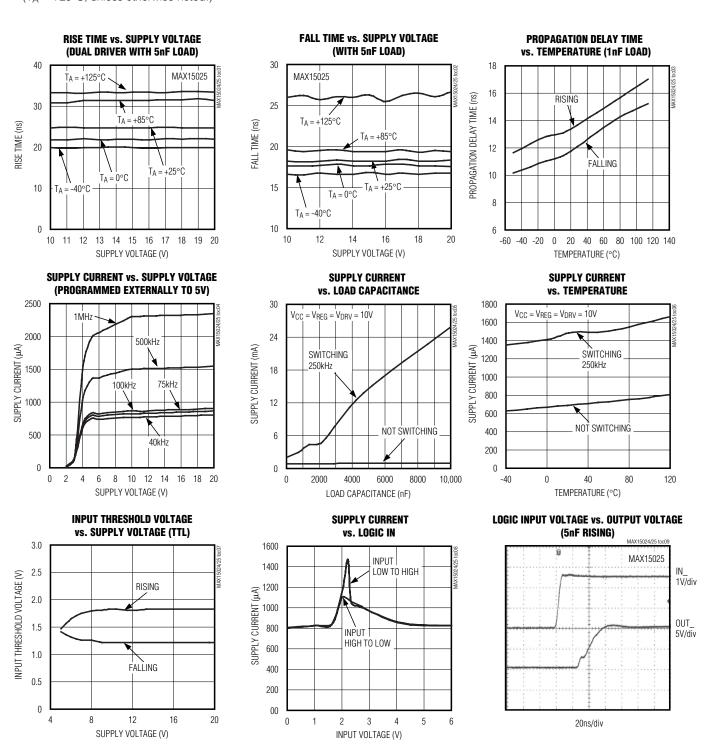

Typical Operating Characteristics

$(T_A = +25$ °C, unless otherwise noted.)

# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

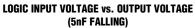

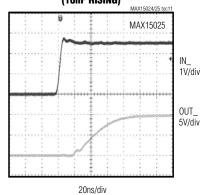

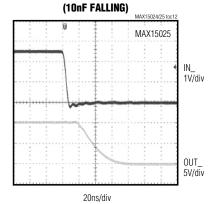

Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, unless otherwise noted.)$

# LOGIC INPUT VOLTAGE vs. OUTPUT VOLTAGE (10nF RISING)

### LOGIC INPUT VOLTAGE vs. OUTPUT VOLTAGE

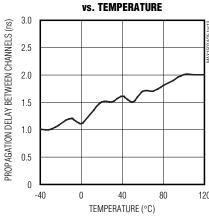

### PROPAGATION DELAY MISMATCH

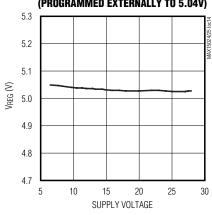

## LINE REGULATION OF V<sub>REG</sub> (PROGRAMMED EXTERNALLY TO 5.04V)

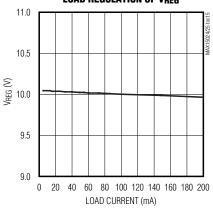

#### LOAD REGULATION OF VREG

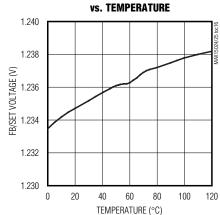

### FB/SET VOLTAGE

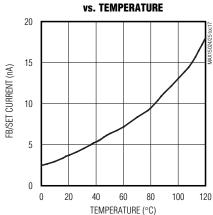

### FB/SET CURRENT

# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

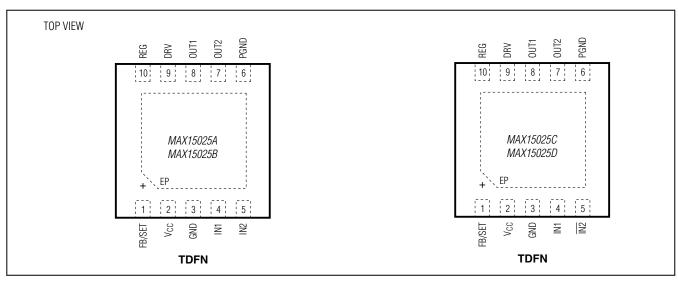

#### **Pin Description**

|          | PIN                    |                        |        |                                                                                                                                                                                                                                                                                                                                                             |  |  |

|----------|------------------------|------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MAX15024 | MAX15025A<br>MAX15025B | MAX15025C<br>MAX15025D | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 1        | 1                      | 1                      | FB/SET | LDO Regulator Output Set. Feedback for V <sub>REG</sub> adjustment (V <sub>FB</sub> > 200mV). Connect FB/SET to GND for a fixed 10V output REG. Connect FB/SET to a resistor ladder to set V <sub>REG</sub> .                                                                                                                                               |  |  |

| 2        | 2                      | 2                      | Vcc    | Power-Supply Input. Bypass to GND with a low-ESR ceramic capacitor of 1µF. Input of the internal housekeeping regulator and of the main REG regulator.                                                                                                                                                                                                      |  |  |

| 3        | 3                      | 3                      | GND    | Signal Ground                                                                                                                                                                                                                                                                                                                                               |  |  |

| 4        | _                      | _                      | IN+    | Driver Noninverting Logic Input. Connect to V <sub>CC</sub> when not used.                                                                                                                                                                                                                                                                                  |  |  |

| _        | 4                      | 4                      | IN1    | Driver 1 Noninverting Logic Input                                                                                                                                                                                                                                                                                                                           |  |  |

| 5        | _                      | _                      | IN-    | Driver Inverting Logic Input. Connect to GND when not used.                                                                                                                                                                                                                                                                                                 |  |  |

| _        | 5                      | _                      | IN2    | Driver 2 Noninverting Logic Input                                                                                                                                                                                                                                                                                                                           |  |  |

| _        | _                      | 5                      | ĪN2    | Driver 2 Inverting Logic Input                                                                                                                                                                                                                                                                                                                              |  |  |

| 6        | 6                      | 6                      | PGND   | Power Ground. Sink current return. Source of the internal pulldown n-channel transistor.                                                                                                                                                                                                                                                                    |  |  |

| 7        | _                      |                        | N_OUT  | Sink Output. Open-drain n-channel output. N_OUT sinks current for power MOSFET turn-off.                                                                                                                                                                                                                                                                    |  |  |

| _        | 7                      | 7                      | OUT2   | Driver 2 Output                                                                                                                                                                                                                                                                                                                                             |  |  |

| 8        | _                      | _                      | P_OUT  | Source Output. Pullup p-channel output (open drain). Sources current for power MOSFET turn-on.                                                                                                                                                                                                                                                              |  |  |

| _        | 8                      | 8                      | OUT1   | Driver 1 Output                                                                                                                                                                                                                                                                                                                                             |  |  |

| 9        | 9                      | 9                      | DRV    | Output Driver Supply Voltage. Decouple DRV with a low ESR > $0.1\mu F$ ceramic capacitor to PGND placed in close proximity to the device. DRV can be powered independently from REG. Connect DRV, REG, and VCC together when there is no need for special DRV supply sequencing and the power-MOSFET gate voltage does not need to be regulated or limited. |  |  |

| 10       | 10                     | 10                     | REG    | Voltage Regulator Output. Connect to DRV for driving the power MOSFET with regulated VGS amplitude. Bypass with a low-ESR 1µF (minimum) ceramic capacitor to GND placed in close proximity to the device to ensure regulator stability.                                                                                                                     |  |  |

| _        | _                      | _                      | EP     | Exposed Pad. Internally connected to GND. Connect to GND plane or thermal pad and use multiple vias to a solid copper area on the bottom of the PCB.                                                                                                                                                                                                        |  |  |

# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

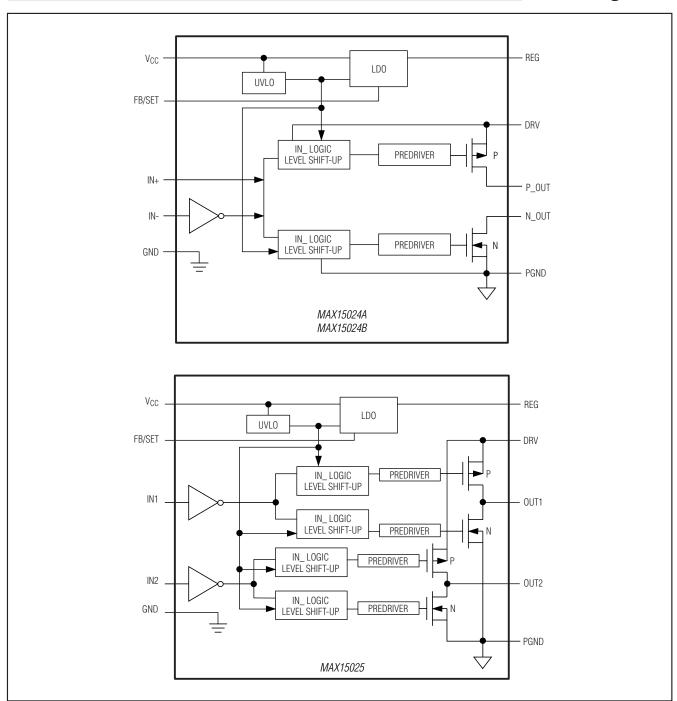

#### **Detailed Description**

The MAX15024 single gate driver's internal source and sink transistor outputs are brought out of the IC to independent outputs allowing control of the external MOSFET's rise and fall time. The MAX15024 single gate driver is capable of sinking an 8A peak current and sourcing a 4A peak current. The MAX15025 dual gate drivers are capable of sinking a 4A peak current and sourcing a 2A peak current.

An integrated adjustable low-dropout linear voltage regulator (LDO) provides gate drive amplitude control and optimization. The single gate-driver propagation delay time is minimized and matched between the inverting and noninverting inputs. The dual gate-driver propagation delay is matched between channels.

The MAX15024 has a dual input (IN+ and IN-), allows the use of an inverting or noninverting input, and is offered in TTL or CMOS-logic standards. The MAX15025 is offered with configurations of inverting and noninverting inputs with TTL or CMOS standards (see the *Selector Guide*).

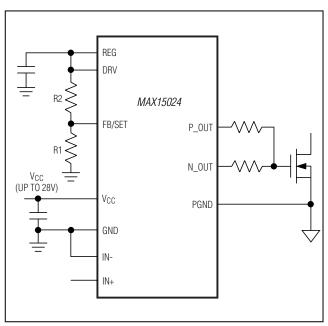

#### **LDO Voltage Regulator Feedback Control**

The MAX15024/MAX15025 include an internal LDO designed to deliver a stable reference voltage for use as a supply voltage for the internal MOSFET gate drivers. Connect the LDO feedback FB/SET to GND to set VREG to a stable 10V. Connect FB/SET to a resistor-divider between VREG and GND to set VREG:

$V_{REG} = V_{FB/SET} \times (1 + R2 / R1)$  (see Figure 2)

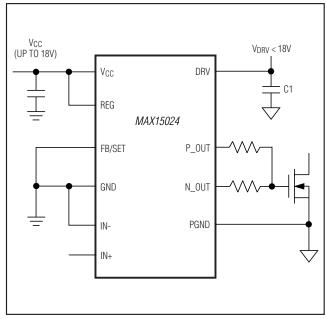

#### **Vcc Undervoltage Lockout**

When V<sub>CC</sub> is below the UVLO threshold, the internal n-channel transistor is ON and the internal p-channel transistor is OFF, holding the output at GND independent of the state of the inputs so that the external MOSFETs remain OFF in the UVLO condition. The UVLO threshold is 3.5V (typ) with 200mV (typ) hysteresis to avoid chattering.

When the device is operated at very low temperatures and below the UVLO threshold, the driver output could go high impedance. In this case, it is recommended adding a  $10k\Omega$  resistor to PGND to discharge the gate of the external MOSFET (see Figures 4 and 5).

#### **Input Control**

The MAX15024 features inverting and noninverting input terminals. These inputs provide for flexibility of design and use. Connect IN+ to VCC when using IN- as an inverting input. Connect IN- to GND when using IN+ as a noninverting input.

#### **Shoot-Through Protection**

The MAX15024/MAX15025 provide protection that avoids any cross-conduction between the internal p-channel and n-channel devices. It also eliminates shoot-through, thus reducing the quiescent supply current.

#### **Exposed Pad (EP)**

The MAX15024/MAX15025 include an exposed pad allowing greater heat dissipation from the internal die to the outside environment. Solder the exposed pad carefully to GND or thermal pad to enhance the thermal performance.

#### Applications Information

#### Supply Bypassing, Device Grounding, and Placement

Ample supply bypassing and device grounding are extremely important because when large external capacitive loads are driven, the peak current at the VDRV pin can approach 4A, while at the PGND pin, the peak current can approach 8A. VDRV drops and ground shifts are forms of negative feedback for inverters and, if excessive, can cause multiple switching when the inverting input is used and the input slew rate is low. The device driving the input should be referenced to the MAX15024/MAX15025 GND. Ground shifts due to insufficient device grounding can disturb other circuits sharing the same AC ground return path. Any series inductance in the VDRV, OUT, and/or PGND paths can cause oscillations due to the very high di/dt that results when the MAX15024/MAX15025 are switched with any capacitive load. A 0.1µF or larger value ceramic capacitor is recommended for bypassing VDRV to GND and should be placed as close to the pins as possible. When driving very large loads (> 10nF) at minimum rise time, 10µF or more of parallel storage capacitance is recommended. A ground plane is highly recommended to minimize ground return resistance and series inductance. Care should be taken to place the MAX15024/MAX15025 as close as possible to the external MOSFET being driven to further minimize board inductance and AC path resistance.

## Single/Dual, 16ns, High Sink/Source Current Gate Drivers

#### **Power Dissipation**

Power dissipation of the MAX15024/MAX15025 consists of three components: the quiescent current, capacitive charge and discharge of internal nodes, and the output current (either capacitive or resistive load). The sum of these components must be kept below the maximum power-dissipation limit. The quiescent current is 700µA typ. The current required to charge and discharge the internal nodes is frequency dependent (see the *Typical Operating Characteristics*). The MAX15024/MAX15025 power dissipation when driving a ground-referenced resistive load is:

$$P = D \times RON(MAX) \times ILOAD^2$$

where D is the fraction of the period the MAX15024/ MAX15025s' output pulls high,  $R_{ON(MAX)}$  is the maximum on-resistance of the device with the output high (p-channel), and  $I_{LOAD}$  is the output load current of the MAX15024/MAX15025. For capacitive loads, the power dissipation for each driver is:

$$P = C_{LOAD} \times V_{DRV}^2 \times FREQ$$

where  $C_{LOAD}$  is the capacitive load,  $V_{DRV}$  is the driver supply voltage, and FREQ is the switching frequency.

#### **Layout Information**

The MAX15024/MAX15025 MOSFET drivers source and sink large currents to create very fast rise and fall edges at the gate of the switching MOSFET. The high di/dt can cause unacceptable ringing if the trace lengths and impedances are not well controlled. The following

printed-circuit board (PCB) layout guidelines are recommended when designing with the MAX15024/MAX15025:

- Place one or more 1μF decoupling ceramic capacitor(s) from V<sub>DRV</sub> to PGND as close to the device as possible. At least one storage capacitor of 10μF (min) should be located on the PCB with a low resistance path to the V<sub>CC</sub> pin of the MAX15024/MAX15025.

- There are two AC current loops formed between the device and the gate of the MOSFET being driven. The MOSFET looks like a large capacitance from gate to source when the gate is being pulled low. The active current loop is from MOSFET gate to OUT of the MAX15024/MAX15025 to PGND of the MAX15024/MAX15025, and to the source of the MOSFET. When the gate of the MOSFET is being pulled high, the active current loop is from the VDD terminal of the VDRV terminal of decoupling capacitor, to the VDRy of the MAX15024/MAX15025, to the OUT\_ of the MAX15024/MAX15025, to the MOSFET gate, to the MOSFET source, and to the negative terminal of the decoupling capacitor. Both charging current loop and discharging current loop are important. It is important to minimize the physical distance and the impedance in these AC current paths.

- Keep the device as close as possible to the MOSFET.

- In the multilayer PCB, the inner layers should consist of a GND plane containing the discharging and charging current loops.

Figure 1. Timing Diagram

# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

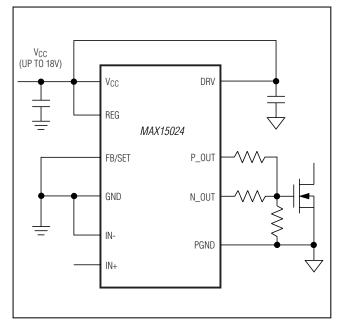

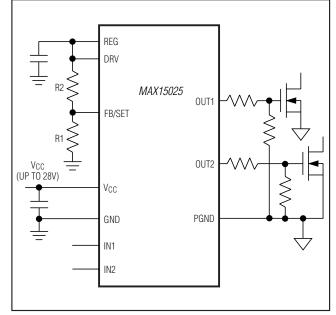

#### **Typical Operating Circuits**

Figure 2. Use R1, R2 to program  $V_{REG} < 18V$ , OR. Connect FB/SET to GND for  $V_{REG} = 10V$  (Connect EP to GND)

Figure 3. Operation Using a Different Supply Rail for DRV (Connect EP to GND)

Figure 4. Operation Using a  $V_{CC}$  = DRV = REG (Connect EP to GND)

Figure 5. Use R1, R2 to program  $V_{REG} < 18V$ , OR. Connect FB/SET to GND for  $V_{REG} = 10V$  (Connect EP to GND)

# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

#### **Block Diagrams**

## Single/Dual, 16ns, High Sink/Source Current Gate Drivers

#### **Selector Guide**

| PART            | NO. OF<br>CHANNELS | PEAK CURRENTS<br>(SINK/SOURCE) | INPUTS                             | LOGIC<br>LEVELS | TOP<br>MARK |

|-----------------|--------------------|--------------------------------|------------------------------------|-----------------|-------------|

| MAX15024AATB+   | 1                  | 8A/4A                          | Complementary                      | TTL             | ATX         |

| MAX15024AATB/V+ | 1                  | 8A/4A                          | Complementary                      | TTL             | AWT         |

| MAX15024BATB+   | 1                  | 8A/4A                          | Complementary                      | CMOS            | ATY         |

| MAX15025AATB+   | 2                  | 4A/2A                          | Noninverting                       | TTL             | ATZ         |

| MAX15025AATB/V+ | 2                  | 4A/2A                          | Noninverting                       | TTL             | AYE         |

| MAX15025BATB+   | 2                  | 4A/2A                          | Noninverting                       | CMOS            | AUA         |

| MAX15025CATB+   | 2                  | 4A/2A                          | Noninverting (1)/<br>Inverting (2) | TTL             | AUB         |

| MAX15025DATB+   | 2                  | 4A/2A                          | Noninverting (1)/<br>Inverting (2) | CMOS            | AUC         |

Note: All devices operate in a -40°C to +125°C temperature range and come in a 10-pin TDFN package.

### Pin Configurations (continued)

## Single/Dual, 16ns, High Sink/Source Current Gate Drivers

**Chip Information**

PROCESS: BiCMOS

#### **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE | LAND        |

|---------|---------|---------|-------------|

| TYPE    | CODE    | NO.     | PATTERN NO. |

| 10 TDFN | T1033+1 | 21-0137 | 90-0003     |

# Single/Dual, 16ns, High Sink/Source Current Gate Drivers

#### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                 | PAGES<br>CHANGED  |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------|-------------------|

| 0                  | 10/07            | Initial release                                                                                             | _                 |

| 1                  | 3/08             | Released MAX15024A/MAX15025B/C/D versions                                                                   | 1–6, 9, 13        |

| 2                  | 4/10             | Removed future product (MAX15024C/D, MAX15025E-H); minimum and maximum specifications added to the EC table | 1–6, 9, 10, 12–15 |

| 3                  | 4/11             | Added automotive part numbers to <i>Ordering Information</i> and <i>Selector Guide</i>                      | 1, 14             |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Maxim Integrated 160 Rio Robles, San Jose, CA 95134 USA 1-408-601-1000

16

© 2011 Maxim Integrated