## **ABSOLUTE MAXIMUM RATINGS**

| 12V <sub>GATE</sub>                               | –0.3V to 25V   |

|---------------------------------------------------|----------------|

| 12V <sub>OUT</sub> - 12V <sub>GATE</sub> (Note 3) | 4.5V to 0.3V   |

| AUXOUT                                            | –0.3V to 10V   |

| Operating Temperature Range                       |                |

| LTC4223-1C/ LTC4223-2C                            | 0°C to 70°C    |

| LTC4223-1I/ LTC4223-2I                            | –40°C to 85°C  |

| Storage Temperature Range                         |                |

| GN Package                                        | –65°C to 150°C |

| DHD Package                                       | –65°C to 125°C |

| Lead Temperature (Soldering, 10sec)               |                |

| GN Package                                        | 300°C          |

| •                                                 |                |

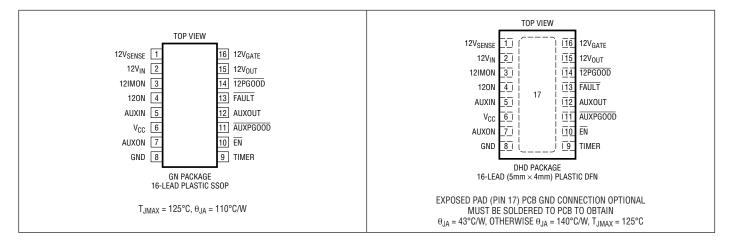

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|---------------|---------------------------------|-------------------|

| LTC4223CDHD-1#PBF | LTC4223CDHD-1#TRPBF | 42231         | 16-Lead (5mm × 4mm) Plastic DFN | 0°C to 70°C       |

| LTC4223CDHD-2#PBF | LTC4223CDHD-2#TRPBF | 42232         | 16-Lead (5mm × 4mm) Plastic DFN | 0°C to 70°C       |

| LTC4223IDHD-1#PBF | LTC4223IDHD-1#TRPBF | 42231         | 16-Lead (5mm × 4mm) Plastic DFN | -40°C to 85°C     |

| LTC4223IDHD-2#PBF | LTC4223IDHD-2#TRPBF | 42232         | 16-Lead (5mm × 4mm) Plastic DFN | -40°C to 85°C     |

| LTC4223CGN-1#PBF  | LTC4223CGN-1#TRPBF  | 42231         | 16-Lead Plastic SSOP            | 0°C to 70°C       |

| LTC4223CGN-2#PBF  | LTC4223CGN-2#TRPBF  | 42232         | 16-Lead Plastic SSOP            | 0°C to 70°C       |

| LTC4223IGN-1#PBF  | LTC4223IGN-1#TRPBF  | 422311        | 16-Lead Plastic SSOP            | -40°C to 85°C     |

| LTC4223IGN-2#PBF  | LTC4223IGN-2#TRPBF  | 422312        | 16-Lead Plastic SSOP            | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. Consult LTC Marketing for information on non-standard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

#

| SYMBOL                   | PARAMETER                                                                            | CONDITIONS                                                                       |   | MIN               | TYP                | MAX               | UNITS          |

|--------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|---|-------------------|--------------------|-------------------|----------------|

| Supplies                 |                                                                                      |                                                                                  |   |                   |                    |                   |                |

| V <sub>DD</sub>          | Input Supply Range                                                                   | V <sub>CC</sub><br>AUXIN<br>12V <sub>IN</sub>                                    | • | 2.7<br>2.7<br>10  |                    | 6<br>6<br>14      | V<br>V         |

| I <sub>DD</sub>          | Input Supply Current                                                                 | V <sub>CC</sub><br>AUXIN<br>12V <sub>IN</sub>                                    | • |                   | 0.8<br>0.4<br>0.6  | 2<br>1<br>1       | mA<br>mA<br>mA |

| V <sub>DD(UVLO)</sub>    | Input Supply Undervoltage Lockout                                                    | V <sub>CC</sub> Rising<br>V <sub>AUXIN</sub> Rising<br>V <sub>12VIN</sub> Rising | • | 2.3<br>2.4<br>9.4 | 2.45<br>2.5<br>9.7 | 2.6<br>2.6<br>10  | V<br>V         |

| $\Delta V_{DD(UVLO,}$    | Input Supply Undervoltage Lockout<br>Hysteresis                                      | V <sub>CC</sub><br>AUXIN<br>12V <sub>IN</sub>                                    | • | 40<br>70<br>70    | 110<br>110<br>110  | 180<br>150<br>150 | mV<br>mV<br>mV |

| <b>Current Limit</b>     |                                                                                      |                                                                                  |   |                   |                    |                   |                |

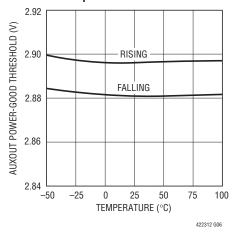

| $\Delta V_{SENSE(CB)}$   | Circuit Breaker Trip Sense Voltage,<br>(V <sub>12VIN</sub> – V <sub>12VSENSE</sub> ) |                                                                                  | • | 47.5              | 50                 | 52.5              | mV             |

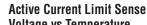

| $\Delta V_{SENSE(ACL)}$  | Active Current Limit Sense Voltage, (V <sub>12VIN</sub> – V <sub>12VSENSE</sub> )    |                                                                                  | • | 54                | 60                 | 66                | mV             |

| I <sub>AUX(ACL)</sub>    | AUXOUT Active Current Limit                                                          | V <sub>AUXOUT</sub> = 0V                                                         | • | 165               | 240                | 330               | mA             |

| Integrated Sw            | itch                                                                                 |                                                                                  |   |                   |                    |                   |                |

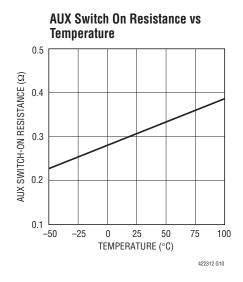

| R <sub>DS(ON)</sub>      | Switch Resistance<br>(V <sub>AUXIN</sub> – V <sub>AUXOUT</sub> )/I <sub>AUXOUT</sub> | I <sub>AUXOUT</sub> = 150mA (Note 4)                                             | • |                   | 0.3                | 0.5               | Ω              |

| Gate Drive               |                                                                                      |                                                                                  |   |                   |                    |                   |                |

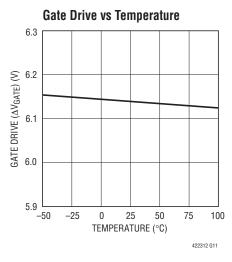

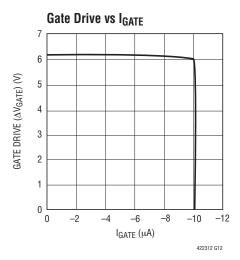

| $\Delta V_{GATE}$        | External N-Channel Gate Drive (V <sub>12VGATE</sub> - V <sub>12VOUT</sub> )          | (Note 3)                                                                         | • | 4.5               | 6.2                | 7.9               | V              |

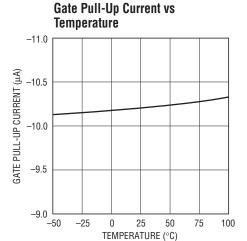

| I <sub>GATE(UP)</sub>    | External N-Channel Gate Pull-Up Current                                              | Gate Drive On, V <sub>12VGATE</sub> = 0V                                         | • | -7                | -10                | -14               | μΑ             |

| I <sub>GATE(DN)</sub>    | External N-Channel Gate Pull-Down Current                                            | Gate Drive Off<br>V <sub>12VGATE</sub> = 17V, V <sub>12VOUT</sub> = 12V          | • | 0.5               | 1                  | 2                 | mA             |

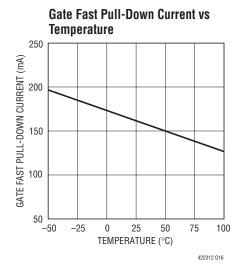

| I <sub>GATE(FPD)</sub>   | External N-Channel Gate Fast Pull-Down<br>Current                                    | Fast Turn Off<br>V <sub>12VGATE</sub> = 17V, V <sub>12VOUT</sub> = 12V           | • | 90                | 160                | 250               | mA             |

| <b>Current Sense</b>     |                                                                                      |                                                                                  |   |                   |                    |                   |                |

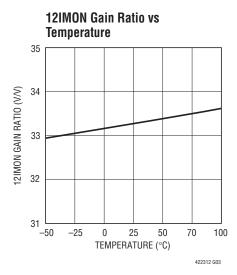

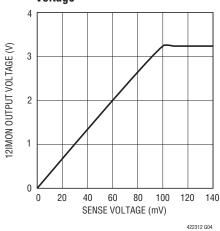

| G <sub>12IMON</sub>      | 12IMON Pin Gain Ratio $\Delta V_{12IMON}/\Delta(V_{12VIN} - V_{12VSENSE})$           | $(V_{12VIN} - V_{12VSENSE}) = (75mV, 25mV)$                                      | • | 30                | 33                 | 36                | V/V            |

| V <sub>12IMON</sub>      | 12IMON Pin Output Voltage                                                            | $(V_{12VIN} - V_{12VSENSE}) = 75mV, V_{CC} = 2.7V$                               | • | 2.25              | 2.475              | 2.7               | V              |

| $\Delta V_{SENSE(MAX)}$  | 12IMON Pin Maximum Input Sense Voltage                                               |                                                                                  | • | 82.5              |                    |                   | m۷             |

| V <sub>12IMON(CLP)</sub> | 12IMON Pin Clamp Voltage                                                             | $(V_{12VIN} - V_{12VSENSE}) = 150mV, V_{CC} = 2.7V$                              | • | 2.9               | 3.2                | 3.5               | V              |

| R <sub>12IMON</sub>      | 12IMON Pin Output Resistance                                                         | $(V_{12VIN} - V_{12VSENSE}) = 0V$                                                | • | 115               | 165                | 215               | kΩ             |

| V <sub>12IMON(MIN)</sub> | 12IMON Pin Minimum Output Voltage                                                    | $(V_{12VIN} - V_{12VSENSE}) = 0V$                                                | • |                   | 0                  | 130               | m۷             |

| Comparator In            | puts                                                                                 |                                                                                  |   |                   |                    |                   |                |

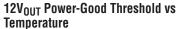

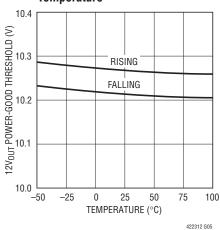

| V <sub>PG(TH)</sub>      | Power Good Threshold Voltage                                                         | V <sub>12VOUT</sub> Falling<br>V <sub>AUXOUT</sub> Falling                       | • | 10<br>2.8         | 10.3<br>2.885      | 10.6<br>2.97      | V              |

| V <sub>PG(HYST)</sub>    | Power Good Hysteresis                                                                | V <sub>12VOUT</sub><br>V <sub>AUXOUT</sub>                                       | • | 20<br>5           | 60<br>16           | 110<br>30         | mV<br>mV       |

| V <sub>TMR(TH)</sub>     | TIMER Pin Threshold Voltage                                                          | V <sub>TIMER</sub> Rising<br>V <sub>TIMER</sub> Falling                          | • | 1.198<br>0.15     | 1.235<br>0.2       | 1.272<br>0.25     | V<br>V         |

## LTC4223-1/LTC4223-2

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are $T_A = 25^{\circ}C$ , $V_{CC} = 3.3V$ , $V_{AUXIN} = 3.3V$ , $V_{12VIN} = 12V$ , unless otherwise specified. (Note 2)

| SYMBOL                  | PARAMETER                                                                                     | CONDITIONS                                                                                                                                |   | MIN                 | TYP                | MAX                | UNITS          |

|-------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------|--------------------|--------------------|----------------|

| I <sub>TMR(UP)</sub>    | TIMER Pull-Up Current                                                                         | V <sub>TIMER</sub> = 1V, Initial Timing Cycle<br>V <sub>TIMER</sub> = 0V, In AUX Fault Mode<br>V <sub>TIMER</sub> = 0V, In 12V Fault Mode | • | -7<br>-7<br>-140    | -10<br>-10<br>-200 | -13<br>-13<br>-260 | μΑ<br>μΑ<br>μΑ |

| I <sub>TMR(DN)</sub>    | TIMER Pull-Down Current                                                                       | V <sub>TIMER</sub> = 2V, No Faults<br>V <sub>TIMER</sub> = 2V, In Reset Mode                                                              | • | 1.3<br>2            | 2<br>8             | 2.6<br>16          | μA<br>mA       |

| Open Drain O            | utputs                                                                                        |                                                                                                                                           |   |                     |                    |                    |                |

| $V_{0L}$                | Output Low Voltage (FAULT, 12PGOOD, AUXPGOOD)                                                 | I <sub>OL</sub> = 3mA                                                                                                                     | • |                     | 0.15               | 0.4                | V              |

| V <sub>OH</sub>         | Output High Voltage (FAULT, 12PGOOD, AUXPGOOD)                                                | (Note 5)                                                                                                                                  | • | V <sub>CC</sub> – 1 |                    |                    | V              |

| I <sub>PU</sub>         | Output Pin Pull-Up Current (FAULT, 12PGOOD, AUXPGOOD)                                         | V <sub>PU</sub> = 1.5V                                                                                                                    | • | -6                  | -10                | -14                | μА             |

| Logic Inputs            |                                                                                               |                                                                                                                                           |   |                     |                    |                    |                |

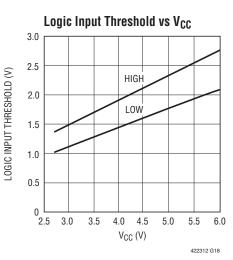

| $V_{IN(TH)}$            | Logic Input Threshold (120N, AUXON, $\overline{\text{EN}}$ )                                  |                                                                                                                                           | • | 0.8                 |                    | 2                  | V              |

| I <sub>IN(LEAK)</sub>   | Input Leakage Current (120N, AUXON)                                                           | $V_{IN} = V_{CC}$                                                                                                                         | • |                     |                    | ±1                 | μA             |

| R <sub>PU</sub>         | EN Pin Pull-Up Resistance                                                                     |                                                                                                                                           | • | 60                  | 100                | 140                | kΩ             |

| Other Pin Fun           | octions                                                                                       |                                                                                                                                           |   |                     |                    |                    |                |

| I <sub>12VSENSE</sub>   | 12V <sub>SENSE</sub> Pin Input Current                                                        | V <sub>12VSENSE</sub> = 12V                                                                                                               | • | 10                  | 50                 | 100                | μА             |

| I <sub>12VOUT</sub>     | 12V <sub>OUT</sub> Pin Input Current                                                          | Gate Drive On, V <sub>12VOUT</sub> = 12V                                                                                                  | • | 20                  | 50                 | 100                | μА             |

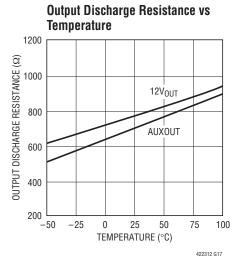

| R <sub>OUT(DIS)</sub>   | OUT Pin Discharge Resistance<br>12V <sub>OUT</sub><br>AUXOUT                                  | Gate Drive Off V <sub>12VOUT</sub> = 6V V <sub>AUXVOUT</sub> = 2V                                                                         | • | 400<br>375          | 800<br>750         | 1600<br>1500       | Ω              |

| Propagation I           | Delays                                                                                        |                                                                                                                                           | ' |                     |                    |                    |                |

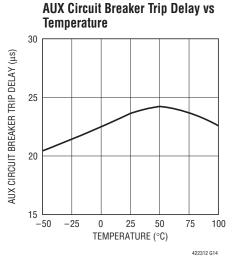

| $t_{CB}$                | AUX Circuit Breaker Trip Delay                                                                | After Power Up                                                                                                                            | • | 12                  | 25                 | 50                 | μs             |

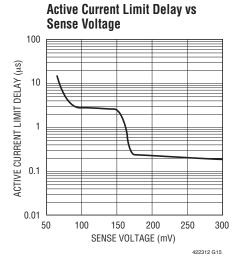

| t <sub>PHL(SENSE)</sub> | Sense Voltage, (12V <sub>IN</sub> – 12V <sub>SENSE</sub> )<br>High to 12V <sub>GATE</sub> Low | $\Delta V_{SENSE} = 300$ mV, $C_{12VGATE} = 10$ nF<br>$\Delta V_{SENSE} = 100$ mV, $C_{12VGATE} = 10$ nF                                  | • |                     | 0.5<br>5           | 1<br>12            | μs<br>μs       |

| t <sub>PHH(AUXON)</sub> | AUXON High to AUXOUT High                                                                     |                                                                                                                                           | • |                     | 15                 | 30                 | μs             |

| t <sub>PHH(120N)</sub>  | 120N High to 12V <sub>GATE</sub> High                                                         |                                                                                                                                           | • |                     | 30                 | 60                 | μs             |

| t <sub>RST(ON)</sub>    | Input Low (120N, AUXON) to FAULT High                                                         |                                                                                                                                           | • |                     | 20                 | 40                 | μs             |

| t <sub>RST(VCC)</sub>   | V <sub>CC</sub> Low to FAULT High                                                             |                                                                                                                                           | • |                     | 80                 | 150                | μs             |

| t <sub>PLL(UVL0)</sub>  | 12V <sub>IN</sub> Low to 12V <sub>GATE</sub> Low                                              |                                                                                                                                           | • | 6                   | 12                 | 18                 | μs             |

|                         | AUXIN Low to AUXPGOOD High                                                                    |                                                                                                                                           | • | 6                   | 12                 | 18                 | μs             |

| t <sub>PHL(GATE)</sub>  | EN High to 12V <sub>GATE</sub> Low                                                            |                                                                                                                                           | • |                     | 20                 | 40                 | μs             |

| t <sub>PLH(PG)</sub>    | 12V <sub>OUT</sub> Low to 12PGOOD High                                                        |                                                                                                                                           | • |                     | 20                 | 40                 | μs             |

|                         | AUXOUT Low to AUXPGOOD High                                                                   |                                                                                                                                           | • |                     | 20                 | 40                 | μs             |

| t <sub>P(12IMON)</sub>  | Input Sense Voltage Step to 12IMON<br>Propagation Delay                                       | ΔV <sub>SENSE</sub> = 100mV                                                                                                               | • |                     | 2                  | 6                  | μs             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into device pins are positive; all currents out of the device pins are negative. All voltages are referenced to GND unless otherwise specified.

**Note 3:** An internal clamp limits the  $12V_{GATE}$  pin to a minimum of 4.5V above  $12V_{OUT}$ . Driving this pin to voltages beyond the clamp may damage the device

**Note 4:** For the DFN package, the AUX switch on resistance,  $R_{DS(ON)}$  limit is guaranteed by correlation to wafer test measurements.

**Note 5:** The output pins  $\overline{FAULT}$ ,  $\overline{12PGOOD}$  and  $\overline{AUXPGOOD}$  have an internal pull-up to  $V_{CC}$  of  $10\mu A$ . However, an external pull-up resistor may be used when faster rise time is required or for  $V_{OH}$  voltages greater than  $V_{CC}$ .

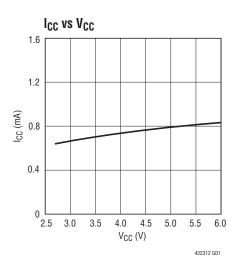

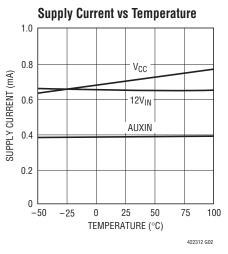

# **TYPICAL PERFORMANCE CHARACTERISTICS** 3.3V, V<sub>12VIN</sub> =12V, unless otherwise specified.

Specifications are  $T_A = 25$ °C,  $V_{CC} = 3.3V$ ,  $V_{AUXIN} =$

#### 12IMON Output Voltage vs Sense Voltage

**AUXOUT Power-Good Threshold** vs Temperature

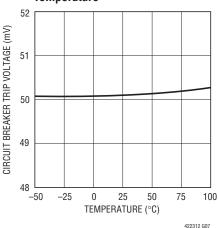

#### Circuit Breaker Trip Voltage vs **Temperature**

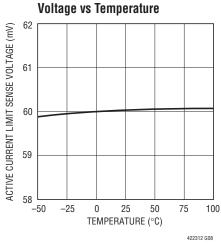

# **AUX Active Current Limit vs**

4223121

# TYPICAL PERFORMANCE CHARACTERISTICS 3.3V, V<sub>12VIN</sub> =12V, unless otherwise specified.

Specifications are  $T_A = 25^{\circ}C$ ,  $V_{CC} = 3.3V$ ,  $V_{AUXIN} =$

422312 G13

## PIN FUNCTIONS

**12V**<sub>SENSE</sub> (**Pin 1**): 12V Current Sense Input. Connect this pin to the output of the current sense resistor. The electronic circuit breaker trips if the voltage across the sense resistor exceeds 50mV for more than a fault filter delay.

$12V_{IN}$  (Pin 2): 12V Supply Input. Undervoltage lockout disables the 12V supply until the input at  $12V_{IN}$  exceeds 9.7V.

**12IMON (Pin 3):** 12V Current Sense Monitoring Output. This pin monitors the sense voltage between  $12V_{IN}$  and  $12V_{SENSE}$ . The gain ratio between this pin's voltage and the sense voltage is 33.

**120N (Pin 4):** 12V Supply On Control Digital Input. A rising edge turns on the external N-channel MOSFET if  $\overline{\text{EN}}$  is pulled low and a falling edge turns it off. A high-to-low transition on this pin will clear the 12V supply faults.

**AUXIN (Pin 5):** Auxiliary Supply Input. An internal  $0.3\Omega$  switch is connected between AUXIN and AUXOUT pins. Undervoltage lockout holds the switch off until the input at AUXIN exceeds 2.5V.

$V_{CC}$  (**Pin 6**): Bias Supply Input. This pin provides power to the device's internal circuitry and operates from 2.7V to 6V. Undervoltage lockout circuit disables the device until the input at  $V_{CC}$  exceeds 2.45V. Bypass with 330nF.

**AUXON (Pin 7):** Auxiliary Supply On Control Digital Input. A rising edge turns on the internal switch if  $\overline{\text{EN}}$  is pulled low and a falling edge turns it off. A high-to-low transition on both this pin and 120N pin will clear the auxiliary supply faults.

GND (Pin 8): Device Ground.

**TIMER (Pin 9):** Timer Capacitor Terminal. Connect a capacitor between this pin and ground to set a 741ms/μF duration for initial timing cycle, 123ms/μF for AUX current limit during power-up and 6ms/μF duration for 12V current limit before the external MOSFET is turned off.

**EN (Pin 10):** Enable Input Intended for Card Presence Detect. Ground this pin to enable the external N-channel MOSFET and internal switch to turn on. If this pin is pulled high, the switches are not allowed to turn on. An internal 100k resistor pulls up this pin. A high-to-low transition will clear faults.

**AUXPGOOD** (**Pin 11**): Auxiliary Supply Power Status Output. Open drain output that is normally pulled high by an internal  $10\mu A$  current source or an external pull-up resistor to  $V_{CC}$ . It pulls low when the AUXOUT pin voltage exceeds the power-good threshold of 2.901V.

**AUXOUT (Pin 12):** Auxiliary Supply Output. This pin is the output from the internal switch connected between AUXIN and AUXOUT pins. It signals  $\overline{AUXPGOOD}$  low when it exceeds 2.901V. A  $750\Omega$  active pull-down discharges AUXOUT to ground when the internal switch is turned off.

**FAULT** (**Pin 13**): Auxiliary and 12V Supply Fault Status Output. Open drain output that is normally pulled high by an internal  $10\mu\text{A}$  current source or an external pull-up resistor to  $V_{CC}$ . It pulls low when the circuit breaker is tripped due to an overcurrent fault on auxiliary or 12V supply.

**12PG00D** (**Pin 14**): 12V Supply Power Status Output. Open drain output that is normally pulled high by an internal  $10\mu$ A current source or an external pull-up resistor to  $V_{CC}$ . It pulls low when the  $12V_{OUT}$  pin voltage exceeds the power-good threshold of 10.36V.

**12V<sub>OUT</sub>** (**Pin 15**): 12V Gate Drive Return and Power-Good Input. Connect this pin to the source of the external N-channel MOSFET for gate drive return. This pin signals  $\overline{12PGOOD}$  low when it exceeds 10.36V. When the external MOSFET is turned off,  $12V_{OUT}$  is discharged to ground through a  $800\Omega$  active pull-down.

**12V**<sub>GATE</sub> (**Pin 16**): Gate Drive for 12V Supply External N-Channel MOSFET. An internal 10 $\mu$ A current source charges the gate of the external N-channel MOSFET. An internal clamp limits the gate voltage to 6.2V above 12V<sub>OUT</sub>. A resistor and capacitor network from this pin to ground sets the turn-on rate and compensates the active current limit. During turn-off, a 1mA pull-down current discharges 12V<sub>GATE</sub> to ground. During short circuit or undervoltage lockout, a 160mA pull-down current between 12V<sub>GATE</sub> and 12V<sub>OUT</sub> is activated.

**Exposed Pad (Pin 17, DHD Package):** Exposed pad may be left open or connected to device ground.

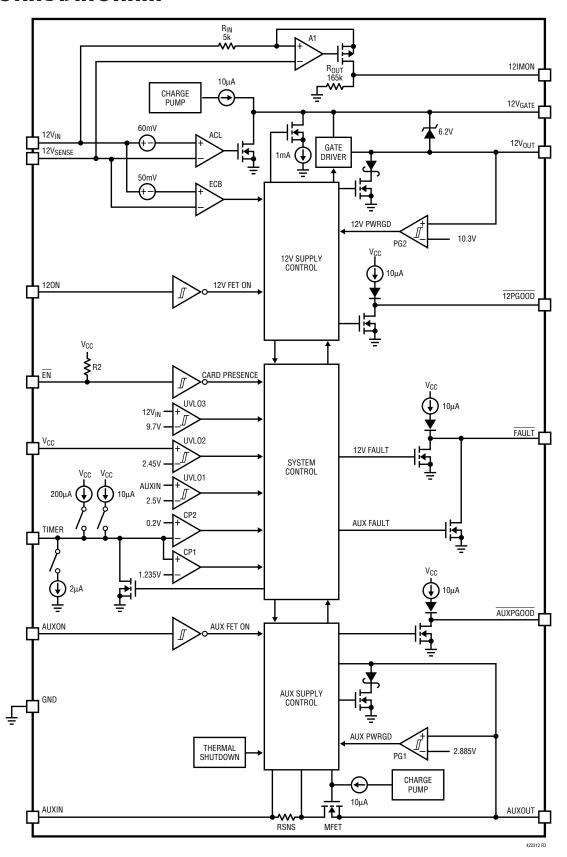

## **FUNCTIONAL DIAGRAM**

**TLINEAR**

## **OPERATION**

The LTC4223 is designed to control the power on an Advanced Mezzanine Card (AMC) or MicroTCA backplane, allowing boards to be safely inserted and removed. It controls the 12V main and 3.3V auxiliary power through an external N-channel MOSFET and integrated pass transistor. These two supplies can be turned on and off independently by their respective ON control pins.

If either AUXON or 120N is pulled high, an initial timing cycle set by the TIMER capacitor value is initiated once all these conditions are met: input supplies out of undervoltage lockout; TIMER < 0.2V and  $\overline{\text{EN}}$  low. At the end of the initial timing cycle, if the AUXON pin is high, the internal pass transistor turns on. It enters into an active current limit loop if the inrush current charging the load capacitor exceeds 240mA. When the load is in current limit, a  $10\mu\text{A}$  pull-up charges the TIMER pin capacitor. If the load capacitor is fully charged and the switch is no longer in current limit before the TIMER reaches 1.235V,  $\overline{\text{AUXPGOOD}}$  pulls low indicating that power is good. Otherwise the internal switch turns off and  $\overline{\text{FAULT}}$  pulls low when TIMER reaches 1.235V.

If 120N pin is high at the end of the initial timing cycle, an internal charge pump charges the gate of the external MOSFET with  $10\mu A$  pull-up. Connecting an external gate capacitor limits the inrush current charging the load capacitor. If the inrush current exceeds its limited current

value, an internal analog current limit (ACL) amplifier servos the gate to force 60mV across the external sense resistor connected between 12VIN and 12V<sub>SENSE</sub> pins. During this period, TIMER pin capacitor is charged by a 200µA pull-up. If the load is fully charged and no longer in current limit before the TIMER reaches 1.235V, 12PGOOD pulls low. Otherwise 12V shuts off and FAULT pulls low when TIMER reaches 1.235V.

If an overcurrent fault occurs on the auxiliary supply after power-up, the current is limited to 240mA and after a  $25\mu\text{s}$  delay, the circuit breaker trips and FAULT pulls low. Thermal shutdown protects the internal pass transistor from overheating by shutting it off at  $150^{\circ}\text{C}$ . If an overcurrent fault occurs on the 12V supply, the current is limited to  $60\text{mV/R}_{\text{SENSE}}$ . After a timing cycle delay set by  $200\mu\text{A}$  charging the TIMER capacitor, the circuit breaker trips and FAULT pulls low. An overcurrent fault on the auxiliary supply shuts off 12V; a fault on the 12V supply does not affect the auxiliary supply.

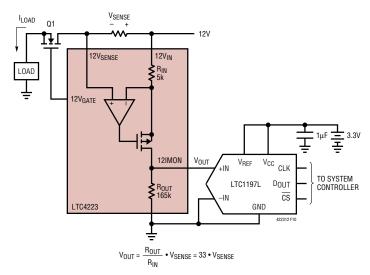

The LTC4223 provides high side current sensing information for the 12V supply at the 12IMON pin. The 12IMON output voltage is 33 times the sense voltage, allowing it to be used with an external ADC.

In the off condition,  $12V_{OUT}$  and AUXOUT are discharged to ground by internal N-channel pull downs.

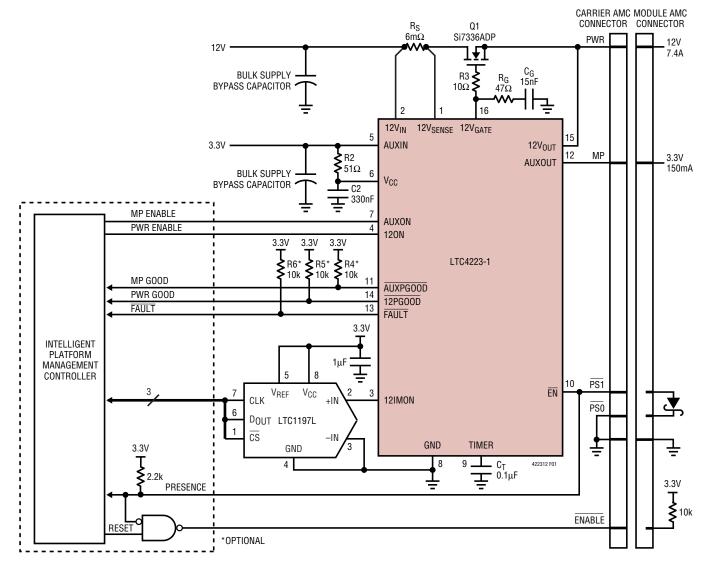

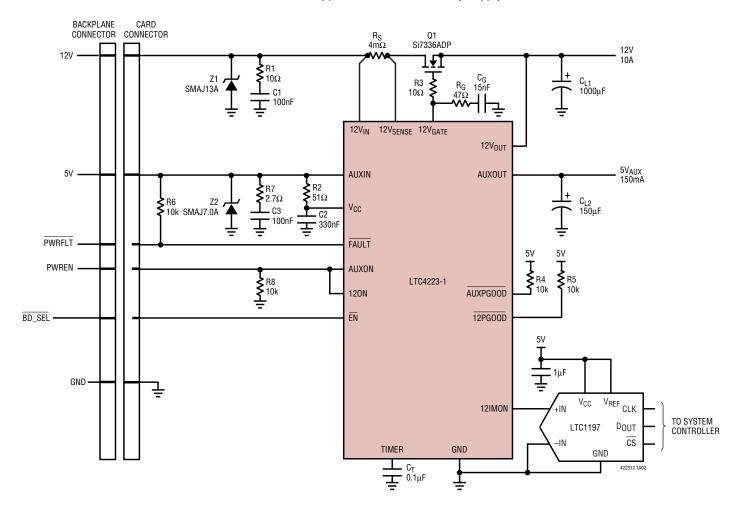

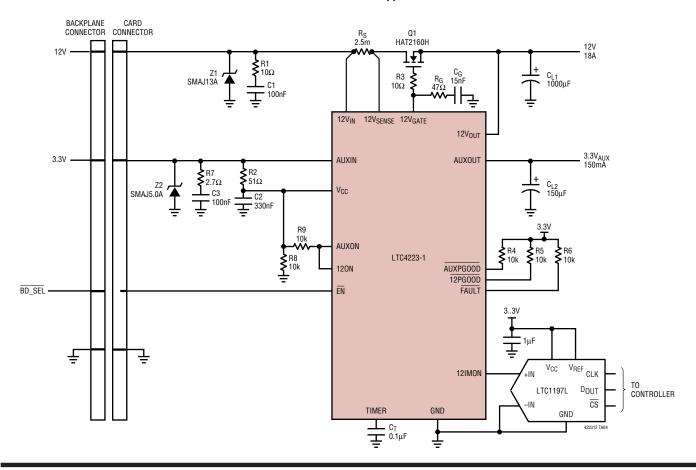

Figure 1. Advanced Mezzanine Card/MicroTCA Application

The typical LTC4223 application is in a Carrier board for Advanced Mezzanine Cards (AMC), delivering 3.3V auxiliary and 12V power to the AMC module. A controller on the Carrier board sequences the turn-on of power supplies and manages the fault and power-good reports from the LTC4223.

The LTC4223 detects board presence during insertion and extraction, allowing power to be delivered in a controlled manner without damaging the connector. The typical LTC4223 application circuit is shown in Figure 1. External component selection is discussed in detail in the Design Example section.

#### **Turn-On Sequence**

The power supplies delivered to an AMC module are controlled by the external N-channel pass transistor, Q1 in the 12V power path and an internal pass transistor in the 3.3V auxiliary power path. Sense resistor  $R_S$  monitors the 12V load current for fault detection and current sensing information. GATE capacitor  $C_G$  provides gate slew rate control to limit the inrush current. Resistor  $R_G$  with  $C_G$  compensates the current control loop while R3 prevents parasitic oscillations in Q1.

LINEAR TECHNOLOGY

Several conditions must be met before the external and internal switches are allowed to turn on. First  $V_{CC}$  and the input supplies (12 $V_{IN}$ , AUXIN) must exceed their undervoltage lockout thresholds. Next TIMER must be <0.2V and  $\overline{EN}$  must be pulled low.

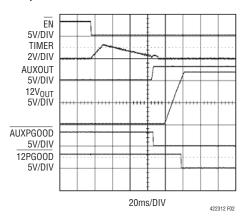

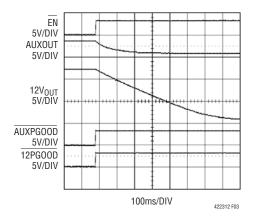

Once these conditions are met, a debounce timing cycle is initiated when AUXON or 120N pin is toggled from low to high. These two control pins turn on/off the 3.3V auxiliary and 12V supplies. At the end of the debounce cycle, the ON pins and fault status are checked. If both ON pins are high and fault is cleared, the 3.3V auxiliary supply starts up first followed by the 12V supply. Note that the turn-on delay for the AUXON and 120N pins is 15 $\mu$ s and 30 $\mu$ s. Figure 2 shows the two supplies turning on in sequence after  $\overline{\text{EN}}$  goes low.

By default, the internal pass transistor turns on first if both ON pins are high and start-up conditions met. The output is current limited at 240mA by its internal ACL amplifier as the load current charging the output capacitor increases. This causes the TIMER to ramp up with a  $10\mu A$  pull-up. Normally the AUXOUT voltage exceeds its power-good threshold before TIMER time-out and then AUXPGOOD pulls low.

Figure 2. Normal Power-Up Sequence

Once AUXOUT signals power is good and the TIMER pin returns to <0.2V, the external MOSFET is then allowed to turn on by charging up the GATE with a 10 $\mu$ A current source (Figure 2). The voltage at the GATE pin rises with a slope equal to  $10\mu$ A/C<sub>G</sub> and the supply inrush current flowing into the load capacitor C<sub>I 1</sub> (see Figure 14) is limited to:

$$I_{INRUSH} = \frac{C_{L1}}{C_G} \cdot 10 \mu A$$

The 12V output follows the GATE voltage when the MOSFET turns on. If the voltage across the current sense resistor  $R_S$  becomes too high, the inrush current is limited by the internal current limit circuitry. Once the output,  $12V_{OUT}$  exceeds its power-good threshold,  $\overline{12PGOOD}$  also pulls low.

If only the 120N pin is high at the end of debounce cycle, the external MOSFET turns on first. After that, if AUXON pulls high, the internal switch turns on only after the 12V output signals power is good and TIMER <0.2V.

Table 1. 12V and Auxiliary Supply Turn-Off Conditions

| CONDITION                 | RESULT    |           | CLEARED BY                                                                                 |

|---------------------------|-----------|-----------|--------------------------------------------------------------------------------------------|

|                           | AUX       | 12V       |                                                                                            |

| AUXON Goes<br>Low         | Turns Off | No Effect | AUXON High                                                                                 |

| 120N Goes Low             | No Effect | Turns Off | 120N High                                                                                  |

| EN Goes High              | Turns Off | Turns Off | EN Low                                                                                     |

| UVLO on V <sub>CC</sub>   | Turns Off | Turns Off | V <sub>CC</sub> > UVLO                                                                     |

| UVLO on AUXIN             | Turns Off | No Effect | AUXIN > UVLO                                                                               |

| UVLO on 12V <sub>IN</sub> | No Effect | Turns Off | 12V <sub>IN</sub> > UVLO                                                                   |

| AUX Overcurrent<br>Fault  | Turns Off | Turns Off | AUXON and 120N Low,<br>EN High-to-Low, UVLO<br>on V <sub>CC</sub>                          |

| 12V Overcurrent<br>Fault  | No Effect | Turns Off | 120N Low, EN High-to-<br>Low, UVLO on V <sub>CC</sub>                                      |

| Thermal<br>Shutdown       | Turns Off | Turns Off | AUXON and 120N Low,<br>EN High-to-Low, UVLO<br>on V <sub>CC</sub> , Temperature <<br>120°C |

#### **Turn-Off Sequence**

The switches can be turned off by various conditions and this is summarized in Table 1.

When the 120N pin goes low, the external switch is turned off with the GATE pin pulled to ground by 1mA current sink. The 12PGOOD pin pulls high indicating that power is no longer good, while an internal N-channel transistor discharges the output to ground. Similarly, when the AUXON pin goes low, the internal switch is turned off, AUXPGOOD pulls high while its output is discharged to ground through an internal N-channel transistor. Figure 3 shows the two supplies being turned off by EN going high.

#### **Card Presence Detect**

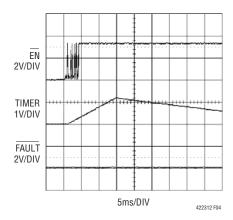

In an AMC system,  $\overline{PS1}$  and  $\overline{PS0}$  signals are used to detect the presence of a card upon insertion or removal. Normally  $\overline{PS1}$  is connected to the  $\overline{EN}$  pin with a pull-up resistor. If AUXON or 120N is high when the  $\overline{EN}$  pin goes low, indicating a board insertion, a timing cycle for contact debouncing is initiated. Upon insertion, any bounces on the  $\overline{EN}$  pin will re-start the timing cycle. When TIMER finally reaches its threshold during ramp up, the fault latches will be cleared. If the  $\overline{EN}$  pin remains low at the end of the timing cycle, the switches are allowed to turn on.

If the  $\overline{EN}$  pin is toggled from low to high, indicating board removal, all the switches will be turned off after a 20µs delay. Any latched faults will not be cleared. However, removing the card could cause the  $\overline{EN}$  pin voltage to bounce, clearing the fault latches undesirably. This is prevented by blanking

Figure 3. Normal Power-Down Sequence

the bounces internally with a TIMER ramp up period given by  $C_T \cdot 123[ms/\mu F]$  as shown in Figure 4.

#### **Timer Functions**

An external capacitor  $C_T$  connected from the TIMER pin to ground is used to perform several functions.

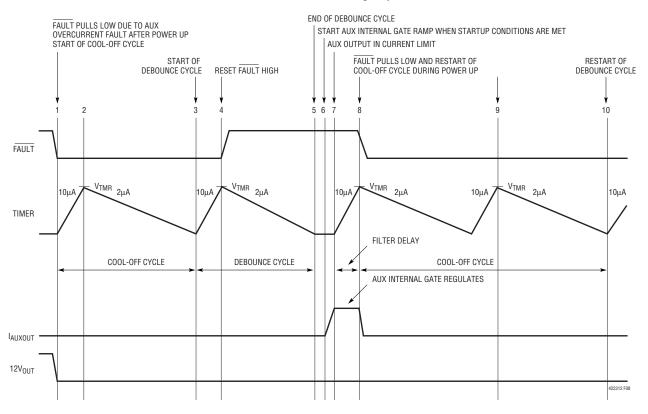

- 1. Ignore contact debouncing during card insertion when the device is enabled. The debounce cycle is given by ramping up  $C_T$  with  $10\mu A$  current to TIMER high threshold (1.235V) and then ramping down with  $2\mu A$  current to below TIMER low threshold (0.2V). This gives an average debounce cycle time of  $C_T$   $741[ms/\mu F]$ . After that, if any ON pin is pulled high and  $\overline{EN}$  pin is low, the switches can be turned on.

- 2. Blanking contact bounce on the EN pin that might trigger unwanted fault clearing during card removal. The blanking time is given by C<sub>T</sub> 123[ms/μF].

- 3. Fault filtering during auxiliary supply power-up in analog current limit. TIMER pulls up with  $10\mu A$  and pulls down with  $2\mu A$ . The filter time is given by  $C_T \cdot 123[ms/\mu F]$ .

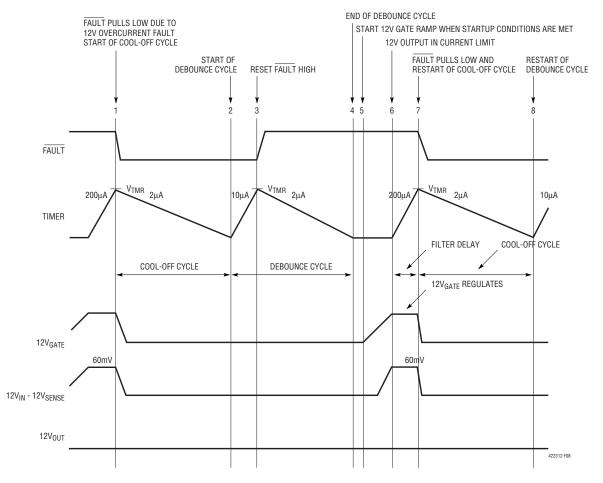

- 4. 12V supply fault filtering during and after power-up in analog current limit. TIMER pulls up with 200 $\mu$ A and pulls down with 2 $\mu$ A. The filter time is given by  $C_T \cdot 6[ms/\mu F]$ .

- 5. For cooling off during an auto-retry cycle after an overcurrent fault on auxiliary or 12V supply (LTC4223-2). The cool-off time is given by  $C_T \cdot 1482$  [ms/ $\mu$ F] after an auxiliary supply fault and  $C_T \cdot 1358$ [ms/ $\mu$ F] after a 12V supply fault.

Figure 4. Debouncing by TIMER during Card Removal

As the TIMER capacitor is used for fault filtering during power-up for both the auxiliary and 12V supplies, only one supply can be started up at any one time. The other supply waits until the power-good signal is generated by the powering-up supply and the TIMER pin voltage falls below 0.2V. By default, the 3.3V auxiliary supply starts up first if both AUXON and 12ON are high at the end of the debounce cycle.

Whenever both AUXON and 120N are pulled low, the device is in reset mode and TIMER capacitor is discharged to ground by an 8mA current sink.

#### Thermal Shutdown

The internal 3.3V auxiliary supply switch is protected by thermal shutdown. If the switch's temperature reaches 150°C, the aux switch will shut off immediately and FAULT will pull low. The external 12V supply switch also turns off. The switches are allowed to turn on again by cycling both the AUXON and 120N pins low then high after the internal switch's temperature falls below 120°C.

#### **Overcurrent Fault**

The LTC4223 features an adjustable current limit with circuit breaker function that protects the external MOSFET against

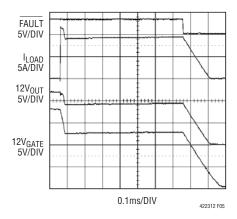

Figure 5. Overcurrent Fault on 12V Output

short circuits or excessive load current on 12V supply. The voltage across the external sense resistor is monitored by the analog current limit (ACL) amplifier and the electronic circuit breaker (ECB) comparator. If an overcurrent fault occurs that causes the sense voltage to reach the ACL threshold (60mV), the ACL amplifier regulates the MOSFET to prevent any further increase in current. This overcurrent condition results in a sense voltage that exceeds the ECB threshold. As a result, the TIMER capacitor is charged by a 200µA current. If the condition persists, the TIMER pin voltage will reach its threshold (1.235V). When this occurs, the FAULT pin pulls low and a 1mA current pulls the GATE pin to ground causing the MOSFET to turn off. The circuit breaker time delay, the time required for the TIMER pin capacitor to charge from ground to the TIMER pin threshold, is given by  $C_T \cdot 6[ms/\mu F]$ .

After the MOSFET turns off, the TIMER pin capacitor discharges with a  $2\mu A$  pull-down current. For the auto-retry version (LTC4223-2), if the TIMER discharges to below 0.2V, a new start-up cycle will begin. The TIMER starts ramping up and clears faults when it exceeds 1.235V; thereafter it ramps down (see the section on Auto-Retry for details). Figure 5 shows an overcurrent fault on the 12V output.

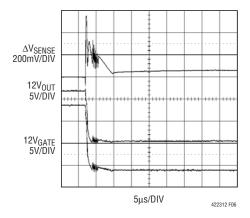

In the event of a severe short-circuit fault on 12V output as shown in Figure 6, the output current can surge to tens of amperes. The LTC4223 responds within a very short time to bring the current under control by pulling the MOSFET's GATE-to-SOURCE pin voltage down to zero volts. Thereafter, the GATE of the MOSFET recovers rapidly due to the  $R_G/C_G$  compensation network and enters into active current limiting until the TIMER times out. Due to parasitic supply lead inductance, an input supply without any bypass capacitor will collapse during the high current surge and then spike upwards when the current is interrupted. An input supply transient protection network comprising of Z1, R1 and C1 shown in Figure 13 is recommended if there is no input capacitance.

There are two different modes of fault time-out for the 3.3V auxiliary supply: adjustable delay through TIMER capacitor during power-up when  $\overline{AUXPGOOD}$  not asserted; fixed 25µs delay after power-up when  $\overline{AUXPGOOD}$  asserted low. Under the situation whereby AUXON toggles low then high for short duration after power-up while  $\overline{AUXPGOOD}$  still pulling low due to output load capacitor, 25µs fault time-out applies.

When the auxiliary supply is powered up into an output short, the ACL amplifier will regulate the gate of the internal pass transistor to produce 240mA output current. At this time a 10 $\mu$ A pull-up current starts charging up the TIMER pin capacitor until it exceeds its threshold (1.235V). The internal pass transistor then turns off and FAULT pulls low. Thereafter, the TIMER is discharged by a 2 $\mu$ A pull-down current. The fault filter delay is given by C<sub>T</sub> • 123[ms/ $\mu$ F].

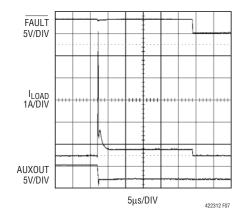

After a successful power-up cycle, the ACL amplifier protects the auxiliary supply from overcurrent by pulling down the gate of the internal pass transistor rapidly as shown in Figure 7. Thereafter, the gate recovers and servos the output current to about 240mA for 25µs before pulling down to ground gently, turning the transistor off. At this time, FAULT pulls low and the 12V external MOSFET is also turned off by the 1mA GATE pull-down current.

Figure 6. Short-Circuit Fault on 12V Output

Whenever the 3.3V auxiliary supply trips off due to an overcurrent fault, the 12V supply also shuts off. The auxiliary supply is, however, unaffected by faults on the 12V supply. In either case FAULT latches low when the affected channels turn off, and FAULT is cleared by toggling the ON pins. Faults are cleared automatically in the LTC4223-2 auto-retry version.

If there is significant supply lead inductance, a severe output short may collapse the input to ground before the LTC4223 can bring the current under control. In this case the undervoltage lockout will activate after a 12µs filter delay, and pull the gate down. Then the ACL amplifier will take control and regulate the output in active current limit. Under this situation, the fault time-out is set by TIMER delay instead of 25µs filter delay.

#### **Undervoltage Fault**

An undervoltage fault occurs if either AUXIN or  $12V_{IN}$  falls below its undervoltage threshold for longer than  $12\mu s$ . This turns off the affected supply's switch instantly, but does not clear the fault latches. Further, an undervoltage fault on one supply does not affect the operation of the other supply. If the bias supply input,  $V_{CC}$  falls below its UVLO threshold for more than  $80\mu s$ , all supply switches are turned off and the fault latches are cleared. Operation resumes from a fresh start-up cycle when  $V_{CC}$  is restored.

Figure 7. Short-Circuit Fault on 3.3VAUX Output

LINEAR TECHNOLOGY

### **Power-Good Monitor**

Internal circuitry monitors the output voltages, AUXOUT and  $12V_{OUT}$ . The power-good status is reported via their respective open drain outputs, AUXPGOOD and 12PGOOD. Several conditions must be met before the power-good outputs assert low.

- 1. The monitored output should be above its power-good threshold and hysteresis.

- 2. The input supply is above undervoltage lockout.

- 3.  $\overline{\mathsf{EN}}$  is low.

- 4. The associated ON pin is high.

- 5. Thermal shutdown is not activated.

If any of the supply outputs falls below its power-good threshold for more than 20 $\mu$ s, the respective power-good output will be pulled high by the external pull-up resistor or internal 10 $\mu$ A pull-up.

### Resetting Faults (LTC4223-1)

Any supply faults tripping the circuit breaker are latched and FAULT asserts low. For the latched-off version (LTC4223-1), to reset a fault latch due to overcurrent or thermal shutdown on auxiliary supply, pull both AUXON and 120N pins low together for at least 100µs, after which the FAULT will go high. Toggling both the ON pins high together again initiates the debounce timing cycle, thereafter the auxiliary supply starts up first followed by 12V supply. To skip the debounce timing cycle, first pull only AUXON low then high for at least 50µs before toggling 120N low then high. The fault latch clears on the falling edge of 120N and the auxiliary supply powers up. Thereafter, the 12V supply powers up if 120N pulls high.

To reset a fault on the 12V supply and re-start the output, toggle only the 120N pin low and then high again. Toggling the  $\overline{\text{EN}}$  pin high then low again or bringing the bias input,  $V_{CC}$  below its UVLO threshold for more than 100µs will initiate the debounce timing cycle and reset all fault latches before power-up. Bringing AUXIN or 12V<sub>IN</sub> below its undervoltage threshold will not reset the fault latches. For the auto-retry version (LTC4223-2), the latched fault will be cleared automatically after a cool-off timing cycle.

#### Auto-Retry after a Fault (LTC4223-2)

At time point 1 in Figure 8, if a fault latched-off the 3.3V auxiliary supply after power-up, a cool-off cycle begins. The TIMER capacitor charges up to 1.235V with a 10µA current and then discharges with a 2µA current to 0.2V at time point 3. This is followed by a debounce timing cycle whereby the fault latch is cleared, and FAULT pulls high when TIMER reaches its threshold at time point 4. At the end of debounce cycle, the internal switch is allowed to turn on. If the output short persists, the auxiliary supply powers up into a short with active current limiting. At time point 7, the fault filter delay begins with TIMER ramping up with a 10uA current. If the TIMER times out at time point 8, FAULT will be pulled low and a new cool-off cycle begins with TIMER ramping down with a 2µA current. The whole process repeats itself until the output-short is removed.

In Figure 9, a fault latches off the 12V supply at time point 1; a cool-off cycle begins by discharging the TIMER capacitor with  $2\mu A$  current from 1.235V to 0.2V threshold. At time point 2 a new debounce timing cycle is initiated where the fault latch is cleared, and FAULT pulls high when TIMER reaches its threshold at time point 3. At the end of the debounce cycle, the 12V GATE is allowed to start up. If the output short persists, the 12V supply powers up into a short with active current limiting. At time point 6, the fault filter delay begins with TIMER ramping up with a 200 $\mu$ A current. The TIMER times out at time point 7, FAULT pulls low and a new cool-off cycle begins with TIMER ramping down with a  $2\mu$ A current. The whole process repeats itself until the output-short is removed.

The auto-retry duty cycle is given by:

$$DutyCycle = \frac{t_{FILTER} \bullet 100\%}{t_{COOL} + t_{DEBOUNCE} + t_{FILTER}}$$

For example, if TIMER capacitor,  $C_T = 0.1 \mu F$ , the auto-retry duty cycle for auxiliary and 12V supply is 6.5% and 0.5% respectively.

#### **GATE Pin Voltage**

The gate drive at 12V<sub>GATE</sub> is compatible with any logic level MOSFET. The guaranteed range of gate drive is 4.5V to 7.9V, with a typical of 6.2V.

#### **Active Current Loop Compensation**

The compensation network consisting of resistor  $R_G$  and gate slew rate control capacitor  $C_G$  stabilizes the internal active current limit circuit. The value of  $C_G$  is selected based on the inrush current allowed. The suggested value for  $R_G$  is  $47\Omega.$  The value of  $C_G$  should be  $\leq\!330nF$  and  $R_G$  is between  $10\Omega$  and  $100\Omega$  for optimum performance.

### **High Side Current Sense**

The 12V load current is monitored via the voltage across an external sense resistor. The LTC4223 features a high side current sense amplifier that translates the sense voltage from the positive rail to the negative rail using a resistor ratio of 33 times. The output voltage at 12IMON pin can

then be fed into an LTC1197L ADC as shown in Figure 10 for data conversion. The current sense information can be used by the system controller to manage the power budget allocated to the modules on the card. Full scale input to the current sense amplifier is 82.5mV, corresponding to an output of about 2.7V. If the input exceeds 100mV, the output clamps at 3.2V.

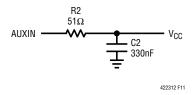

#### **V<sub>CC</sub> Supply Filtering**

The internal circuitry of the LTC4223 is powered from the  $V_{CC}$  pin. Bypass  $V_{CC}$  with at least 330nF to ground. If  $V_{CC}$  is derived from the same supply as is AUXIN, include a decoupling resistor as shown in Figure 11. This RC network allows the  $V_{CC}$  pin to ride out supply glitches caused by short circuits on the auxiliary output or on adjacent boards, thus preventing an undervoltage lockout condition on  $V_{CC}$ . Since the absolute maximum rating for  $V_{CC}$  is 7V as compared to 10V for AUXIN, select R2 and C2 to keep the peak voltage seen by  $V_{CC}$  below 7V during any voltage spikes.

Figure 8. Auto-Retry after AUX Overcurrent Fault

LINEAR TECHNOLOGY

Figure 9. Auto-Retry after 12V Overcurrent Fault

## **Supply Transient Protection**

The supply inputs, AUXIN and  $12V_{IN}$  are fed directly from the regulated output of the backplane supply, where bulk bypassing assures a spike-free operating environment. In other applications where the bulk bypassing is located far from the LTC4223, spikes generated during output short circuit events could exceed the absolute maximum ratings for AUXIN and  $12V_{IN}$ . To minimize such spikes, use wider traces or heavier trace plating to reduce the power trace inductance. Also, bypass locally with a  $10\mu$  electrolytic and 100nF ceramic, or alternatively clamp the input with a transient voltage suppressor (Z1, Z2) as shown in Figure 13. A  $10\Omega$ , 100nF snubber damps the response and eliminates ringing. A recommended layout of the 12V transient protection devices Z1, R1 and C1 around the LTC4223 is shown in Figure 12.

Figure 10. High Side Current Sense with LTC1197L ADC

Figure 11. RC Network for V<sub>CC</sub> Filtering

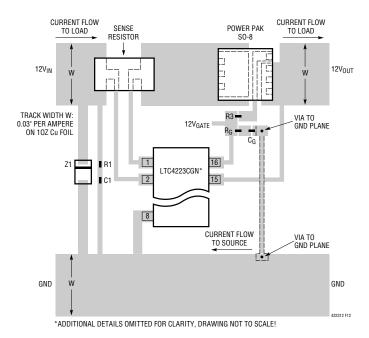

#### **PCB Layout Considerations**

For proper operation of the LTC4223's circuit breaker, Kelvin-connection to the sense resistor is strongly recommended. The PCB layout should be balanced and symmetrical to minimize wiring errors. In addition, the PCB layout for the sense resistor and the power MOSFET should include good thermal management techniques for optimal device power dissipation. A recommended PCB layout for the 12V sense resistor and the power MOSFET is illustrated in Figure 12.

In applications where load current exceeds 10A, wide PCB traces are recommended to minimize resistance and temperature rise. The suggested trace width for 1 oz copper foil is 0.03" for each ampere of DC current to keep PCB trace resistance, voltage drop and temperature rise to a minimum. Note that the sheet resistance of 1 oz copper foil is approximately  $0.5 m\Omega/s$ quare, and voltage drops due to trace resistance add up quickly in high current applications.

In most applications, it will be necessary to use platedthrough via to make circuit connections from component layers to power and ground layers internal to the PCB. For 1 oz copper foil plating, a general rule is 1A of DC current per via. Consult your PCB fabrication facility for design rules pertaining to other plating thicknesses.

It is important to place the  $V_{CC}$  bypass capacitor C2 as close as possible between  $V_{CC}$  and GND. The transient voltage suppressors Z1 and Z2 are also placed between the supply inputs and ground using short wide traces.

#### **Design Example**

As a design example, consider the AMC Hot Swap application shown earlier in Figure 1 with the power supply requirements given in Table 2.

Figure 12. Recommended Layout for Power MOSFET, Sense Resistor and GATE Components on 12V Rail

The first step is to select the appropriate value of  $R_{SENSE}$  for the 12V supply. Calculating  $R_{SENSE}$  value is based on the maximum load current and the lower limit for the circuit breaker threshold,  $\Delta V_{SENSE(CB)(MIN)}$ .

$$R_{SENSE} = \frac{\Delta V_{SENSE(CB)(MIN)}}{I_{LOAD(MAX)}} = \frac{47.5mV}{7.4A} = 6m\Omega$$

If a 1% tolerance is assumed for the  $6m\Omega$  sense resistor, the minimum and maximum circuit breaker trip current is calculated as follows:

**Table 2. AMC Power Supply Requirements**

| SUPPLY VOLTAGE      | MAXIMUM LOAD<br>Current | MAXIMUM LOAD CAPACITANCE |

|---------------------|-------------------------|--------------------------|

| 12V                 | 7.4A                    | 800µF                    |

| 3.3V <sub>AUX</sub> | 150mA                   | 150µF                    |

Table 3. MicroTCA Power Supply Requirements

| SUPPLY VOLTAGE      | MAXIMUM LOAD<br>Current | MAXIMUM LOAD<br>Capacitance |

|---------------------|-------------------------|-----------------------------|

| 12V                 | 7.6A                    | 1600µF                      |

| 3.3V <sub>AUX</sub> | 150mA                   | 150µF                       |

$$\begin{split} I_{TRIP(MIN)} = & \frac{\Delta V_{SENSE(CB)(MIN)}}{R_{SENSE(MAX)}} = \frac{47.5 mV}{6.06 m\Omega} = 7.8 A \\ I_{TRIP(MAX)} = & \frac{\Delta V_{SENSE(CB)(MAX)}}{R_{SENSE(MIN)}} = \frac{52.5 mV}{5.94 m\Omega} = 8.8 A \end{split}$$

For proper operation,  $I_{TRIP(MIN)}$  must exceed the maximum load current with margin, so  $R_{SENSE}$  =  $6m\Omega$  should suffice for the 12V supply.

The second step is to determine the TIMER capacitance based on the time required to charge up completely the output load capacitor on auxiliary supply in active current limit without exceeding the fault filter delay. The worst-case start-up time is calculated using the minimum active current limit value for the auxiliary supply.

$$t_{STUP(AUX)} = \frac{C_{L2} \cdot 3.3 V_{AUX}}{I_{AUX(ACL)(MIN)}} = \frac{150 \mu F \cdot 3.3 V}{165 mA} = 3 ms$$

For a start-up time of 3ms with a 2x safety margin, the TIMER capacitance is calculated as:

$$C_T = \frac{2 \cdot t_{STUP(AUX)}}{123[ms/\mu F]} = \frac{6ms}{123[ms/\mu F]} \approx 0.05 \mu F$$

Considering the tolerances for the TIMER charging rate and capacitance, a value of  $0.1\mu F$  (±10%) for  $C_T$  should suffice.

Since the TIMER charging rate during fault time-out is 20 times faster for the 12V supply as compared to the auxiliary supply during start-up, this scheme ensures that the external MOSFET will not overheat under any output-short condition. The fault filter delay for the 12V supply is given by  $0.1\mu\text{F} \cdot 6[\text{ms/}\mu\text{F}] = 600\mu\text{s}$  versus 12ms for the auxiliary supply.

The next step is to verify that the thermal ratings of the selected external MOSFET for the 12V supply aren't exceeded during power-up or an output-short.

Assuming the MOSFET dissipates power only due to inrush current charging the load capacitor, the energy dissipated in the MOSFET during power-up is the same as that stored into the load capacitor. The average power dissipated in the MOSFET is given by:

$$P_{AVG} = \frac{C_{L1} \cdot 12 V_{OUT}^2}{2 \cdot t_{CHARGE}}$$

The inrush current can be limited by using the GATE capacitance ( $C_G$ ) so that the power dissipated in the MOSFET is well within its safe operating area (SOA). For  $I_{GATE} = 10\mu A$  and  $C_{L1} = 800\mu F$ , we choose  $C_G = 15nF$  to set the inrush current to 0.5A.

$$I_{INRUSH} = \frac{C_{L1} \cdot I_{GATE}}{C_{G}} = 0.5A$$

$$t_{CHARGE} = \frac{C_{L1} \cdot 12V_{OUT}}{I_{INBUSH}} = 19ms$$

This results in  $P_{AVG}$  = 3W and the MOSFET selected must be able to tolerate 3W for 19ms. The increase in steady state junction temperature due to power dissipated in the MOSFET is  $\Delta T = P_{AVG} \cdot Z_{th}$  where  $Z_{th}$  is the thermal impedance.

Under this condition, the Si7336ADP datasheet's Transient Thermal Impedance plot indicates that the junction temperature will increase by 2.4°C using  $Z_{thJC} = 0.8$ °C/W (single pulse).

The duration and magnitude of the power pulse that results during a short-circuit condition on the 12V output are a function of the TIMER capacitance and LTC4223's analog current limit. The short-circuit duration is given as  $0.1\mu F$  •  $6[ms/\mu F]=600\mu s$  for  $C_T=0.1\mu F$ . The maximum short-circuit current is calculated using the maximum analog current limit threshold,  $\Delta V_{SENSE(ACL)(MAX)}$  and minimum  $R_{SENSE}$  value.

$$I_{SHORT(MAX)} = \frac{\Delta V_{SENSE(ACL)(MAX)}}{R_{SENSE(MIN)}} = \frac{66mV}{5.94m\Omega} = 11A$$

So the maximum power dissipated in the MOSFET is 11A • 12V or 132W for 600µs. The Si7336ADP datasheet's Transient Thermal Impedance plot indicates that the worse-case increase in junction temperature during the short-circuit condition is 13.2°C using  $Z_{thJC} = 0.1$ °C/W (single pulse). This will not cause the maximum junction temperature to be exceeded. The SOA curves of the Si7336ADP are also checked to be safe under this condition.

## TYPICAL APPLICATION

#### Card Resident Application with 5V Auxiliary Supply

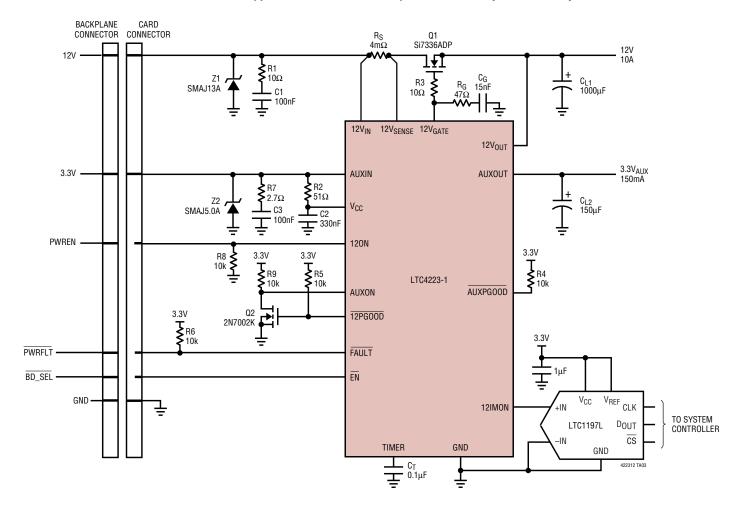

## TYPICAL APPLICATION

#### Card Resident Application with 12V Power Up First Followed by 3.3V Auxiliary

## PACKAGE DESCRIPTION

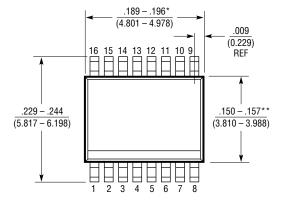

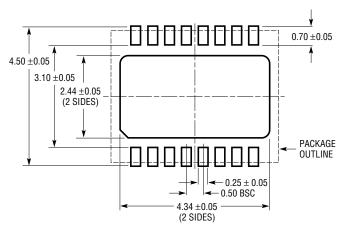

#### GN Package 16-Lead Plastic SSOP (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1641)

NOTE: 1. CONTROLLING DIMENSION: INCHES

2. DIMENSIONS ARE IN  $\frac{\text{INCHES}}{\text{(MILLIMETERS)}}$

- 3. DRAWING NOT TO SCALE

- \*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

- \*\*DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

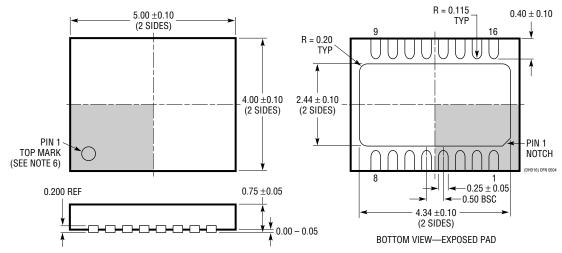

## PACKAGE DESCRIPTION

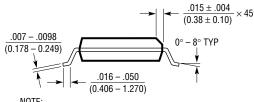

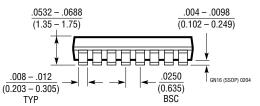

#### DHD Package 16-Lead Plastic DFN (5mm × 4mm)

(Reference LTC DWG # 05-08-1707)

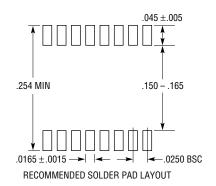

#### **RECOMMENDED** SOLDER PAD PITCH AND DIMENSIONS

#### NOTE:

- 1. DRAWING PROPOSED TO BE MADE VARIATION OF VERSION (WJGD-2) IN JEDEC PACKAGE OUTLINE MO-229

- 2. DRAWING NOT TO SCALE

- 3. ALL DIMENSIONS ARE IN MILLIMETERS

- 4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

- 5. EXPOSED PAD SHALL BE SOLDER PLATED

- 6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

## TYPICAL APPLICATION

#### 12V/18A Card Resident Application

## **RELATED PARTS**

| PART NUMBER                                       | DESCRIPTION                           | COMMENTS                                                                                            |

|---------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------|

| LTC1421                                           | Dual Channel, Hot Swap Controller     | Operates from 3V to 12V, Supports –12V, SSOP-24                                                     |

| LTC1645                                           | Dual Channel, Hot Swap Controller     | Operates from 3V to 12V, Power Sequencing, SO-8 or SO14                                             |

| LTC1647-1/LTC1647-2/<br>LTC1647-3                 | Dual Channel, Hot Swap Controller     | Operates from 2.7V to 16.5V, SO-8 or SSOP-16                                                        |

| LTC4210                                           | Single Channel, Hot Swap Controller   | Operates from 2.7V to 16.5V, Active Current Limiting, SOT23-6                                       |

| LTC4211                                           | Single Channel, Hot Swap Controller   | Operates from 2.7V to 16.5V, Multifunction Current Control, MSOP-8 or MSOP-10                       |

| LTC4215                                           | Single Channel, Hot Swap Controller   | Operates from 2.9V to 15V, I <sup>2</sup> C Compatible Monitoring, SSOP-16 or QFN-24 (4mm × 5mm)    |

| LTC4216                                           | Single Channel, Hot Swap Controller   | Operates from 0V to 6V, MSOP-10 or DFN-12 (4mm × 3mm)                                               |

| LTC4221                                           | Dual Channel, Hot Swap Controller     | Operates from 1V to 13.5V, Multifunction Current Control, SSOP-16                                   |

| LTC4245                                           | Multiple Channel, Hot Swap Controller | 3.3V, 5V, ±12V Supplies, I <sup>2</sup> C Compatible Monitoring, SSOP-36 or QFN-38 (5mm × 7mm)      |

| LTC4252-1/LTC4252-2/<br>LTC4252A-1/<br>LTC4252A-2 | -48V Hot Swap Controller              | Fast Active Current Limiting with Drain Accelerated Response, Supplies from -15V, MSOP-8 or MSOP-10 |

LT 0807 · PRINTED IN USA

LINEAR TECHNOLOGY CORPORATION 2007