# Contents

| 1    | Bloc  | k diagram                                              |

|------|-------|--------------------------------------------------------|

| 2    | Pins  | description                                            |

|      | 2.1   | Pin definitions and functions                          |

| 3    | Elec  | trical specifications 11                               |

|      | 3.1   | Absolute maximum ratings11                             |

|      | 3.2   | ESD protection                                         |

|      | 3.3   | Thermal data                                           |

|      | 3.4   | Electrical characteristics 12                          |

|      | 3.5   | Outputs OUT1 and OUT2                                  |

|      | 3.6   | Temperature dependent current reduction                |

|      | 3.7   | Free-wheeling diodes                                   |

|      | 3.8   | SPI / logic electrical characteristics 19              |

| 4    | Appl  | lication information                                   |

|      | 4.1   | Power stage switching behavior 21                      |

|      |       | 4.1.1 PWM mode (same current direction)                |

|      | 4.2   | Protection and monitoring 23                           |

|      |       | 4.2.1 Current feedback                                 |

|      |       | 4.2.2 Current limitation                               |

|      |       | 4.2.3 Temperature dependent current reduction          |

|      |       | 4.2.4 Short to battery (SCB) and short to Ground (SCG) |

|      |       | 4.2.5 Short circuit over load (SCL)                    |

|      | 4.0   | 4.2.6 Open load (OL)                                   |

|      | 4.3   | VS-undervoltage                                        |

|      | 4.4   | Inverse current at V <sub>S</sub>                      |

|      | 4.5   | /ABE pin                                               |

|      | 4.6   | VDD-monitor                                            |

|      | 4.7   | VDD-monitor test                                       |

|      | 4.8   | Power-on reset                                         |

| 5    | SPI f | functional description                                 |

| 2/43 |       | DocID023416 Rev 6                                      |

|   | 5.1    | General  | description                           | <u>29</u> |

|---|--------|----------|---------------------------------------|-----------|

|   |        | 5.1.1    | SPI select (SS)                       | 29        |

|   |        | 5.1.2    | Serial data In (SI)                   | 29        |

|   |        | 5.1.3    | Serial clock (SCK)                    | 29        |

|   |        | 5.1.4    | Serial out (SO)                       | 29        |

|   |        | 5.1.5    | SPI communication flow                | 29        |

|   | 5.2    | SPI-inst | ruction                               | 31        |

|   | 5.3    | Device r | egister map                           | 31        |

|   | 5.4    | SPI - co | ntrol and status registers 3          | 32        |

|   |        | 5.4.1    | Reset sources                         | 37        |

|   |        | 5.4.2    | Configuration registers reset sources | 37        |

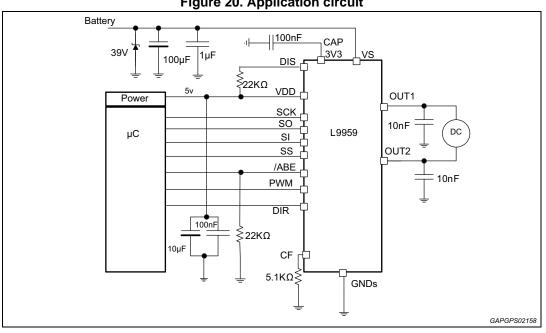

| 6 | Applie | cation c | ircuit                                | 8         |

| 7 | Packa  | ige info | rmation                               | 39        |

| 8 | Revis  | ion hist | ory4                                  | 1         |

# List of tables

| Table 1.  | Device summary                                             |

|-----------|------------------------------------------------------------|

| Table 2.  | L9959S pinout                                              |

| Table 3.  | L9959T (Two H-Bridge drivers in one package) pinout9       |

| Table 4.  | Absolute maximum ratings                                   |

| Table 5.  | ESD protection                                             |

| Table 6.  | Thermal data                                               |

| Table 7.  | Supply                                                     |

| Table 8.  | Power-on reset                                             |

| Table 9.  | V <sub>DD</sub> monitoring                                 |

| Table 10. | Undervoltage shutdown                                      |

| Table 11. | On-resistance (4.5 V < V <sub>S</sub> < 28 V)              |

| Table 12. | Power output switching times (8 V < V <sub>S</sub> < 18 V) |

| Table 13. | Current feedback (CF)                                      |

| Table 14. | Current limiting                                           |

| Table 15. | Over-current detection (8 V < $V_S$ < 18 V)                |

| Table 16. | Openload detection                                         |

| Table 17. | Retest delay                                               |

| Table 18. | Temperature dependent current reduction                    |

| Table 19. | Free-wheel diodes                                          |

| Table 20. | Inputs: SI, SS, SCK, DIR, DIS and PWM; Output: SO          |

| Table 21. | Dynamic characteristics                                    |

| Table 22. | Device states with respect to supply voltage               |

| Table 23. | SPI instruction byte                                       |

| Table 24. | Check byte                                                 |

| Table 25. | Command overview                                           |

| Table 26. | Device identifier (ID)                                     |

| Table 27. | Revision register (REV)                                    |

| Table 28. | DIA_REG1                                                   |

| Table 29. | Diagnosis bits (DIA_REG1)                                  |

| Table 30. | Diagnosis register 2 (DIA_REG2)                            |

| Table 31. | Diagnosis bits (DIA_REG2)                                  |

| Table 32. | Configuration register (CONFIG_REG)                        |

| Table 33. | Current Level (CONFIG_REG)                                 |

| Table 34. | Status and configuration register (STATCON_REG)            |

| Table 35. | Special register (SPECIAL_REG)                             |

| Table 36. | Document revision history                                  |

|           |                                                            |

# List of figures

| Figure 1.   | Block diagram                                     |

|-------------|---------------------------------------------------|

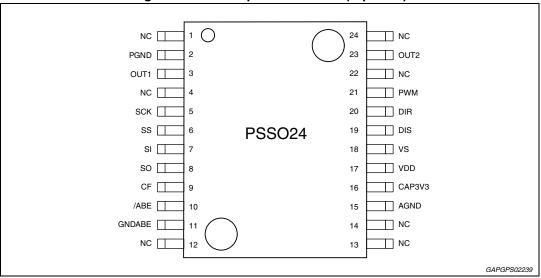

| Figure 2.   | PSSO24 pin connection (top view)                  |

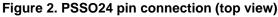

| Figure 3.   | PSSO36 pin connection (top view)                  |

| Figure 4.   | Output delay times (e.g. low-side output)         |

| Figure 5.   | Output rise and fall times                        |

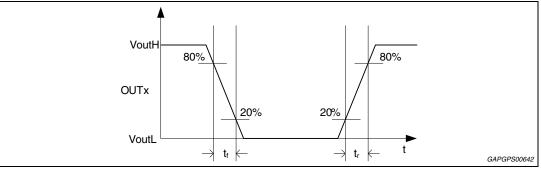

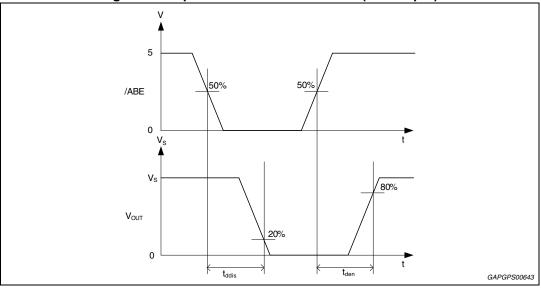

| Figure 6.   | Output disable and enable time (/ABE Input)       |

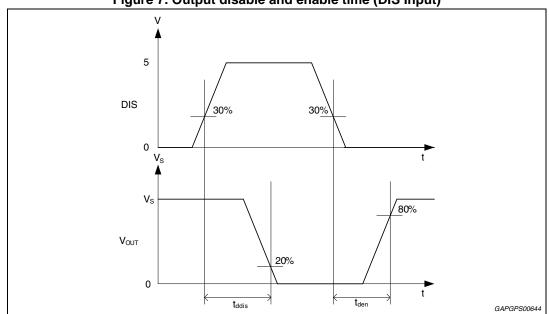

| Figure 7.   | Output disable and enable time (DIS Input)        |

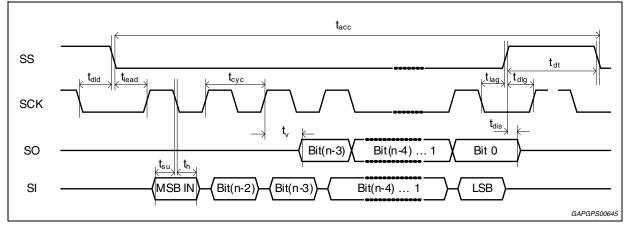

| Figure 8.   | SPI timing information                            |

| Figure 9.   | PWM mode current flow                             |

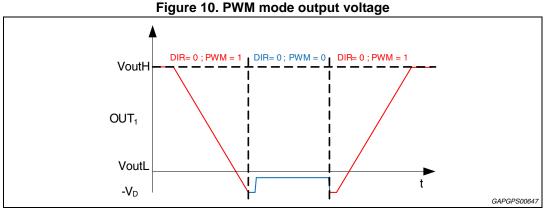

| Figure 10.  | PWM mode output voltage                           |

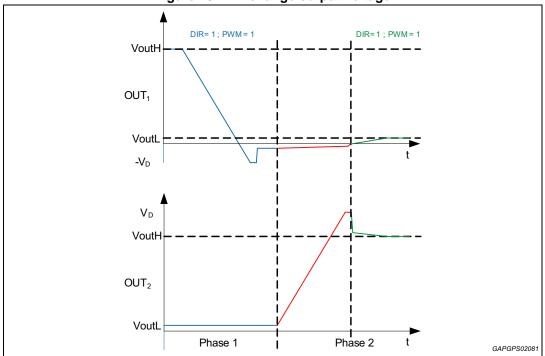

| Figure 11.  | DIR-change (current is changing its direction)    |

| Figure 12.  | DIR-change current flow phase 2                   |

| Figure 13.  | DIR-change output voltage                         |

| Figure 14.  | Current feedback and current limiting             |

| Figure 15.  | Current limitation                                |

| Figure 16.  | Temperature dependent current reduction           |

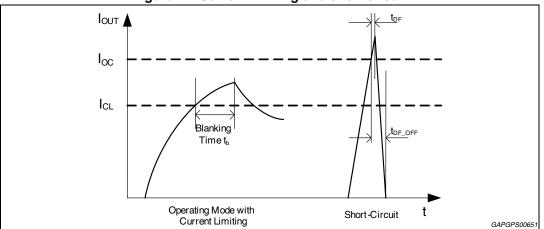

| Figure 17.  | Current limiting and short circuit                |

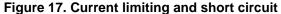

| Figure 18.  | Write access                                      |

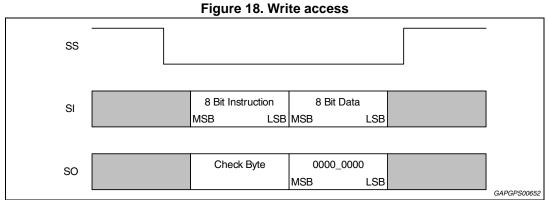

| Figure 19.  | Read access                                       |

| Figure 20.  | Application circuit                               |

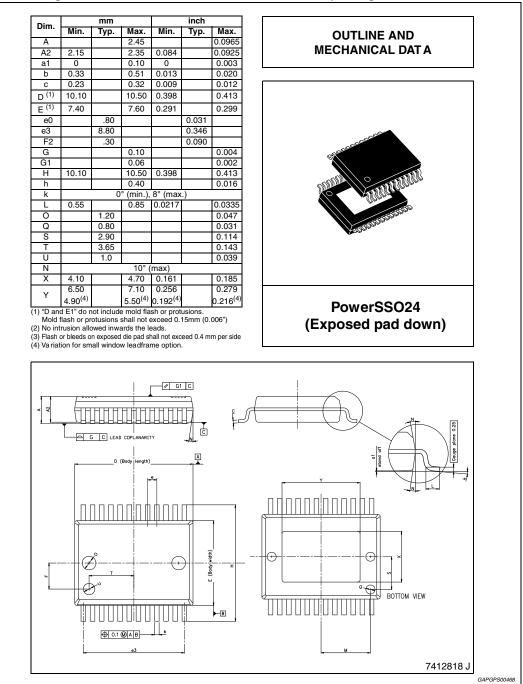

| Figure 20.  | PowerSSO24 mechanical data and package dimensions |

| Figure 21.  |                                                   |

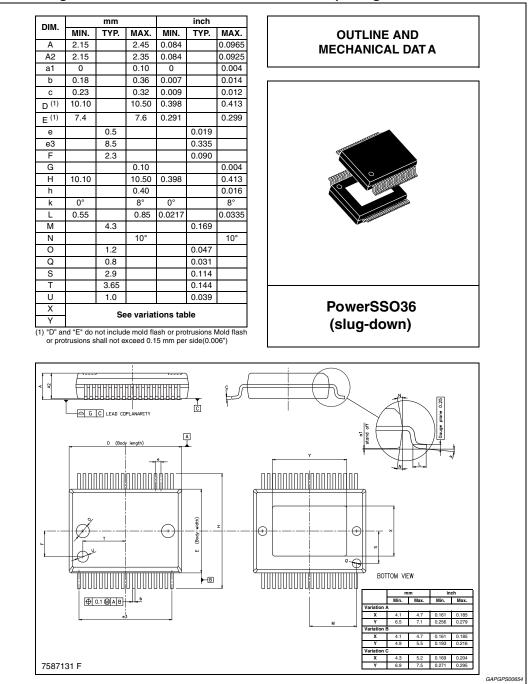

| i iyule zz. | PowerSSO36 mechanical data and package dimensions |

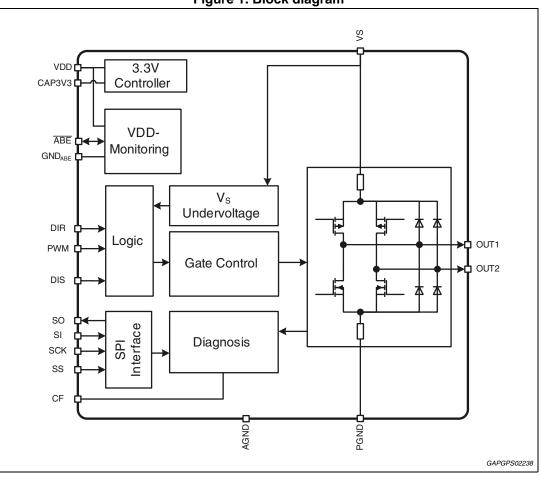

# 1 Block diagram

Figure 1. Block diagram

# 2 Pins description

#### Figure 3. PSSO36 pin connection (top view)

## 2.1 Pin definitions and functions

| Pin | Symbol | Function                                                                                                                                                                                                                                         |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18  | VS     | Power supply voltage for power stage outputs (external reverse protection required)                                                                                                                                                              |

| 2   | PGND   | Power Ground                                                                                                                                                                                                                                     |

| 16  | CAP3V3 | Pin for external capacitor:<br>This capacitor is used for the internal 3.3 V controller. A capacitance between 60 nF and<br>150 nF (typical 100 nF) is required and has to be connected close to this pin with low<br>inductance and resistance. |

| 17  | VDD    | VDD Supply: 5 V Supply                                                                                                                                                                                                                           |

| 11  | GNDABE | Sense Ground for VDD monitoring                                                                                                                                                                                                                  |

| 15  | AGND   | Device Ground                                                                                                                                                                                                                                    |

| 3   | OUT1   | Bridge output 1 and 2:                                                                                                                                                                                                                           |

| 23  | OUT2   | The bridge outputs are built of a high-side p-channel and a low-side n-channel transistor.                                                                                                                                                       |

| 20  | DIR    | Direction input:<br>The DIR pin controls the switch direction of OUT1 and OUT2.                                                                                                                                                                  |

| 21  | PWM    | PWM input:<br>The PWM input switches OUT1 and OUT2.                                                                                                                                                                                              |

| 19  | DIS    | Disable input:<br>DIS switches OUT1 and OUT2 to tristate.                                                                                                                                                                                        |

| 10  | /ABE   | Bidirectional Ability/Enable Pin:<br>Open-Drain Output, which is pulled low in case of VDD over- and under-voltage. If the input<br>is pulled to low, all output stages are switched off.                                                        |

| 9   | CF     | Current Proportional Feedback output:<br>The CF pin provides in conjunction with an external resistor an output current, which is<br>proportional to the H-Bridge current.                                                                       |

| 5   | SCK    | Serial clock input:<br>This input controls the internal shift register of the SPI.                                                                                                                                                               |

| 7   | SI     | Slave in (Serial data input):<br>The input receives serial data from the microcontroller.                                                                                                                                                        |

| 8   | SO     | Slave Out (Serial data output):<br>The diagnosis data is available via the SPI through this tristate-output.                                                                                                                                     |

| 6   | SS     | Slave Select input:<br>The serial data transfer between the device and the micro controller is enabled by pulling<br>the input SS to low level.                                                                                                  |

| EP  | AGND   | Exposed Pad:<br>Connected to AGND.                                                                                                                                                                                                               |

#### Table 2. L9959S pinout

8/43

| Pin      | Symbol               | Function                                                                                                                                                                                                                                         |  |  |  |  |

|----------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 13,14,   | VS2 <sup>(1)</sup>   | Power supply voltage for power stage outputs (external reverse protection required):                                                                                                                                                             |  |  |  |  |

| 31, 32   | VS1 <sup>(1)</sup>   | Important: For the capability of driving the full current at the outputs all pins of VS must be externally connected.                                                                                                                            |  |  |  |  |

| 1        | PGND1 <sup>(2)</sup> | Ground:                                                                                                                                                                                                                                          |  |  |  |  |

| 19       | PGND2 <sup>(2)</sup> | Important: For the capability of driving the full current at the outputs, all ground pins must be externally connected.                                                                                                                          |  |  |  |  |

| 11, 29   | CAP3V3               | Pin for external capacitor:<br>This capacitor is used for the internal 3.3 V controller. A capacitance between 60 nF and<br>150 nF (typical 100 nF) is required and has to be connected close to this pin with low<br>inductance and resistance. |  |  |  |  |

| 12       | VDD1 <sup>(3)</sup>  |                                                                                                                                                                                                                                                  |  |  |  |  |

| 30       | VDD2 <sup>(3)</sup>  | VDD Supply: 5V Supply.                                                                                                                                                                                                                           |  |  |  |  |

| 9        | GNDABE1              | Samaa Cround for VDD monitoring                                                                                                                                                                                                                  |  |  |  |  |

| 27       | GNDABE2              | Sense Ground for VDD monitoring                                                                                                                                                                                                                  |  |  |  |  |

| 10, 28   | AGND                 | Device Ground                                                                                                                                                                                                                                    |  |  |  |  |

| 2        | OUT11                |                                                                                                                                                                                                                                                  |  |  |  |  |

| 36 OUT12 |                      | Bridge output 11, 12, 21, and 22:<br>The bridge outputs are built of a high-side p-channel and a low-side n-channel transistor.                                                                                                                  |  |  |  |  |

| 20       | OUT21                | The bridge outputs of chip 1 are OUT11 and OUT12, of chip 2 OUT21 and OUT22.                                                                                                                                                                     |  |  |  |  |

| 18       | OUT22                |                                                                                                                                                                                                                                                  |  |  |  |  |

| 34       | DIR1                 | Direction input 1:<br>DIR1 pin controls the switch direction of OUT11 and OUT12.                                                                                                                                                                 |  |  |  |  |

| 35       | PWM1                 | PWM input 1:<br>PWM1 input switches OUT11 and OUT12.                                                                                                                                                                                             |  |  |  |  |

| 33       | DIS1                 | Disable input 1:<br>DIS1 switches OUT11 and OUT12 to tristate                                                                                                                                                                                    |  |  |  |  |

| 8        | /ABE1                | Bidirectional Ability/Enable Pin 1:<br>Open-Drain Output, which is pulled low in case of VDD over- and under-voltage. If the input<br>is pulled to low, all output stages are switched off. /ABE1 belongs to chip 1.                             |  |  |  |  |

| 16       | DIR2                 | Direction input 2:<br>DIR2 pin controls the switch direction of OUT21 and OUT22.                                                                                                                                                                 |  |  |  |  |

| 17       | PWM2                 | PWM input 2:<br>PWM1 input switches OUT21 and OUT22.                                                                                                                                                                                             |  |  |  |  |

| 15       | DIS2                 | Disable input 2:<br>DIS2 switches OUT21 and OUT22 to tristate.                                                                                                                                                                                   |  |  |  |  |

| 26       | /ABE2                | Bidirectional Ability/Enable Pin 2:<br>Open-Drain Output, which is pulled low in case of VDD over- and under-voltage. If the input<br>is pulled to low, all output stages are switched off. /ABE2 belongs to chip 2.                             |  |  |  |  |

| 7        | CF1                  | Current Proportional Feedback output:                                                                                                                                                                                                            |  |  |  |  |

| 25       | CF2                  | The CF pin provides in conjunction with an external resistor an output current, which is proportional to the H-Bridge current. CF1 belongs to OUT11 and OUT12, CF2 to OUT21 and OUT22.                                                           |  |  |  |  |

#### Table 3. L9959T (Two H-Bridge drivers in one package) pinout

| -   |                     |                                                                                                                                                                   |  |  |  |  |  |

|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin | Symbol              | Function                                                                                                                                                          |  |  |  |  |  |

| 3   | SCK1                | Serial clock input:                                                                                                                                               |  |  |  |  |  |

| 21  | SCK2                | This input controls the internal shift register of the SPI.<br>SCK1 belongs to chip 1 and SCK2 to chip 2.                                                         |  |  |  |  |  |

| 5   | SI1                 | Slave in (Serial data input):                                                                                                                                     |  |  |  |  |  |

| 23  | SI2                 | The input receives serial data from the microcontroller.<br>SI1 belongs to chip 1 and SI2 to chip 2.                                                              |  |  |  |  |  |

| 6   | SO1                 | Slave Out (Serial data output):                                                                                                                                   |  |  |  |  |  |

| 24  | SO2                 | The diagnosis data is available via the SPI through this tristate-output.<br>SO1 belongs to chip 1 and SO2 to chip 2.                                             |  |  |  |  |  |

| 4   | SS1                 | Slave Select input:                                                                                                                                               |  |  |  |  |  |

| 22  | SS2                 | The serial data transfer between the device and the micro controller is enabled by pulling the input SS to low level.<br>SS1 belongs to chip 1 and SS2 to chip 2. |  |  |  |  |  |

| EP  | AGND <sup>(4)</sup> | Exposed PAD: connected to AGND                                                                                                                                    |  |  |  |  |  |

Table 3. L9959T (Two H-Bridge drivers in one package) pinout (continued)

1. Pins 13 and 14 are referred to die2 , whereas pins 31 and 32 are referred to die1.

2. Pins 1 is referred to die1 , whereas 19 is referred to die2.

3. Pins 12 is referred to die2, whereas 30 is referred to die1.

4. Pins 10 is referred to die1, whereas 28 is referred to die2.

## 3 Electrical specifications

### 3.1 Absolute maximum ratings

Warning: Stressing the device above the rating listed in the "Absolute maximum ratings" table may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics SURE program and other relevant quality document.

| Symbol                                                                                                                                        | Parameter / Test condition                                                         | Value [DC Voltage] | Unit |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------|------|--|--|--|--|

| V <sub>VS</sub>                                                                                                                               | DC supply voltage                                                                  | -1.0 to +40        | V    |  |  |  |  |

| V <sub>VDD</sub>                                                                                                                              | Stabilized supply voltage, logic supply                                            | -0.3 to 18         | V    |  |  |  |  |

| V <sub>3V3</sub>                                                                                                                              | 3.3 V Controller output                                                            | -0.3 to 4.6        | V    |  |  |  |  |

| C <sub>F</sub>                                                                                                                                | Current feedback output                                                            | -0.3 to 5          | V    |  |  |  |  |

| $\begin{array}{c} V_{\text{SI}}, V_{\text{SCK}}, V_{\text{SS}}, V_{\text{SO}}, \\ V_{\text{DIR}}, V_{\text{PWM}}, V_{\text{DIS}} \end{array}$ | Logic input / output voltage range                                                 | -0.3 to 18         | V    |  |  |  |  |

| M                                                                                                                                             | Output voltage (n=1,2 or 11,12,21,22);<br>V <sub>OUTn</sub> < V <sub>S</sub> + 1 V | -1.0 to 40         | V    |  |  |  |  |

| V <sub>OUTn</sub>                                                                                                                             | Dynamic pulse / t < 500ms;<br>V <sub>OUTn</sub> < V <sub>S</sub> + 2 V             | -2.0 to 40         | V    |  |  |  |  |

| Тј                                                                                                                                            | Operating junction temperature                                                     | -40 to 150         | °C   |  |  |  |  |

| T <sub>stg</sub>                                                                                                                              | Storage temperature                                                                | -55 to 150         | °C   |  |  |  |  |

#### Table 4. Absolute maximum ratings

## 3.2 ESD protection

#### Table 5. ESD protection

| Parameter                                                                                                                | Value             | Unit |

|--------------------------------------------------------------------------------------------------------------------------|-------------------|------|

| All pins versus ground group (AGND, PGND1, PGND2, GND_ABE1, GND_ABE2)                                                    | ±2 <sup>(1)</sup> | kV   |

| Power Output Pins: OUT1, OUT2 or OUT11, OUT12, OUT21, OUT22 versus ground group (AGND, PGND1, PGND2, GND_ABE1, GND_ABE2) | ±4 <sup>(2)</sup> | kV   |

1. HBM according to MIL 883C, Method 3015.7 or EIA/JESD22-A114-A.

2. HBM with all unzipped pins grounded.

## 3.3 Thermal data

| Symbol                | Parameter                                 | PSSO24 | PSSO36 | Unit |

|-----------------------|-------------------------------------------|--------|--------|------|

| R <sub>thj-case</sub> | Thermal resistance junction-to-case (max) | 2      | 3.5    | °C/W |

#### Table 6. Thermal data

## 3.4 Electrical characteristics

The voltages are referred to ground and currents are assumed positive, when the current flows into the pin. 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  18 V, 4.5 V  $\leq$  V<sub>DD</sub>  $\leq$  5.5 V; all outputs open; T<sub>j</sub> = -40 °C to 150 °C, unless otherwise specified.

| Symbol                              | Parameter                                            | Test condition                                                                                                                                                         | Min. | Тур. | Max. | Unit |

|-------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VS                                  | Operating voltage range                              | -                                                                                                                                                                      | 4.5  | -    | 28   | V    |

|                                     | V <sub>S</sub> current consumption in<br>active mode | $V_{DD} = 5 V$ ; $V_S = 5 V$ and $V_S = 18 V$ ;<br>Bridge disabled                                                                                                     | -    | -    | 5    | mA   |

| I <sub>VS</sub>                     |                                                      | $\label{eq:VDD} \begin{array}{l} V_{DD} = 5 \ V; \ V_S = 5 \ V \ \text{and} \\ V_S = 18 \ V; \ f_{OUT} = 2 \ \text{kHz}; \\ I_{OUT} = 0 \ \text{A} \end{array}$        | -    | -    | 6    | mA   |

|                                     |                                                      | $\label{eq:VD} \begin{array}{l} V_{DD}=5 \text{ V};  V_{S}=5 \text{ V} \text{ and} \\ V_{S}=18 \text{ V};  f_{OUT}=10  \text{kHz}; \\ I_{OUT}=0  \text{A} \end{array}$ | -    | -    | 14   | mA   |

|                                     |                                                      | V <sub>DD</sub> = 5 V; V <sub>S</sub> = 28 V;<br>f <sub>OUT</sub> = 10 kHz; I <sub>OUT</sub> = 0 A                                                                     | -    | -    | 14   | mA   |

| I <sub>VS(stby)</sub>               | V <sub>S</sub> current consumption in passive mode   | V <sub>DD</sub> = 0 V                                                                                                                                                  | 0    | -    | 2.5  | mA   |

| V <sub>VS_slew</sub> <sup>(1)</sup> | Slew rate on V <sub>S</sub>                          | -                                                                                                                                                                      | -    | -    | 100  | V/µs |

| V <sub>VS_slew</sub> <sup>(2)</sup> | Slew rate on V <sub>S</sub>                          | -                                                                                                                                                                      | -    | -    | 20   | V/µs |

| V <sub>DD</sub>                     | Operating voltage range                              | -                                                                                                                                                                      | 4.5  | -    | 5.5  | V    |

| I <sub>VDD</sub>                    | V <sub>DD</sub> supply current                       | V <sub>S</sub> = 18 V; V <sub>DD</sub> = 5 V                                                                                                                           | -    | -    | 10   | mA   |

#### Table 7. Supply

1. No change of parameters for VDD-monitoring and in SPI logic

2. No change of parameters

| Symbol                | Parameter                     | Test condition | Min. | Тур. | Max. | Unit |  |  |  |

|-----------------------|-------------------------------|----------------|------|------|------|------|--|--|--|

| V <sub>DDRES</sub>    | Reset active threshold        | -              | 2.8  | -    | 3.4  | V    |  |  |  |

| V <sub>DDPOR</sub>    | Power-on reset threshold      | -              | 3.3  | -    | 3.9  | V    |  |  |  |

| V <sub>DDPORHYS</sub> | Power-on reset hysteresis     | -              | -    | 600  | -    | mV   |  |  |  |

| t <sub>POR</sub>      | Power-on reset extension time | -              | -    | -    | 1    | ms   |  |  |  |

#### Table 8. Power-on reset

| Symbol                     | Parameter                                                                               | Test condition                                                                                | Min.               | Тур. | Max. | Unit  |

|----------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------|------|------|-------|

| V <sub>DD</sub>            | V <sub>DD</sub> monitoring voltage range                                                | -                                                                                             | V <sub>DDPOR</sub> | -    | 18   | V     |

| V <sub>DD_THL</sub>        | Under voltage threshold                                                                 | V <sub>S</sub> = 0 V                                                                          | 4.2                | -    | 4.5  | V     |

| V <sub>DD_THH</sub>        | Over voltage threshold                                                                  | V <sub>S</sub> = 0 V                                                                          | 5.25               | -    | 5.5  | V     |

| t <sub>FIL_OFF</sub>       | Switch-off filtering time                                                               | Cuerenteed by eeen                                                                            | 60                 | -    | 135  | μs    |

| t <sub>FIL_ON</sub>        | Switch-on filtering time                                                                | Guaranteed by scan.                                                                           | 60                 | -    | 135  | μs    |

| V <sub>TEST_THL</sub>      | Under voltage test threshold                                                            | -                                                                                             | 5.25               | -    | 5.5  | V     |

| V <sub>TEST_THH</sub>      | Over voltage test threshold                                                             | -                                                                                             | 4.2                | -    | 4.4  | V     |

| V <sub>DD_MR</sub>         | Full V <sub>DD</sub> supply range                                                       | -                                                                                             | -0.3               | -    | 18   | V     |

| V <sub>DD_SLEW</sub>       | V <sub>DD</sub> slew                                                                    | -                                                                                             |                    | -    | 500  | mV/µs |

| $\Delta V_{DD_THX}$        | Threshold (V <sub>DD_THH</sub> , V <sub>DD_THL</sub> ) shift during vs. inverse current | -                                                                                             | -0.1               | -    | 0.1  | V     |

| V <sub>ABE_INL</sub>       | /ABE input low-level                                                                    | -                                                                                             | -0.3               | -    | 1.65 | V     |

| V <sub>ABE_INH</sub>       | /ABE input high-level                                                                   | -                                                                                             | 3.15               | -    | 18   | V     |

| V <sub>ABE_INHY</sub><br>S | /ABE input hysteresis                                                                   | -                                                                                             | 0.2                | -    | 1.0  | V     |

|                            |                                                                                         | 0 V < V <sub>ABE</sub> < 1.5 V                                                                | 0                  | -    | 60   | μA    |

| I <sub>ABE_IN</sub>        | /ABE input pull-down current                                                            | V <sub>ABE</sub> = 2.1 V, 5 V, 18 V;<br>V <sub>S</sub> = 18 V; V <sub>DD</sub> = 5 V,<br>18 V | 20                 | 40   | 60   | μΑ    |

| V <sub>ABE_OUTL</sub>      | /ABE output low voltage                                                                 | 2.5 V < V <sub>DD</sub> < V <sub>DD_THL</sub> ;<br>I <sub>ABE_OUTL</sub> < 2.5 mA             | 0                  | -    | 1.0  | V     |

| V <sub>ABE_OUTL</sub>      | /ABE output low voltage                                                                 | 2 x V <sub>DD_THL</sub> < V <sub>DD</sub> < 18V;<br>I <sub>ABE_OUTL</sub> < 7.5 mA            | 0                  | -    | 1.2  | V     |

| V <sub>ABE_OUTL</sub>      | /ABE output passive low voltage                                                         | -                                                                                             | 0                  | -    | 1.2  | V     |

| $\Delta I_{ABE}$           | I <sub>ABE</sub> Change during vs. inverse current                                      | -                                                                                             | -100               | -    | 100  | μA    |

### Table 9. V<sub>DD</sub> monitoring

|                     |                      | iei enaci renage chata                   | -    |      |      |      |

|---------------------|----------------------|------------------------------------------|------|------|------|------|

| Symbol              | Parameter            | Test condition                           | Min. | Тур. | Max. | Unit |

| V <sub>UV_OFF</sub> | VS UV threshold      | VS decreasing                            | 3.1  | 3.8  | 4.5  | V    |

| V <sub>UV_ON</sub>  | VS UV threshold      | VS increasing                            | 3.3  | 4.0  | 4.7  | V    |

| V <sub>UV_HYS</sub> | VS UV hysteresis     | V <sub>UV_ON</sub> - V <sub>UV_OFF</sub> | 0.1  | -    | 1    | V    |

| t <sub>FUV</sub>    | VS UV detection time | -                                        | -    | -    | 1.5  | μs   |

Table 10. Undervoltage shutdown

## 3.5 Outputs OUT1 and OUT2

|                              |                                |                                                                            | 5 - = • • • / |      |      |      |

|------------------------------|--------------------------------|----------------------------------------------------------------------------|---------------|------|------|------|

| Symbol                       | Parameter                      | Test condition                                                             | Min.          | Тур. | Max. | Unit |

| r <sub>ONVS</sub><br>OUT1,2  | On-resistance to supply        | V <sub>DD</sub> = 5 V; V <sub>S</sub> = 10 V,<br>I <sub>OUT1,2</sub> = 3 A | -             | -    | 315  | mΩ   |

| r <sub>ONGND</sub><br>OUT1,2 | On-resistance to PGND          | V <sub>DD</sub> = 5 V; V <sub>S</sub> = 10 V,<br>I <sub>OUT1,2</sub> = 3 A | -             | -    | 225  | mΩ   |

|                              | Switched-off output current of | V <sub>DD</sub> = 5 V; V <sub>S</sub> = 13 V;<br>V <sub>OUT</sub> = 0 V    | -200          | -    | -    | μA   |

| ILEAK                        | OUT1,2                         | $V_{DD} = 5 \text{ V}; \text{ V}_{S} = 13 \text{ V};$<br>$V_{OUT} = V_{S}$ | -             | -    | 200  | μΑ   |

#### Table 11. On-resistance (4.5 V < V<sub>S</sub> < 28 V)

#### Table 12. Power output switching times (8 V < $V_S$ < 18 V)

| Symbol                            | Parameter                                                                                             | Test condition                                                                       | Min.         | Тур. | Max.     | Unit |

|-----------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------|------|----------|------|

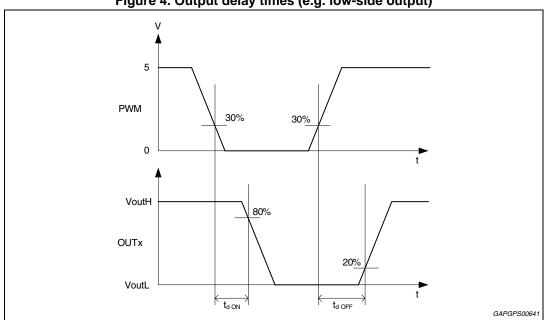

| t <sub>d ON</sub>                 | Output delay time driver on                                                                           | -                                                                                    | -            | -    | 6        | μs   |

| t <sub>d OFF</sub>                | Output delay time driver off                                                                          | -                                                                                    | -            | -    | 16       | μs   |

| t <sub>d dis</sub> <sup>(1)</sup> | Disable delay time                                                                                    |                                                                                      | -            | -    | 12.5     | μs   |

| t <sub>d pwon</sub>               | Power-on delay time                                                                                   | Guaranteed through<br>scan                                                           | -            | -    | 1        | ms   |

| t <sub>d en</sub>                 | Enable delay time                                                                                     |                                                                                      | -            | -    | 50       | μs   |

| dl <sub>OUT</sub> /dt             | Current slew rate                                                                                     | -                                                                                    | -            | 1.6  |          | A/µs |

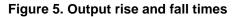

| dV <sub>OUTHS</sub> /dt           | Output rise/fall slew-rate high-side<br>low selected with bit SR = 0<br>fast selected with bit SR = 1 |                                                                                      | 0.975<br>2.8 | -    | 2.7<br>8 | V/µs |

| dV <sub>rOUTLS</sub> /dt          | Output rise slew-rate low-side valid only after the toggling of DIR input                             | $V_{DD} = 5 V; V_{S} = 14 V R_{LOAD1,2} = 2.6 \Omega (8 V_{S}), 6 \Omega (18 V_{S})$ | 0.975        | -    | 2.7      | V/µs |

| dV <sub>fOUTLS</sub> /dt          | Output fall slew-rate low-side                                                                        |                                                                                      | 2.5          | 4    | 8        | V/µs |

| f <sub>pwmmax</sub>               | PWM input frequency                                                                                   | -                                                                                    | -            | -    | 11       | kHz  |

1. Driven by /ABE or DIS input.

The slew-rates (dV<sub>OUT</sub>/dt1) are defined by dV (voltage difference 20% - 80%) divided by the rise-/fall times (t<sub>r</sub>/t<sub>f</sub> see Figure 5: Output rise and fall times).

Figure 4. Output delay times (e.g. low-side output)

Figure 7. Output disable and enable time (DIS Input)

#### Table 13. Current feedback (CF)

| Symbol                         | Parameter                       | Test condition                                                                                       | Min. | Тур.  | Max. | Unit |

|--------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------|------|-------|------|------|

|                                | <sup>(1)</sup> CF voltage range | $V_{S} > 6.5 V$ , OUTx = 0 A,<br>T <sub>J</sub> = -40 °C; Current<br>level 2,3,4                     | 0.01 | 0.05  | 0.20 | V    |

| V <sub>CF</sub> <sup>(1)</sup> |                                 | V <sub>S</sub> > 6.5 V, OUTx =<br>250mA, T <sub>J</sub> = 130 °C;<br>Current level 2,3,4             | 0.04 | 0.275 | 0.5  | V    |

| VCF V                          |                                 | $V_{S} > 6.5 V$ , OUTx = 0.4 *<br>$I_{clx}$ , $T_{J} = 130 °C$ ; Current<br>level 2,3,4              | 1.71 | 1.80  | 1.89 | V    |

|                                |                                 | $V_S > 6.5 V$ , OUTx = I <sub>max</sub> ,<br>T <sub>J</sub> = -40°C to 150°C;<br>Current level 2,3,4 | 3.82 | 4.5   | 5.18 | V    |

| R <sub>CF</sub> <sup>(2)</sup> | CF resistor range               | -                                                                                                    | -    | 5.1   | -    | kΩ   |

| I <sub>OFFSET</sub>            | CF offset current               | -                                                                                                    | -    | 10    | -    | μΑ   |

1. Measured at a 5.1k resistor between CF and GND ( $R_{CF}$ ). Levels see Table 33 Current Level (CONFIG\_REG).

2. Defined by design, not tested.

Note: This signal has an individual error ±5 % in each of the three currents levels, at trimming temperature of 130 °C. Additional an individual error ± 10 % in each of the three current levels over temperature and aging. So the maximum error is of ± 15 % in each of the three current levels. The offset and the gain errors may be different in each current level. The adjustment is done at 130 °C and compensates the error between 0.3 \* Imax to 0.6 \* Imax.

| 5                                    |                                       |                        |                           |      |                            |      |

|--------------------------------------|---------------------------------------|------------------------|---------------------------|------|----------------------------|------|

| Symbol                               | Parameter                             | Test condition         | Min.                      | Тур. | Max.                       | Unit |

| I <sub>CL2</sub>   <sup>(1)</sup>    | Current limit <sub>2</sub>            |                        | 4.25                      | 5    | 5.75                       | А    |

| I <sub>CL3</sub>   <sup>(1)</sup>    | Current limit <sub>3</sub>            | R <sub>CF</sub> = 5.1k | 5.6                       | 6.6  | 7.6                        | А    |

| I <sub>CL4</sub>   <sup>(1)</sup>    | Current limit <sub>4</sub>            |                        | 7.3                       | 8.6  | 9.9                        | А    |

| I <sub>HYS2-4</sub>   <sup>(1)</sup> | Current limit hysteresis <sub>1</sub> | -                      | -5%<br>ICL <sub>2-4</sub> | -    | -10%<br>ICL <sub>2-4</sub> | А    |

| t <sub>b</sub>                       | Blanking time                         | Guaranteed through     | 8                         | 11   | 15                         | μs   |

| t <sub>trans</sub>                   | Time between two transient            | scan.                  | 90                        | -    | 130                        | μs   |

#### Table 14. Current limiting

Programmable current levels see Table 33 Current Level (CONFIG\_REG). Measured using a 5.1k resistor between CF and GND (R<sub>CF</sub>).

| Symbol                               | Parameter                                     | Test condition        | Min. | Тур. | Max. | Unit |

|--------------------------------------|-----------------------------------------------|-----------------------|------|------|------|------|

| I <sub>OC2_LS</sub> I <sup>(1)</sup> | Low side over current threshold <sub>2</sub>  | $V_{DD} = 5 V$        | 4.9  | -    | 8.2  | А    |

| I <sub>OC3_LS</sub>   <sup>(1)</sup> | Low side over current threshold <sub>3</sub>  | V <sub>DD</sub> = 5 V | 6.7  | -    | 11.1 | А    |

| I <sub>OC4_LS</sub>   <sup>(1)</sup> | Low side over current threshold <sub>4</sub>  | V <sub>DD</sub> = 5 V | 8.4  | -    | 14   | А    |

| I <sub>OC2_HS</sub> I <sup>(1)</sup> | High side over current threshold <sub>2</sub> | V <sub>DD</sub> = 5 V | 5.5  | -    | 9.2  | А    |

| I <sub>OC3_HS</sub>   <sup>(1)</sup> | High side over current threshold <sub>3</sub> | V <sub>DD</sub> = 5 V | 6.9  | -    | 11.5 | А    |

| I <sub>OC4_HS</sub>   <sup>(1)</sup> | High side over current threshold <sub>4</sub> | V <sub>DD</sub> = 5 V | 8.6  | -    | 14.4 | А    |

| I <sub>TRACK-1</sub> <sup>(1)</sup>  | I <sub>OC1_LS</sub>   -  I <sub>CL1_LS</sub>  | V <sub>DD</sub> = 5 V | 0.4  | -    | 5.5  | А    |

| I <sub>TRACK-2</sub> <sup>(1)</sup>  | I <sub>OC2_LS</sub>   -  I <sub>CL2_LS</sub>  | V <sub>DD</sub> = 5 V | 0.4  | -    | 5.5  | А    |

| I <sub>TRACK-3</sub> <sup>(1)</sup>  | I <sub>OC3_LS</sub>   -  I <sub>CL3_LS</sub>  | $V_{DD} = 5 V$        | 0.4  | -    | 5.5  | А    |

| I <sub>TRACK-4</sub> <sup>(1)</sup>  | I <sub>OC4_LS</sub>   -  I <sub>CL4_LS</sub>  | V <sub>DD</sub> = 5 V | 0.4  | -    | 5.5  | А    |

| t <sub>DF</sub>                      | Delay time for fault detection                | -                     | 1    | 2    |      | μs   |

| t <sub>DF_off</sub>                  | Switch-off delay time                         | -                     |      |      | 6    | μs   |

| t <sub>DF_del</sub>                  | Delayed switch-off time                       | -                     | 20   |      | 200  | μs   |

## Table 15. Over-current detection (8 V < V<sub>S</sub> < 18 V)

1. Programmable current levels see Table 33 Current Level (CONFIG\_REG).

#### Table 16. Openload detection

If the value of the connected load is below 2.5 k $\Omega$ , no Open Load is detected; if the value of the connected load is more than 50 k $\Omega$ , Open Load is detected.

If the load is in the range between (2.5 ... 50) k $\Omega$ , the Open Load diagnosis is not reliable.

| Symbol               | Parameter                                   | Test condition     | Min. | Тур. | Max. | Unit |

|----------------------|---------------------------------------------|--------------------|------|------|------|------|

| R <sub>OL</sub>      | Openload detection threshold                | -                  | 5    | -    | 50   | kΩ   |

| t <sub>DIAGOL</sub>  | Openload diagnosis enable<br>delay          | Guaranteed through | 100  | -    | 150  | ms   |

| t <sub>DIAGOL1</sub> | Openload diagnosis filter time <sub>1</sub> | scan.              | 2.4  | -    | 3.6  | ms   |

| t <sub>DIAGOL2</sub> | Openload diagnosis filter time <sub>2</sub> |                    | 200  | -    | 300  | μs   |

#### Table 17. Retest delay

| Symbol                    | Parameter                                | Test condition           | Min. | Тур. | Max. | Unit |

|---------------------------|------------------------------------------|--------------------------|------|------|------|------|

| t <sub>delay</sub> retest | Retest delay for failures: SCB, SCG, SCL | Guaranteed through scan. | 290  | 350  | 410  | μs   |

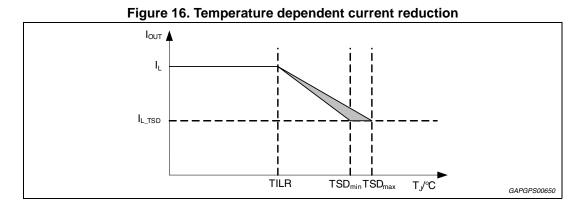

## **3.6** Temperature dependent current reduction

| Symbol                            | Parameter                                        | Test condition           | Min. | Тур. | Max. | Unit |

|-----------------------------------|--------------------------------------------------|--------------------------|------|------|------|------|

| $ I_{L_{TSD}} $                   | Current limit at T <sub>SD</sub>                 | -                        | 1.4  | 2.5  | 3.6  | А    |

| T <sub>ILR</sub>                  | Start of temperature dependent current reduction | -                        | 150  | 165  | -    | °C   |

| T <sub>SD</sub>                   | Thermal shut-down                                | -                        | 175  | -    | -    | °C   |

| T <sub>SD</sub> -T <sub>ILR</sub> | Range of temperature dependent current reduction | -                        | 20   | 25   | 30   | °C   |

| T <sub>fTSD</sub>                 | Thermo-shut-down detection filter time           | Guaranteed through scan. | 6    | -    | 18   | μs   |

Table 18. Temperature dependent current reduction

Note: see also Figure 16: Temperature dependent current reduction.

## 3.7 Free-wheeling diodes

| Symbol                         | Parameter                                 | Test condition         | Min. | Тур. | Max. | Unit |

|--------------------------------|-------------------------------------------|------------------------|------|------|------|------|

| U <sub>D</sub>                 | Free-wheeling diode forward voltage       | I <sub>OUT</sub> = 3 A | -    | -    | 2    | V    |

| T <sub>it</sub> <sup>(1)</sup> | Free-wheeling diode reverse recovery time | -                      | -    | -    | 100  | ns   |

1. Not subject to production test; specified by design.

## 3.8 SPI / logic electrical characteristics

The voltages are referred to ground and currents are assumed positive, when the current flows into the pin. 4.5 V  $\leq$  V<sub>S</sub>  $\leq$  18 V, 4.5 V  $\leq$  V<sub>CC</sub>  $\leq$  5.5 V; all outputs open; T<sub>j</sub> = -40 °C to 150 °C, unless otherwise specified.

| Symbol                             | Parameter                                                                    | Test condition                                   | Min     | Тур | Мах     | Unit |

|------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------|---------|-----|---------|------|

| Inputs: SI,                        | SS, SCK DIR, PWM                                                             |                                                  |         |     |         |      |

| V <sub>IL</sub>                    | Input voltage low-level                                                      | put voltage low-level V <sub>DD</sub> = 5 V -0.3 |         | -   | 0.75    | V    |

| V <sub>IH</sub>                    | Input voltage high-level                                                     | V <sub>DD</sub> = 5 V                            | 1.75    | -   | VDD+0.3 | V    |

| V <sub>IHYS</sub>                  | Input hysteresis                                                             | V <sub>DD</sub> = 5 V                            | 0.2     | -   | 1.0     | V    |

| R <sub>PUin</sub>                  | Input pull-up resistor                                                       | V <sub>DD</sub> = 5 V                            | 50      | -   | 250     | kΩ   |

| I <sub>INx</sub>                   | PWM, DIR input current                                                       | V <sub>INx</sub> > 3.0V                          | -5      | -   | 5       | μA   |

| C <sub>Slin</sub> <sup>(1)</sup>   | SI input capacitance                                                         | -                                                | -       | -   | 10      | pF   |

| C <sub>SCKin</sub> <sup>(1)</sup>  | SCK input capacitance                                                        | -                                                | -       | -   | 10      | pF   |

| C <sub>SSin</sub> <sup>(1)</sup>   | SS Input Capacitance                                                         | -                                                | -       | -   | 15      | pF   |

| C <sub>DIR, PWMin</sub>            | DIR, PWM input capacitance                                                   | -                                                | -       | -   | 20      | pF   |

| Input: DIS                         |                                                                              |                                                  |         |     |         |      |

| R <sub>DISPU</sub>                 | Pull-up resistor                                                             | 0 V < V <sub>DIS</sub> < 2.1 V                   | 10      | -   | 45      | kΩ   |

| I <sub>DISx</sub>                  | DIS input current                                                            | V <sub>DIS</sub> > 3 V                           | -5      | -   | 5       | μA   |

| C <sub>DIS in</sub> <sup>(1)</sup> | DIS input capacitance                                                        | -                                                | -       | -   | 20      | pF   |

| tDIS                               | DIS pulse width                                                              | -                                                | 0.5     | 1   | 1.5     | μs   |

| Input pin d                        | isturbance (SI, SS, SCK DIR, F                                               | PWM,DIS)                                         | 1 1     |     |         |      |

| $\Delta Vx_HL$                     | Change of $V_{IH}$ and $V_{IL}$ during inverse current on $V_{\rm S}$        |                                                  | -0.1    | -   | 0.1     | V    |

| ∆ISx                               | Change of input current of SPI<br>input pins during inverse<br>current on VS | Not subjected to test in<br>production.          | -100    | -   | 100     | μA   |

| Output: SO                         | )                                                                            |                                                  |         |     |         |      |

| V <sub>SOL</sub>                   | Output voltage low level                                                     | I <sub>OL</sub> = 2 mA,                          | 0       | -   | 0.4     | V    |

| V <sub>SOH</sub>                   | Output voltage high level                                                    | I <sub>OH</sub> = -2 mA                          | VDD-0.5 | -   | VDD     | V    |

| $\mathrm{SR}_{\mathrm{SO}}^{(1)}$  | Slew rate                                                                    | C <sub>LOAD</sub> = 200 pF                       | 0.3     | -   | 0.6     | V/ns |

| I <sub>SOLK</sub>                  | Tristate leakage current                                                     | V <sub>SS</sub> = V <sub>DD</sub>                | -10     | -   | 10      | μA   |

| C <sub>SO out</sub> <sup>(1)</sup> | SO output capacitance                                                        | -                                                | -       | -   | 10      | pF   |

|                                    | disturbance (SO)                                                             |                                                  | · 1     |     | · •     |      |

| $\Delta I_{SOLK}$                  | Change of I <sub>SOLK</sub> during inverse Current on VS                     | -                                                | -100    | -   | 100     | μA   |

#### Table 20. Inputs: SI, SS, SCK, DIR, DIS and PWM; Output: SO

1. Not measured in production test. Parameter guaranteed by design.

#### **Electrical specifications**

| Symbol            | Parameter         | Test condition                                    | Min. | Тур. | Max. | Unit |

|-------------------|-------------------|---------------------------------------------------|------|------|------|------|

| t <sub>cyc</sub>  | Cycle time        | -                                                 | 490  | -    | -    | ns   |

| t <sub>lead</sub> | Enable lead time  | -                                                 | 300  | -    | -    | ns   |

| t <sub>lag</sub>  | Enable lag time   | -                                                 | 150  | -    | -    | ns   |

|                   |                   | SCK = 2 V; SO = 0.2 V;<br>C <sub>L</sub> = 40 pF  | 40   | -    | -    | ns   |

| t <sub>v</sub>    | Data valid        | SCK = 2 V; SO = 0.2 V;<br>C <sub>L</sub> = 200 pF | 150  | -    | -    | ns   |

|                   |                   | SCK = 2 V; SO = 0.2 V;<br>C <sub>L</sub> = 350 pF | 230  | -    | -    | ns   |

| t <sub>su</sub>   | Data setup time   | -                                                 | 40   | -    | -    | ns   |

| t <sub>h</sub>    | Data hold time    | -                                                 | 40   | -    | -    | ns   |

| t <sub>dis</sub>  | Disable time      | -                                                 | 0    | -    | 100  | ns   |

| t <sub>dt</sub>   | Transfer delay    | -                                                 | 300  | -    | -    | ns   |

| t <sub>dld</sub>  | Disable lead time | -                                                 | 250  | -    | -    | ns   |

| t <sub>dlg</sub>  | Disable lag time  | -                                                 | 250  | -    | -    | ns   |

| t <sub>acc</sub>  | Access time       | -                                                 | 8.35 | -    | -    | μs   |

| Table 21 | . Dynamic charac | teristics |

|----------|------------------|-----------|

|----------|------------------|-----------|

### Figure 8. SPI timing information

## 4 Application information

### 4.1 Power stage switching behavior

The L9959 output stages can either be controlled by the pins PWM and DIR or by their corresponding SPI registers (SPWM and SDIR: see *Table 32: Configuration register* (*CONFIG\_REG*)). The SPI bit MUX in the configuration register (CONFIG\_REG) determines this. If the power stages are disabled by /ABE or DIS, this bit is reset and the pins PWM and DIR control the outputs.

The active free-wheeling, in which the body diode is actively shorted by its associated Power-MOS, can be disabled by the bit FW in the configuration register. By default, active free-wheeling is enabled.

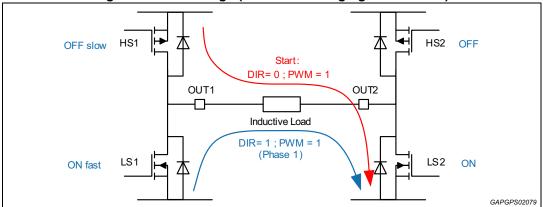

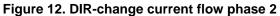

The device minimizes electro-magnetic emission by switching the high-side and low-side drivers in a special sequence. Two cases are distinguished: The PWM-mode, during which the current direction does not change and the direction switch using the DIR, which changes the current direction (see *Figure 9*, *Figure 11* and *Figure 12*).

#### 4.1.1 PWM mode (same current direction)

The PWM input pin switches the high-/low-side output of the half-bridge, which is selected by the DIR pin. DIR = '0': OUT1 is switched, DIR = '1': OUT2 is switched.

PWM = '0': Switched low-side is on, PWM = '1': Switched high-side is on.

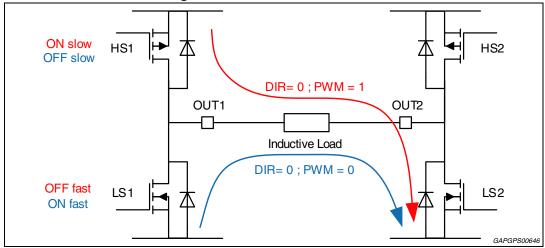

Figure 9. PWM mode current flow

During PWM mode the high-side (e.g. *Figure 9* HS1) output is switched off with a slow slew rate until it is off and the low-side body-diode has taken over the entire current. Then the associated low-side transistor (e.g. *Figure 9* LS1) is turned on with a fast slope to reduce the voltage across the device and to minimize the power.

The output is pulled to high voltage, by first turning off the low-side driver with a fast slew rate and, after it is off, the high-side driver is switched on by a slow one (e.g. *Figure 9* LS1, HS1).

This assures, that the voltage and current change over the body diode is done smoothly, reducing the electromagnetic emission.

Figure 11. DIR-change (current is changing its direction)

22/43

Figure 13. DIR-change output voltage

The first part of the sequence is identical to the PWM-mode (s.a.). After this has been finished and the associated low-side driver is on (e.g. *Figure 11* LS1), in phase 1 the other low-side driver is turned on (e.g. *Figure 11* LS2). Then in phase 2 the low-side output of OUT2 is switched-off slowly and the current through the load is taken over by the body-diode of the high-side (e.g. *Figure 12* HS2). Depending on the inductance of the load, the current vanishes more or less quickly. After the low-side driver is turned off, the high-side is switched on with a slow slew-rate.

This assures, that direction switch occurs while the current over the load has vanished, which reduces the electromagnetic emission.

### 4.2 Protection and monitoring

All errors are confirmed after their occurrence by accessing the error condition after time td<sub>elay\_retest</sub> a second time. Only after the error is confirmed it is entered into the diagnosis register 1 (DIA\_REG1), and the device is disabled and no further diagnosis is run. The device can be enabled again by following actions: Power-on reset, disabling or enabling the device using the pins /ABE or DIS (e.g. disabling - enabling sequence). The diagnosis registers can be cleared by sending a reset command by SPI (STATCON\_REG) to either diagnosis register 1 (DIA\_REG1) or 2 (DIA\_REG2). The bit1 (Reset) of the CONFIG\_REG if forced to zero is resetting both the device registers configuration and diagnosis registers to default but is not able to restart the device. In order to restart IC is necessary to force a transition LOW/HIGH/LOW on DIS pin or a transition HIGH/LOW/HIGH on /ABE pin.

The errors in the diagnosis register 1 (DIA\_REG1) are transferred to the diagnosis register 2 by setting the bit DIACLR1 in the status and configuration register (STATCON\_REG) or by using the enabling -disabling sequence on /ABE or DIS. This will also clear the diagnosis register 1.

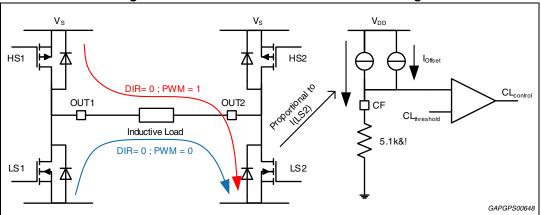

#### 4.2.1 Current feedback

A feedback current signal is provided at pin CF (Current Feedback). This current is proportional to the current in the H-Bridge, but does not change its direction. It is measured in the low-side transistor, which is not switched by PWM. This is determined by the input DIR or the SDIR register respectively. Therefore, the direction of the current can be seen from this direction signal. Whenever the current direction changes, the current feedback signal is blanked. In *Table 13: Current feedback (CF)* the CF behavior over an external resistor of 5.1k Ohm is specified. The current out of CF consists of a static offset current and a current proportional to the current in the select low-side transistor. The voltage at pin CF scales with the resistor at this pin.

*Figure 14* Current Feedback and Current Limiting shows the current feedback in case the OUT1 is controlled by PWM (DIR = 0). In this case, the current is measured through low-side 2. If the direction is inverted, the current is measured through low-side 1.

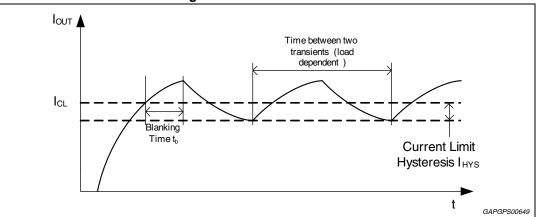

#### 4.2.2 Current limitation

The H-Bridge output current can be limited to three different values (see *Table 14: Current limiting*). If the current reaches the current limiting threshold ICL, the output driver is switched off after the blanking time  $t_b$ , and switched on again after the current dropped below the lower current limit hysteresis threshold ( $I_{CL} - I_{HYS}$ ). The current limiting thresholds can be adjusted using the resistor at pin CF. The values in *Table 14* refer to a 5.1k Ohm external resistor. The current limiting threshold can be calculated by (4.5V/R<sub>CF</sub> -  $I_{OFFSET}$ ) \* ( $I_{CLx}$ \*5.1k/4.45V) from *Table 14* and  $I_{OFFSET}$ =10µA (typical). R<sub>CF</sub> is the resistor used at pin CF. The overcurrent threshold is not changed by RCF (see *Table 15*). The current limitation is active as long as the output driver is switched on. The current limitation is also active during free-wheeling. The information that the device is in current limitation is stored in the diagnosis register 2 (DIA\_REG2).

#### 4.2.3 Temperature dependent current reduction

If the device reaches the temperature TILR, the current will be reduced (see *Figure 16: Temperature dependent current reduction*). If the temperature reaches the temperature shutdown threshold, the outputs are switched off. The current limitation information is written into the diagnosis register 2 (DIA\_REG2).

#### 4.2.4 Short to battery (SCB) and short to Ground (SCG)

While the power stages are on, the current through them is monitored. If the output current reaches the current limit IL, the output is switched off after the blanking time  $t_b$ . In case the current reaches the limit  $I_{OC}$  during this time, a short to battery (SCB) on low-sides or a short to ground (SCG) on high-sides is diagnosed, the affected output driver is switched off immediately, the not affected one after the time  $t_{DF\_del}$ . In order to confirm this error, the outputs are turned on again. Only if the error is then again detected, it is entered into the diagnosis register (DIA\_REG1) and the device is disabled. Otherwise, the event is disregarded.

The three different over-current limits are related to the programmable current limitation, which can be programmed into the SPI register (*Table 32: Configuration register* (*CONFIG\_REG*)). The over-current limits are independent of the resistor at pin CF.

#### 4.2.5 Short circuit over load (SCL)

Short circuit over load (SCL) is diagnosed by a retest sequence after a short to battery (SCB) or a short to ground (SCG) has been detected and confirmed by a retry on the switched-on high-side and low-side driver. Then after the time  $t_{SCLretest}$ , the opposite driver is switched off (i.e. the high-side in case of a short to battery on the low-side and vice versa). If the failure then disappears, a short over load (SCL) is detected.

The error is only entered into the diagnosis register and the device is disabled, if it is confirmed.

#### 4.2.6 Open load (OL)

Open load can either be detected in active mode or while the output drivers are in tri-state condition, disabled by DIS or /ABE. Open load in active mode is enabled using the OLDA in the configuration register (CONFIG\_REG).

#### Open load in active mode

The open load condition can only be diagnosed if an inductive load is used. In normal operation, the output free wheels via the built-in diodes below ground, if the high-side output driver is switched-off. If the output does not go below ground, an open load is detected.

#### Open load in inactive mode

In inactive mode the open load condition is detected by applying a pull-down current ( $I_{PD}$ ) to both outputs. A pull-up current is generated at one output to compensate these two output currents. If the pull-up current is in the range of one pull-down current, an open load is diagnosed. If the load is connected, the pull up current is in the range of the sum of both pull-down currents. An open load is detected, if the load resistance is above the open load resistance threshold, no open load is detected, if it is below this threshold ( $R_{OL}$ ). After the outputs are disabled, it takes the time  $t_{DIAGOL}$  until the open load diagnostic can be enabled. The open load settling time to reach the correct pull up current is  $t_{diagOL1}$ , the open load filter time is  $t_{diagOL2}$ .

### 4.3 VS-undervoltage

VS is monitored for under-voltage. If VS goes below the VS-undervoltage threshold, the outputs are switched to tristate after the time  $t_{FUV}$ .

### 4.4 Inverse current at V<sub>S</sub>

An inverse current of maximum 5 A, which decreases during a period of max 250 ms out of the device at VS does not lead to any destruction. After the exposure to such an inverse current the device returns to the specified functionality.

### 4.5 /ABE pin

/ABE (Ability/Enable) is a bidirectional pin, with an open-drain output. In normal operating condition, this pin is pulled up by an external resistor. If /ABE is set to low, the outputs enter tristate mode.

/ABE can be used to switch off the outputs quickly by an external signal. It is especially possible to connect the /ABE pins of several devices together, so all of them can be disabled in case one detects an error, which is flagged by the /ABE-pin.

### 4.6 VDD-monitor

$V_{DD}$  is monitored for under- and over-voltage referenced to  $GND_{ABE}$ . If  $V_{DD}$  goes below  $V_{DD\_THL}$  or above  $V_{DD\_THH}$ , /ABE is pulled to low and the outputs enter tristate mode after the time  $t_{FIL\_OFF}$ . The VDD-monitoring state is stored into the status and control register (STACON\_REG). If VDD increases above  $V_{DD\_THL}$ , /ABE is pulled to high after the filter time  $t_{FIL\_ON}$ . The SPI remains functional as long as  $V_{DD}$  is above the power-on reset threshold.

The behavior of the pin /ABE and the output stages after VDD goes below VDD\_THH from VDD-overvoltage is determined by bit CONFIG 0 in the status and configuration register (STATCON):

CONFIG0 = 1: /ABE is latched and the outputs remain in tristate

CONFIG0 = 0: /ABE goes to inactive and the output stages are enabled after the filtering time  $t_{FIL_ON}$ .

### 4.7 VDD-monitor test

VDD-Monitor blocks can be tested in the application via SPI. During this test, the output stages are still switched off in case of over- and under-voltage.

#### Upper threshold

The over-voltage threshold can be reduced using the configuration registers 1 and 2 (CONFIG1 and CONFIG2) in the status and control register (STACON\_REG) to V<sub>TEST\_THH</sub> (see T*Table 34: Status and configuration register (STATCON\_REG)*). Since V<sub>TEST\_THH</sub> is below the normal VDD voltage, the status bit STATUS0 shows a VDD overvoltage.

#### Lower threshold

The under-voltage threshold can be increased to  $V_{TEST_THL}$  using CONFIG1 and CONFIG2 in the STATCON register. Since the VDD voltage is below  $V_{TEST_THL}$ , the resulting VDD-undervoltage resets STATUS0.

After leaving the VDD-monitor test mode, the bits in the STACON register return to their normal state.

#### 4.8 **Power-on reset**

At power-on, while VDD increases, the internal registers are cleared and the outputs are set to tristate at the reset-active voltage  $V_{DDRES}$ . Above the power-on reset threshold  $V_{DDPOR}$  the device starts to operate after the time  $t_{POR}$ . If VDD drops below  $V_{DDPOR}$ , the device enters its reset state, i.e. all internal registers are cleared and the outputs are set to tristate.

| V <sub>S</sub> [V] | V <sub>DD</sub> [V]      | Functional state                                                                                   |  |  |  |  |  |  |

|--------------------|--------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 28 - 40            | 0 – 18                   | No damage to the device, no functional behavior guaranteed                                         |  |  |  |  |  |  |

| 4.5 - 6.5          | 4.5 - 5.5                | Device functional, Current Feedback accuracy reduced                                               |  |  |  |  |  |  |

| 6.5 – 28           | 4.5 - 5.5                | Device functional                                                                                  |  |  |  |  |  |  |

| 4.5 – 28           | 4.0 – 4.5 5.5 - 18       | Device functional, but power-outputs tristate by VDD-monitor, /ABE pulled to low, SPI functional   |  |  |  |  |  |  |

| 0 - 4.5 4.5 - 28   | VDD <sub>POR</sub> – 4.5 | Device in reset mode, SPI functional, power-outputs tristate, /ABE pulled to low                   |  |  |  |  |  |  |

| 0 - 4.5 4.5 - 28   | 2.5 - VDD <sub>POR</sub> | Device in reset mode, SPI reset, power-outputs tristate, /ABE tristate                             |  |  |  |  |  |  |

| 0 - 4.5            | 4.5 – 5.5                | Device functional, outputs are tristate by Vs-<br>undervoltage                                     |  |  |  |  |  |  |

| 0 - 4.5            | 4.0 – 4.5 5.5 - 18       | Device functional, outputs are tristate by Vs-<br>undervoltage and VDD-monitor, /ABE pulled to low |  |  |  |  |  |  |

Note: All voltages are nominal. Please refer to Section 3: Electrical specifications for their specified values.

## 5 SPI functional description

### 5.1 General description

The SPI communication is based on a Serial Peripheral Interface structure using SS (SPI Select), SI (Serial Data In), SO (Serial Data Out) and SCK (Serial Clock) signal lines. The first data at pin SI is latched into the device with the first falling edge of the clock SCK after the clock has changed from low to high, which is the second edge after SPI-Select has been pulled to low. Therefore the  $\mu$ C protocol is according to CPOL = 0 and CPHA = 1 (see *Figure 8: SPI timing information*).

#### 5.1.1 SPI select (SS)