Contents L6234

### **Contents**

| 1 | Block diagram 3                        |

|---|----------------------------------------|

| 2 | Pin connections                        |

| 3 | Thermal data 5                         |

| 4 | Maximum ratings 6                      |

|   | 4.1 Recommended operating conditions 6 |

| 5 | Electrical characteristics             |

| 6 | Circuit description                    |

| 7 | Typical characteristics                |

| 8 | Mechanical data                        |

| 9 | Revision history                       |

L6234 Block diagram

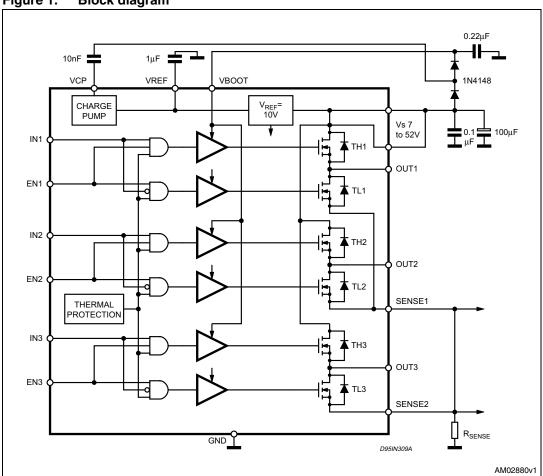

## 1 Block diagram

Figure 1. Block diagram

Pin connections L6234

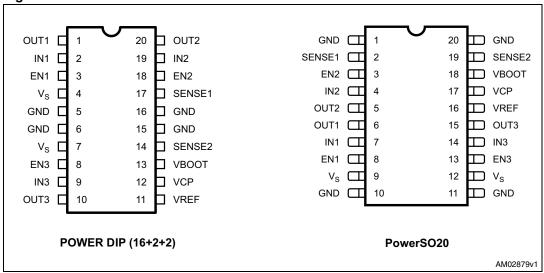

#### 2 Pin connections

Figure 2. Pin connections

Table 2. Pin functions

| PowerDIP     | PowerSO20     | Name                                                                                                    | Function                                                                                                                        |  |

|--------------|---------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|

| 1            | 6             | OUT 1                                                                                                   |                                                                                                                                 |  |

| 20           | 5             | OUT 2                                                                                                   | Output of the channels 1/2/3.                                                                                                   |  |

| 10           | 15            | OUT 3                                                                                                   |                                                                                                                                 |  |

| 2            | 7             | IN 1                                                                                                    | Logic input of channels 1/2/3. A logic HIGH level (when the                                                                     |  |

| 19           | 4             | IN 2                                                                                                    | corresponding EN pin is HIGH) switches ON the upper DMOS                                                                        |  |

| 9            | 14            | IN 3                                                                                                    | Power Transistor, while a logic LOW switches ON the corresponding low side DMOS Power.                                          |  |

| 3            | 8             | EN 1                                                                                                    |                                                                                                                                 |  |

| 18           | 3             | EN 2                                                                                                    | Enable of the channels 1/2/3. A logic LOW level on this pin switches off both power DMOS of the related channel.                |  |

| 8            | 13            | EN 3                                                                                                    | switches on both power DMOS of the related channel.                                                                             |  |

| 4,7          | 9, 12         | Vs                                                                                                      | Power supply voltage.                                                                                                           |  |

| 14           | 19            | SENSE2 A sense resistor connected to this pin provides feedback motor current control for the bridge 3. |                                                                                                                                 |  |

| 17           | 2             | SENSE1                                                                                                  | A sense resistor connected to this pin provides feedback for motor current control for the bridges 1 and 2.                     |  |

| 11           | 16            | VREF                                                                                                    | Internal voltage reference. A capacitor connected from this pin to GND increases the stability of the Power DMOS drive circuit. |  |

| 12           | 17            | VCP                                                                                                     | P Bootstrap oscillator. Oscillator output for the external charge pump.                                                         |  |

| 13           | 18            | VBOOT                                                                                                   | Overvoltage input to drive the upper DMOS                                                                                       |  |

| 5,6<br>15,16 | 1,10<br>11,20 | GND                                                                                                     | Common ground terminal. In PowerDIP and SO packages these pins are used to dissipate the heat forward the PCB.                  |  |

577

L6234 Thermal data

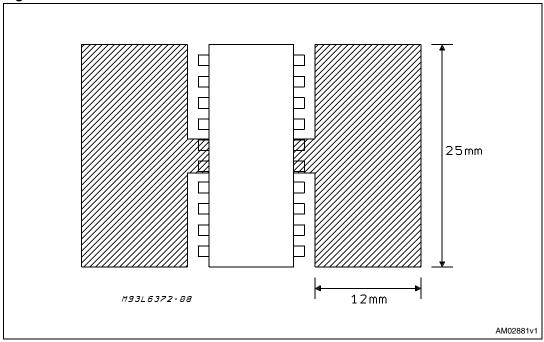

#### 3 Thermal data

Table 3. Thermal data

| Symbol                 | Parameter                                                | DIP16+2+2         | PowerSO20 | Unit |

|------------------------|----------------------------------------------------------|-------------------|-----------|------|

| R <sub>th j-pin</sub>  | Thermal resistance, junction to pin                      | 12 <sup>(1)</sup> | _         | °C/W |

| R <sub>th j-amb1</sub> | Thermal resistance, junction to ambient                  | 40 <sup>(2)</sup> | 1         | °C/W |

| R <sub>th j-amb2</sub> | Thermal resistance, junction characteristics) to ambient | 50 <sup>(3)</sup> | -         | °C/W |

| R <sub>th j-case</sub> | Thermal resistance junction-case                         | _                 | 1.5       | °C/W |

- 1. The thermal resistance is referred to the thermal path from the dissipating region on the top surface of the silicon chip, to the points along the four central pins of the package, at a distance of 1.5 mm away from the stand-offs.

- 2. If a dissipating surface, thick at least 35 mm, and with a surface similar or bigger than the one shown in *Figure 3*, is created making use of the printed circuit. Such heatsinking surface is considered on the bottom side of an horizontal PCB (worst case).

- 3. If the power dissipating pins (the four central ones), as well as the others, have a minimum thermal connection with the external world (very thin strips only) so that the dissipation takes place through still air and through the PCB itself. It is the same situation of note 2, without any heatsinking surface created on purpose on the board.

Figure 3. Printed Heatsink

Maximum ratings L6234

## 4 Maximum ratings

Table 4. Absolute maximum ratings

| Symbol                            | Parameter                                                   | Value              | Unit |

|-----------------------------------|-------------------------------------------------------------|--------------------|------|

| V <sub>S</sub>                    | Power supply voltage                                        | 52                 | V    |

| $V_{IN}, V_{EN}$                  | Input enable voltage                                        | - 0.3 to 7         | V    |

| I <sub>peak</sub>                 | Pulsed output current (1)                                   | 5                  | Α    |

| V <sub>SENSE</sub>                | Sensing voltage (DC voltage)                                | -1 to 4            | V    |

| V <sub>boot</sub>                 | Bootstrap peak voltage                                      | 62                 | V    |

| V <sub>OD</sub>                   | Differential output voltage (between any of the 3 OUT pins) | 60                 | V    |

| f <sub>C</sub>                    | Commutation frequency                                       | 150                | kHz  |

| $V_{REF}$                         | Reference voltage                                           | 12                 | V    |

| P <sub>tot</sub>                  | Total power dissipation L6234PD, T <sub>A</sub> = 70°C      | 2.3                | W    |

| P <sub>tot</sub>                  | Total power dissipation L6234, T <sub>A</sub> = 70°C        | 1.6 <sup>(2)</sup> | W    |

| T <sub>stg</sub> , T <sub>j</sub> | Storage and junction temperature range                      | -40 to 150         | °C   |

<sup>1.</sup> Pulse width limited only by junction temperature and the transient thermal impedance

#### 4.1 Recommended operating conditions

Table 5. Recommended operating conditions

| Symbol             | Parameter                                                                 | Value      | Unit |

|--------------------|---------------------------------------------------------------------------|------------|------|

| V <sub>S</sub>     | Supply voltage                                                            | 7 to 42    | V    |

| V <sub>OD</sub>    | Peak to peak differential voltage (between any of the 3 out pins)         | 52         | V    |

| l <sub>out</sub>   | DC output current powerSO20 (T <sub>A</sub> = 25°C)                       | 4          | Α    |

|                    | DC output current powerDIP (T <sub>A</sub> = 25°C) with infinite heatsink | 2.8        | Α    |

| V                  | Sensing voltage (pulsed t <sub>w</sub> < 300 nsec)                        | -4 to 4    | V    |

| V <sub>SENSE</sub> | Sensing voltage (DC)                                                      | -1 to 1    | V    |

| Tj                 | Junction temperature range                                                | -40 to 125 | °C   |

<sup>2.</sup> Mounted on board with minimized copper area

## 5 Electrical characteristics

$\mbox{V}_{\mbox{\scriptsize S}}$  = 42 V;  $\mbox{T}_{j}$  = 25 °C unless otherwise specified.

Table 6. Electrical characteristics

| Symbol                              | Parameter                           | Test condition                    | Min. | Тур. | Max. | Unit |

|-------------------------------------|-------------------------------------|-----------------------------------|------|------|------|------|

| V <sub>S</sub>                      | Supply voltage                      |                                   | 7    |      | 52   | V    |

| V <sub>ref</sub>                    | Reference voltage                   |                                   |      | 10   |      | V    |

| I <sub>S</sub>                      | Quiescent supply current            |                                   |      | 6.5  |      | mA   |

| T <sub>S</sub>                      | Thermal shutdown                    |                                   | 150  |      |      | °C   |

| T <sub>D</sub>                      | Dead time protection                |                                   |      | 300  |      | ns   |

| Output dm                           | os transistor                       | •                                 | •    | •    | •    |      |

| I <sub>DSS</sub>                    | Leakage current                     |                                   |      |      | 1    | mA   |

| R <sub>DSon</sub>                   | R <sub>DSon</sub> ON resistance 0.3 |                                   |      | Ω    |      |      |

| Source dra                          | Source drain diode                  |                                   |      |      |      |      |

| V <sub>SD</sub>                     | Forward ON voltage                  | I <sub>SD</sub> = 4A; EN =<br>LOW |      | 1.2  |      | V    |

| T <sub>RR</sub>                     | Reverse recovery time               | I <sub>F</sub> = 4A               |      | 900  |      | ns   |

| T <sub>pr</sub>                     | Forward recovery time               |                                   |      | 200  |      | ns   |

| Logic levels                        |                                     |                                   |      |      |      |      |

| V <sub>INL</sub> , V <sub>ENL</sub> | Input LOW voltage                   |                                   | -0.3 |      | 0.8  | V    |

| V <sub>INH</sub> , V <sub>ENH</sub> | Input HIGH voltage                  |                                   | 2    |      | 7    | V    |

| I <sub>INL</sub> , I <sub>ENL</sub> | Input LOW current                   | $V_{IN}, V_{EN} = L$              |      |      | -10  | μA   |

| I <sub>INH</sub> , I <sub>ENH</sub> | Input HIGH current                  | $V_{IN}, V_{EN} = H$              |      | 30   |      | μA   |

Circuit description L6234

### 6 Circuit description

L6234 is a triple half bridge designed to drive brushless DC motors. Each half bridge has 2 power DMOS transistors with  $R_{DSon}$  = 0.3  $\Omega$ .

The 3 half bridges can be controlled independently by means of the 3 inputs IN1, IN2, IN3 and the 3 inputs EN1, EN2, and EN3. An external connection to the 3 common low side DMOS sources is provided to connect a sensing resistor for constant current chopping application.

The driving stage and the logic stage are designed to work from 7 V to 52 V.

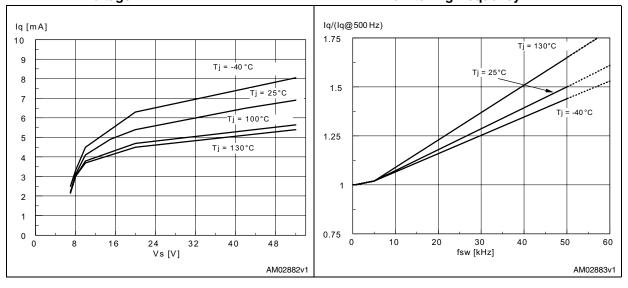

## 7 Typical characteristics

Figure 4. Quiescent current vs. supply voltage

Figure 5. Normalized quiescent current vs. switching frequency

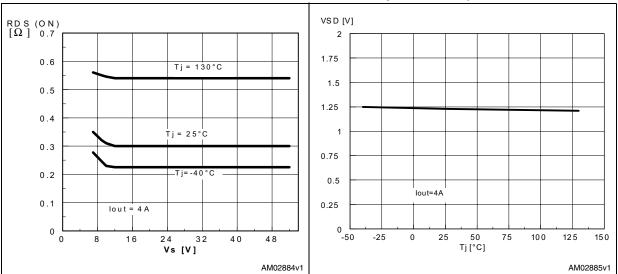

Figure 6. Typical  $R_{DSon}$  vs. supply voltage

Figure 7. Source drain forward on voltage vs. junction temperature

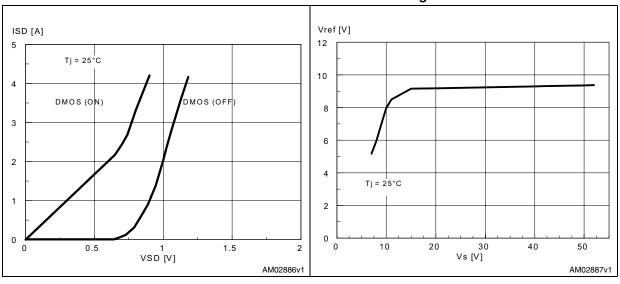

Figure 8. Typical diode forward ON characteristics

Figure 9. Reference voltage vs. supply voltage

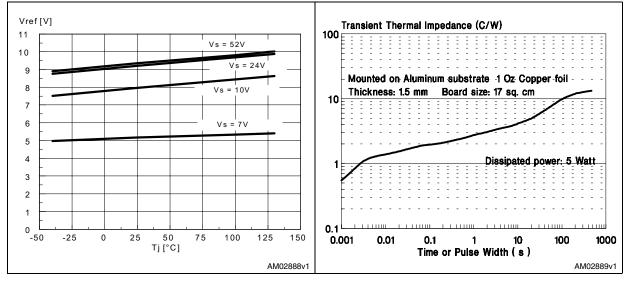

Figure 10. Reference voltage vs. junction temperature

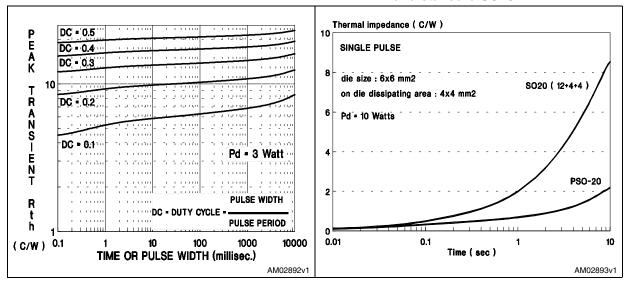

Figure 11. PowerSO-20 transient thermal resistance

57

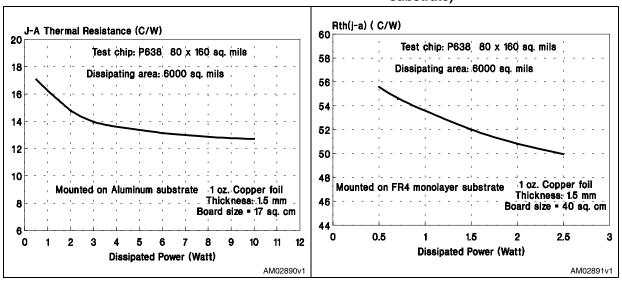

Figure 12. PowerSO-20 thermal resistance (mounted on Aluminium substrate)

Figure 13. PowerSO-20 thermal resistance (mounted on FR4 monolayer substrate)

Figure 14. PowerSO-20: with external heatsink Figure 15. Thermal impedance of PowerSO-20 and standard SO20

Mechanical data L6234

#### 8 Mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

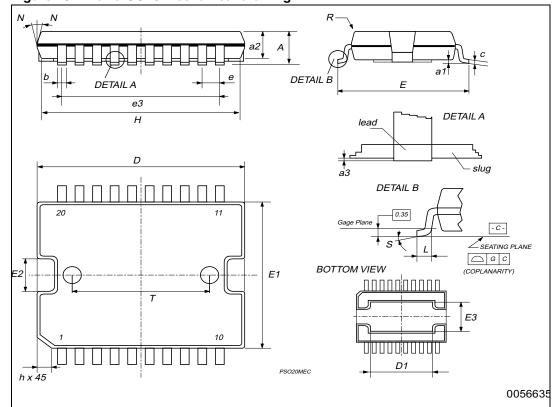

Table 7. PowerSO20 mechanical data

| Dim    |           | mm        |      |

|--------|-----------|-----------|------|

| Dim.   | Min.      | Тур.      | Max. |

| А      |           |           | 3.6  |

| a1     | 0.1       |           | 0.3  |

| a2     |           |           | 3.3  |

| а3     | 0         |           | 0.1  |

| b      | 0.4       |           | 0.53 |

| С      | 0.23      |           | 0.32 |

| D (1)  | 15.8      |           | 16   |

| D1     | 9.4       |           | 9.8  |

| E      | 13.9      |           | 14.5 |

| е      |           | 1.27      |      |

| e3     |           | 11.43     |      |

| E1 (1) | 10.9      |           | 11.1 |

| E2     |           |           | 2.9  |

| E3     | 5.8       |           | 6.2  |

| G      | 0         |           | 0.1  |

| Н      | 15.5      |           | 15.9 |

| h      |           |           | 1.1  |

| L      | 0.8       |           | 1.1  |

| N      | 8° (typ.) |           |      |

| S      |           | 8° (max.) |      |

| Т      |           | 10        |      |

L6234 Mechanical data

Figure 16. PowerSO20 mechanical drawing

Mechanical data L6234

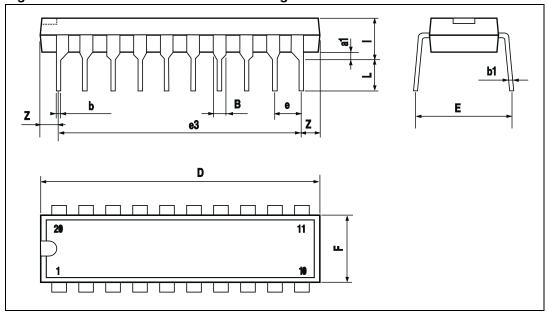

Table 8. PowerDIP20 mechanical data

| Dim.   | mm   |       |       |  |

|--------|------|-------|-------|--|

| Dilli. | Min. | Тур.  | Max.  |  |

| a1     | 0.51 |       |       |  |

| В      | 0.85 |       | 1.40  |  |

| b      |      | 0.50  |       |  |

| b1     | 0.38 |       | 0.50  |  |

| D      |      |       | 24.80 |  |

| E      |      | 8.80  |       |  |

| е      |      | 2.54  |       |  |

| e3     |      | 22.86 |       |  |

| F      |      |       | 7.10  |  |

| I      |      |       | 5.10  |  |

| L      |      | 3.30  |       |  |

| Z      |      |       | 1.27  |  |

Figure 17. PowerDIP20 mechanical drawing

L6234 Revision history

# 9 Revision history

Table 9. Document revision history

| Date           | Revision | Changes                                   |

|----------------|----------|-------------------------------------------|

| 01-Aug-2003    | 9        |                                           |

| 15-Nov-2011 10 |          | Updated Features in coverpage and Table 4 |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

16/16 Doc ID 1107 Rev 10