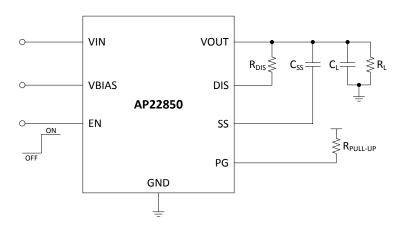

# **Typical Applications Circuit**

# **Pin Descriptions**

| Pin Name                                                                                        | Pin Number | Function                                                                                                  |

|-------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------|

| <b>SS</b> 1                                                                                     |            | Soft-Start Adjust An external capacitor connected between this pin and VOUT sets the ramp-up time of VOUT |

| EN 2 Enable Input<br>Active high                                                                |            | '                                                                                                         |

| VIN                                                                                             | 3, 4       | Input Voltage Connects to the Source of the P-channel MOSFET                                              |

| GND                                                                                             | 5          | Ground                                                                                                    |

| VRIAS                                                                                           |            | Supply Voltage<br>Recommended range: 2.5V ≤ VBIAS ≤ 5.5V                                                  |

| PG 7 Power Good Open-drain output to indicate w                                                 |            | Power Good Open-drain output to indicate when the P-channel pass switch is fully enhanced                 |

| DIS  Output Discharge An external resistor between DIS and VOUT sets the discharge rate of VOUT |            | i g                                                                                                       |

| VOUT PAD Output Voltage PAD connects to the Drain of the P-channel                              |            | Output Voltage PAD connects to the Drain of the P-channel MOSFET                                          |

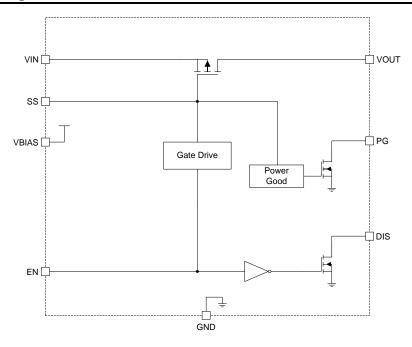

### **Functional Block Diagram**

### Absolute Maximum Ratings (@T<sub>A</sub> = +25°C, unless otherwise specified.) (Note 4)

| Symbol              | Parameter                               | Ratings  | Units       |      |

|---------------------|-----------------------------------------|----------|-------------|------|

| V <sub>IN</sub>     | Input Voltage                           |          | 12.0        | V    |

| V <sub>OUT</sub>    | Output Voltage                          |          | 12.0        | V    |

| V <sub>EN</sub>     | Enable Voltage                          |          | 6.0         | V    |

| V <sub>BIAS</sub>   | Bias Voltage                            |          | 6.0         | V    |

| IL                  | Load Current                            | 8.0      | А           |      |

| T <sub>J(max)</sub> | Maximum Junction Temperature            | 125      | °C          |      |

| T <sub>ST</sub>     | Storage Temperature                     |          | −55 to +150 | °C   |

|                     | Davies Discinction                      | (Note 5) | 0.35        | W    |

| P <sub>D</sub>      | Power Dissipation                       | (Note 6) | 1.8         | W    |

| -                   | The second Decision on the Australia    | (Note 5) | 300         | 2011 |

| $R_{\theta JA}$     | Thermal Resistance, Junction to Ambient | (Note 6) | 60          | °C/W |

| R <sub>0</sub> JC   | Thermal Resistance, Junction to Case    | -        | 5           | °C/W |

Notes:

- 4. Stresses greater than the 'Absolute Maximum Ratings' specified above may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions exceeding those indicated in this specification is not implied. Device reliability may be affected by exposure to absolute maximum rating conditions for extended periods of time.

- 5. For a device surface mounted on minimum recommended pad layout, in still air conditions; the device is measured when operating in a steady state condition.

- 6. For a device surface mounted on 25mm by 25mm by 1.6mm FR4 PCB with high coverage of single sided 2oz copper, in still air conditions; the device is measured when operating in a steady state condition.

# Recommended Operating Conditions (@T<sub>A</sub> = +25°C, unless otherwise specified.)

| Symbol          | Parameter                     | Min | Max  | Units |

|-----------------|-------------------------------|-----|------|-------|

| V <sub>IN</sub> | Input Voltage                 | 4.5 | 11.0 | V     |

| $V_{BIAS}$      | Bias Voltage                  | 2.5 | 5.5  | V     |

| V <sub>EN</sub> | Enable Voltage                | 0   | 5.5  | V     |

| $V_{PG}$        | Power Good Voltage Range      | 0   | 11.0 | V     |

| T <sub>A</sub>  | Operating Ambient Temperature | -40 | +85  | °C    |

# $\hline \textbf{Electrical Characteristics} \ \ (@T_A = +25^{\circ}C, \ \ V_{BIAS} = 2.5V - 5.5V, \ C_{IN} = 1 \mu F, \ C_L = 100 nF, \ unless \ otherwise \ specified.)$

| Symbol                | Parameters                          | Condition                                                                 | ns                       | Min | Тур | Max  | Unit |

|-----------------------|-------------------------------------|---------------------------------------------------------------------------|--------------------------|-----|-----|------|------|

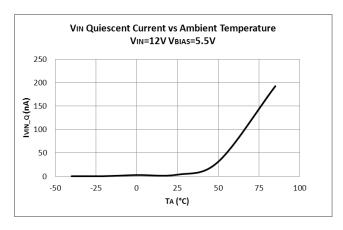

|                       |                                     |                                                                           | V <sub>IN</sub> = 10.0V  | -   | 5.0 | 200  |      |

| $I_{VIN\_Q}$          | V <sub>IN</sub> Quiescent Current   | I <sub>OUT</sub> = 0A                                                     | $V_{IN} = 8.4V$          | -   | 3.0 | 200  | nA   |

|                       |                                     |                                                                           | $V_{IN} = 5.0V$          | -   | 1.0 | 200  |      |

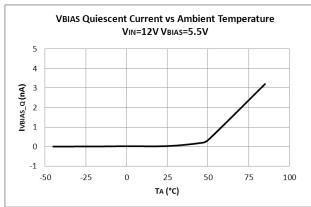

| I <sub>VBIAS_Q</sub>  | V <sub>BIAS</sub> Quiescent Current | V <sub>IN</sub> = 12.0V, I <sub>OUT</sub> = 0A                            |                          | -   | 1.0 | 200  | nA   |

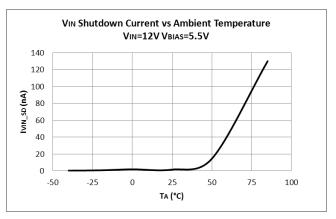

| I <sub>VIN_SD</sub>   | V <sub>IN</sub> Shutdown Current    | V <sub>IN</sub> = 12.0V, V <sub>EN</sub> = 0V                             |                          | -   | 2.0 | 200  | nA   |

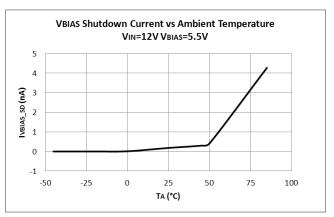

| I <sub>VBIAS_SD</sub> | V <sub>BIAS</sub> Shutdown Current  | V <sub>IN</sub> = 12.0V, V <sub>EN</sub> = 0V                             |                          | -   | 2.0 | 200  | nA   |

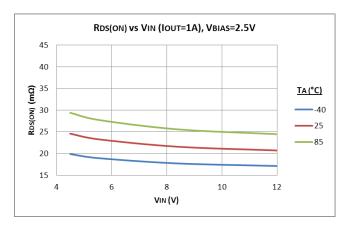

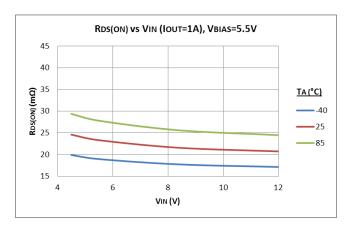

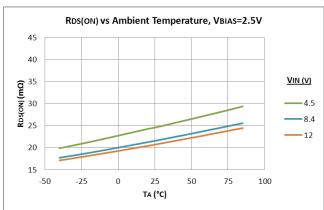

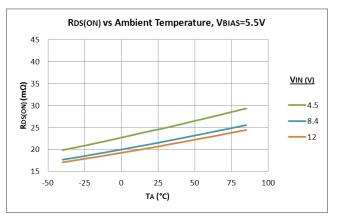

|                       | Load Switch On-Resistance           | I <sub>OUT</sub> = −1A                                                    | V <sub>IN</sub> = 10.0V  | -   | 21  | 31   |      |

| R <sub>DS(ON)</sub>   |                                     |                                                                           | V <sub>IN</sub> = 8.4V   | -   | 21  | 31   | mΩ   |

|                       |                                     |                                                                           | $V_{IN} = 5.0V$          | -   | 23  | 33   |      |

| $V_{\text{IH\_EN}}$   | EN Input Logic High Voltage         | -                                                                         |                          | 1.0 | -   | -    | V    |

| $V_{IL_{\_}EN}$       | EN Input Logic Low Voltage          | -                                                                         |                          | -   | -   | 0.5  | V    |

| I <sub>LEAK_EN</sub>  | EN Input Leakage                    | V <sub>EN</sub> = V <sub>BIAS</sub>                                       |                          | -   | -   | 100  | nA   |

| D                     | Discharge FFT On Begintage          | )/ 0)/ l 40m/                                                             | V <sub>BIAS</sub> = 5.0V | -   | 8   | 11   | Ω    |

| R <sub>DS_DIS</sub>   | Discharge FET On-Resistance         | $V_{EN} = 0V$ , $I_{DIS} = 10mA$                                          | $V_{BIAS} = 2.5V$        | -   | 11  | 16   | Ω    |

| $V_{OL\_PG}$          | Power Good Output Low Level         | I <sub>OL_PG</sub> = 100μA, V <sub>EN</sub> = 0V                          |                          | -   | -   | 0.2  | V    |

| I <sub>OZ_PG</sub>    | Power Good High-Impedance Current   | V <sub>PG</sub> = V <sub>BIAS</sub> , V <sub>EN</sub> = V <sub>BIAS</sub> |                          | -   | -   | 0.05 | μΑ   |

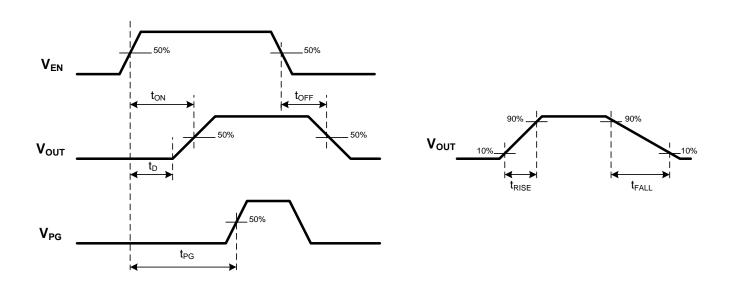

### Switching Characteristics (@ $T_A = +25^{\circ}C$ , $V_{BIAS} = 2.5V - 5.5V$ , $C_{IN} = 1\mu F$ , $C_L = 100nF$ , unless otherwise specified)

| Symbol            | Parameters                 | Conditions                                               | 3                       | Min | Тур | Max | Unit |

|-------------------|----------------------------|----------------------------------------------------------|-------------------------|-----|-----|-----|------|

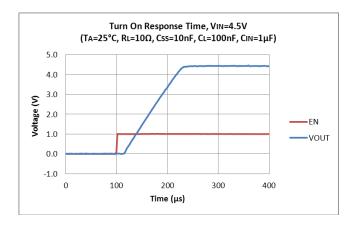

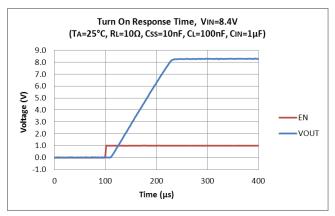

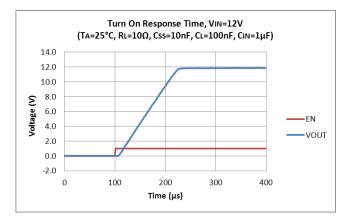

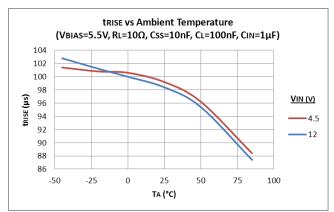

|                   |                            |                                                          | V <sub>IN</sub> = 10.0V |     | 100 |     |      |

| t <sub>RISE</sub> | Output Rise Time           | $R_L=10\Omega,C_{SS}=10nF$                               | V <sub>IN</sub> = 8.4V  | -   | 102 | -   | μs   |

|                   |                            |                                                          | V <sub>IN</sub> = 5.0V  |     | 104 |     |      |

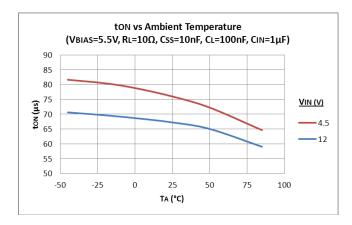

|                   |                            |                                                          | V <sub>IN</sub> = 10.0V |     | 70  |     |      |

| t <sub>ON</sub>   | Output Turn-ON Delay Time  | $R_L=10\Omega,C_{SS}=10nF$                               | $V_{IN} = 8.4V$         | -   | 75  | -   | μs   |

|                   |                            |                                                          | $V_{IN} = 5.0V$         |     | 82  |     |      |

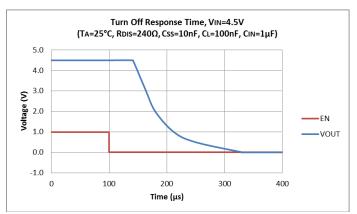

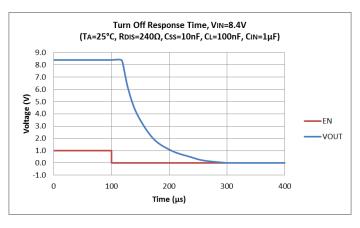

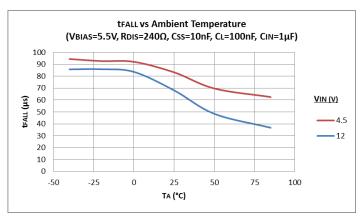

| tFALL             | Output Fall Time           | $R_L = Open, R_{DIS} = 240\Omega,$<br>$C_{SS} = 10nF$    | V <sub>IN</sub> = 10.0V |     | 70  |     |      |

|                   |                            |                                                          | $V_{IN} = 8.4V$         | -   | 71  | -   | μs   |

|                   |                            |                                                          | V <sub>IN</sub> = 5.0V  |     | 75  |     |      |

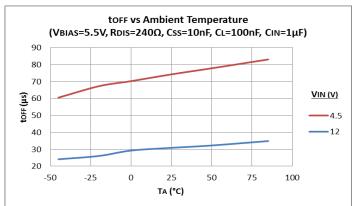

|                   |                            | $R_L$ = Open, $R_{DIS}$ = 240 $\Omega$ , $C_{SS}$ = 10nF | V <sub>IN</sub> = 10.0V |     | 41  |     | μs   |

| t <sub>OFF</sub>  | Output Turn-OFF Delay Time |                                                          | $V_{IN} = 8.4V$         | -   | 45  | -   |      |

|                   |                            |                                                          | $V_{IN} = 5.0V$         |     | 60  |     |      |

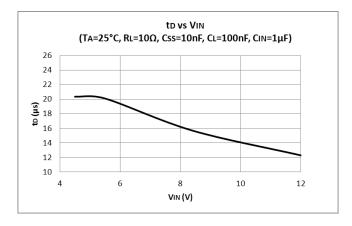

|                   |                            |                                                          | V <sub>IN</sub> = 10.0V |     | 12  |     |      |

| $t_D$             | Output Start Delay Time    | $R_L = 10\Omega$ , $C_{SS} = 10nF$                       | $V_{IN} = 8.4V$         | -   | 16  | -   | μs   |

|                   |                            |                                                          | $V_{IN} = 5.0V$         |     | 22  |     |      |

|                   |                            |                                                          | V <sub>IN</sub> = 10.0V |     | 250 |     |      |

| $t_{PG}$          | Power Good Delay Time      | $R_L = 10\Omega$ , $C_{SS} = 10nF$                       | V <sub>IN</sub> = 8.4V  | -   | 230 | -   | μs   |

|                   |                            |                                                          | V <sub>IN</sub> = 5.0V  |     | 205 |     |      |

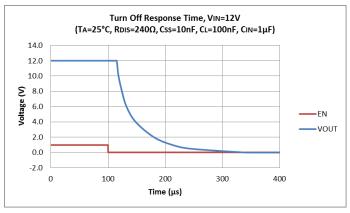

### ton/toff Waveforms

### Typical Performance Characteristics (@T<sub>A</sub> = +25°C, VBIAS = 5V, unless otherwise specified.)

### Typical Performance Characteristics (cont.) (@T<sub>A</sub> = +25°C, VBIAS = 5V, unless otherwise specified.)

### Typical Performance Characteristics (cont.) (@T<sub>A</sub> = +25°C, VBIAS = 5V, unless otherwise specified.)

### **Application Information**

#### **Theory of Operation**

The AP22850 is a load switch that can be used to isolate or power-down part of a system in order to reduce power consumption, particularly in battery-powered devices. The PMOS pass element in AP22850 is turned on when the EN pin is pulled high. This provides a controlled current source to decrease the voltage on the SS pin to GND, effectively turning on the PMOS pass switch and connecting VOUT to VIN.

During the turn-on phase, once the SS voltage reaches close to GND, the PMOS pass switch is fully enhanced with maximum available overdrive. Power is deemed to be good and the Power Good (PG) output is pulled high via an external pull-up resistor. The rise-time on VOUT is controlled by the value of the external capacitor between the SS and VOUT pin.

When EN is pulled low, the switch turns off and isolates VOUT from VIN. In addition, PG is pulled to indicate that the power is no longer good. The discharge pin keeps VOUT grounded while EN is low. The fall time on VOUT is largely controlled by the value of the discharge resistor and the capacitance on the output.

#### Input and Output Voltage

The Input Voltage (VIN) should be between 4.5V and 11V. With the switch is activated, the Output Voltage (VOUT) will be the input voltage minus the voltage drop across the device.

#### **Enable**

The GPIO compatible EN input allows the output current to be switched on and off. A high signal (switch on) should be at least 1V, and the low signal (switch off) no higher than 0.5V.

This pin should not be left floating. It is advisable to hold EN low when applying or removing power.

#### **VBIAS**

The VBIAS input provides a positive power supply to the controller circuitry. It should be set in the range of 2.5V to 5.5V. VBIAS signal is essential for the device to power up and should be set before the switch is enabled.

#### **Power Good**

Power Good is an open-drain output that indicates when the pass switch is enhanced enough to deliver current to the load. PG is high (open-drain high impedance) when power is deemed good, and low when the power is deemed to not be good.

PG can be pulled up to any voltage to a maximum of 11V, although it is recommended to pull it up to VOUT with a resistor greater than  $20k\Omega$ . The advantage of pulling up PG to VOUT is that when EN is low, VOUT is also grounded. Thus, no power is wasted in the pull-up resistor.

If this feature is not required, then PG pin can be left floating

#### Input and Output Capacitors

AP22850 does not require any capacitor on VIN for successful operation. In addition, this device has no input-to-output capacitor ratio stipulation to account for current through the body diode. However, to minimize voltage dip on VIN due to inrush current at start-up, a capacitor can be place on VIN.

For heavier loads, it is recommended that the VIN and VOUT trace lengths be kept to a minimum. In addition, a bulk capacitor (≥ 10µF) may also be placed close to the VOUT pin. If using a bulk capacitor on VOUT, it is important to control the inrush current by choosing an appropriate soft-start time in order to minimize the droop on the input supply.

### **Application Information (cont.)**

#### Adjustable Slew Rate/Soft-Start

SS pin allows the output ramp time of the switch to be controlled using an external capacitor ( $C_{SS}$ ). This timing capacitor is connected between the SS and VOUT pin. Rise times (in  $\mu$ s) for different values of  $C_{SS}$  and  $V_{IN}$  are shown in the table below with  $V_{BIAS} = 5.5V$ .

| Measured at +2                     | Rise Time (in $\mu$ s) Measured at +25°C using 0805 X7R 10% 50V capacitors, $C_L$ = 100nF, $R_{DIS}$ = 1K, $R_L$ = 10 $\Omega$ |       |       |       |  |  |  |  |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--|--|--|--|

| V <sub>IN</sub><br>C <sub>SS</sub> | 4.5V                                                                                                                           | 7.0V  | 9.0V  | 11.0V |  |  |  |  |

| 1nF                                | 13.6                                                                                                                           | 12.4  | 12.0  | 11.4  |  |  |  |  |

| 10nF                               | 97.2                                                                                                                           | 99.2  | 98.8  | 97.9  |  |  |  |  |

| 100nF                              | 955                                                                                                                            | 1,075 | 1,154 | 1253  |  |  |  |  |

**Table 1 Timing Capacitors and Rise Times**

#### **Adjustable Discharge**

When EN goes low, VOUT is discharged to ground through the discharge resistor ( $R_{DIS}$ ) on the DIS pin. A value greater than 240 $\Omega$  is recommended for  $R_{DIS}$ .

While the discharge/fall-time on VOUT can be controlled using  $R_{DIS}$ , capacitors on VOUT and SS also contribute to the timing. Higher discharge resistance increases the RC time constant and hence, the discharge time. Fall times (in  $\mu$ s) for different values of  $R_{DIS}$  and  $V_{IN}$  are shown in the table below with  $V_{BIAS} = 5.5V$ .

| 1,206 250mW 1%<br>Discharge resistor (Ω) | Fall Time (in $\mu$ s) Measured at +25°C, C <sub>L</sub> = 100nF, C <sub>SS</sub> = 1nF, R <sub>L</sub> = open |       |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------|--|

|                                          | 5V                                                                                                             | 11V   |  |

| 240                                      | 71.8                                                                                                           | 69.5  |  |

| 1,000                                    | 264.2                                                                                                          | 276.7 |  |

| 3,900                                    | 1,029                                                                                                          | 1,078 |  |

Table 2 Discharge Resistors and Output Voltage Fall Time

March 2015

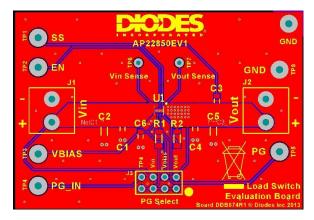

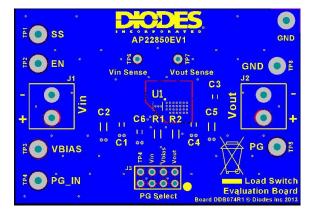

### **Board Layout and Thermal Considerations**

Due to the high current capacity of the load switch, PCB layout needs to ensure good thermal distribution during operation. The top and bottom of AP22850EV1, (the evaluation board for AP22850), can be seen below.

Figure 3 PCB Copper Layout & Silk Screen - Top

Figure 4 PCB Copper Layout & Silk Screen - Bottom

Thermal vias are used directly underneath the chip to help distribute the heat from the device. The ground plane on the underside of the board effectively acts as a large heatsink. The widths of the tracks carrying VIN and VOUT are kept wide. Vias are also distributed around the board to aid thermal conduction and to ensure a consistent potential, particularly around the ground connections of the capacitors. All capacitors used are located as close as possible to the AP22850 to minimize any parasitic effects.

The maximum junction temperature of the AP22850 is +125°C. To ensure that this is not exceeded, the following equation can be used to give an approximation of junction temperature. Temperature readings taken with a thermal camera can also give a good approximation of power dissipation with the use of this equation. The board layout has a major influence on the parameter  $\theta_{IA}$ .

$$T_I = T_A + (\theta_{IA} \times P_D)$$

Where,  $T_I$  = Junction Temperature (°C)

$T_A$  = Ambient Temperature (°C)

$\theta_{IA}$  = Junction to Ambient Thermal Impedance (°C/W)

$P_D$  = Power Dissipation (voltage drop across device × output current) (W)

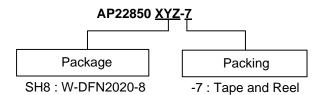

### **Ordering Information**

| Part Number  | Package | Packaging   | 7" Tape a         | and Reel           |

|--------------|---------|-------------|-------------------|--------------------|

| Part Number  | Code    | (Note 7)    | Quantity          | Part Number Suffix |

| AP22850SH8-7 | SH8     | W-DFN2020-8 | 3,000/Tape & Reel | -7                 |

Note:

7. Pad layout as shown on Diodes Inc. suggested pad layout document AP02001, which can be found on our website at http://www.diodes.com/datasheets/ap02001.pdf.

### **Marking Information**

#### W-DFN2020-8

(Top View)

XX: Identification code

Y: Year 0~9

$\underline{W}$ : Week: A~Z: 1~26 week;

a~z: 27~52 week; z represents 52 and 53 week

X: A~Z: Internal Code

| Device       | Package     | Identification Code |  |

|--------------|-------------|---------------------|--|

| AP22850SH8-7 | W-DFN2020-8 | WC                  |  |

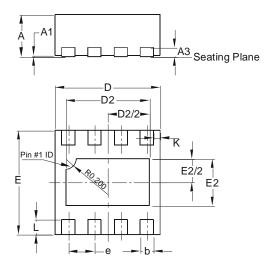

# Package Outline Dimensions (All dimensions in mm)

Please see AP02002 at http://www.diodes.com/datasheets/ap02002.pdf for the latest version.

|                | W-DFN2020-8<br>Type C |       |       |  |  |  |  |  |

|----------------|-----------------------|-------|-------|--|--|--|--|--|

| Dim Min Max Ty |                       |       |       |  |  |  |  |  |

| Α              | 0.770                 | 0.830 | 0.800 |  |  |  |  |  |

| A1             | 0                     | 0.05  | 0.02  |  |  |  |  |  |

| А3             | -                     | -     | 0.152 |  |  |  |  |  |

| b              | 0.20                  | 0.30  | 0.25  |  |  |  |  |  |

| D              | 1.950                 | 2.075 | 2.000 |  |  |  |  |  |

| D2             | 1.50                  | 1.70  | 1.60  |  |  |  |  |  |

| E              | 1.950                 | 2.075 | 2.000 |  |  |  |  |  |

| E2             | 0.80                  | 1.00  | 0.90  |  |  |  |  |  |

| е              | -                     | -     | 0.50  |  |  |  |  |  |

| K              | -                     | -     | 0.125 |  |  |  |  |  |

| L              | 0.240                 | 0.340 | 0.290 |  |  |  |  |  |

| All            | All Dimensions in mm  |       |       |  |  |  |  |  |

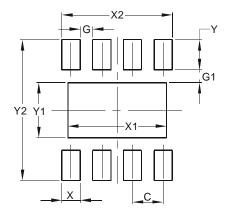

### **Suggested Pad Layout**

Please see AP02001 at http://www.diodes.com/datasheets/ap02001.pdf for the latest version.

| Dimensions | Value (in mm) |

|------------|---------------|

| С          | 0.500         |

| G          | 0.200         |

| G1         | 0.210         |

| Х          | 0.300         |

| X1         | 1.600         |

| X2         | 1.750         |

| Y          | 0.490         |

| Y1         | 0.900         |

| Y2         | 2.300         |

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel. Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### **LIFE SUPPORT**

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2015, Diodes Incorporated

www.diodes.com

Downloaded from Arrow.com.