## **Application Note**

| AN41908A    |      |  |  |  |  |

|-------------|------|--|--|--|--|

| Total Pages | Page |  |  |  |  |

| 70          | 2    |  |  |  |  |

### Contents

| ■ Serial Interface              | 3  |

|---------------------------------|----|

| ■ VD Signal Internal Processing | 13 |

| ■ Micro Step Motor Driver       | 14 |

| ■ Reset / Protection Circuit    | 36 |

| ■ Iris Control                  | 38 |

| ■ Iris Control Hall Sensor      | 62 |

| ■ LED Driver                    | 69 |

| ■ Technical Data                | 70 |

| Revision 0.06 |  |

|---------------|--|

| 2012-09-06    |  |

|                  | A south a diam Night | AN41908A    |      |  |  |

|------------------|----------------------|-------------|------|--|--|

|                  | Application Note     | Total Pages | Page |  |  |

| Serial Interface |                      | 70          | 3    |  |  |

### Serial Interface

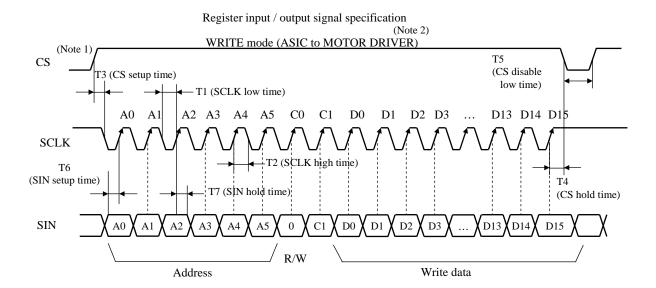

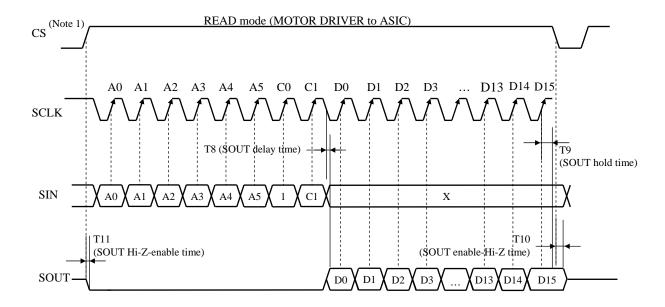

### ■ Timing Chart

Note) The characteristics listed below are reference values derived from the design of the IC and are not guaranteed.

Note 1) CS default value of each cycle (Write / Read mode) starts from Low-level.

Note 2) It is necessary to input the system clock OSCIN at write mode.

|                  | Amuliantina Nata | AN41908A |      |  |  |

|------------------|------------------|----------|------|--|--|

|                  | Application Note |          | Page |  |  |

| Serial Interface |                  | 70       | 4    |  |  |

■Electrical Characteristics (Reference values for design) at AVDD5, MVCCx = 4.8 V, DVDD, AVDD3 = 3.1 V Notes)  $T_a = 25^{\circ}C \pm 2^{\circ}C$  unless otherwise specified. The characteristics listed below are reference values derived from the design of the IC and are not guaranteed by inspection.

If a problem does occur related to these characteristics, we will respond in good faith to user concerns.

| D.N.s | . Parameter          | Cymbol                      | Conditions | Refe    | Lloit |     |      |

|-------|----------------------|-----------------------------|------------|---------|-------|-----|------|

| B No. | Parameter            | Parameter Symbol Conditions |            | Min Typ |       | Max | Unit |

| S1    | Serial clock         | Sclock                      | _          | 1       | _     | 5   | MHz  |

| S2    | SCLK low time        | T1                          | _          | 100     | _     | _   | ns   |

| S3    | SCLK high time       | T2                          | _          | 100     | _     | _   | ns   |

| S4    | CS setup time        | Т3                          | _          | 60      | _     | _   | ns   |

| S5    | CS hold time         | T4                          | _          | 60      | _     | _   | ns   |

| S6    | CS disable low time  | T5                          | _          | 100     | _     | _   | ns   |

| S7    | SIN setup time       | Т6                          | _          | 50      | _     | _   | ns   |

| S8    | SIN hold time        | T7                          | _          | 50      | _     | _   | ns   |

| S9    | SOUT delay time      | Т8                          | _          | _       | _     | 60  | ns   |

| S10   | SOUT hold time       | Т9                          | _          | 60      | _     | _   | ns   |

| S11   | SOUT enable-Hiz time | T10                         | _          | _       | _     | 60  | ns   |

| S12   | SOUT Hiz-enable time | T11                         | _          | _       | _     | 60  | ns   |

| S13   | SOUT Cload           | Tsc                         | _          | _       | _     | 40  | pF   |

| Revision 0.06 |  |

|---------------|--|

| 2012-09-06    |  |

|                  | Application Note | AN41908A    |      |  |  |

|------------------|------------------|-------------|------|--|--|

|                  |                  | Total Pages | Page |  |  |

| Serial Interface | · ·              | 70          | 5    |  |  |

### ■ Register Map

|     | D15                         | D14    | D13      | D12        | D11          | D10           | D9             | D8               | D7                     | D6                                   | D5              | D4             | D3          | D2         | D1        | D0       |

|-----|-----------------------------|--------|----------|------------|--------------|---------------|----------------|------------------|------------------------|--------------------------------------|-----------------|----------------|-------------|------------|-----------|----------|

| 00H |                             |        |          |            |              |               |                |                  |                        |                                      | IRS_TO          | GT[9:0]        |             |            | •         |          |

| 01H |                             |        |          | DGAIN[6:0  | ]            | ASOU          |                |                  | ND_LPF_F               | ND_LPF_FC[2:0] AS_FLT DEC<br>OFF AVE |                 | DEC<br>_AVE    | OVER_LPF_FC |            |           |          |

| 02H | PID_POLE[3:0] PID_ZERO[3:0] |        |          |            |              |               | IRIS_RO        | UND[3:0]         |                        |                                      |                 | .C_NR[3:0]     | .[210]      |            |           |          |

| 03H |                             |        | DT_ADJ   | _IRIS[1:0] | PV           | VM_IRIS[2     | :0]            | PW               | M_LPF_FC               | [2:0]                                | PWM_FLT<br>_OFF | LMT<br>_ENB    |             | ARV        | V[3:0]    |          |

| 04H |                             |        | Н        | ALL_OFFS   | ET_DAC[7:    | 0]            |                |                  |                        |                                      | 1               | HALL_BIA       | S_DAC[7:0   | )]         |           |          |

| 05H |                             |        |          | AAF_FC     |              | HALL_C        | GAIN[3:0]      |                  |                        |                                      | PID_INV         | TGT_FLT<br>OFF |             | TGT_LP     | F_FC[3:0] |          |

| 06H |                             |        |          |            |              |               |                |                  |                        |                                      | STAR            |                |             |            |           |          |

| 07H | PIEN                        |        |          |            |              |               |                |                  |                        | WIDTI                                | H1[11:0]        |                |             |            |           |          |

| 08H |                             |        |          |            |              |               |                |                  |                        |                                      | STAR            | Γ2[9:0]        |             |            |           |          |

| 09H | P2EN                        |        |          |            |              |               |                |                  |                        |                                      |                 |                | WIDT        | H2[5:0]    |           |          |

| 0AH |                             |        |          |            |              | DUTY<br>_TEST |                |                  | ,                      |                                      | TGT_IN_         | TEST[9:0]      |             |            |           |          |

| 0BH |                             | PID_CI | LIP[3:0] |            | ADC<br>_TEST | PDWNB         | MODESEL<br>_FZ | MODESEL<br>_IRIS | TESTEN1                |                                      |                 | ASWMO          | DDE[1:0]    |            |           |          |

| 0CH |                             |        |          |            |              |               |                |                  | IRSAD[9:0] (Read Only) |                                      |                 |                |             |            |           |          |

| 0DH |                             |        |          |            |              |               |                |                  |                        |                                      |                 |                |             |            |           |          |

| 0EH |                             |        |          |            | AV           | E_SPEED[      | 4:0]           |                  |                        |                                      |                 | TGT_UPI        | DATE[7:0]   |            |           |          |

| 0FH |                             |        |          |            |              | Reserved      |                |                  |                        |                                      | Rese            | erved          |             |            |           |          |

| 10H |                             |        |          |            |              |               |                |                  |                        |                                      |                 |                |             |            |           |          |

| 20H |                             | PWMR   | ES[1:0]  |            | PW           | /MMODE[4      | 4:0]           |                  |                        | _                                    |                 | DT1            | [7:0]       |            |           |          |

| 21H |                             |        |          |            |              |               |                |                  | TESTEN2                |                                      |                 |                | 1           | FZTEST[4:0 | )]        |          |

| 22H |                             |        |          |            | PHMOD        | AB[5:0]       |                |                  |                        |                                      |                 | DT2A           | A[7:0]      |            |           |          |

| 23H |                             |        |          | PPWB[7:0]  |              |               |                |                  |                        |                                      | PPW             | <b>A</b> [7:0] |             |            |           |          |

| 24H |                             |        | MICRO    | AB[1:0]    | LEDB         | ENDISAB       | BRAKE<br>AB    | CCWCW<br>AB      |                        |                                      |                 | PSUM           | AB[7:0]     |            |           |          |

| 25H |                             |        |          |            |              |               |                | INTCTA           | AB[15:0]               |                                      |                 |                |             |            |           |          |

| 26H |                             |        |          |            |              |               |                |                  |                        |                                      |                 |                |             |            |           |          |

| 27H | PHMODCD[5:0]                |        |          |            |              |               | DT2B[7:0]      |                  |                        |                                      |                 |                |             |            |           |          |

| 28H | PPWD[7:0]                   |        |          |            |              | PPWC[7:0]     |                |                  |                        |                                      |                 |                |             |            |           |          |

| 29H |                             |        | MICRO    | CD[1:0]    | LEDA         | ENDISCD       | BRAKE<br>CD    | CCWCW<br>CD      |                        |                                      |                 |                |             |            |           |          |

| 2AH |                             |        |          |            |              |               |                | INTCTO           | CD[15:0]               |                                      |                 |                |             |            |           |          |

| 2ВН |                             |        |          |            |              |               |                |                  |                        |                                      |                 |                |             |            |           |          |

| 2CH |                             |        |          |            |              |               |                |                  |                        |                                      |                 |                |             | Reserved   | Reserved  | Reserved |

| Revision 0.06 |  |

|---------------|--|

| 2012-09-06    |  |

|                  | A sanding tion Night | AN41908A |   |  |  |

|------------------|----------------------|----------|---|--|--|

|                  | Application Note     |          |   |  |  |

| Serial Interface |                      | 70       | 6 |  |  |

### ■ Register List

| Address | Register name / Bit wide | Function                                                      | Page |

|---------|--------------------------|---------------------------------------------------------------|------|

| 00h     | IRS_TGT[9:0]             | Iris target                                                   | 40   |

| 01h     | OVER_LPF_FC_1ST[1:0]     | ADC feedback filter (1) cut-off frequency                     | 41   |

|         | OVER_LPF_FC_2ND[1:0]     | ADC feedback filter (2) cut-off frequency                     | 41   |

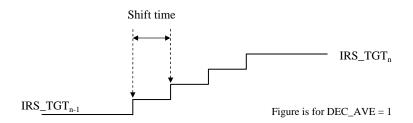

|         | DEC_AVE                  | Moving average of Iris target                                 | 42   |

|         | AS_FLT_OFF               | Filter before PID controller enable / disable                 | 42   |

|         | ASOUND_LPF_FC[2:0]       | Filter cut-off frequency before PID controller                | 43   |

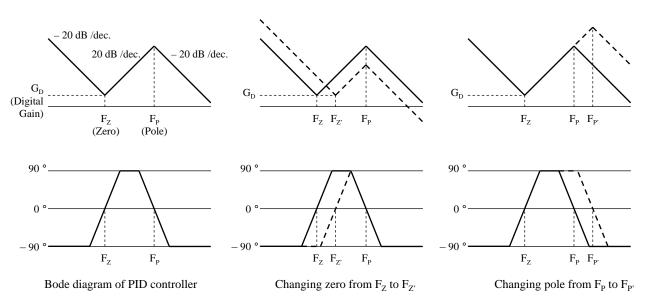

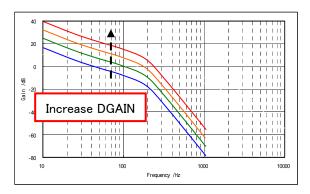

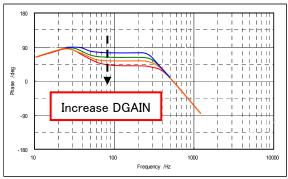

|         | DGAIN[6:0]               | PID controller digital gain                                   | 43   |

| 02h     | IRIS_CALC_NR[3:0]        | PID controller integral error cumulative prevention level     | 45   |

|         | IRIS_ROUND[3:0]          | PID controller differential error cumulative prevention level | 45   |

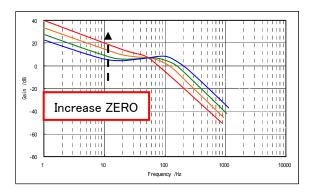

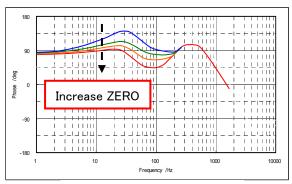

|         | PID_ZERO[3:0]            | PID controller zero point                                     | 46   |

|         | PID_POLE[3:0]            | PID controller pole                                           | 46   |

| 03h     | ARW[3:0]                 | Number of bits in PID controller integrator                   | 49   |

|         | LMT_ENB                  | PID controller integral stop                                  | 49   |

|         | PWM_FLT_OFF              | LPF after PID controller enable / disable                     | 50   |

|         | PWM_LPF_FC[2:0]          | LPF cut-off frequency after PID controller                    | 50   |

|         | PWM_IRIS[2:0]            | PWM frequency of Iris block output                            | 51   |

|         | DT_ADJ_IRIS[1:0]         | Dead time correction of Iris block output                     | 51   |

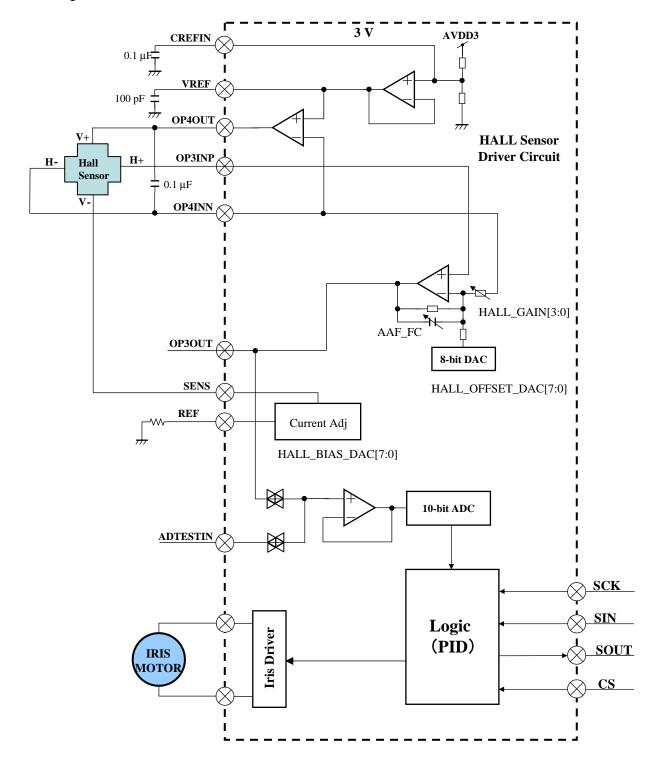

| 04h     | HALL_BIAS_DAC[7:0]       | Drive current value for hall element                          | 63   |

|         | HALL_OFFSET_DAC[7:0]     | Offset adjustment for hall element output amplifier           | 63   |

| 05h     | TGT_LPF_FC[3:0]          | Iris target value LPF cut-off frequency                       | 52   |

|         | TGT_FLT_OFF              | Iris target value LPF function enable / disable               | 52   |

|         | PID_INV                  | PID controller polarity                                       | 53   |

|         | HALL_GAIN[3:0]           | Hall element output amplifier gain                            | 64   |

|         | AAF_FC                   | Cut-off frequency of hall element output amplifier            | 64   |

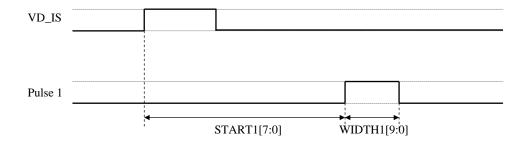

| 06h     | START1[9:0]              | Pulse 1 start time                                            | 54   |

| 07h     | WIDTH1[11:0]             | Pulse 1 width                                                 | 54   |

|         | PIEN                     | Pulse 1 output enable                                         | 54   |

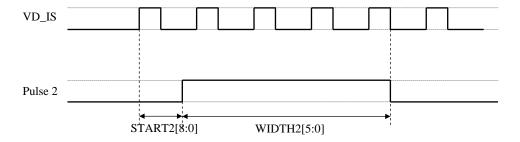

| 08h     | START2[9:0]              | Pulse 2 start time                                            | 56   |

| 09h     | WIDTH2[5:0]              | Pulse 2 width                                                 | 56   |

|         | P2EN                     | Pulse 2 output enable                                         | 56   |

| Revision 0.06 |  |

|---------------|--|

|               |  |

| 2012-09-06    |  |

|                  | A P C N l        | AN41        | 908A |

|------------------|------------------|-------------|------|

|                  | Application Note | Total Pages | Page |

| Serial Interface |                  | 70          | 7    |

### ■ Register List (continued)

| Address | Register name / Bit wide | Function                                     | Page |

|---------|--------------------------|----------------------------------------------|------|

| 0Ah     | TGT_IN_TEST[9:0]         | Iris output duty direct specified value      | 58   |

|         | DUTY_TEST                | Iris output duty direct specification enable | 59   |

| 0Bh     | ASWMODE[1:0]             | ADTESTIN pin connection selection            | 65   |

|         | TESTEN1                  | Test mode enable 1                           | 31   |

|         | MODESEL_IRIS             | VD_IS polarity selection                     | 13   |

|         | MODESEL_FZ               | VD_FZ polarity selection                     | 13   |

|         | PDWNB                    | Power down of Iris block                     | 65   |

|         | ADC_TEST                 | ADC read value updated timing                | 65   |

|         | PID_CLIP[3:0]            | Iris output PWM maximum duty                 | 67   |

| 0Ch     | IRSAD[9:0]               | ADC output for Iris (read only)              | 68   |

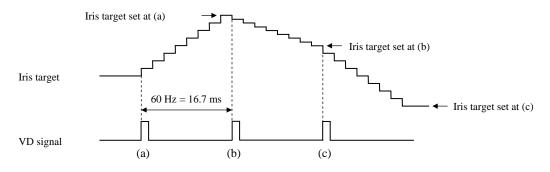

| 0Eh     | TGT_UPDATE[7:0]          | IRS_TGT (iris target) update delay time      | 60   |

| UEII    | AVE_SPEED[4:0]           | Iris target moving average speed             | 61   |

|                  | A 1' 4' N1 4     | AN41        | 908A |

|------------------|------------------|-------------|------|

|                  | Application Note | Total Pages | Page |

| Serial Interface |                  | 70          | 8    |

### ■ Register List (continued)

| Address | Register name / Bit wide | Function                                 | Page |

|---------|--------------------------|------------------------------------------|------|

| 20h     | DT1[7:0]                 | Start point wait time                    | 18   |

|         | PWMMODE[4:0]             | Micro step output PWM frequency          | 20   |

|         | PWMRES[1:0]              | Micro step output PWM resolution         | 20   |

| 21h     | FZTEST[4:0]              | PLS1/2 pin output signal selection       | 29   |

|         | TESTEN2                  | Test mode enable 2                       | 31   |

| 22h     | DT2A[7:0]                | α motor start point excitation wait time | 19   |

|         | PHMODAB[5:0]             | α motor phase correction                 | 21   |

| 23h     | PPWA[7:0]                | Driver A peak pulse width                | 22   |

|         | PPWB[7:0]                | Driver B peak pulse width                | 22   |

| 24h     | PSUMAB[7:0]              | α motor step count number                | 23   |

|         | CCWCWAB                  | α motor rotation direction               | 24   |

|         | BRAKEAB                  | α motor brake                            | 25   |

|         | ENDISAB                  | α motor enable/disable control           | 26   |

|         | LEDB                     | LED B output control                     | 69   |

|         | MICROAB[1:0]             | α motor sine wave division number        | 27   |

| 25h     | INTCTAB[15:0]            | α motor step cycle                       | 28   |

| 27h     | DT2B[7:0]                | β motor start point excitation wait time | 19   |

|         | PHMODCD[5:0]             | $\beta$ motor phase correction           | 21   |

| 28h     | PPWC[7:0]                | Driver C peak pulse width                | 22   |

|         | PPWD[7:0]                | Driver D peak pulse width                | 22   |

| 29h     | PSUMCD[7:0]              | β motor step count number                | 23   |

|         | CCWCWCD                  | β motor rotation direction               | 24   |

|         | BRAKECD                  | β motor brake                            | 25   |

|         | ENDISCD                  | β motor enable/disable control           | 26   |

|         | LEDA                     | LED A output control                     | 69   |

|         | MICROCD[1:0]             | $\beta$ motor sine wave division number  | 27   |

| 2Ah     | INTCTCD[15:0]            | β motor step cycle                       | 28   |

# Application Note Application Note AN41908A Total Pages Page 70 9

### ■ Serial Interface Specifications

Data transfer starts at the rising edge of CS, and stops at the falling edge of CS.

One unit of data is 24 bits. (24 bits of the following format are called a data set in this book.)

Address and data are serially input from SIN pin in synchronization with the data clock SCK at CS = 1.

Data is retrieved at the rising edge of SCK.

Moreover, data is output from SOUT pin at data readout. (Data is output at the rising edge of SCK.)

SOUT outputs Hi-Z at CS = 0, and outputs "0" except data readout at CS = 1.

The control circuit of serial interface is reset at CS = 0.

#### ■ Data Format

| 0  | 1  | 2   | 3   | 4   | 5   | 6   | 7   |

|----|----|-----|-----|-----|-----|-----|-----|

| A0 | A1 | A2  | A3  | A4  | A5  | C0  | C1  |

|    |    |     |     |     |     |     |     |

| 8  | 9  | 10  | 11  | 12  | 13  | 14  | 15  |

| D0 | D1 | D2  | D3  | D4  | D5  | D6  | D7  |

|    |    |     |     |     |     |     |     |

| 16 | 17 | 18  | 19  | 20  | 21  | 22  | 23  |

| D8 | D9 | D10 | D11 | D12 | D13 | D14 | D15 |

C0: Register write / read selection 0: write mode, 1: read mode

C1: Unused

A5 to A0 : Address of register D15 to D0 : Data written in register

When C0 bit is "0", the write mode is selected. The address and data are retrieved from SIN in synchronization with the rising edge of data clock SCLK, and the data is stored in internal register in synchronization with the rising edge of CS.

SOUT outputs "0" in the write mode.

When the data which is 23 or less bits per 1 processing is received in the write mode, the received data becomes invalid

The data of 25 or more bits is regarded as the continuous write mode, and the write operation is performed whenever the data of 24 bits is received. When the last data set is less than 24 bits in the continuous write mode, it becomes invalid. (The previous data set is valid.)

Even if noise occurs on SCK signal in the continuous write mode and the shifted data is received, pay attention to continue receiving or updating the shifted data.

When C0 bit is "1", the read mode is selected. The address is retrieved from SIN in synchronization with the rising edge of SCK, and then the register value of the address specified is output as LSB first from SOUT, in synchronization with the rising edge of SCK.

When C0 bit is "1", the values of D15 to D0 of SIN do not be cared.

### ■ Formatting

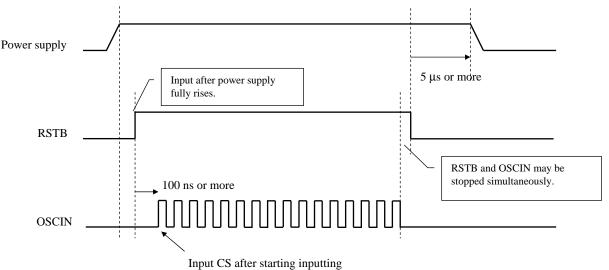

All the SIF functions containing a data register are formatted at RSTB = 0.

| Revision 0.06                                    |  |

|--------------------------------------------------|--|

| <del>                                     </del> |  |

| 2012-09-06                                       |  |

|                  | A P (            | AN41        | 908A |

|------------------|------------------|-------------|------|

|                  | Application Note | Total Pages | Page |

| Serial Interface |                  | 70          | 10   |

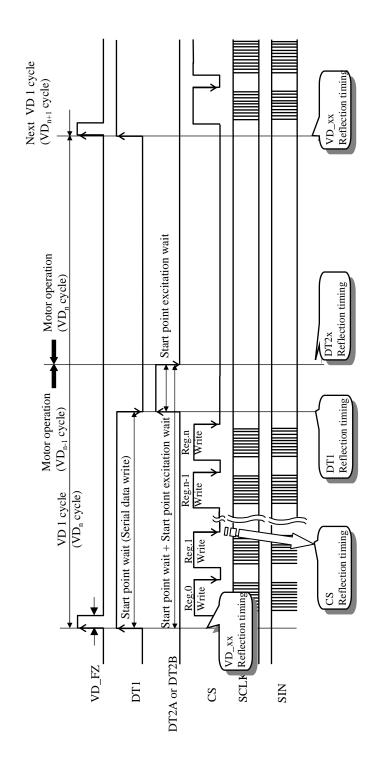

### ■ Register Setup Timing

| Revision 0.06 |  |

|---------------|--|

| 2012-09-06    |  |

## Application Note

| AN41908A         |    |  |  |  |  |  |  |

|------------------|----|--|--|--|--|--|--|

| Total Pages Page |    |  |  |  |  |  |  |

| 70               | 11 |  |  |  |  |  |  |

### ■ Register Setup Timing (continued)

Serial Interface

| Address | Register Name         | Setup Timing         |  |  |

|---------|-----------------------|----------------------|--|--|

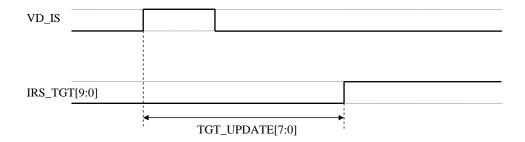

| 00h     | IRS_TGT[9:0]          | VD_IS+Adjusted value |  |  |

| 01h     | OVER_LPF_FC_1ST[1:0]  | VD_IS                |  |  |

|         | OVER_LPF_FC_2ND[1:0]  | VD_IS                |  |  |

|         | DEC_AVE               | VD_IS                |  |  |

|         | AS_FLT_OFF            | VD_IS                |  |  |

|         | AS_LPF_FC[2:0]        | VD_IS                |  |  |

|         | DGAIN[6:0]            | VD_IS                |  |  |

| 02h     | IRIS_CALC_NR[3:0]     | VD_IS                |  |  |

|         | IRIS_ROUND[3:0]       | VD_IS                |  |  |

|         | PID_ZERO[3:0]         | VD_IS                |  |  |

|         | PID_POLE[3:0]         | VD_IS                |  |  |

| 03h     | ARW[3:0]              | VD_IS                |  |  |

|         | LMT_ENB               | VD_IS                |  |  |

|         | PWM_FLT_OFF           | VD_IS                |  |  |

|         | PWM_LPF_FC[2:0]       | VD_IS                |  |  |

|         | PWM_IRIS[2:0]         | VD_IS                |  |  |

|         | DT_ADJ_IRIS[1:0]      | VD_IS                |  |  |

| 04h     | HALL_BIAS_DAC[7:0]    | VD_IS                |  |  |

|         | HALL_OFFSET _DAC[7:0] | VD_IS                |  |  |

| 05h     | TGT_LPF_FC[3:0]       | VD_IS                |  |  |

|         | TGT_FLT_OFF           | VD_IS                |  |  |

|         | PID_INV               | VD_IS                |  |  |

|         | HALL_GAIN[3:0]        | VD_IS                |  |  |

|         | AAF_FC                | VD_IS                |  |  |

| 06h     | START1[9:0]           | VD_IS                |  |  |

| 07h     | WIDTH1[11:0]          | VD_IS                |  |  |

|         | P1EN                  | VD_IS                |  |  |

| 08h     | START2[9:0]           | VD_IS                |  |  |

| 09h     | WIDTH2[5:0]           | VD_IS                |  |  |

|         | P2EN                  | VD_IS                |  |  |

| 0Ah     | TGT_IN_TEST[9:0]      | CS                   |  |  |

|         | DUTY_TEST             | CS                   |  |  |

| 0Bh     | ASWMODE[1:0]          | CS                   |  |  |

|         | TESTEN1               | CS                   |  |  |

|         | MODESEL_IRIS          | CS                   |  |  |

| Address | Register Name   | Setup Timing |

|---------|-----------------|--------------|

| 0Bh     | MODESEL_FZ      | CS           |

|         | PDWNB           | CS           |

|         | ADC_TEST        | CS           |

|         | PID_CLIP[3:0]   | VD_IS        |

| 0Ch     | IRSAD[9:0]      | Read Only    |

| 0Eh     | TGT_UPDATE[7:0] | CS           |

|         | AVE_SPEED[4:0]  | VD_IS        |

| 20h     | DT1[7:0]        | VD_FZ        |

|         | PWMMODE[4:0]    | DT1          |

|         | PWMRES[1:0]     | DT1          |

| 21h     | FZTEST[4:0]     | CS           |

|         | TESTEN2         | CS           |

| 22h     | DT2A[7:0]       | DT1          |

|         | PHMODAB[5:0]    | DT2A         |

| 23h     | PPWA[7:0]       | DT1          |

|         | PPWB[7:0]       | DT1          |

| 24h     | PSUMAB[7:0]     | DT2A         |

|         | CCWCWAB         | DT2A         |

|         | BRAKEAB         | DT2A         |

|         | ENDISAB         | DT1 or DT2A  |

|         | LEDB            | CS           |

|         | MICROAB[1:0]    | DT2A         |

| 25h     | INTCTAB[15:0]   | DT2A         |

| 27h     | DT2B[7:0]       | DT1          |

|         | PHMODCD[5:0]    | DT2B         |

| 28h     | PPWC[7:0]       | DT1          |

|         | PPWD[7:0]       | DT1          |

| 29h     | PSUMCD[7:0]     | DT2B         |

|         | CCWCWCD         | DT2B         |

|         | BRAKECD         | DT2B         |

|         | ENDISCD         | DT1 or DT2B  |

|         | LEDA            | CS           |

|         | MICROCD[1:0]    | DT2B         |

| 2Ah     | INTCTCD[15:0]   | DT2B         |

|               |  | 0 | 1. Iclicated at D 11 | 0. Tellected at D 12x |

|---------------|--|---|----------------------|-----------------------|

| Revision 0.06 |  |   |                      |                       |

| 2012-09-06    |  |   |                      |                       |

|                  | Application Note | AN41        | 908A |

|------------------|------------------|-------------|------|

|                  | Application Note | Total Pages | Page |

| Serial Interface |                  | 70          | 12   |

### ■ Register Setup Timing (continued)

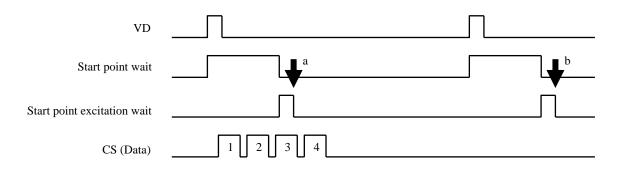

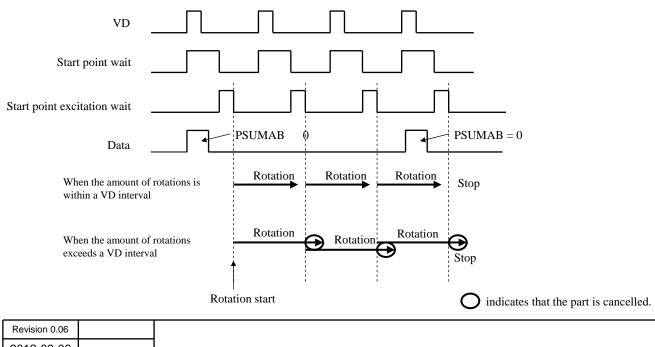

In principle, the setup of registers for micro step should be performed during the interval of start point wait (Refer to the figure in page 10). The data which is written at timing except the interval of start point wait can be also received. However, if the write operation continues after the reflecting timing such as the end of start point excitation wait, the setup reflection timing may not be performed at the intended timing (Refer to the following figure). For example, if the data 1 to 4 which is updated at the end of start point excitation wait are written as the following figure, data 1 and 2 is updated at the timing a, and data 3 and 4 is updated at the timing b. Even if the data is written continuously like this, the update timing may be shifted to 1 VD.

Due to the above reason, the setup of registers should be performed during the interval of start point wait in order to reflect the updated content certainly.

| Revision 0.06 |  |

|---------------|--|

|               |  |

| 2012-09-06    |  |

|                               | Application Note | AN41        | 908A |

|-------------------------------|------------------|-------------|------|

|                               | Application Note | Total Pages | Page |

| VD Signal Internal Processing |                  | 70          | 13   |

### VD signal internal processing

### ■ Specifications

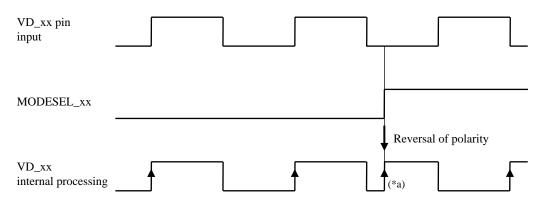

In this LSI, reflection timing and rotation timing of a stepping motor are based on the rising edge of VD\_IS and VD\_FZ respectively. The polarities of VD\_IS and VD\_FZ which are used for the internal processing can be set by the following setup.

### ■ Register detail description

- MODESEL\_IRIS (VD\_IS polarity selection)

- MODESEL\_FZ (VD\_FZ polarity selection)

| A   | Addres | s   |     | 0Bh |        | lni   | tial Val | ue     |    | 0  |    |    |    |    |    |

|-----|--------|-----|-----|-----|--------|-------|----------|--------|----|----|----|----|----|----|----|

| D15 | D14    | D13 | D12 | D11 | D10    | D9    | D8       | D7     | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|     |        |     |     | М   | DDESEI | _IRIS | MODE     | SEL_FZ |    |    |    |    |    |    |    |

MODESEL\_IRIS and MODESEL\_FZ respectively set the polarities of VD\_IS and VD\_FZ signals which is input to this IC.

When setting to "0", the polarity is based on the rising edge of VD\_xx inputted.

When setting to "1", the polarity is based on the falling edge of VD\_xx inputted.

MODESEL\_xx selects the polarity of VD\_xx inputted. Therefore, depending on the selection timing of MODESEL\_xx, the timing which is not related to the edge (\*a) of VD\_xx which is input as the following figure may be regarded as an edge.

| Setup value | VD polarity   |

|-------------|---------------|

| 0           | Non-inverting |

| 1           | Inverting     |

Based on the rising edge of VD\_xx internal processing

| Revision 0.06 |  |

|---------------|--|

|               |  |

| 2012-09-06    |  |

|                             | A mark and a mark a | AN41        | 908A |

|-----------------------------|---------------------|-------------|------|

|                             | Application Note    | Total Pages | Page |

| Micro Stepping Motor Driver | , -                 | 70          | 14   |

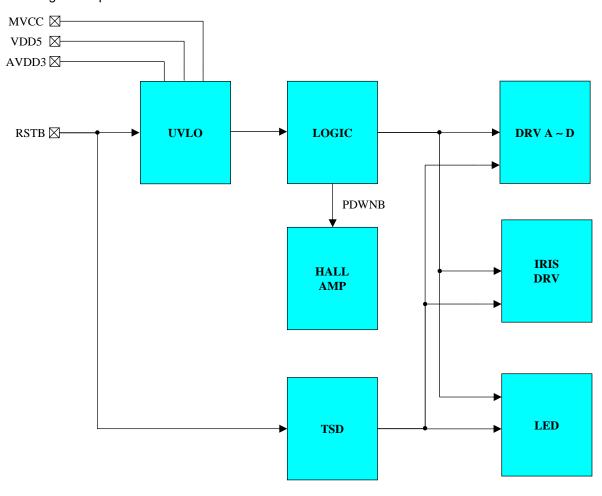

### Micro Stepping Motor Driver

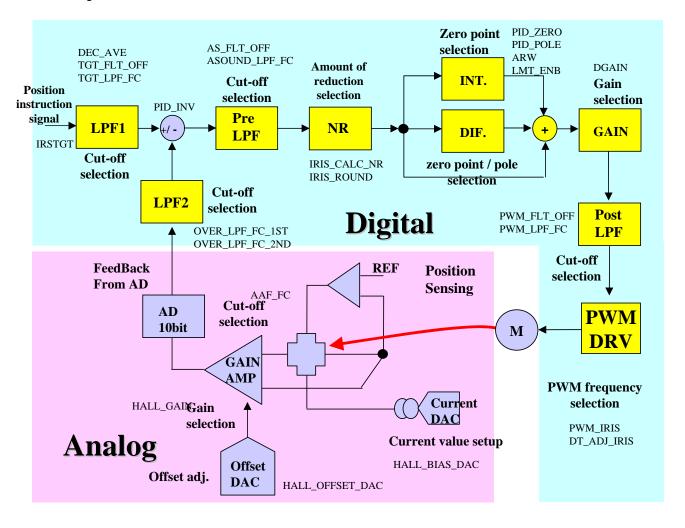

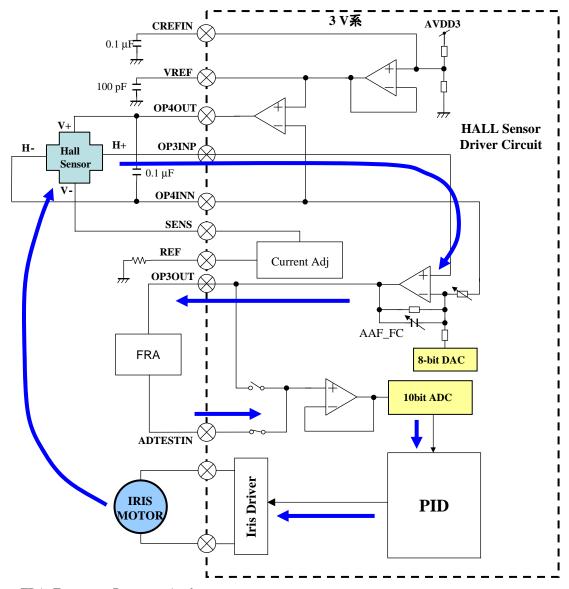

### ■ Block Diagram

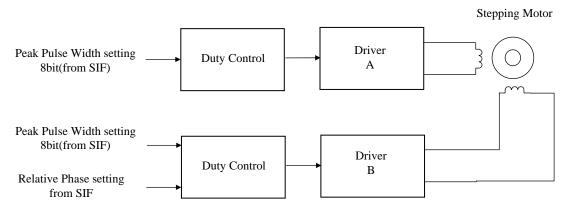

- •This block is a stepping motor driver for focus and zoom, and the following setup can be performed by serial control. (The following description is for  $\alpha$  motor: driver A/B.  $\beta$  motor: driver C/D is the same function as  $\alpha$  motor.)

- •Main setup parameters

- 1) Phase correction : The phase difference between a driver A and a driver B is on the basis of 90 degree, and can be adjusted from -22.5 degree to +21.8 degree. • • PHMODAB[5:0]

- 2) Amplitude correction : It is possible to set the load current of driver A/B independently. • PPWA[7:0] , PPWB[7:0]

- 3) PWM frequency: PWM driver chopping frequency is set. • PWMMODE[4:0] , PWMRES[1:0]

- 4) Quasi-sine wave: Number of divisions can be set to 64, 128 and 256. ••• MICROAB[1:0]

- 5) Stepping cycle: Motor rotation speed is set. The rotation speed is constant regardless of number of divisions of quasi-sine wave.

· · · INTCTAB[15:0]

### ■ Electrical Characteristics at AVDD5, MVCCx = 4.8 V, DVDD, AVDD3 = 3.1 V Notes) T<sub>a</sub> = 25°C±2°C unless otherwise specified.

| Nia   | Downston                     | Cruss book          | Conditions  |     | I Imit |     |      |  |

|-------|------------------------------|---------------------|-------------|-----|--------|-----|------|--|

| No.   | Parameter                    | Symbol              | Conditions  | Min | Тур    | Max | Unit |  |

| Motor | Motor driver 1 (Focus, Zoom) |                     |             |     |        |     |      |  |

| 1     | 1 H bridge ON-resistance     |                     | IM = 100 mA | _   | _      | 2.5 | Ω    |  |

| 2     | H bridge leak current        | I <sub>leakFZ</sub> | _           | _   | _      | 0.8 | μΑ   |  |

| Revision 0.06 | l |

|---------------|---|

|               |   |

| 2012-09-06    | İ |

|                             | Application Note | AN41        | 908A |

|-----------------------------|------------------|-------------|------|

|                             | Application Note | Total Pages | Page |

| Micro Stepping Motor Driver |                  | 70          | 15   |

### ■ Setup Timing for Each Setup

Setup timing and number of times are shown as follows.

Since the setups for address 27h to 2Ah are the same as those of 22h to 25h, the descriptions for address 27h to 2Ah are omitted. If each setup is set once, the setup is reflected at every VD pulses. Therefore, when the same setup is performed at two or more VD pulses, it is unnecessary to write at every VD pulse.

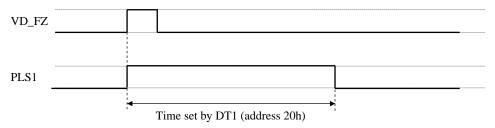

### DT1[7:0] (Start point wait, Address 20h)

Update timing is set. After hard reset release (Pin 39 RSTB: Low → High), this setup should be performed before starting to excite and drive a motor.

Since this setup is updated by the start of VD, it is unnecessary to write during the start point wait.

### PWMMODE[4:0], PWMRES[1:0] (Micro step output PWM frequency setup, Address 20h)

Micro step output PWM frequency is set. After hard reset release (Pin 39 RSTB: Low to High), this setup should be performed before starting to excite and drive a motor (DT1 ends).

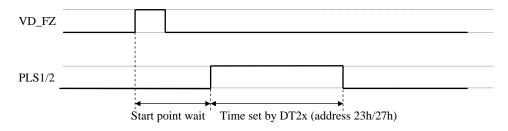

### DT2A[7:0] (Start point excitation wait, Address 22h)

Updated timing is set. After hard reset release (Pin 39 RSTB : Low → High), this setup should be performed before starting to excite and drive a motor (DT1 ends).

### PHMODAB[5:0] (Phase correction, Address 22h)

The correlation phase difference between coil A and B is corrected, and the driving noise is reduced. Since the amount of suitable phase correction depends on the rotation direction or rotation speed, the change of this setup should be performed simultaneously with the changes of the rotations direction (CCWCWAB) or rotation speed (INTCTAB), or it should be performed when a motor does not rotate.

### PPWA[7:0], PPWB[7:0] (Peak pulse width, Address 23h)

PWM maximum duty is set. This setup should be performed before starting to excite and drive a motor (DT1 ends).

#### PSUMAB[7:0] (Step count number, Address 24h)

The amount of motor rotations in 1 VD interval is set.

Every time VD pulse is input, the motor keeps rotating depending on the amount of rotations. Therefore, set to "0" in order to stop rotation of the motor.

When the amount of rotations which exceeds 1 VD interval is set, the amount of rotations of a part which exceeds 1 VD interval is cancelled.

# Application Note Application Note AN41908A Total Pages Page 70 16

### ■ Setup Timing of Each Setup (continued)

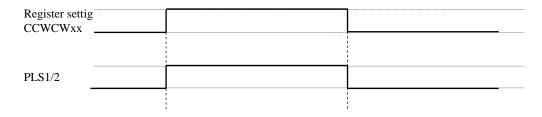

#### CCWCWAB (Rotation direction, Address 24h)

Rotation direction is set. This setup should be performed just before switching the rotation direction.

### BRAKEAB (Brake setup, Address 24h)

A current is set to 0 by braking. Since it becomes impossible to get the excitation position of a motor by braking, this setup should not be preformed except for the case of stopping immediately.

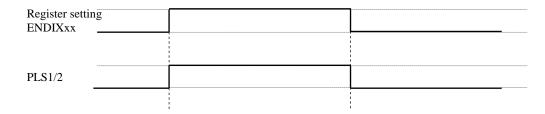

#### ENDISAB (Motor enable/disable setup, Address 24h)

Enable of a motor is set. Since a motor pin is Hi-Z when it is set to "Disable", do not set to "Disable" while a motor keeps rotating.

### LEDA (LED setup, Address 24h)

LED ON/OFF is set. The setup is performed at the falling edge of CS.

(It is understood that it is not related to driving a motor. It is possible to turn ON/OFF independently.)

### MICROAB[1:0] (Number of sine wave divisions, Address 24h)

Number of sine wave divisions is set. Even if this setup is changed, the amount of rotations and rotation speed do not vary. If only the control which the number of divisions varies depending on the rotation speed is not performed, the problem dose not occur if it is set once after hard reset release (Pin 39 RSTB: Low  $\rightarrow$  High).

#### INTCTAB[15:0] (Pulse cycle, Address 25h)

Pulse cycle is set. Rotation speed is determined by this setup.

| Revision 0.06 |  |

|---------------|--|

| 2012-09-06    |  |

# Application Note Application Note AN41908A Total Pages Page 70 17

### How to adjust register setting for micro stepping motor driver

In order to control lens, it is required to set motor rotation speed and amount of rotation per VD. Register settings relating to speed and amount of rotation are:

INTCTxx[15:0]: set time of each step (that is, the rotation speed)

PSUMxx[7:0]: amount of rotation per VD period

When driving the motor continuously for several VD period, it is best to match rotation time (per VD) to VD period. Below is a method to calculate INTCTxx[15:0] and PSUMxx[7:0] for smooth motor rotation.

1) Calculate INTCTxx[15:0] from desired rotation speed.

INTCTxx[15:0]  $\times$  768 = OSCIN frequency / rotation frequency

2) Calculate PSUMxx[7:0] from INTCTxx[15:0]. Round off if the result of PSUMxx[7:0] is not integer. When the below equation is satisfied, the rotation time is equal to VD period, and smooth rotation is realized.

$INTCTxx[15:0] \times PSUMxx[7:0] \times 24 = OSCIN frequency / VD frequency$

3) If PSUMxx[7:0] is rounded off, recalculate INTCTxx[15:0] from the equation in 2).

Example) OSCIN frequency = 27 MHz, VD frequency = 60 Hz

Calculate PSUMxx[7:0] and INTCTxx[15:0] to rotate motor at 800 pps (1-2 phase).

800 pps = 100 Hz, so from equation in 1),

$INTCTxx[15:0] = 27 \text{ MHz} / (100 \text{ Hz} \times 768) = 352$

Next, calculate PSUMxx[7:0] from equation in 2):

$PSUMxx[7:0] = 1/(60 \text{ Hz}) \times 27 \text{ MHz} / (352 \times 24) = 53$

Since PSUMxx[7:0] is rounded off, recalculate INTCTxx[15:0] from equation in 2):

$INTCTxx[15:0] = 1/(60 \text{ Hz}) \times 27 \text{ MHz} / (53 \times 24) = 354$

Refer to pages 23 and 28 for detail of PSUMxx[7:0] and INTCTxx[15:0].

If the value of left-hand side in 2) is smaller than right-hand side, the rotation time will be shorter than VD period and will cause discontinuous rotation. If left-hand side is smaller, the rotation time that exceeds 1 VD will be cancelled.

| Revision 0.06 |  |

|---------------|--|

|               |  |

| 2012-09-06    |  |

|                             | A south a Care Night | AN41        | 908A |

|-----------------------------|----------------------|-------------|------|

|                             | Application Note     | Total Pages | Page |

| Micro Stepping Motor Driver |                      | 70          | 18   |

### ■ Detail descriptions of register

### • DT1[7:0] (Start point wait time)

| Address |     | 20h |     |     | lni | tial Val | lue 0Ah |          |    |    |    |    |    |    |    |

|---------|-----|-----|-----|-----|-----|----------|---------|----------|----|----|----|----|----|----|----|

| D15     | D14 | D13 | D12 | D11 | D10 | D9       | D8      | D7       | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|         |     |     |     |     |     |          |         | DT1[7:0] |    |    |    |    |    |    |    |

DT1[7:0] sets the delay time (start point wait time) until the data written in the serial data communication sends to the output.

It becomes possible to excite a motor after a start point wait switches "1" to "0". The start point wait starts to count after the rising edge of video sync signal (VD\_FZ).

Since start point wait time is the trigger required for data acquisition, be sure to set to other than "0". When the value of register is "0", the data cannot be updated.

Refer to page 10 for the relationship of VD\_FZ and start point wait time.

| DT1 | Start point wait |

|-----|------------------|

| 0   | Prohibition      |

| 1   | 303.4 μs         |

| 255 | 77.4 ms          |

| n   | n × 8192/27 MHz  |

| Revision 0.06 |  |

|---------------|--|

|               |  |

| 2012-09-06    |  |

|                             | A soll soll so Nicks | AN41908A    |      |  |  |  |

|-----------------------------|----------------------|-------------|------|--|--|--|

|                             | Application Note     | Total Pages | Page |  |  |  |

| Micro Stepping Motor Driver |                      | 70          | 19   |  |  |  |

• DT2A[7:0] (Start point excitation wait  $\alpha$  motor)

| Address |     | 22h |     |     | Ini | tial Val | ue | 03h       |    |    |    |    |    |    |    |

|---------|-----|-----|-----|-----|-----|----------|----|-----------|----|----|----|----|----|----|----|

| D15     | D14 | D13 | D12 | D11 | D10 | D9       | D8 | D7        | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|         |     |     |     |     |     |          |    | DT2A[7:0] |    |    |    |    |    |    |    |

• DT2B[7:0] (Start point excitation wait β motor)

| Address |     | 27h |     |     | Initial Value |    |    | 03h       |    |    |    |    |    |    |    |

|---------|-----|-----|-----|-----|---------------|----|----|-----------|----|----|----|----|----|----|----|

| D15     | D14 | D13 | D12 | D11 | D10           | D9 | D8 | D7        | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|         |     |     |     |     |               |    |    | DT2B[7:0] |    |    |    |    |    |    |    |

DT2A[7:0] and DT2B[7:0] set the delay time (start point excitation wait) until  $\alpha$  motor and  $\beta$  motor start rotation. Motor rotation starts after start point excitation wait switches "1" to "0". The start point excitation wait starts to count after the falling edge of start point wait.

Since the falling edge is the trigger pulse which is required for data acquisition, be sure to input the data of other than "0". When the value of register is "0", the data cannot be updated.

Refer to page 10 for the relationship of VD\_FZ and start point excitation wait time.

| Setup value | Start point excitation wait |

|-------------|-----------------------------|

| 0           | Prohibition                 |

| 1           | 303.4 μs                    |

| 255         | 77.4 ms                     |

| n           | n × 8192/27 MHz             |

|                             | Americantina Nigra | AN41        | 908A |

|-----------------------------|--------------------|-------------|------|

|                             | Application Note   | Total Pages | Page |

| Micro Stepping Motor Driver |                    | 70          | 20   |

- Detail descriptions of register (continued)

- PWMMODE[4:0] (Micro step output PWM frequency)

| Address |     | 20h |              |     | Initial Value |    |    | 1Ch |    |    |    |    |    |    |    |

|---------|-----|-----|--------------|-----|---------------|----|----|-----|----|----|----|----|----|----|----|

| D15     | D14 | D13 | D12          | D11 | D10           | D9 | D8 | D7  | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|         |     |     | PWMMODE[4:0] |     |               |    |    |     |    |    |    |    |    |    |    |

• PWMRES[1:0] (Micro step output PWM frequency resolution)

| A   | Address |     | 20h |     |     | Initial Value |    |    | 1  |    |    |    |    |    |    |

|-----|---------|-----|-----|-----|-----|---------------|----|----|----|----|----|----|----|----|----|

| D15 | D14     | D13 | D12 | D11 | D10 | D9            | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|     | PWMRES  |     |     |     |     |               |    |    |    |    |    |    |    |    |    |

PWMMODE[4:0] sets the frequency division value of system clock, OSCIN, which is used as the standard of PWM signal for micro step output. PWMMODE[4:0] can set in the range from 1 to 31. PWM frequency at PWMMODE = 0 is the same as that at PWMMODE = 1.

PWMRES[1:0] sets the resolution of frequency division value set by PWMMODE[4:0].

PWM frequency is calculated by the following formula.

PWM frequency = OSCIN frequency / ((PWMMODE ×

$$2^3$$

) ×  $2^{PWMRES}$ )

Refer to page 32 for the specific PWM frequency set by PWMMODE[4:0] and PWMRES[1:0] at OSCIN = 27 MHz..

|                             | A collection Nicke | AN41908A    |      |  |  |

|-----------------------------|--------------------|-------------|------|--|--|

|                             | Application Note   | Total Pages | Page |  |  |

| Micro Stepping Motor Driver | • •                | 70          | 21   |  |  |

- Detail descriptions of register (continued)

- PHMODAB[5:0] (Phase correction  $\alpha$  motor)

| Address |     | 22h          |     |     | Initial Value |    |    | 0  |    |    |    |    |    |    |    |

|---------|-----|--------------|-----|-----|---------------|----|----|----|----|----|----|----|----|----|----|

| D15     | D14 | D13          | D12 | D11 | D10           | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|         |     | PHMODAB[5:0] |     |     |               |    |    |    |    |    |    |    |    |    |    |

• PHMODCD[5:0] (Phase correction β motor)

| <i>A</i> | Address |     | 27h          |     |     | Initial Value |    |    | 0  |    |    |    |    |    |    |

|----------|---------|-----|--------------|-----|-----|---------------|----|----|----|----|----|----|----|----|----|

| D15      | D14     | D13 | D12          | D11 | D10 | D9            | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|          |         |     | PHMODCD[5:0] |     |     |               |    |    |    |    |    |    |    |    |    |

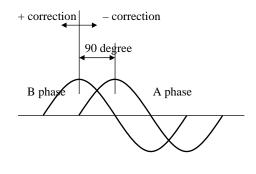

Current phase differences of  $\alpha$  motor and  $\beta$  motor shifts from 90 degree by PHMODAB[5:0] and PHMODCD[5:0] respectively. Setup resolution is 0.7 degree, and data is set in two's complement.

| PHMODAB    | Amount of phase correction    |

|------------|-------------------------------|

| 000000     | ±0 degree                     |

| 000001     | +0.70 degree                  |

| 011111     | +21.80 degree                 |

| 100000     | -22.50 degree                 |

| 111111     | -0.70 degree                  |

| Resolution | 360 degree /512 = 0.70 degree |

Stepping motor is configured so that phase difference between coils becomes 90 degree. However, the phase difference may shift from 90 degree due to the variation of a motor.

Therefore, even if phase difference in current waveform is exactly 90 degree, driving noise may occur due to the occurrence of rotation torque ripple.

This setup is for reducing the torque ripple which is occurred by the variation of a motor.

| Revision 0.06 |  |

|---------------|--|

|               |  |

| 2012-09-06    |  |

|                             | A soft of the Night | AN41908A    |      |  |  |

|-----------------------------|---------------------|-------------|------|--|--|

|                             | Application Note    | Total Pages | Page |  |  |

| Micro Stepping Motor Driver |                     | 70          | 22   |  |  |

- Detail descriptions of register (continued)

- PPWA[7:0] (Driver A peak pulse width)

- PPWB[7:0] (Driver B peak pulse width)

| l A | Addres    | s   | 23h |                   | Initial Valu |    | lue 0, 0  |    |    |    |    |    |    |  |

|-----|-----------|-----|-----|-------------------|--------------|----|-----------|----|----|----|----|----|----|--|

| D15 | D14       | D13 | D12 | D12 D11 D10 D9 D8 |              | D7 | D6        | D5 | D4 | D3 | D2 | D1 | D0 |  |

|     | PPWB[7:0] |     |     |                   |              |    | PPWA[7:0] |    |    |    |    |    |    |  |

- PPWC[7:0] (Driver C peak pulse width)

- PPWD[7:0] (Driver D peak pulse width)

| ,   | Addres    | s   | 28h |             | Initial Valu |    | ue 0,0    |    |          |  |  |    |    |    |    |

|-----|-----------|-----|-----|-------------|--------------|----|-----------|----|----------|--|--|----|----|----|----|

| D15 | D14       | D13 | D12 | D12 D11 D10 |              | D9 | D8        | D7 | D6 D5 D4 |  |  | D3 | D2 | D1 | D0 |

|     | PPWD[7:0] |     |     |             |              |    | PPWC[7:0] |    |          |  |  |    |    |    |    |

PPWA[7:0] to PPWD[7:0] set the maximum duty of PWM at the position which the currents in driver A to D are peak value respectively. The maximum duty is calculated by the following formula.

Driver X Maximum duty = PPWx / (PWMMODE

$$\times$$

8)

When PPWx = 0 is set, coil current becomes 0.

Refer to page 34 for the operation at the time when the duty exceeding 100% is set.

Example) When PPWA[7:0] = 200, PWMMODE[4:0] = 28 is set, maximum duty of driver A will be

$$200 / (28 \times 8) = 0.89$$

# Application Note Application Note AN41908A Total Pages Page 70 23

### ■ Detail descriptions of register (continued)

• PSUMAB[7:0] (α motor step count number)

| /   | Addres | s   | 24h |     | lni | tial Val | ue    | ue 0 |    |    |      |        |    |    |    |

|-----|--------|-----|-----|-----|-----|----------|-------|------|----|----|------|--------|----|----|----|

| D15 | D14    | D13 | D12 | D11 | D10 | D9       | D9 D8 |      | D6 | D5 | D4   | D3     | D2 | D1 | D0 |

|     |        |     |     |     |     |          |       |      |    | ]  | PSUM | AB[7:0 | ]  |    |    |

### • PSUMCD[7:0] (β motor step count number)

| A   | Addres | S   | 29h |     | Ini | tial Val | ue 0 |             |    |    |    |    |    |    |    |

|-----|--------|-----|-----|-----|-----|----------|------|-------------|----|----|----|----|----|----|----|

| D15 | D14    | D13 | D12 | D11 | D10 | D9       | D8   | D7          | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|     |        |     |     |     |     |          |      | PSUMCD[7:0] |    |    |    |    |    |    |    |

PSUMAB[7:0] and PSUMCD[7:0] set the number of step counts of  $\alpha$  motor and  $\beta$  motor respectively. Since the number of setup step counts is converted to 256-step inside, the amount of rotation becomes the same regardless of the number of divisions.

To stop the rotation of a motor, set PSUMxx[7:0] = 0.

| Cotting          | Number of steps    |                        |                        |  |  |  |  |  |  |

|------------------|--------------------|------------------------|------------------------|--|--|--|--|--|--|

| Setting<br>value | 64-step conversion | 128-step<br>conversion | 256-step<br>conversion |  |  |  |  |  |  |

| 0                | 0                  | 0                      | 0                      |  |  |  |  |  |  |

| 1                | 2                  | 4                      | 8                      |  |  |  |  |  |  |

| 255              | 510                | 1 020                  | 2 040                  |  |  |  |  |  |  |

| n                | 2n                 | 4n                     | 8n                     |  |  |  |  |  |  |

If maximum duty is set to other than "0" at PSUMxx[7:0] = 0, the position is held in the state of excitation. If a motor can hold the position by cogging torque without motor current, the position is held even if the maximum duty is set to 0.

Example) When PSUMAB[7:0] = 8 is set, the amount of rotation is 16 steps (64-step conversion). This is 16/64 = 1/4 of a sine wave. The amount of rotation becomes 1/4 of a sine wave also in 128 and 256-step conversion.

| Revision 0.06                                    |  |

|--------------------------------------------------|--|

| <del>                                     </del> |  |

| 2012-09-06                                       |  |

|                             | Americantina Nigra | AN41        | 908A |

|-----------------------------|--------------------|-------------|------|

|                             | Application Note   | Total Pages | Page |

| Micro Stepping Motor Driver |                    | 70          | 24   |

### $\bullet$ CCWCWAB ( $\alpha$ motor rotation direction)

| ,   | Addres | s   |     | 24h |     | Initial Value |          |   | 0  |    |    |    |    |    |    |

|-----|--------|-----|-----|-----|-----|---------------|----------|---|----|----|----|----|----|----|----|

| D15 | D14    | D13 | D12 | D11 | D10 | D9            | D9 D8 D7 |   | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|     |        |     |     |     |     | CC            | WCWA     | В |    |    |    |    |    |    |    |

### • CCWCWCD (β motor rotation direction)

| P   | Addres | s   |     | 29h |     | Initial Value |      |    | 0  |    |    |    |    |    |    |

|-----|--------|-----|-----|-----|-----|---------------|------|----|----|----|----|----|----|----|----|

| D15 | D14    | D13 | D12 | D11 | D10 | D9            | D8   | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|     |        |     |     |     |     | CC            | WCWC | D  |    |    |    |    |    |    |    |

CCWCWAB and CCWCWCD set the rotation direction of  $\alpha$  motor and  $\beta$  motor respectively. Refer to page 35 for the definition of rotation direction.

| Setup value | Motor rotation direction |

|-------------|--------------------------|

| 0           | Forward                  |

| 1           | Reverse                  |

|                             | A sull sull sur Nilston | AN41        | 908A |

|-----------------------------|-------------------------|-------------|------|

|                             | Application Note        | Total Pages | Page |

| Micro Stepping Motor Driver |                         | 70          | 25   |

### • BRAKEAB (α motor brake)

| Address |     | 24h |     |     | Initial Value |       |    |    | 0  |    |    |    |    |    |    |

|---------|-----|-----|-----|-----|---------------|-------|----|----|----|----|----|----|----|----|----|

| D15     | D14 | D13 | D12 | D11 | D10           | D9 D8 |    | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|         |     |     |     |     | В             | RAKEA | AВ |    |    |    |    |    |    |    |    |

### • BRAKECD (β motor brake)

| Address |     | 29h |     | Initial Value |     |         |    | 0  |    |    |    |    |    |    |    |

|---------|-----|-----|-----|---------------|-----|---------|----|----|----|----|----|----|----|----|----|

| D15     | D14 | D13 | D12 | D11           | D10 | D9      | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|         |     |     |     |               | В   | BRAKECD |    |    |    |    |    |    |    |    |    |

BRAKEAB and BRAKECD set the brake mode of  $\alpha$  motor and  $\beta$  motor respectively.

| Setup value | $\alpha$ motor brake |

|-------------|----------------------|

| 0           | Normal operation     |

| 1           | Brake mode           |

Both of upper-side P-ch MOSs of output H bridge turn on in brake mode. The brake mode is not used in normal operation, and is used for emergency shutdown. It is recommended to use only in abnormal state.

|                             | A sull sull sur Nilster | AN41        | 908A |

|-----------------------------|-------------------------|-------------|------|

|                             | Application Note        | Total Pages | Page |

| Micro Stepping Motor Driver |                         | 70          | 26   |

- Detail descriptions of register (continued)

- ENDISAB (α motor Enable/Disable)

| 1   | Address 24h |     | 24h |     | Initial Value |    |    |    | 0  |    |    |    |    |    |    |

|-----|-------------|-----|-----|-----|---------------|----|----|----|----|----|----|----|----|----|----|

| D15 | D14         | D13 | D12 | D11 | D10           | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|     |             |     |     |     | ENDIS         | AB |    |    |    |    |    |    |    |    |    |

• ENDISCD (β motor Enable/Disable)

| Address |     | 29h |     |     | Initial Value |    |    |    | 0  |    |    |    |    |    |    |

|---------|-----|-----|-----|-----|---------------|----|----|----|----|----|----|----|----|----|----|

| D15     | D14 | D13 | D12 | D11 | D10           | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|         |     |     |     |     | ENDIS         | CD |    |    |    |    |    |    |    |    |    |

ENDISAB and ENDISCD configure the setting for output stage control of  $\alpha$  motor and  $\beta$  motor respectively. The output becomes the state of OFF (Hi-Z) at ENDISxx = 0. However, internal excitation position counter keeps counting even ENDISxx = 0. Therefore, when stopping the motor during normal operation, set PSUMxx[7:0] = 0 (not ENDISxx = 0).

| Setup value | Motor output condition |

|-------------|------------------------|

| 0           | Output OFF (Hi-Z)      |

| 1           | Output ON              |

| Revision 0.06 |  |

|---------------|--|

|               |  |

| 2012-09-06    |  |

|                             | Annella a Care Nia ta | AN41        | 908A |

|-----------------------------|-----------------------|-------------|------|

|                             | Application Note      | Total Pages | Page |

| Micro Stepping Motor Driver |                       | 70          | 27   |

- Detail descriptions of register (continued)

- $\bullet$  MICROAB[1:0] ( $\alpha$  motor quasi-sin wave division number)

| Address |     | 24h     |             | Initial Value |    |    |    | 0        |  |    |    |    |    |  |  |

|---------|-----|---------|-------------|---------------|----|----|----|----------|--|----|----|----|----|--|--|

| D15     | D14 | D13     | D12 D11 D10 |               | D9 | D8 | D7 | D6 D5 D4 |  | D3 | D2 | D1 | D0 |  |  |

|         |     | MICROAB |             |               |    |    |    |          |  |    |    |    |    |  |  |

• MICROCD[1:0] (β motor quasi-sine wave division number)

| A   | Addres | S       |     | 29h |     | Ini | tial Val | ue |    | 0  |    |    |    |    |    |

|-----|--------|---------|-----|-----|-----|-----|----------|----|----|----|----|----|----|----|----|

| D15 | D14    | D13     | D12 | D11 | D10 | D9  | D8       | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|     |        | MICROCD |     |     |     |     |          |    |    |    |    |    |    |    |    |

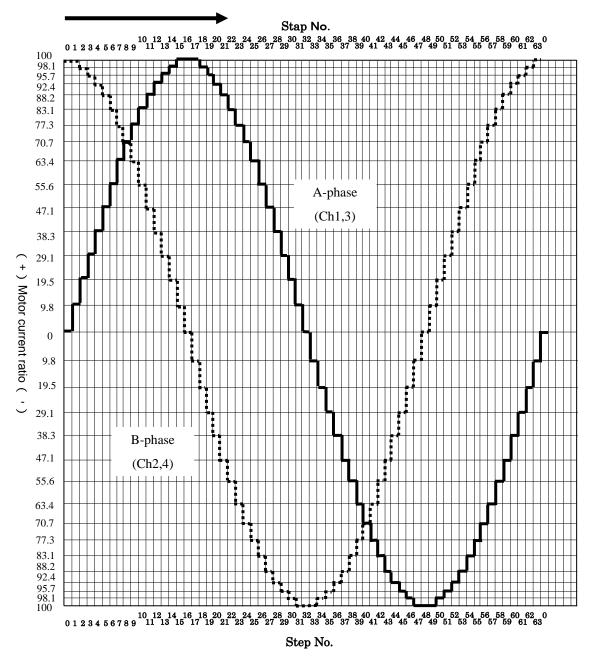

MICROAB[1:0] and MICROCD[1:0] set the number of quasi-sine wave divisions for  $\alpha$  motor and  $\beta$  motor respectively. Waveform example for 64 divisions is on page 35.

| MICROAB | Number of divisions |

|---------|---------------------|

| 00      | 256                 |

| 01      | 256                 |

| 10      | 128                 |

| 11      | 64                  |

| Revision 0.06 |  |

|---------------|--|

| 2012-09-06    |  |

# Application Note Application Note AN41908A Total Pages Page 70 28

### ■ Detail descriptions of register (continued)

• INTCTAB[15:0] (α motor step cycle setup)

| A             | Addres | s   |     | 25h |     | Ini | tial Val | ue |          | 0080h |    |    |    |    |  |

|---------------|--------|-----|-----|-----|-----|-----|----------|----|----------|-------|----|----|----|----|--|

| D15           | D14    | D13 | D12 | D11 | D10 | D9  | D8       | D7 | D6 D5 D4 |       | D3 | D2 | D1 | D0 |  |

| INTCTAB[15:0] |        |     |     |     |     |     |          |    |          |       |    |    |    |    |  |

• INTCTCD[15:0] (β motor step cycle setup)

| ,   | Addres        | s   |     | 2Ah |     | Ini | tial Va | lue |    | 0080h |    |    |    |    |    |

|-----|---------------|-----|-----|-----|-----|-----|---------|-----|----|-------|----|----|----|----|----|

| D15 | D14           | D13 | D12 | D11 | D10 | D9  | D8      | D7  | D6 | D5    | D4 | D3 | D2 | D1 | D0 |

|     | INTCTCD[15:0] |     |     |     |     |     |         |     |    |       |    |    |    |    |    |

INTCTAB[15:0] and INTCDCD[15:0] set the step cycle of  $\alpha$  motor and  $\beta$  motor respectively. Since the step cycle is converted to 64-step inside, motor rotation speed becomes the same regardless of the number of divisions set by MICROxx[1:0].

| Cotus value |            | Step cycle |           |

|-------------|------------|------------|-----------|

| Setup value | 64-step    | 128-step   | 256-step  |

| 0           | 0          | 0          | 0         |

| 1           | 444 ns     | 222 ns     | 111 ns    |

| Max         | 29.1 ms    | 14.6 ms    | 7.3 ms    |

| n           | 12n/27 MHz | 6n/27 MHz  | 3n/27 MHz |

If maximum duty is set to other than "0" at INTCTxx[15:0] = 0, the position is held in the state of excitation. If a motor can hold the position by cogging torque without motor current, the position is held even if the maximum duty is set to 0.

e. g.) If ITCTAB[15:0] = 400 is set, time of 1 step for 64-step is

$12 \times 400 / 27 \text{ MHz} = 0.178 \text{ ms}$

Therefore, period of one sinusoidal wave cycle is 11.4 ms (87.9 Hz).

This is the same for 128-step and 256-step.

|                             | Americantian Nigton | AN41908A    |      |  |

|-----------------------------|---------------------|-------------|------|--|

|                             | Application Note    | Total Pages | Page |  |

| Micro Stepping Motor Driver | • •                 | 70          | 29   |  |

### • FZTEST[4:0] (Test signal output setup)

| -   | Addres | s   |     | 21h |     | Ini | tial Val | lue |    | 0  |             |    |    |    |    |

|-----|--------|-----|-----|-----|-----|-----|----------|-----|----|----|-------------|----|----|----|----|

| D15 | D14    | D13 | D12 | D11 | D10 | D9  | D8       | D7  | D6 | D5 | D4          | D3 | D2 | D1 | D0 |

|     |        |     |     |     |     |     |          |     |    |    | FZTEST[4:0] |    |    |    |    |

FZTEST[4:0] makes a choice of the test signal which is output to PLS1 and PLS2 pins.

TESTEN1 (0Bh) and TESTEN2 (21h) should be set to "1" in order to enable the test signal.

Since the test signal used in our company is output, do not set other than the setups described in the following table.

| Setup | Step                          | cycle                         | Description                                                    |

|-------|-------------------------------|-------------------------------|----------------------------------------------------------------|

| value | PLS1                          | PLS2                          | Description                                                    |

| 0     | PLS1                          | PLS2                          | Pulse 1/2 normal function                                      |

| 1     | Start point wait              | 0                             | "H" output during start point wait                             |

| 2     | Start point excitation wait A | Start point excitation wait B | "H" output during start point excitation wait                  |

| 3     | ENDISAB                       | ENDISCD                       | ENDISxx setting                                                |

| 4     | CCWCWAB                       | CCWCWCD                       | CCWCWxx setting                                                |

| 5     | Pulse output monitor A        | Pulse output monitor<br>B     | During motor rotation, "H"/"L" changes at the speed of 64-step |

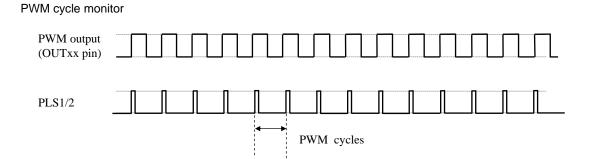

| 6     | PWM cycle monitor             | 0                             | PWM frequency signal for micro step                            |

| 7     | Pulse completion output A     | Pulse completion output B     | "H" output during motor rotation                               |

Waveform for each test signal is described below.

### Start point wait

| Revision 0.06 |  |

|---------------|--|

| 2012-09-06    |  |

|                             | A sull sull sur Nilster | AN41        | 908A |

|-----------------------------|-------------------------|-------------|------|

|                             | Application Note        | Total Pages | Page |

| Micro Stepping Motor Driver |                         | 70          | 30   |

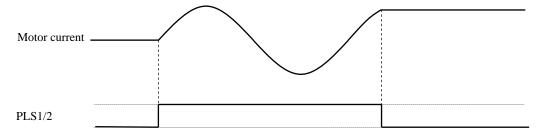

### Start point excitation wait

### **ENDISxx**

### **CCWCWxx**

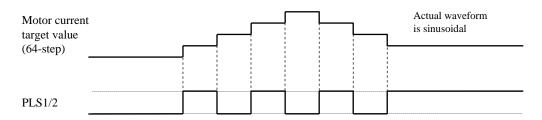

### Pulse output monitor

For 128-step and 256-step, "H"/"L" of PLS1/2 changes every 2 and 4 steps respectively.

| Revision 0.06 |  |

|---------------|--|

| 2012-09-06    |  |

|                             | A P C Nl . ( .   | AN41        | 908A |

|-----------------------------|------------------|-------------|------|

|                             | Application Note | Total Pages | Page |

| Micro Stepping Motor Driver |                  | 70          | 31   |

### Pulse completion output

### • TESTEN1 (Test setting 1)

| A   | Addres | s   |     | 0Bh |     | Ini | tial Val | ue    |    | 0  |    |    |    |    |    |

|-----|--------|-----|-----|-----|-----|-----|----------|-------|----|----|----|----|----|----|----|

| D15 | D14    | D13 | D12 | D11 | D10 | D9  | D8       | D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|     |        |     |     |     |     |     | Т        | ESTEN | 1  |    |    |    |    |    |    |

### • TESTEN2 (Test setting 2)

| A   | Addres | s   |     | 21h |     | Ini | tial Val | ue    |    | 0  |    |    |    |    |    |

|-----|--------|-----|-----|-----|-----|-----|----------|-------|----|----|----|----|----|----|----|

| D15 | D14    | D13 | D12 | D11 | D10 | D9  | D8       | D7    | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|     |        |     |     |     |     |     | Т        | ESTEN | 2  |    |    |    |    |    |    |

By setting TESTEN1=TESTEN2=1, above PLS1(37pin) and PLS2(38pin) test signal output is available. Also, some settings can be used.

| Revision 0.06 |  |

|---------------|--|

|               |  |

| 2012-09-06    |  |

|                             | A L C N          | AN41        | 908A |

|-----------------------------|------------------|-------------|------|

|                             | Application Note | Total Pages | Page |

| Micro Stepping Motor Driver |                  | 70          | 32   |

### ■ PWM frequency setup

PWM frequency for OSCIN = 27 MHz is shown in below table.

| DIAMANAODE |        | PWMRES |       |

|------------|--------|--------|-------|

| PWMMODE    | 0      | 1      | 2     |

| 1          | 3375.0 | 1687.5 | 843.8 |

| 2          | 1687.5 | 843.8  | 421.9 |

| 3          | 1125.0 | 562.5  | 281.3 |

| 4          | 843.8  | 421.9  | 210.9 |

| 5          | 675.0  | 337.5  | 168.8 |

| 6          | 562.5  | 281.3  | 140.6 |

| 7          | 482.1  | 241.1  | 120.5 |

| 8          | 421.9  | 210.9  | 105.5 |

| 9          | 375.0  | 187.5  | 93.8  |

| 10         | 337.5  | 168.8  | 84.4  |

| 11         | 306.8  | 153.4  | 76.7  |

| 12         | 281.3  | 140.6  | 70.3  |

| 13         | 259.6  | 129.8  | 64.9  |

| 14         | 241.1  | 120.5  | 60.3  |

| 15         | 225.0  | 112.5  | 56.3  |

| 16         | 210.9  | 105.5  | 52.7  |

| 17         | 198.5  | 99.3   | 49.6  |

| 18         | 187.5  | 93.8   | 46.9  |

| 19         | 177.6  | 88.8   | 44.4  |

| 20         | 168.8  | 84.4   | 42.2  |

| 21         | 160.7  | 80.4   | 40.2  |

| 22         | 153.4  | 76.7   | 38.4  |

| 23         | 146.7  | 73.4   | 36.7  |

| 24         | 140.6  | 70.3   | 35.2  |

| 25         | 135.0  | 67.5   | 33.8  |

| 26         | 129.8  | 64.9   | 32.5  |

| 27         | 125.0  | 62.5   | 31.3  |

| 28         | 120.5  | 60.3   | 30.1  |

| 29         | 116.4  | 58.2   | 29.1  |

| 30         | 112.5  | 56.3   | 28.1  |

| 31         | 108.9  | 54.4   | 27.2  |

(kHz)

# Application Note Application Note AN41908A Total Pages Page 70 33

### ■ PWM frequency setup and Maximum duty setup

The setups method example of PWM frequency and maximum duty are shown as follows.

### • PWM frequency setup

PWM frequency is calculated by the following formula with PWMMODE[4:0] and PWMRES[1:0] as shown in page 20 of this book.

PWM frequency = OSC frequency / ((PWMMODE

$$\times 2^3$$

)  $\times 2^{PWMRES}$ )

PWM frequency corresponding to the each setup value of PWMMODE and PWMRES is shown in page 28 of this book. Note that there may be two kinds of combination of the setup value corresponding to PWM frequency. For example, there are two kinds of setup to realize that PWM frequency is 56.3 kHz.

$$\begin{aligned} & PWMMODE = 30 \text{ , } PWMRES = 1 \\ & PWMMODE = 15 \text{ , } PWMRES = 2 \end{aligned}$$

In such a case, PWMMODE should be set so that it is a larger value as described hereinbelow.

### Maximum duty setup

PWM output maximum duty is calculated by the following formula as shown in page 22 of this book.

Maximum duty =

$$PPWx / (PWMMODE \times 8)$$

For example, when PWM frequency is set as follows,

PWMMODE = 30 , PWMRES = 1

$$\rightarrow$$

PWM frequency = 56.3 kHz maximum duty becomes the following value by setting to PPWx = 200. 200 / (30 × 8) = 0.83

Since resolution of sine wave amplitude is determined by PPW setup, PWMMODE should be also set to as large a value as possible so that PPW becomes as large as possible.

| Revision 0.06 |  |

|---------------|--|

| 0040 00 00    |  |

| 2012-09-06    |  |

|                             | A sollow Com Night | AN41        | 908A |

|-----------------------------|--------------------|-------------|------|

|                             | Application Note   | Total Pages | Page |

| Micro Stepping Motor Driver |                    | 70          | 34   |

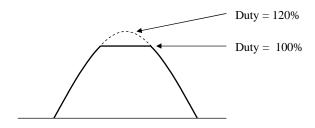

### ■ Peak duty setup which exceeds 100%

PWM maximum duty at peak position of micro step current is determined by PWMMODE[4:0] and PPWx[7:0].

$$Maximum \ duty = PPWx \ / \ (PWMMODE \times 8)$$

Maximum duty may exceed 100% depending on the setup values of PWMMODE and PPWx.

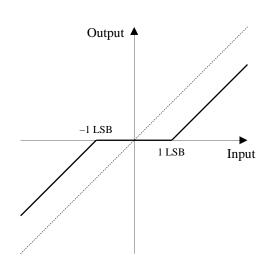

Since the duty does not certainly exceed 100% at PWM operation in this case, the peak point of sine wave (current waveform) becomes flat as follows.

Example 1 ) When PWMMODE =

$$10$$

, PPWx =  $96$ ,

Maximum duty =

$$96 / (10 \times 8) = 120\%$$

The target current waveform is indicated as the following full line.

Example 2 ) When PWMMODE = 5, PPWx = 255,

Maximum duty =

$$255 / (5 \times 8) = 638\%$$

The target current waveform becomes close to 2-phase drive.

## **Application Note**

| AN41908A    |      |  |  |  |  |

|-------------|------|--|--|--|--|

| Total Pages | Page |  |  |  |  |

| 70          | 35   |  |  |  |  |

Micro Stepping Motor Driver

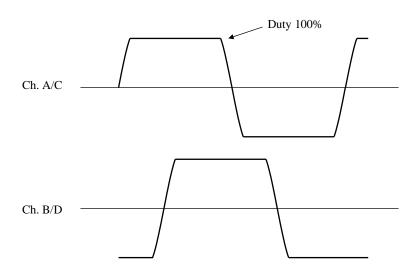

### Micro step drive (64-step)

### (1) Forward rotation

The direction of current which flows into OUTx2 pin from OUTx1 pin is defined as positive direction.

|                            | A sull sull sur Nilster | AN41908A    |      |  |

|----------------------------|-------------------------|-------------|------|--|

|                            | Application Note        | Total Pages | Page |  |

| Reset / Protection Circuit |                         | 70          | 36   |  |

### Reset / Protection circuit

### ■ Block Diagram / Specifications

Stop direction (Enable  $\rightarrow$  Disable) is shown as above. The specifications are shown as follows.

|                                     | COMMON  | HALL_AMP                 | FZ output | Iris output                | LED |

|-------------------------------------|---------|--------------------------|-----------|----------------------------|-----|

| RSTB pin                            | Disable | Logic reset<br>→ Disable |           |                            |     |

| Thermal shutdown (TSD)              | ×       | ×                        |           | Output OFF                 |     |

| Under-voltage<br>lock-out<br>(UVLO) | ×       | Logic reset<br>→ Disable | Logic     | $reset \rightarrow Output$ | OFF |

Note 1 ×: Don't care

Note 2 The protection circuit is for maintaining safety against abnormal operation. Therefore, the protection circuit should not work during normal operation.

Especially for the thermal protection circuit, if the area of safe operation or the absolute maximum rating is momentarily exceeded due to output pin to  $V_{CC}$  short (Power supply fault), or output pin to GND short (Ground fault), the LSI might be damaged before the thermal protection circuit could operate.

| Revision 0.06                                    |  |

|--------------------------------------------------|--|

| <del>                                     </del> |  |

| 2012-09-06                                       |  |

# Application Note Application Note AN41908A Total Pages Page 70 37

■Electrical Characteristics (Reference values for design) at AVDD5, MVCCx = 4.8 V, DVDD, AVDD3 = 3.1 V Notes)  $T_a = 25$ °C±2°C unless otherwise specified.

The characteristics listed below are reference values derived from the design of the IC and are not guaranteed by inspection. If a problem does occur related to these characteristics, we will respond in good faith to user concerns.

| NI-       | No. Parameter Symbol Conditions                |                       | erence values |     | 1.1:4 |     |      |

|-----------|------------------------------------------------|-----------------------|---------------|-----|-------|-----|------|

| NO.       | Parameter                                      | Symbol                | Conditions    | Min | Тур   | Max | Unit |