**Table 1. Electrical Characteristics (continuous)**

| Parameters                       | Symbol   | Min. | Тур.         | Max.          | Unit      | Condition                                                                                         |  |

|----------------------------------|----------|------|--------------|---------------|-----------|---------------------------------------------------------------------------------------------------|--|

| LVCMOS Output Characteristics    |          |      |              |               |           |                                                                                                   |  |

| Duty Cycle                       | DC       | 45   | ı            | 55            | %         |                                                                                                   |  |

| Rise/Fall Time <sup>[3]</sup>    | T_r, T_f | -    | 4            | 8             | ns        | Vdd = 1.8 V, 20% - 80%. Contact SiTime for other programmable rise/fall options                   |  |

|                                  |          | -    | ı            | 8             | ns        | Vdd = 2.25 V to 3.63 V, 20% - 80%. Contact SiTime for other programmable rise/fall options        |  |

| Output High Voltage              | VOH      | 90%  | -            | -             | VDD       | IOH = -0.5 mA (Vdd = 1.8 V)<br>IOH = -1.2 mA (Vdd = 2.25 V to 3.63 V)                             |  |

| Output Low Voltage               | VOL      | -    | -            | 10%           | VDD       | IOL = 0.5 mA (Vdd = 1.8 V)<br>IOL = 1.2 mA (Vdd = 2.25 V to 3.63 V)                               |  |

|                                  |          |      | Inpu         | t Characteris | tics      |                                                                                                   |  |

| Input High Voltage               | VIH      | 80%  | _            | _             | VDD       |                                                                                                   |  |

| Input Low Voltage                | VIL      | _    | _            | 20%           | VDD       |                                                                                                   |  |

| Input Slew Rate                  | In-slew  | 10   | ı            | ı             | V/µs      |                                                                                                   |  |

| Input Pull-down Impedance        | Z_in     | 300  | ı            | ı             | kΩ        | Active mode (ST pin = LOW), Vdd = 1.8 V                                                           |  |

|                                  |          | 270  | ı            | ı             | kΩ        | Active mode (ST pin = LOW), Vdd = 2.25 V to 3.63 V                                                |  |

|                                  |          | 2.5  | -            | -             | МΩ        | Standby mode (ST pin = HIGH), Vdd = 1.8 V                                                         |  |

|                                  |          | 1.3  | ı            | ı             | ΜΩ        | Standby mode (ST pin = HIGH), Vdd = 2.25 V to 3.63 V                                              |  |

|                                  |          | S    | tartup, Star | dby and Res   | ume Timin | g                                                                                                 |  |

| Startup Time                     | T_start  | -    | 75           | 150           | ms        | Measured from the time VDD reaches 90% of its final value                                         |  |

| Standby Time                     | T_stdby  | -    | Ī            | 20            | μs        | Measured from the time ST pin crosses 50% threshold                                               |  |

| Resume Time                      | T_resume | -    | 2            | 3             | ms        | Measured from the time ST pin crosses 50% threshold                                               |  |

| Jitter                           |          |      |              |               |           |                                                                                                   |  |

| RMS Period Jitter <sup>[3]</sup> | T_jitt   | _    | 75           | 110           | ps        | f = 6.144 MHz, Vdd = 1.8 V                                                                        |  |

|                                  |          | -    | -            | 110           | ps        | f = 6.144 MHz, Vdd = 2.25 V to 3.63 V                                                             |  |

| RMS Phase Jitter <sup>[3]</sup>  | T_phj    | _    | 0.8          | 2.5           | ns        | f = 6.144 MHz, Vdd = 1.8 V,<br>Integration bandwidth = 100 Hz to 40 kHz <sup>[2]</sup>            |  |

|                                  |          | -    | -            | 2.5           | ns        | f = 6.144 MHz, Vdd = 2.25 V to 3.63 V,<br>Integration bandwidth = 100 Hz to 40 kHz <sup>[2]</sup> |  |

#### Notes:

- 1. Current consumption with load is a function of the output frequency and output load. For any given output frequency, the capacitive loading will increase current consumption equal to C\_load\*VDD\*f(MHz).

- 2. Max spec inclusive of 25 mV peak-to-peak sinusoidal noise on VDD. Noise frequency 100 Hz to 20 MHz.

- 3. Refer to the performance plot section for typical values at 2.5, 2.8, 3.0 and 3.3 V condition

# **Table 2. Pin Description**

| Pin | Symbol | Functionality |                                                                                                                                    |  |

|-----|--------|---------------|------------------------------------------------------------------------------------------------------------------------------------|--|

| 1   | ST     | Input         | L: Specified frequency output H: Output is low (weak pull down). Device goes to the standby mode. Supply current reduces to I_std. |  |

| 2   | OUT    | Output        | LVCMOS clock output                                                                                                                |  |

| 3   | VDD    | Power         | Supply voltage. Bypass with a 0.01 µF X7R capacitor.                                                                               |  |

| 4   | GND    | Power         | Connect to ground                                                                                                                  |  |

## **Top View**

Figure 1. Pin Assignments

# **Table 3. Absolute Maximum Limits**

Attempted operation outside the absolute maximum ratings may cause permanent damage to the part. Actual performance of the IC is only guaranteed within the operational specifications, not at absolute maximum ratings.

| Parameter                                                            | Test Condition        | Value        | Unit |

|----------------------------------------------------------------------|-----------------------|--------------|------|

| Continuous Power Supply Voltage Range (VDD)                          |                       | -0.5 to 3.63 | V    |

| Short Duration Maximum Power Supply Voltage (VDD)                    | <30 seconds           | 4.0          | V    |

| Continuous Maximum Operating Temperature                             |                       | 105          | °C   |

| Short Duration Maximum Operating Temperature                         | ≤30 seconds           | 125          | °C   |

| Human Body Model (HBM) ESD Protection                                | JESD22-A115           | 2000         | V    |

| Charge-Device Model (CDM) ESD Protection                             | JESD22-C101           | 750          | V    |

| Machine Model (MM) ESD Protection                                    | T <sub>A</sub> = 25°C | 200          | V    |

| Latch-up Tolerance                                                   | JESD.                 | 78 Compliant |      |

| Mechanical Shock Resistance                                          | MII 883, Method 2002  | 10,000       | g    |

| Mechanical Vibration Resistance                                      | MII 883, Method 2007  | 70           | g    |

| 1508 CSP Junction Temperature                                        |                       | 150          | °C   |

| Storage Temperature                                                  |                       | -65 to 150   | °C   |

| Soldering Temperature (follow standard Pb free soldering guidelines) | _                     | 260          | °C   |

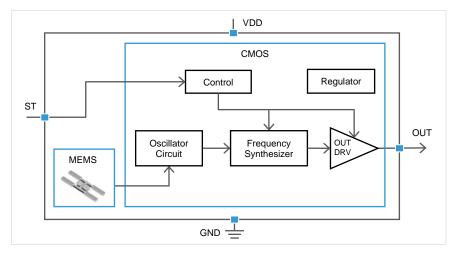

# **Block Diagram**

Figure 2. SiT8021 Block Diagram

# **Device Operating Modes and Outputs**

The SiT8021 supports a  $\leq$ 0.7 µA standby mode for battery-powered and other power sensitive applications. The switching between the active and standby modes is controlled by the logic level on the ST pin as shown in the table below.

**Table 4. Operating Modes and Output States**

| ST Pin | MODE                                        | OUTPUT                                           | IDD Example       |  |

|--------|---------------------------------------------|--------------------------------------------------|-------------------|--|

| LOW    | Active                                      | Specified frequency                              | 60 μA @ 3.072 MHz |  |

| FLOAT  | Active<br>with 200 kΩ<br>internal pull-down | Specified frequency                              | 60 μA @ 3.072 MHz |  |

| HIGH   | Standby                                     | Hi-Z, pulled-down with 1 $\rm M\Omega$ impedence | 1.3 μΑ            |  |

### **Active Mode**

The SiT8021 operates in the active mode when the ST pin is at logic LOW or FLOAT. In the active mode, the device uses the on-chip frequency synthesizer to generate an output from the internal MEMS resonator reference. The frequency of the output is factory programmed based on the device ordering code.

#### Standby Mode

The SiT8021 operates in the standby mode when the ST pin is at logic HIGH. In the standby mode, all internal circuits with the exception of the MEMS oscillator circuit and the ST pin detection logic are turned off to reduce power consumption. While in standby mode, the input impedance of the ST pin is increased to further reduce system-level power consumption.

The output driver of the device in the standby mode is pulled-down with 1  $M\Omega$  impedance.

#### **Output During Startup and Resume**

The SiT8021 starts up with the output disabled. The output is enabled once all internal circuit blocks are active, and logic LOW or FLOAT is detected on the ST pin.

As shown in Table 4, logic HIGH at the ST pin forces the SiT8021 into the "standby" state, causing the output to disable. Upon pulling the ST pin LOW, the device enters the "resume" state, keeping the output disabled. Once the "resume" state ends, the device output enables.

The first clock pulse after startup or resume is accurate to the rated stability.

### **Low Power Design Guidelines**

For high EM noise environments, we recommend the following design guidelines:

- Place oscillator as far away from EM noise sources as possible (e.g., high-voltage switching regulators, motor drive control).

- Route noisy PCB traces, such as digital data lines or high di/dt power supply lines, away from the SiTime oscillator.

- Place a solid GND plane underneath the SiTime oscillator to shield the oscillator from noisy traces on the other board layers.

#### **Manufacturing Guidelines**

- No Ultrasonic or Megasonic Cleaning: Do not subject the SiT8021 to an ultrasonic or megasonic cleaning environment. Permanent damage or long-term reliability issues to the device may occur in such an event.

- Applying board-level underfill (BLUF) to the device is acceptable, but will cause a slight shift of few ppm in the initial frequency tolerance. Tested with UF3810, UF3808, and FP4530 underfill.

- Reflow profile, per JESD22-A113D.

For additional manufacturing guidelines and marking/tape-reel instructions, refer to SiTime Manufacturing Notes.

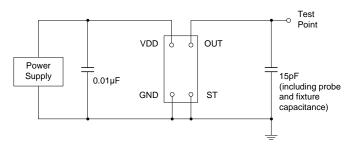

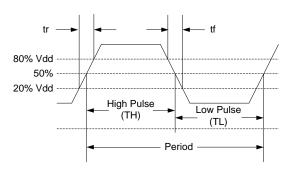

# **Test Circuit and Waveform**

Figure 3. Test Circuit

Figure 4. Waveform<sup>[4]</sup>

#### Note:

4. Duty Cycle is computed as Duty Cycle = TH/Period.

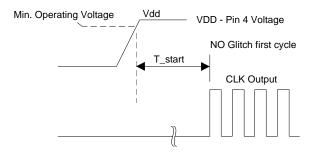

# **Timing Diagram**

T\_start: Time to valid clock output from power on

Figure 5. Startup Timing<sup>[5,6]</sup>

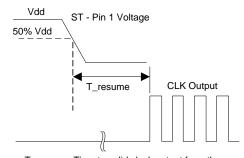

T\_resume: Time to valid clock output from the time ST pin crosses 50% threshold

Figure 6. Resume Timing<sup>[5,6]</sup>

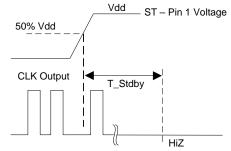

T\_Stdby: Time for output to go high-Z from the time ST pin crosses 50% threshold

Figure 7. Standby Timing<sup>[5]</sup>

### Notes:

- 5. SiT8021 supports "no runt" pulses and "no glitch" output during startup or resume.

- 6. SiT8021 supports gated output which is accurate within rated frequency stability from the first cycle.

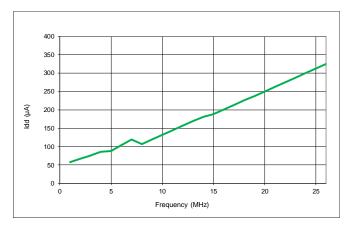

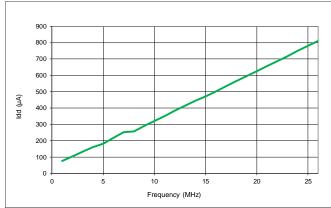

# Performance Plots[7]

Figure 8. Idd vs Frequency without load

Figure 9. Idd vs Frequency with 10 pF load

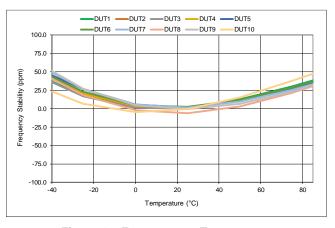

Figure 10. Frequency vs Temperature

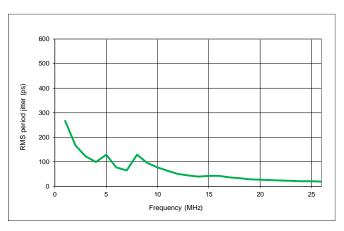

Figure 11. RMS Period Jitter vs Frequency

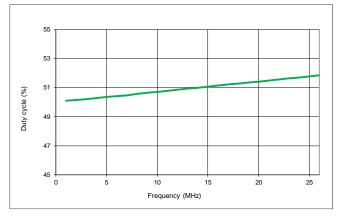

Figure 12. Duty Cycle vs Frequency

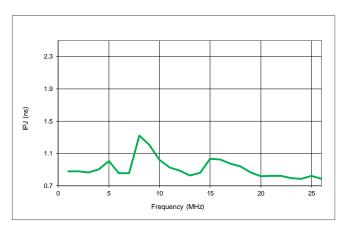

Figure 13. RMS Phase Jitter Random vs Frequency<sup>[8]</sup>

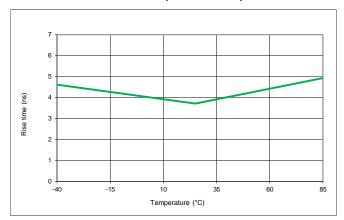

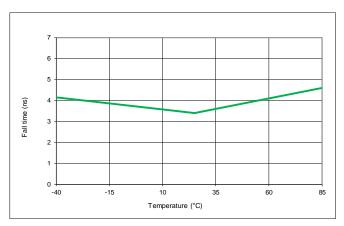

# Performance Plots[7] (continuous)

Figure 14. Rise Time vs Temperature<sup>[9]</sup>

Figure 15. Fall Time vs Temperature<sup>[9]</sup>

- Notes:

7. All data is measured at room temperature, unless otherwise stated.

8. Integration range is from 100 Hz to 40 kHz.

9. Data is measured with 15 pF load.

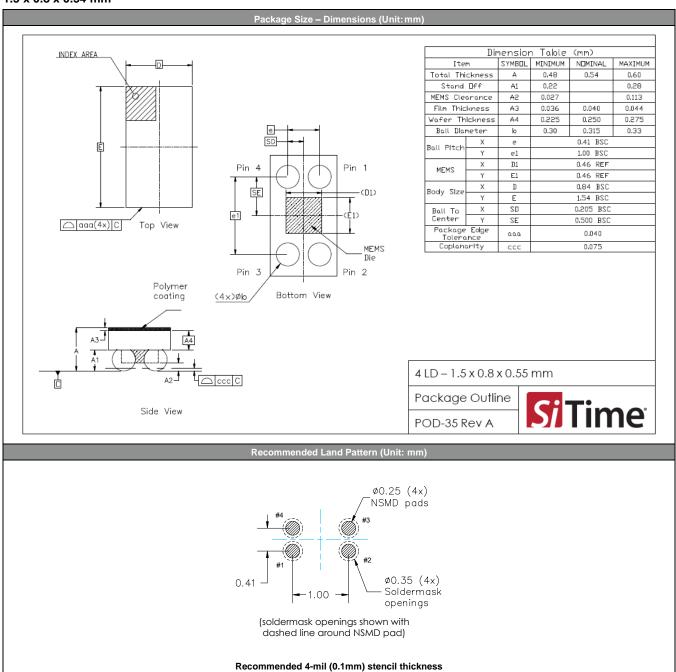

# **Dimensions and Patterns**

#### 1.5 x 0.8 x 0.54 mm

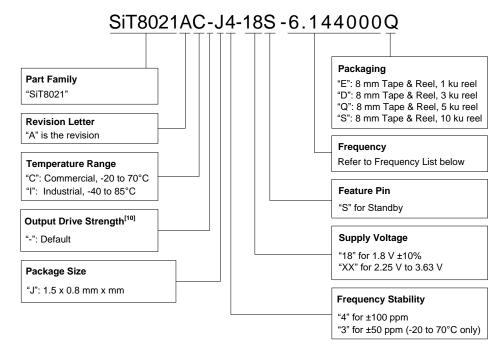

# **Ordering Information**

#### Notes

10. Contact SiTime for other drive strength options that result in different rise/fall time for any given output load.

# Table 5. List of Standard Frequencies[11]

| 2.048 MHz | 4 MHz  | 6.144 MHz | 8 MHz | 12 MHz | 12.288 MHz | 16 MHz |

|-----------|--------|-----------|-------|--------|------------|--------|

| 19.2 MHz  | 24 MHz | 26 MHz    |       |        |            |        |

#### Notes:

11. All frequencies from 1 to 26 MHz are in production. Contact SiTime for minimum order quantity requirement.

#### Table 6. Revision History

| Version | Release Date | Change Summary                                                                                                                                                                 |

|---------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.1     | 15-Dec-2014  | Advance Information                                                                                                                                                            |

| 0.2     | 27-Jan-2015  | Updated CSP dimension tolerance                                                                                                                                                |

|         |              | Removed 2.0 mm x 1.6 mm package                                                                                                                                                |

|         |              | Changed to 6.144 MHz as the reference frequency for jitter, IDD and other relevant parameters                                                                                  |

|         |              | Changed resume time (max) to 5 ms                                                                                                                                              |

|         |              | Changed the parameter PSNR to Power Supply Noise Sensitivity and specified in RMS                                                                                              |

| 0.3     | 31-Mar-2015  | Changed VIL and VIH values in the EC table                                                                                                                                     |

|         |              | Reduced standby time in the EC table                                                                                                                                           |

|         |              | Revised phase jitter condition to include power supply noise sensitivity                                                                                                       |

|         |              | Removed power supply noise spec                                                                                                                                                |

| 0.9     | 22-May-2015  | Added typical values for active and standby current                                                                                                                            |

|         |              | Added current consumption for additional frequencies                                                                                                                           |

|         |              | Changed ±50 ppm option to Contact SiTime                                                                                                                                       |

|         |              | Added manufacturing guideline                                                                                                                                                  |

|         |              | Other miscellaneous format and footnote changes                                                                                                                                |

| 1.0     | 18-Nov-2015  | Revised initial tolerance, current consumption, standby current, input high/low voltage, input pull-down impedance, startup/resume time and RMS period/phase jitter in Table 1 |

|         |              | Added performance plots                                                                                                                                                        |

| 1.1     | 19-Feb-2016  | Added 10 Standard frequencies to the ordering information                                                                                                                      |

| 1.11    | 16-Sep-2016  | Updated the table.5 list of standard frequencies                                                                                                                               |

|         |              | Added a graph of Idd vs Frequency without load to the performance plots section                                                                                                |

| 1.2     | 28-Sep-2017  | Added 2.25 to 3.63 V supply voltage option Updated logo and company address, other page layout changes                                                                         |

|         |              | Added package dimension table to the dimensions and patterns section                                                                                                           |

| 1.3     | 18-Nov-2020  | Added ±50 ppm frequency stability option Formatting, rev table date format and TempFlat MEMS logo update                                                                       |

| 1.31    | 29-Mar-2021  | Added Q-suffix to the Ordering table options Updated hyperlinks, changed date format                                                                                           |

#### SiTime Corporation, 5451 Patrick Henry Drive, Santa Clara, CA 95054, USA | Phone: +1-408-328-4400 | Fax: +1-408-328-4439

© SiTime Corporation 2014-2021. The information contained herein is subject to change at any time without notice. SiTime assumes no responsibility or liability for any loss, damage or defect of a Product which is caused in whole or in part by (i) use of any circuitry other than circuitry embodied in a SiTime product, (ii) misuse or abuse including static discharge, neglect or accident, (iii) unauthorized modification or repairs which have been soldered or altered during assembly and are not capable of being tested by SiTime under its normal test conditions, or (iv) improper installation, storage, handling, warehousing or transportation, or (v) being subjected to unusual physical, thermal, or electrical stress.

Disclaimer: SiTime makes no warranty of any kind, express or implied, with regard to this material, and specifically disclaims any and all express or implied warranties, either in fact or by operation of law, statutory or otherwise, including the implied warranties of merchantability and fitness for use or a particular purpose, and any implied warranty arising from course of dealing or usage of trade, as well as any common-law duties relating to accuracy or lack of negligence, with respect to this material, any SiTime product and any product documentation. Products sold by SiTime are not suitable or intended to be used in a life support application or component, to operate nuclear facilities, or in other mission critical applications where human life may be involved or at stake. All sales are made conditioned upon compliance with the critical uses policy set forth below.

#### CRITICAL USE EXCLUSION POLICY

BUYER AGREES NOT TO USE SITIME'S PRODUCTS FOR ANY APPLICATION OR IN ANY COMPONENTS USED IN LIFE SUPPORT DEVICES OR TO OPERATE NUCLEAR FACILITIES OR FOR USE IN OTHER MISSION-CRITICAL APPLICATIONS OR COMPONENTS WHERE HUMAN LIFE OR PROPERTY MAY BE AT STAKE.

SiTime owns all rights, title and interest to the intellectual property related to SiTime's products, including any software, firmware, copyright, patent, or trademark. The sale of SiTime products does not convey or imply any license under patent or other rights. SiTime retains the copyright and trademark rights in all documents, catalogs and plans supplied pursuant to or ancillary to the sale of products or services by SiTime. Unless otherwise agreed to in writing by SiTime, any reproduction, modification, translation, compilation, or representation of this material shall be strictly prohibited.