# TABLE OF CONTENTS

| Features                       | 1   |

|--------------------------------|-----|

| Enhanced Product Features      | 1   |

| Applications                   | . 1 |

| General Description            | 1   |

| Revision History               | 2   |

| Functional Block Diagram       | . 3 |

| Specifications                 | .4  |

| AC Performance Characteristics | 5   |

| Timing Characteristics                      | 6  |

|---------------------------------------------|----|

| Absolute Maximum Ratings                    | 9  |

| ESD Caution                                 | 9  |

| Pin Configuration and Function Descriptions | 10 |

| Typical Performance Characteristics         | 12 |

| Outline Dimensions                          | 17 |

| Ordering Guide                              | 17 |

#### **REVISION HISTORY**

12/13—Revision 0: Initial Version

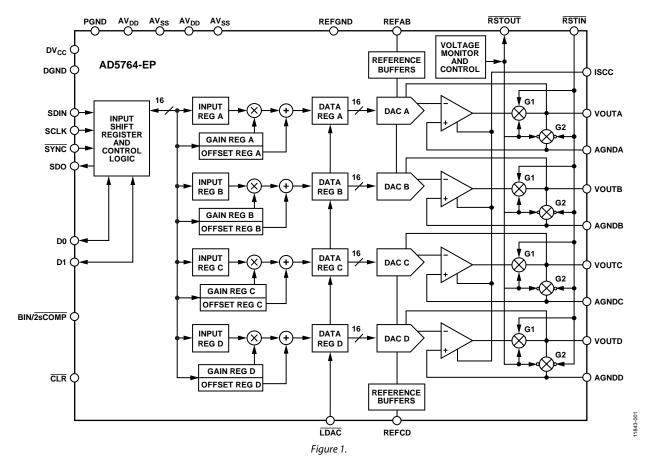

#### FUNCTIONAL BLOCK DIAGRAM

## SPECIFICATIONS

$AV_{DD} = 11.4 \text{ V}$  to 16.5 V,  $AV_{SS} = -11.4 \text{ V}$  to -16.5 V, AGNDx = DGND = REFGND = PGND = 0 V; REFAB = REFCD = 5 V;  $DV_{CC} = 2.7 \text{ V}$  to 5.25 V,  $R_{LOAD} = 10 \text{ k}\Omega$ ,  $C_{LOAD} = 200 \text{ pF}$ . Temperature range:  $-55^{\circ}$ C to  $+105^{\circ}$ C; typical at  $+25^{\circ}$ C. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

#### Table 2.

| Parameter                                              | Min                    | Тур | Max      | Unit                   | Test Conditions/Comments                                              |

|--------------------------------------------------------|------------------------|-----|----------|------------------------|-----------------------------------------------------------------------|

| ACCURACY                                               |                        |     |          |                        | Outputs unloaded                                                      |

| Resolution                                             | 16                     |     |          | Bits                   |                                                                       |

| Relative Accuracy (INL)                                |                        |     | ±2       | LSB                    |                                                                       |

| Differential Nonlinearity (DNL)                        |                        |     | ±1       | LSB                    | Guaranteed monotonic                                                  |

| Bipolar Zero Error                                     |                        |     | ±2       | mV                     | At 25°C; error at other temperatures obtained using bipolar zero TC   |

| Bipolar Zero Temperature Coefficient (TC) <sup>1</sup> |                        |     | ±2       | ppm FSR/°C             |                                                                       |

| Zero-Scale Error                                       |                        |     | ±3       | mV                     | At 25°C; error at other temperatures obtained using zero-scale TC     |

| Zero-Scale TC <sup>1</sup>                             |                        |     | ±2       | ppm FSR/°C             |                                                                       |

| Gain Error                                             |                        |     | ±0.02    | % FSR                  | At 25°C; error at other temperatures obtained using gain TC           |

| Gain TC <sup>1</sup>                                   |                        |     | ±2       | ppm FSR/°C             |                                                                       |

| DC Crosstalk <sup>1</sup>                              |                        |     | 0.5      | LSB                    |                                                                       |

| REFERENCE INPUT <sup>1</sup>                           |                        |     |          |                        |                                                                       |

| Reference Input Voltage                                |                        | 5   |          | V                      | ±1% for specified performance                                         |

| DC Input Impedance                                     | 1                      |     |          | MΩ                     | Typically 100 MΩ                                                      |

| Input Current                                          |                        |     | ±10      | μΑ                     | Typically ±30 nA                                                      |

| Reference Range                                        | 1                      |     | 7        | V                      |                                                                       |

| OUTPUT CHARACTERISTICS <sup>1</sup>                    |                        |     |          |                        |                                                                       |

| Output Voltage Range <sup>2</sup>                      | -10.5263               |     | +10.5263 | V                      | $AV_{DD}/AV_{SS} = \pm 11.4 V$ , $V_{REFIN} = 5 V$                    |

|                                                        | -14                    |     | +14      | V                      | $AV_{DD}/AV_{SS} = \pm 16.5 \text{ V}, V_{REFIN} = 7 \text{ V}$       |

| Output Voltage Drift vs. Time                          |                        | ±13 |          | ppm FSR/<br>500 hours  |                                                                       |

|                                                        |                        | ±15 |          | ppm FSR/<br>1000 hours |                                                                       |

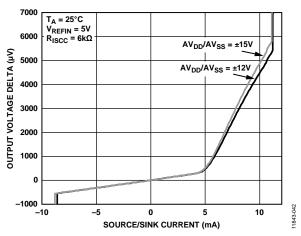

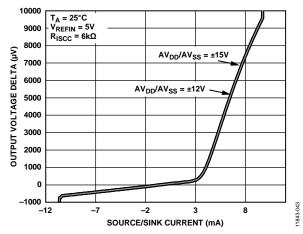

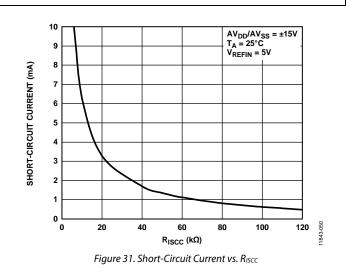

| Short-Circuit Current                                  |                        | 10  |          | mA                     | $R_{ISCC} = 6 k\Omega$ ; see Figure 31                                |

| Load Current                                           |                        |     | ±1       | mA                     | For specified performance                                             |

| Capacitive Load Stability                              |                        |     |          |                        |                                                                       |

| $R_{LOAD} = \infty$                                    |                        |     | 200      | pF                     |                                                                       |

| $R_{LOAD} = 10 \ k\Omega$                              |                        |     | 1000     | pF                     |                                                                       |

| DC Output Impedance                                    |                        |     | 0.3      | Ω                      |                                                                       |

| DIGITAL INPUTS                                         |                        |     |          |                        | D <sub>VCC</sub> = 2.7 V to 5.25 V, JEDEC compliant                   |

| Input High Voltage, V⊮                                 | 2                      |     |          | V                      |                                                                       |

| Input Low Voltage, V <sub>L</sub>                      |                        |     | 0.8      | V                      |                                                                       |

| Input Current                                          |                        |     | ±1       | μΑ                     | Per pin                                                               |

| Pin Capacitance                                        |                        |     | 10       | pF                     | Per pin                                                               |

| DIGITAL OUTPUTS (D0, D1, SDO) <sup>1</sup>             |                        |     |          |                        |                                                                       |

| Output Low Voltage, Vol                                |                        |     | 0.4      | V                      | $DV_{CC} = 5 V \pm 5\%$ , sinking 200 $\mu$ A                         |

| · • •                                                  |                        |     | 0.4      | V                      | $D_{VCC} = 2.7 \text{ V to } 3.6 \text{ V, sinking } 200 \mu\text{A}$ |

| Output High Voltage, V <sub>OH</sub>                   | DVcc – 1               |     |          | v                      | $DV_{cc} = 5 V \pm 5\%$ , sourcing 200 µA                             |

|                                                        | DV <sub>cc</sub> – 0.5 |     |          | V                      | $D_{VCC} = 2.7 V$ to 3.6 V, sourcing 200 $\mu$ A                      |

| High Impedance Leakage Current                         |                        |     | ±1       | μA                     | SDO only                                                              |

| High Impedance Output Capacitance                      |                        | 5   |          | pF                     | SDO only                                                              |

## AD5764-EP

| Parameter                                        | Min   | Тур | Max   | Unit       | Test Conditions/Comments                                   |

|--------------------------------------------------|-------|-----|-------|------------|------------------------------------------------------------|

| POWER REQUIREMENTS                               |       |     |       |            |                                                            |

| AV <sub>DD</sub> /AV <sub>ss</sub>               | ±11.4 |     | ±16.5 | V          |                                                            |

| DVcc                                             | 2.7   |     | 5.25  | V          |                                                            |

| Power Supply Sensitivity <sup>1</sup>            |       |     |       |            |                                                            |

| $\Delta V_{\text{OUT}} / \Delta A V_{\text{DD}}$ |       | -85 |       | dB         |                                                            |

| Aldd                                             |       |     | 3.75  | mA/channel | Outputs unloaded                                           |

| Alss                                             |       |     | -3    | mA/channel | Outputs unloaded                                           |

| Dlcc                                             |       |     | 1.4   | mA         | $V_{IH} = DV_{CC}$ , $V_{IL} = DGND$ , 750 $\mu$ A typical |

| Power Dissipation                                |       | 275 |       | mW         | ±12 V operation, output unloaded                           |

$^{\rm 1}$  Guaranteed by design and characterization; not production tested.  $^{\rm 2}$  Output amplifier headroom requirement is 1.4 V minimum.

#### **AC PERFORMANCE CHARACTERISTICS**

$AV_{DD} = 11.4 \text{ V}$  to 16.5 V,  $AV_{SS} = -11.4 \text{ V}$  to -16.5 V, AGNDx = DGND = REFGND = PGND = 0 V; REFAB = REFCD = 5 V;  $DV_{CC} = 2.7 V$  to 5.25 V,  $R_{LOAD} = 10 k\Omega$ ,  $C_{LOAD} = 200 pF$ . All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Т | ab | le | 3  |

|---|----|----|----|

|   | au | 10 | э. |

| Parameter                                                     | Min | Тур | Max | Unit    | Test Conditions/Comments                    |

|---------------------------------------------------------------|-----|-----|-----|---------|---------------------------------------------|

| DYNAMIC PERFORMANCE <sup>1</sup>                              |     |     |     |         |                                             |

| Output Voltage Settling Time                                  |     | 8   | 10  | μs      | Full-scale step to $\pm 1$ LSB              |

|                                                               |     | 2   |     | μs      | 512 LSB step settling                       |

| Slew Rate                                                     |     | 5   |     | V/µs    |                                             |

| Digital-to-Analog Glitch Energy                               |     | 8   |     | nV-sec  |                                             |

| Glitch Impulse Peak Amplitude                                 |     |     | 37  | mV p-p  |                                             |

| Channel-to-Channel Isolation                                  |     | 80  |     | dB      |                                             |

| DAC-to-DAC Crosstalk                                          |     | 8   |     | nV-sec  |                                             |

| Digital Crosstalk                                             |     | 2   |     | nV-sec  |                                             |

| Digital Feedthrough                                           |     | 2   |     | nV-sec  | Effect of input bus activity on DAC outputs |

| Output Noise                                                  |     |     |     |         |                                             |

| 0.1 Hz to 10 Hz                                               |     | 0.1 |     | LSB p-p |                                             |

| 0.1 Hz to 100 kHz                                             |     |     | 45  | μV rms  |                                             |

| 1/f Corner Frequency                                          |     | 1   |     | kHz     |                                             |

| Output Noise Spectral Density                                 |     | 60  |     | nV/√Hz  | Measured at 10 kHz                          |

| Complete System Output Noise Spectral<br>Density <sup>2</sup> |     | 80  |     | nV/√Hz  | Measured at 10 kHz                          |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

<sup>2</sup> Includes noise contributions from integrated reference buffers, 16-bit DAC, and output amplifier.

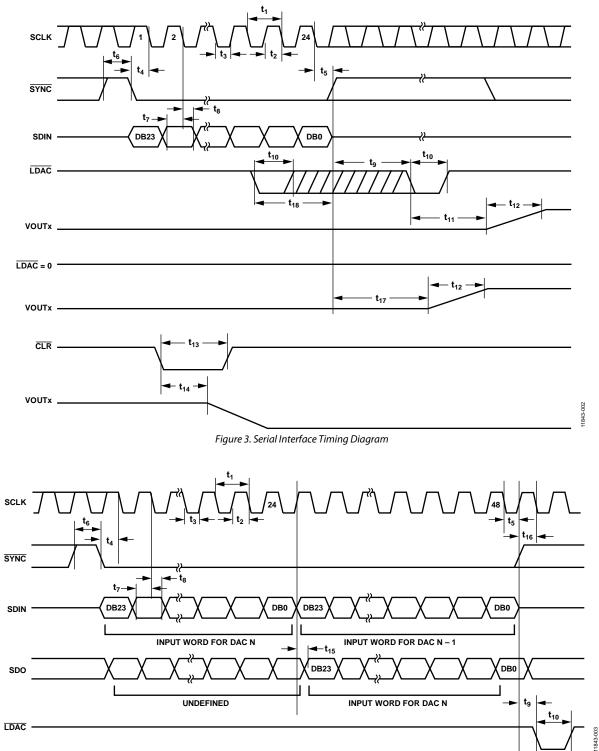

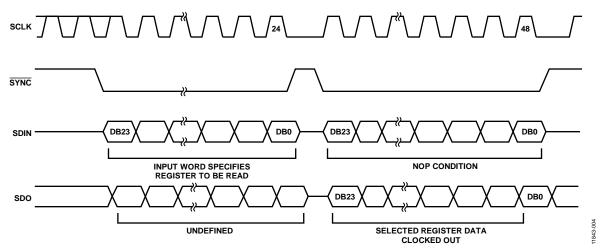

#### TIMING CHARACTERISTICS

$AV_{DD} = 11.4 \text{ V}$  to 16.5 V,  $AV_{SS} = -11.4 \text{ V}$  to -16.5 V, AGNDx = DGND = REFGND = PGND = 0 V; REFAB = REFCD = 5 V;  $DV_{CC} = 2.7 \text{ V}$  to 5.25 V,  $R_{LOAD} = 10 \text{ k}\Omega$ ,  $C_{LOAD} = 200 \text{ pF}$ . All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

| Table 4.                     |                                              |        |                                                                                                   |

|------------------------------|----------------------------------------------|--------|---------------------------------------------------------------------------------------------------|

| Parameter <sup>1, 2, 3</sup> | Limit at T <sub>MIN</sub> , T <sub>MAX</sub> | Unit   | Description                                                                                       |

| t <sub>1</sub>               | 33                                           | ns min | SCLK cycle time                                                                                   |

| <b>t</b> <sub>2</sub>        | 13                                           | ns min | SCLK high time                                                                                    |

| t <sub>3</sub>               | 13                                           | ns min | SCLK low time                                                                                     |

| t <sub>4</sub>               | 13                                           | ns min | SYNC falling edge to SCLK falling edge setup time                                                 |

| t5 <sup>4</sup>              | 13                                           | ns min | 24 <sup>th</sup> SCLK falling edge to SYNC rising edge                                            |

| t <sub>6</sub>               | 90                                           | ns min | Minimum SYNC high time                                                                            |

| t <sub>7</sub>               | 2                                            | ns min | Data setup time                                                                                   |

| t <sub>8</sub>               | 9                                            | ns min | Data hold time                                                                                    |

| t9                           | 1.7                                          | µs min | SYNC rising edge to LDAC falling edge (all DACs updated)                                          |

|                              | 480                                          | ns min | SYNC rising edge to LDAC falling edge (single DAC updated)                                        |

| <b>t</b> <sub>10</sub>       | 17                                           | ns min | LDAC pulse width low                                                                              |

| t11                          | 500                                          | ns max | LDAC falling edge to DAC output response time                                                     |

| t <sub>12</sub>              | 10                                           | µs max | DAC output settling time                                                                          |

| t <sub>13</sub>              | 17                                           | ns min | CLR pulse width low                                                                               |

| t <sub>14</sub>              | 2                                            | µs max | CLR pulse activation time                                                                         |

| t <sub>15</sub> 5, 6         | 25                                           | ns max | SCLK rising edge to SDO valid                                                                     |

| t <sub>16</sub>              | 13                                           | ns min | SYNC rising edge to SCLK falling edge                                                             |

| t <sub>17</sub>              | 2                                            | µs max | $\overline{\text{SYNC}}$ rising edge to DAC output response time ( $\overline{\text{LDAC}} = 0$ ) |

| t <sub>18</sub>              | 170                                          | ns min | LDAC falling edge to SYNC rising edge                                                             |

<sup>1</sup> Guaranteed by design and characterization; not production tested.

<sup>2</sup> All input signals are specified with  $t_R = t_F = 5$  ns (10% to 90% of DV<sub>CC</sub>) and timed from a voltage level of 1.2 V.

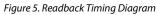

<sup>3</sup> See Figure 3, Figure 4, and Figure 5.

<sup>4</sup> Standalone mode only.

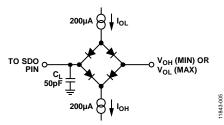

<sup>5</sup> Measured with the load circuit of Figure 2.

<sup>6</sup> Daisy-chain mode only.

Figure 2. Load Circuit for SDO Timing Diagram

#### **Timing Diagrams**

Figure 4. Daisy-Chain Timing Diagram

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25^{\circ}$ C, unless otherwise noted. Transient currents of up to 100 mA do not cause SCR latch-up.

#### Table 5.

| Tuble 5.                               |                                                                  |

|----------------------------------------|------------------------------------------------------------------|

| Parameter                              | Rating                                                           |

| AV <sub>DD</sub> to AGNDx, DGND        | –0.3 V to +17 V                                                  |

| AVss to AGNDx, DGND                    | +0.3 V to -17 V                                                  |

| DVcc to DGND                           | –0.3 V to +7 V                                                   |

| Digital Inputs to DGND                 | -0.3 V to DV <sub>cc</sub> + 0.3 V or 7 V<br>(whichever is less) |

| Digital Outputs to DGND                | -0.3 V to DV <sub>CC</sub> + 0.3 V                               |

| REFAB, REFCD to AGNDx, PGND            | -0.3 V to AV <sub>DD</sub> + 0.3 V                               |

| VOUTA, VOUTB, VOUTC, VOUTD<br>to AGNDx | AVss to AVDD                                                     |

| AGNDx to DGND                          | –0.3 V to +0.3 V                                                 |

| Operating Temperature Range            |                                                                  |

| Industrial                             | –55°C to +105°C                                                  |

| Storage Temperature Range              | –65°C to +150°C                                                  |

| Junction Temperature (TJ max)          | 150℃                                                             |

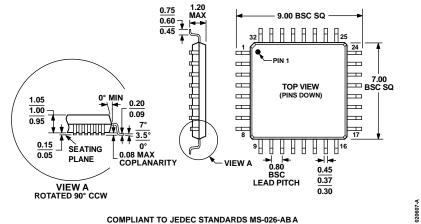

| 32-Lead TQFP                           |                                                                  |

| $\theta_{JA}$ Thermal Impedance        | 65°C/W                                                           |

| $\theta_{JC}$ Thermal Impedance        | 12°C/W                                                           |

| Lead Temperature                       | JEDEC industry standard                                          |

| Soldering                              | J-STD-020                                                        |

|                                        |                                                                  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

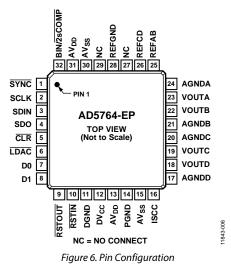

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### **Table 6. Pin Function Descriptions**

| Pin No. | Mnemonic         | Description                                                                                                                                                                                                                                                                                   |

|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SYNC             | Active Low Input. This pin is the frame synchronization signal for the serial interface. While SYNC is low, data is                                                                                                                                                                           |

|         |                  | transferred in on the falling edge of SCLK.                                                                                                                                                                                                                                                   |

| 2       | SCLK             | Serial Clock Input. Data is clocked into the input shift register on the falling edge of SCLK. This input operates at                                                                                                                                                                         |

|         |                  | clock speeds up to 30 MHz.                                                                                                                                                                                                                                                                    |

| 3       | SDIN             | Serial Data Input. Data must be valid on the falling edge of SCLK.                                                                                                                                                                                                                            |

| 4       | SDO              | Serial Data Output. This pin is used to clock data from the serial register in daisy-chain or readback mode.                                                                                                                                                                                  |

| 5       | CLR              | Negative Edge Triggered Input. Asserting this pin sets the data register to 0x0000. This logic input has an internal pull-up device. Therefore, this pin can be left floating and defaults to a Logic 1 condition.                                                                            |

| 6       | LDAC             | Load DAC. This logic input is used to update the data register and, consequently, the analog outputs. When LDAC is tied permanently low, the addressed data register is updated on the rising edge of SYNC. If LDAC is held                                                                   |

|         |                  | high during the write cycle, the DAC input shift register is updated, but the update of the output is delayed until the falling edge of LDAC. In this mode, all analog outputs can be updated simultaneously on the falling edge of LDAC. The LDAC pin must not be left unconnected.          |

| 7, 8    | D0, D1           | Digital I/O Port. These pins can be inputs or outputs that are configurable and readable over the serial interface. When configured as inputs, D0 and D1 have weak internal pull-ups to DV <sub>cc</sub> . When configured as outputs, D0 and D1 are referenced by DV <sub>cc</sub> and DGND. |

| 9       | RSTOUT           | Reset Logic Output. This pin is the output from the on-chip voltage monitor and is used in the reset circuit. If desired, this pin can be used to control other system components.                                                                                                            |

| 10      | RSTIN            | Reset Logic Input. This input allows external access to the internal reset logic. Applying a Logic 0 to this input clamps the DAC outputs to 0 V. In normal operation, RSTIN should be tied to Logic 1. Register values remain unchanged.                                                     |

| 11      | DGND             | Digital Ground.                                                                                                                                                                                                                                                                               |

| 12      | DVcc             | Digital Supply Voltage (2.7 V to 5.25 V).                                                                                                                                                                                                                                                     |

| 13, 31  | AV <sub>DD</sub> | Positive Analog Supply Voltage (11.4 V to 16.5 V).                                                                                                                                                                                                                                            |

| 14      | PGND             | Ground Reference Point for the Analog Circuitry.                                                                                                                                                                                                                                              |

| 15, 30  | AVss             | Negative Analog Supply Voltage (–11.4 V to –16.5 V).                                                                                                                                                                                                                                          |

| 16      | ISCC             | Resistor Connection for Pin Programmable Short-Circuit Current. This pin is used with an optional external resistor to AGND to program the short-circuit current of the output amplifiers.                                                                                                    |

| 17      | AGNDD            | Ground Reference Pin for DAC D Output Amplifier.                                                                                                                                                                                                                                              |

| 18      | VOUTD            | Analog Output Voltage of DAC D. This buffered output has a nominal full-scale output range of $\pm 10$ V. The output amplifier is capable of directly driving a 10 k $\Omega$ , 200 pF load.                                                                                                  |

| 19      | VOUTC            | Analog Output Voltage of DAC C. This buffered output has a nominal full-scale output range of $\pm 10$ V. The output amplifier is capable of directly driving a 10 k $\Omega$ , 200 pF load.                                                                                                  |

| 20      | AGNDC            | Ground Reference Pin for DAC C Output Amplifier.                                                                                                                                                                                                                                              |

| Pin No. | Mnemonic   | Description                                                                                                                                                                                                                                                     |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21      | AGNDB      | Ground Reference Pin for DAC B Output Amplifier.                                                                                                                                                                                                                |

| 22      | VOUTB      | Analog Output Voltage of DAC B. This buffered output has a nominal full-scale output range of $\pm 10$ V. The output amplifier is capable of directly driving a 10 k $\Omega$ , 200 pF load.                                                                    |

| 23      | VOUTA      | Analog Output Voltage of DAC A. This buffered output has a nominal full-scale output range of $\pm 10$ V. The output amplifier is capable of directly driving a 10 k $\Omega$ , 200 pF load.                                                                    |

| 24      | AGNDA      | Ground Reference Pin for DAC A Output Amplifier.                                                                                                                                                                                                                |

| 25      | REFAB      | External Reference Voltage Input for Channel A and Channel B. Reference input range is 1 V to 7 V. This pin programs the full-scale output voltage. $V_{REFIN} = 5 V$ for specified performance.                                                                |

| 26      | REFCD      | External Reference Voltage Input for Channel C and Channel D. Reference input range is 1 V to 7 V. This pin programs the full-scale output voltage. VREFIN = 5 V for specified performance.                                                                     |

| 27, 29  | NC         | No Connect.                                                                                                                                                                                                                                                     |

| 28      | REFGND     | Reference Ground Return for the Reference Generator and Buffers.                                                                                                                                                                                                |

| 32      | BIN/2sCOMP | This pin determines the DAC coding. This pin should be hardwired to either DV <sub>CC</sub> or DGND. When the pin is hardwired to DV <sub>CC</sub> , the input coding is offset binary. When the pin is hardwired to DGND, the input coding is twos complement. |

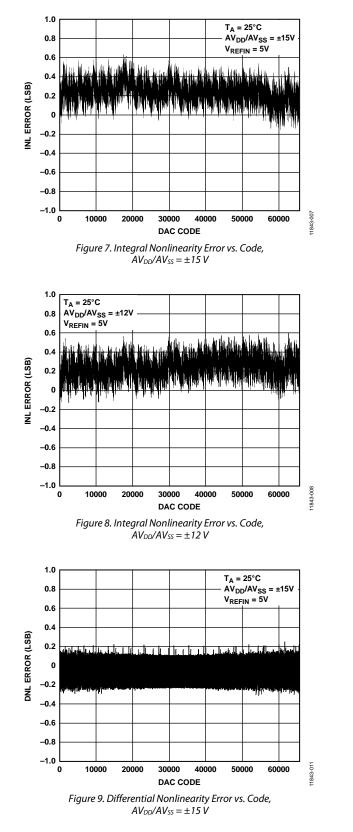

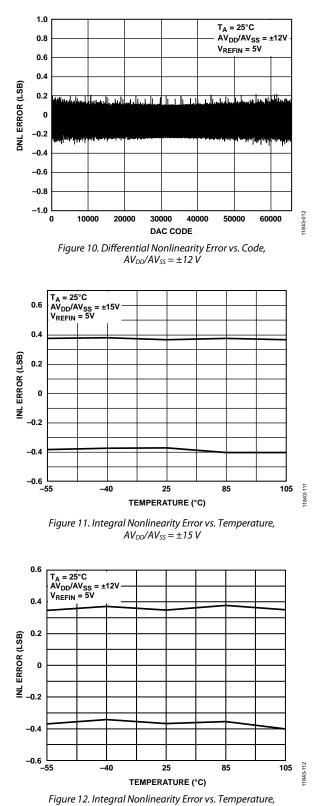

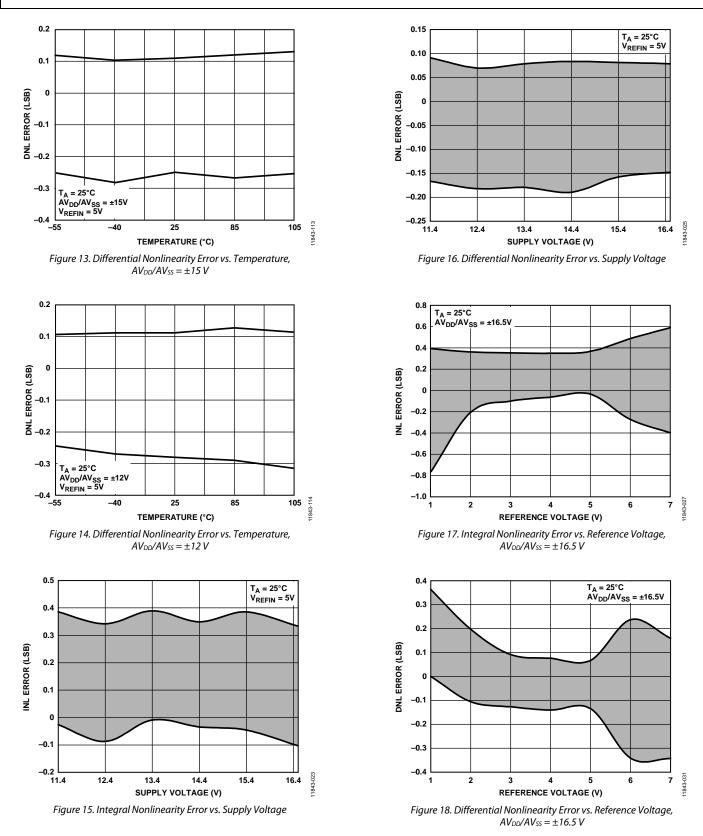

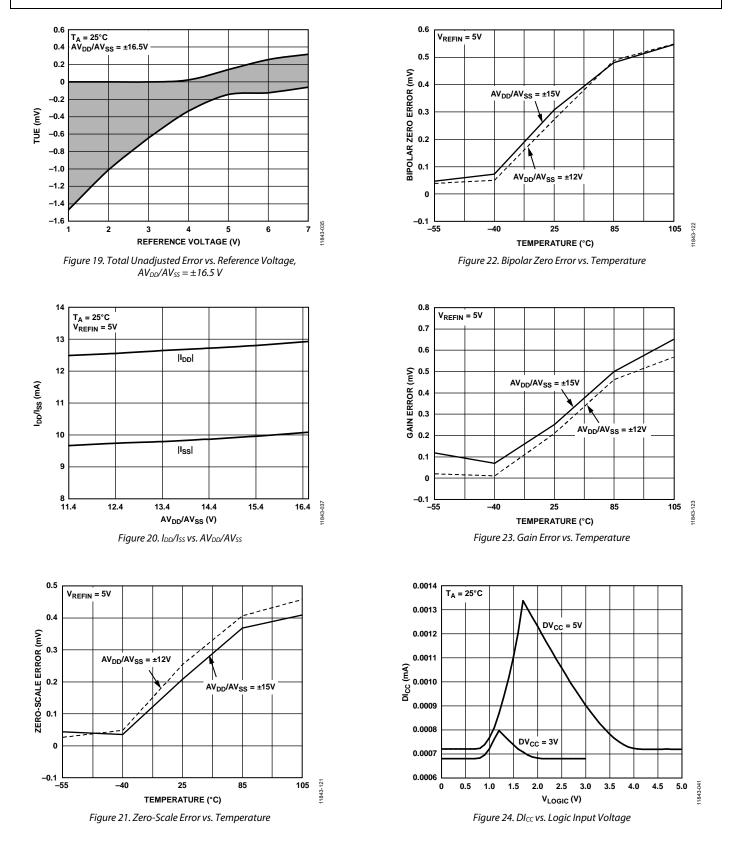

### **TYPICAL PERFORMANCE CHARACTERISTICS**

AD5764-EP

# **Enhanced Product**

## AD5764-EP

Figure 25. Source and Sink Capability of Output Amplifier with Positive Full Scale Loaded

Figure 26. Source and Sink Capability of Output Amplifier with Negative Full Scale Loaded

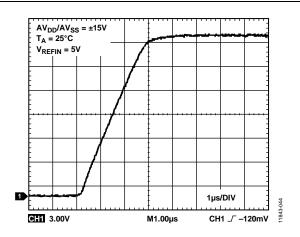

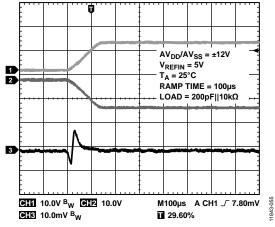

Figure 27. Full-Scale Settling Time

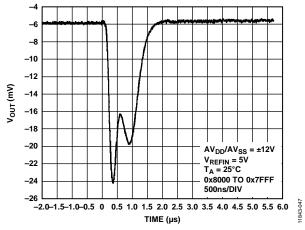

Figure 28. Major Code Transition Glitch Energy,  $AV_{DD}/AV_{SS} = \pm 12 V$

## **Enhanced Product**

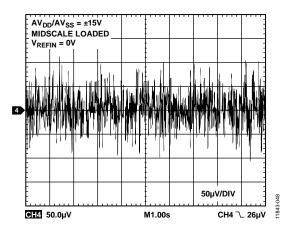

Figure 29. Peak-to-Peak Noise (100 kHz Bandwidth)

Figure 30. VOUT vs. AVDD/AVss on Power-Up

### **OUTLINE DIMENSIONS**

Figure 32. 32-Lead Thin Plastic Quad Flat Package [TQFP] (SU-32-2) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model <sup>1</sup> | INL        | Temperature Range | Package Description | Package Option |

|--------------------|------------|-------------------|---------------------|----------------|

| AD5764SSUZ-EP-RL7  | ±2 LSB max | –55°C to +105°C   | 32-Lead TQFP        | SU-32-2        |

$^{1}$  Z = RoHS Compliant Part.

## NOTES

## NOTES

### NOTES

©2013 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D11843-0-12/13(0)

www.analog.com