# **TABLE OF CONTENTS**

| Features                                        | 1  |

|-------------------------------------------------|----|

| Applications                                    | 1  |

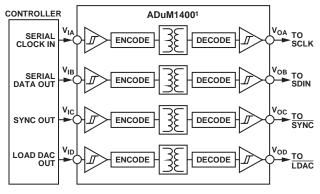

| Functional Block Diagram                        | 1  |

| General Description                             | 1  |

| Product Highlights                              | 1  |

| Revision History                                | 2  |

| Specifications                                  | 3  |

| AC Characteristics                              | 5  |

| Timing Characteristics                          | 6  |

| Daisy-Chain and Readback Timing Characteristics | 7  |

| Absolute Maximum Ratings                        | 9  |

| ESD Caution                                     | 9  |

| Pin Configurations and Function Descriptions    | 10 |

| Typical Performance Characteristics             | 11 |

| Terminology                                     | 16 |

| Theory of Operation                             | 18 |

| Digital-to-Analog Converter                     | 18 |

| Transfer Function                               | 18 |

| DAC Architecture                                | 18 |

|                                                 |    |

|                                                 |    |

|   | Serial Interface                      | 19   |

|---|---------------------------------------|------|

|   | Standalone Operation                  | 20   |

|   | Write and Update Commands             | 20   |

|   | Daisy-Chain Operation                 | 20   |

|   | Readback Operation                    | 21   |

|   | Power-Down Operation                  | 21   |

|   | Load DAC (Hardware LDAC Pin)          | 22   |

|   | LDAC Mask Register                    | . 22 |

|   | Hardware Reset (RESET)                | 23   |

|   | Reset Select Pin (RSTSEL)             | 23   |

| ١ | pplications Information               | 24   |

|   | Microprocessor Interfacing            | 24   |

|   | AD5686/AD5684 to ADSP-BF531 Interface | 24   |

|   | AD5686/AD5684 to SPORT Interface      | 24   |

|   | Layout Guidelines                     | 24   |

|   | Galvanically Isolated Interface       | 25   |

| ) | utline Dimensions                     | 26   |

|   | Ordering Guide                        | 27   |

# **REVISION HISTORY**

3/15—Rev. A to Rev. B

| Changes to Table 4 and Figure 2   | . 6 |

|-----------------------------------|-----|

| Inserted Note 2 to Ordering Guide | 27  |

6/13—Rev. 0 to Rev. A

Changes to Pin GAIN and Pin RSTSEL Descriptions; Table 7..10  $\,$

7/12—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}; V_{REF} = 2.5 \text{ V}; 1.8 \text{ V} \leq V_{LOGIC} \leq 5.5 \text{ V}; \text{ all specifications } T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. } R_L = 2 \text{ k}\Omega; C_L = 200 \text{ pF.}$

Table 2.

|                                                 |     | A Grade | 1                        |     | B Grade | 1                        |             |                                                                                               |

|-------------------------------------------------|-----|---------|--------------------------|-----|---------|--------------------------|-------------|-----------------------------------------------------------------------------------------------|

| Parameter                                       | Min | Тур     | Max                      | Min | Тур     | Max                      | Unit        | Test Conditions/Comments                                                                      |

| STATIC PERFORMANCE <sup>2</sup>                 |     |         |                          |     |         |                          |             |                                                                                               |

| AD5686                                          |     |         |                          |     |         |                          |             |                                                                                               |

| Resolution                                      | 16  |         |                          | 16  |         |                          | Bits        |                                                                                               |

| Relative Accuracy                               |     | ±2      | ±8                       |     | ±1      | ±2                       | LSB         | Gain = 2                                                                                      |

|                                                 |     | ±2      | ±8                       |     | ±1      | ±3                       | LSB         | Gain = 1                                                                                      |

| Differential Nonlinearity                       |     |         | ±1                       |     |         | ±1                       | LSB         | Guaranteed monotonic by design                                                                |

| AD5684                                          |     |         |                          |     |         |                          |             |                                                                                               |

| Resolution                                      | 12  |         |                          | 12  |         |                          | Bits        |                                                                                               |

| Relative Accuracy                               |     | ±0.12   | ±2                       |     | ±0.12   | ±1                       | LSB         |                                                                                               |

| Differential Nonlinearity                       |     |         | ±1                       |     |         | ±1                       | LSB         | Guaranteed monotonic by design                                                                |

| Zero-Code Error                                 |     | 0.4     | 4                        |     | 0.4     | 1.5                      | mV          | All 0s loaded to DAC register                                                                 |

| Offset Error                                    |     | +0.1    | ±4                       |     | +0.1    | ±1.5                     | mV          |                                                                                               |

| Full-Scale Error                                |     | +0.01   | ±0.2                     |     | +0.01   | ±0.1                     | % of<br>FSR | All 1s loaded to DAC register                                                                 |

| Gain Error                                      |     | ±0.02   | ±0.2                     |     | ±0.02   | ±0.1                     | % of<br>FSR |                                                                                               |

| Total Unadjusted Error                          |     | ±0.01   | ±0.25                    |     | ±0.01   | ±0.1                     | % of<br>FSR | Gain = 2                                                                                      |

|                                                 |     |         | ±0.25                    |     |         | ±0.2                     | % of<br>FSR | Gain = 1                                                                                      |

| Offset Error Drift <sup>3</sup>                 |     | ±1      |                          |     | ±1      |                          | μV/°C       |                                                                                               |

| Gain Temperature<br>Coefficient <sup>3</sup>    |     | ±1      |                          |     | ±1      |                          | ppm         | Of FSR/°C                                                                                     |

| DC Power Supply Rejection<br>Ratio <sup>3</sup> |     | 0.15    |                          |     | 0.15    |                          | mV/V        | DAC code = midscale; $V_{DD} = 5 \text{ V} \pm 10\%$                                          |

| DC Crosstalk <sup>3</sup>                       |     | ±2      |                          |     | ±2      |                          | μV          | Due to single channel, full-scale output change                                               |

|                                                 |     | ±3      |                          |     | ±3      |                          | μV/mA       | Due to load current change                                                                    |

|                                                 |     | ±2      |                          |     | ±2      |                          | μV          | Due to powering down (per channel                                                             |

| OUTPUT CHARACTERISTICS <sup>3</sup>             |     |         |                          |     |         |                          | •           |                                                                                               |

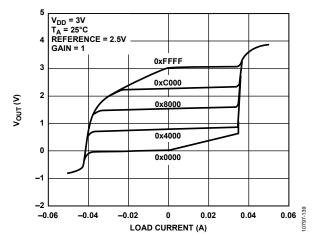

| Output Voltage Range                            | 0   |         | $V_{REF}$                | 0   |         | $V_{REF}$                | V           | Gain = 1                                                                                      |

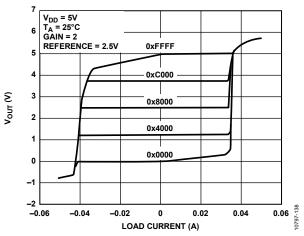

| . 3                                             | 0   |         | $2\times V_{\text{REF}}$ | 0   |         | $2\times V_{\text{REF}}$ | V           | Gain = 2, see Figure 23                                                                       |

| Capacitive Load Stability                       |     | 2       |                          |     | 2       |                          | nF          | R <sub>L</sub> = ∞                                                                            |

| ,                                               |     | 10      |                          |     | 10      |                          | nF          | $R_L = 1 \text{ k}\Omega$                                                                     |

| Resistive Load <sup>4</sup>                     | 1   |         |                          | 1   |         |                          | kΩ          |                                                                                               |

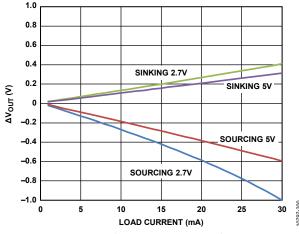

| Load Regulation                                 |     | 80      |                          |     | 80      |                          | μV/mA       | 5 V ± 10%, DAC code = midscale;<br>-30 mA ≤ I <sub>OUT</sub> ≤ +30 mA                         |

|                                                 |     | 80      |                          |     | 80      |                          | μV/mA       | $3 \text{ V} \pm 10\%$ , DAC code = midscale;<br>-20 mA $\leq$ l <sub>0UT</sub> $\leq$ +20 mA |

| Short-Circuit Current⁵                          |     | 40      |                          |     | 40      |                          | mA          |                                                                                               |

| Load Impedance at Rails <sup>6</sup>            |     | 25      |                          |     | 25      |                          | Ω           | See Figure 23                                                                                 |

| Power-Up Time                                   |     | 2.5     |                          |     | 2.5     |                          | μs          | Coming out of power-down mode; $V_{DD} = 5 \text{ V}$                                         |

| REFERENCE INPUT                                 |     |         |                          |     |         |                          |             |                                                                                               |

| Reference Current                               |     | 90      |                          |     | 90      |                          | μΑ          | $V_{REF} = V_{DD} = V_{LOGIC} = 5.5 \text{ V, gain} = 1$                                      |

|                                                 |     | 180     |                          |     | 180     |                          | μA          | $V_{REF} = V_{DD} = V_{LOGIC} = 5.5 \text{ V, gain} = 2$                                      |

| Reference Input Range                           | 1   |         | $V_{DD}$                 | 1   |         | $V_{DD}$                 | V           | Gain = 1                                                                                      |

|                                                 | 1   |         | $V_{DD}/2$               | 1   |         | $V_{\text{DD}}/2$        | V           | Gain = 2                                                                                      |

| Reference Input Impedance                       |     | 16      |                          |     | 16      |                          | kΩ          | Gain = 2                                                                                      |

|                                                 |     | 32      |                          |     | 32      |                          | kΩ          | Gain = 1                                                                                      |

|                                        |                          | A Grade | <sup>1</sup>           |                        | B Grade | , <sup>1</sup>         |      |                                                                                 |

|----------------------------------------|--------------------------|---------|------------------------|------------------------|---------|------------------------|------|---------------------------------------------------------------------------------|

| Parameter                              | Min                      | Тур     | Max                    | Min                    | Тур     | Max                    | Unit | Test Conditions/Comments                                                        |

| LOGIC INPUTS <sup>3</sup>              |                          |         |                        |                        |         |                        |      |                                                                                 |

| Input Current                          |                          |         | ±2                     |                        |         | ±2                     | μΑ   | Per pin                                                                         |

| Input Low Voltage (V <sub>INL</sub> )  |                          |         | $0.3 \times V_{LOGIC}$ |                        |         | $0.3 \times V_{LOGIC}$ | V    |                                                                                 |

| Input High Voltage (V <sub>INH</sub> ) | $0.7 \times V_{LOGIC}$   |         |                        | $0.7 \times V_{LOGIC}$ |         |                        | V    |                                                                                 |

| Pin Capacitance                        |                          | 2       |                        |                        | 2       |                        | рF   |                                                                                 |

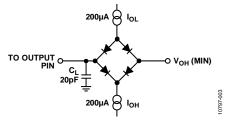

| LOGIC OUTPUTS (SDO) <sup>3</sup>       |                          |         |                        |                        |         |                        |      |                                                                                 |

| Output Low Voltage, Vol                |                          |         | 0.4                    |                        |         | 0.4                    | V    | $I_{SINK} = 200 \mu\text{A}$                                                    |

| Output High Voltage, Vон               | $V_{\text{LOGIC}} - 0.4$ |         |                        | $V_{LOGIC} - 0.4$      |         |                        | V    | $I_{SOURCE} = 200 \mu\text{A}$                                                  |

| Floating State Output<br>Capacitance   |                          | 4       |                        |                        | 4       |                        | pF   |                                                                                 |

| POWER REQUIREMENTS                     |                          |         |                        |                        |         |                        |      |                                                                                 |

| V <sub>LOGIC</sub>                     | 1.8                      |         | 5.5                    | 1.8                    |         | 5.5                    | V    |                                                                                 |

| I <sub>LOGIC</sub>                     |                          |         | 3                      |                        |         | 3                      | μΑ   |                                                                                 |

| $V_{DD}$                               | 2.7                      |         | 5.5                    | 2.7                    |         | 5.5                    | V    | Gain = 1                                                                        |

|                                        | $V_{REF} + 1.5$          |         | 5.5                    | $V_{REF} + 1.5$        |         | 5.5                    | V    | Gain = 2                                                                        |

| I <sub>DD</sub>                        |                          |         |                        |                        |         |                        |      | $V_{IH} = V_{DD}$ , $V_{IL} = GND$ , $V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}$ |

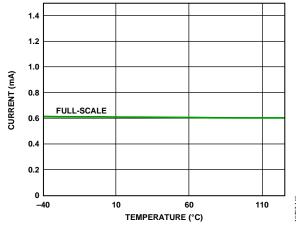

| Normal Mode <sup>7</sup>               |                          | 0.59    | 0.7                    |                        | 0.59    | 0.7                    | mA   |                                                                                 |

| All Power-Down Modes <sup>8</sup>      |                          | 1       | 4                      |                        | 1       | 4                      | μΑ   | -40°C to +85°C                                                                  |

|                                        |                          |         | 6                      |                        |         | 6                      | μΑ   | -40°C to +105°C                                                                 |

<sup>&</sup>lt;sup>1</sup> Temperature range, A and B grade: -40°C to +105°C.

<sup>3</sup> Guaranteed by design and characterization; not production tested.

$^{7}$  Interface inactive. All DACs active. DAC outputs unloaded.

<sup>&</sup>lt;sup>2</sup> DC specifications tested with the outputs unloaded, unless otherwise noted. Upper dead band = 10 mV and exists only when  $V_{REF} = V_{DD}$  with gain = 1 or when  $V_{REF}/2 = V_{DD}$  with gain = 2. Linearity calculated using a reduced code range of 256 to 65,280 (AD5686) or 12 to 4080 (AD5684).

<sup>&</sup>lt;sup>4</sup> Channel A and Channel B can have a combined output current of up to 30 mA. Similarly, Channel C and Channel D can have a combined output current of up to 30 mA up to a junction temperature of 110°C.

<sup>&</sup>lt;sup>5</sup> V<sub>DD</sub> = 5 V. The device includes current limiting that is intended to protect the device during temporary overload conditions. Junction temperature can be exceeded during current limit. Operation above the specified maximum operation junction temperature may impair device reliability.

<sup>&</sup>lt;sup>6</sup> When drawing a load current at either rail, the output voltage headroom with respect to that rail is limited by the 25 Ω typical channel resistance of the output devices. For example, when sinking 1 mA, the minimum output voltage =  $25 \Omega \times 1 \text{ mA} = 25 \text{ mV}$  (see Figure 23).

<sup>&</sup>lt;sup>8</sup> All DACs powered down.

# **AC CHARACTERISTICS**

$V_{DD} = 2.7 \text{ V to } 5.5 \text{ V}; V_{REF} = 2.5 \text{ V}; 1.8 \text{ V} \leq V_{LOGIC} \leq 5.5 \text{ V}; R_L = 2 \text{ k}\Omega \text{ to GND}; C_L = 200 \text{ pF to GND}; all specifications } T_{MIN} \text{ to } T_{MAX}, \text{ unless } T_{MIN} \text{ to } T_{MAX}, \text{ to } T_{MAX},$ otherwise noted.1

Table 3.

| Parameter <sup>2</sup>           | Min | Тур  | Max | Unit   | Test Conditions/Comments <sup>3</sup>                      |

|----------------------------------|-----|------|-----|--------|------------------------------------------------------------|

| Output Voltage Settling Time     |     |      |     |        |                                                            |

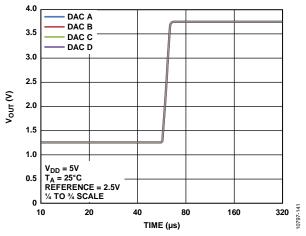

| AD5686                           |     | 5    | 8   | μs     | 1/4 to 3/4 scale settling to ±2 LSB                        |

| AD5684                           |     | 5    | 7   | μs     | 1/4 to 3/4 scale settling to ±2 LSB                        |

| Slew Rate                        |     | 8.0  |     | V/µs   |                                                            |

| Digital-to-Analog Glitch Impulse |     | 0.5  |     | nV-sec | 1 LSB change around major carry                            |

| Digital Feedthrough              |     | 0.13 |     | nV-sec |                                                            |

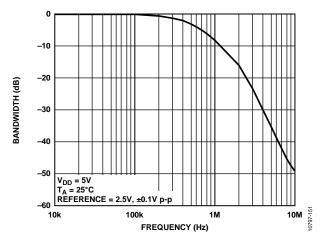

| Multiplying Bandwidth            |     | 500  |     | kHz    |                                                            |

| Digital Crosstalk                |     | 0.1  |     | nV-sec |                                                            |

| Analog Crosstalk                 |     | 0.2  |     | nV-sec |                                                            |

| DAC-to-DAC Crosstalk             |     | 0.3  |     | nV-sec |                                                            |

| Total Harmonic Distortion⁴       |     | -80  |     | dB     | At ambient, BW = 20 kHz, $V_{DD}$ = 5 V, $f_{OUT}$ = 1 kHz |

| Output Noise Spectral Density    |     | 100  |     | nV/√Hz | DAC code = midscale, 10 kHz; gain = 2                      |

| Output Noise                     |     | 6    |     | μV p-p | 0.1 Hz to 10 Hz                                            |

| SNR                              |     | 90   |     | dB     | At ambient, BW = 20 kHz, $V_{DD}$ = 5 V, $f_{OUT}$ = 1 kHz |

| SFDR                             |     | 83   |     | dB     | At ambient, BW = 20 kHz, $V_{DD}$ = 5 V, $f_{OUT}$ = 1 kHz |

| SINAD                            |     | 80   |     | dB     | At ambient, BW = 20 kHz, $V_{DD}$ = 5 V, $f_{OUT}$ = 1 kHz |

$<sup>^{\</sup>rm 1}$  Guaranteed by design and characterization; not production tested.  $^{\rm 2}$  See the Terminology section.

$<sup>^3</sup>$  Temperature range is  $-40^\circ$ C to  $+105^\circ$ C, typical @ 25°C.  $^4$  Digitally generated sine wave @ 1 kHz.

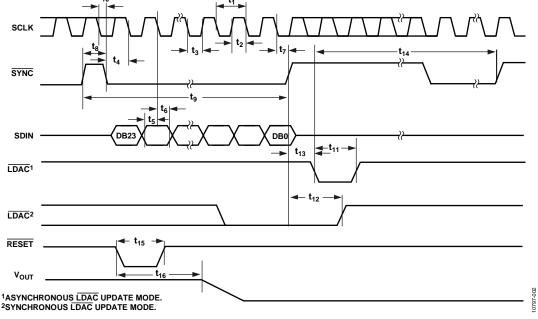

# **TIMING CHARACTERISTICS**

All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of ( $V_{IL} + V_{IH}$ )/2. See Figure 2.  $V_{DD} = 2.7$  V to 5.5 V, 1.8 V  $\leq$  V<sub>LOGIC</sub>  $\leq$  5.5 V;  $V_{REF} = 2.5$  V. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 4.

|                                                              |                       | 1.8 V ≤ V | LOGIC < 2.7 V | 2.7 V ≤ \ | /LOGIC ≤ 5.5 V |      |

|--------------------------------------------------------------|-----------------------|-----------|---------------|-----------|----------------|------|

| Parameter <sup>1</sup>                                       | Symbol                | Min       | Max           | Min       | Max            | Unit |

| SCLK Cycle Time                                              | t <sub>1</sub>        | 33        |               | 20        |                | ns   |

| SCLK High Time                                               | t <sub>2</sub>        | 16        |               | 10        |                | ns   |

| SCLK Low Time                                                | t <sub>3</sub>        | 16        |               | 10        |                | ns   |

| SYNC to SCLK Falling Edge Setup Time                         | t <sub>4</sub>        | 15        |               | 10        |                | ns   |

| Data Setup Time                                              | <b>t</b> <sub>5</sub> | 5         |               | 5         |                | ns   |

| Data Hold Time                                               | t <sub>6</sub>        | 5         |               | 5         |                | ns   |

| SCLK Falling Edge to SYNC Rising Edge                        | <b>t</b> <sub>7</sub> | 15        |               | 10        |                | ns   |

| Minimum SYNC High Time                                       | t <sub>8</sub>        | 20        |               | 20        |                | ns   |

| SYNC Rising Edge to SYNC Rising Edge (DAC Register Update/s) | t <sub>9</sub>        | 870       |               | 830       |                | ns   |

| SYNC Falling Edge to SCLK Fall Ignore                        | t <sub>10</sub>       | 16        |               | 10        |                | ns   |

| LDAC Pulse Width Low                                         | t <sub>11</sub>       | 25        |               | 15        |                | ns   |

| SYNC Rising Edge to LDAC Rising Edge                         | t <sub>12</sub>       | 50        |               | 20        |                | ns   |

| SYNC Rising Edge to LDAC Falling Edge                        | t <sub>13</sub>       | 30        |               | 30        |                | ns   |

| LDAC Falling Edge to SYNC Rising Edge                        | t <sub>14</sub>       | 840       |               | 800       |                | ns   |

| Minimum Pulse Width Low                                      | t <sub>15</sub>       | 30        |               | 30        |                | ns   |

| Pulse Activation Time                                        | t <sub>16</sub>       | 30        |               | 30        |                | ns   |

| Power-Up Time <sup>2</sup>                                   |                       | 4.5       |               | 4.5       |                | μs   |

$<sup>^1</sup>$  Maximum SCLK frequency is 50 MHz at  $V_{DD} = 2.7 \text{ V}$  to 5.5 V, 1.8 V  $\leq$   $V_{LOGIC} \leq$   $V_{DD}$ . Guaranteed by design and characterization; not production tested.

<sup>&</sup>lt;sup>2</sup> Time to exit power-down to normal mode of AD5686/AD5684 operation, 32<sup>nd</sup> clock edge to 90% of DAC midscale value, with output unloaded.

Figure 2. Serial Write Operation

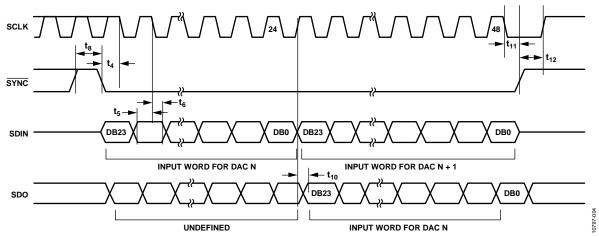

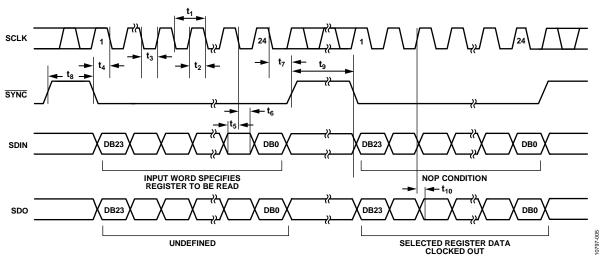

# **DAISY-CHAIN AND READBACK TIMING CHARACTERISTICS**

All input signals are specified with  $t_R = t_F = 1$  ns/V (10% to 90% of  $V_{DD}$ ) and timed from a voltage level of  $(V_{IL} + V_{IH})/2$ . See Figure 4 and Figure 5.  $V_{DD} = 2.7$  V to 5.5 V, 1.8 V  $\leq V_{LOGIC} \leq$  5.5 V;  $V_{REF} = 2.5$  V. All specifications  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.

Table 5.

|                                       |                       | 1.8 \ | $V \leq V_{LOGIC} < 2.7 V$ | 2.7 \ | / ≤ V <sub>LOGIC</sub> ≤ 5.5 V |      |

|---------------------------------------|-----------------------|-------|----------------------------|-------|--------------------------------|------|

| Parameter <sup>1</sup>                | Symbol                | Min   | Max                        | Min   | Max                            | Unit |

| SCLK Cycle Time                       | t <sub>1</sub>        | 66    |                            | 40    |                                | ns   |

| SCLK High Time                        | t <sub>2</sub>        | 33    |                            | 20    |                                | ns   |

| SCLK Low Time                         | t <sub>3</sub>        | 33    |                            | 20    |                                | ns   |

| SYNC to SCLK Falling Edge             | t <sub>4</sub>        | 33    |                            | 20    |                                | ns   |

| Data Setup Time                       | <b>t</b> <sub>5</sub> | 5     |                            | 5     |                                | ns   |

| Data Hold Time                        | t <sub>6</sub>        | 5     |                            | 5     |                                | ns   |

| SCLK Falling Edge to SYNC Rising Edge | t <sub>7</sub>        | 15    |                            | 10    |                                | ns   |

| Minimum SYNC High Time                | t <sub>8</sub>        | 60    |                            | 30    |                                | ns   |

| Minimum SYNC High Time                | t <sub>9</sub>        | 60    |                            | 30    |                                | ns   |

| SDO Data Valid from SCLK Rising Edge  | t <sub>10</sub>       |       | 36                         |       | 25                             | ns   |

| SCLK Falling Edge to SYNC Rising Edge | t <sub>11</sub>       | 15    |                            | 10    |                                | ns   |

| SYNC Rising Edge to SCLK Rising Edge  | t <sub>12</sub>       | 15    |                            | 10    |                                | ns   |

<sup>&</sup>lt;sup>1</sup> Maximum SCLK frequency is 25 MHz or 15 MHz at V<sub>DD</sub> = 2.7 V to 5.5 V, 1.8 V ≤ V<sub>LOGIC</sub> ≤ V<sub>DD</sub>. Guaranteed by design and characterization; not production tested.

# **Circuit and Timing Diagrams**

Figure 3. Load Circuit for Digital Output (SDO) Timing Specifications

Figure 4. Daisy-Chain Timing Diagram

Figure 5. Readback Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 6.

| Parameter                              | Rating                                        |

|----------------------------------------|-----------------------------------------------|

| V <sub>DD</sub> to GND                 | −0.3 V to +7 V                                |

| V <sub>LOGIC</sub> to GND              | −0.3 V to +7 V                                |

| Vout to GND                            | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$    |

| $V_{REF}$ to GND                       | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$    |

| Digital Input Voltage to GND           | $-0.3 \text{ V to V}_{LOGIC} + 0.3 \text{ V}$ |

| Operating Temperature Range            | −40°C to +105°C                               |

| Storage Temperature Range              | −65°C to +150°C                               |

| Junction Temperature                   | 125°C                                         |

| 16-Lead TSSOP, θ <sub>JA</sub> Thermal | 112.6°C/W                                     |

| Impedance, 0 Airflow (4-Layer Board)   |                                               |

| 16-Lead LFCSP, θ <sub>JA</sub> Thermal | 70°C/W                                        |

| Impedance, 0 Airflow (4-Layer Board)   |                                               |

| Reflow Soldering Peak                  | 260°C                                         |

| Temperature, Pb Free (J-STD-020)       |                                               |

| ESD                                    |                                               |

| HBM <sup>1</sup>                       | 4 kV                                          |

| FICDM                                  | 1.5 kV                                        |

<sup>&</sup>lt;sup>1</sup> Human body model (HBM) classification.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

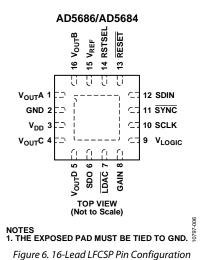

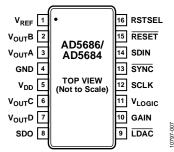

# PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 7. 16-Lead TSSOP Pin Configuration

**Table 7. Pin Function Descriptions**

| F     | Pin No. | _                  |                                                                                                                                                                                                                                                                                    |

|-------|---------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LFCSP | TSSOP   | Mnemonic           | Description                                                                                                                                                                                                                                                                        |

| 1     | 3       | V <sub>OUT</sub> A | Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                 |

| 2     | 4       | GND                | Ground Reference Point for All Circuitry on the Part.                                                                                                                                                                                                                              |

| 3     | 5       | $V_{DD}$           | Power Supply Input. These parts can be operated from 2.7 V to 5.5 V, and the supply should be decoupled with a 10 $\mu$ F capacitor in parallel with a 0.1 $\mu$ F capacitor to GND.                                                                                               |

| 4     | 6       | V <sub>OUT</sub> C | Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                 |

| 5     | 7       | VoutD              | Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                 |

| 6     | 8       | SDO                | Serial Data Output. Can be used to daisy-chain a number of AD5686/AD5684 devices together or can be used for readback. The serial data is transferred on the rising edge of SCLK and is valid on the falling edge of the clock.                                                    |

| 7     | 9       | LDAC               | LDAC can be operated in two modes, asynchronously and synchronously. Pulsing this pin low allows any or all DAC registers to be updated if the input registers have new data. This allows all DAC outputs to be simultaneously updated. This pin can also be tied permanently low. |

| 8     | 10      | GAIN               | Span Set Pin. When this pin is tied to GND, all four DAC outputs have a span from 0 V to $V_{REF}$ . When this pin is tied to $V_{LOGIC}$ , all four DAC outputs have a span from 0 V to 2 $\times$ $V_{REF}$ .                                                                    |

| 9     | 11      | V <sub>LOGIC</sub> | Digital Power Supply. Voltage ranges from 1.8 V to 5.5 V.                                                                                                                                                                                                                          |

| 10    | 12      | SCLK               | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates of up to 50 MHz.                                                                                                                 |

| 11    | 13      | SYNC               | Active Low Control Input. This is the frame synchronization signal for the input data. When SYNC goes low, data is transferred in on the falling edges of the next 24 clocks.                                                                                                      |

| 12    | 14      | SDIN               | Serial Data Input. These devices have a 24-bit input shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                              |

| 13    | 15      | RESET              | Asynchronous Reset Input. The RESET input is falling edge sensitive. When RESET is low, all LDAC pulses are ignored. When RESET is activated, the input register and the DAC register are updated with zero scale or midscale, depending on the state of the RSTSEL pin.           |

| 14    | 16      | RSTSEL             | Power-On Reset Pin. Tying this pin to GND powers up all four DACs to zero scale. Tying this pin to VLOGIC powers up all four DACs to midscale.                                                                                                                                     |

| 15    | 1       | $V_{REF}$          | Reference Input Voltage.                                                                                                                                                                                                                                                           |

| 16    | 2       | V <sub>оит</sub> В | Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                 |

| 17    | N/A     | EPAD               | Exposed Pad. The exposed pad must be tied to GND.                                                                                                                                                                                                                                  |

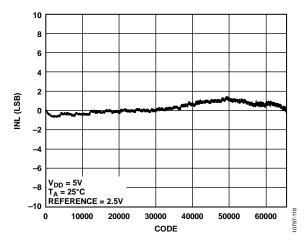

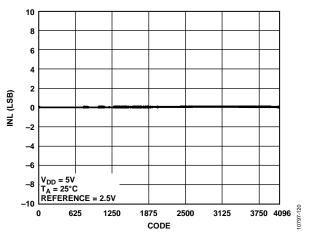

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 8. AD5686 INL

Figure 9. AD5684 INL

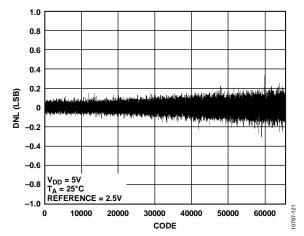

Figure 10. AD5686 DNL

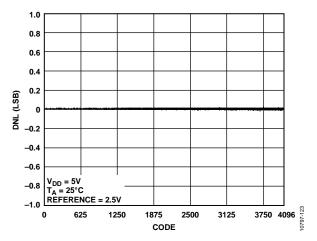

Figure 11. AD5684 DNL

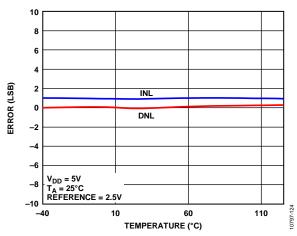

Figure 12. INL Error and DNL Error vs. Temperature

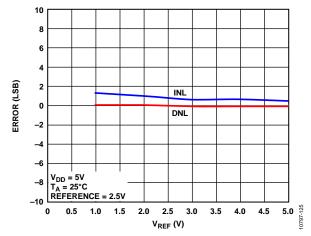

Figure 13. INL Error and DNL Error vs. V<sub>REF</sub>

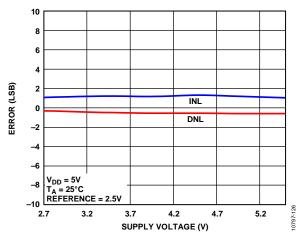

Figure 14. INL Error and DNL Error vs. Supply Voltage

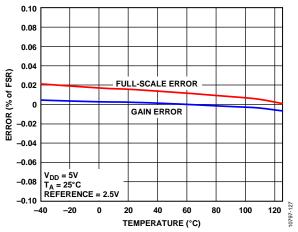

Figure 15. Gain Error and Full-Scale Error vs. Temperature

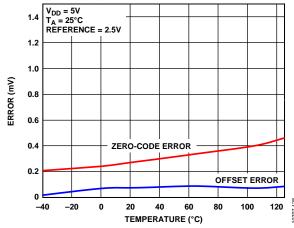

Figure 16. Zero-Code Error and Offset Error vs. Temperature

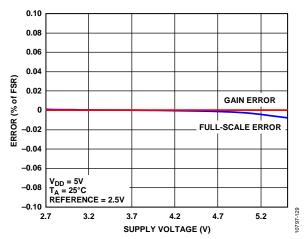

Figure 17. Gain Error and Full-Scale Error vs. Supply Voltage

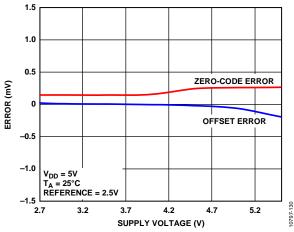

Figure 18. Zero-Code Error and Offset Error vs. Supply Voltage

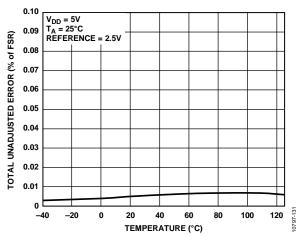

Figure 19. TUE vs. Temperature

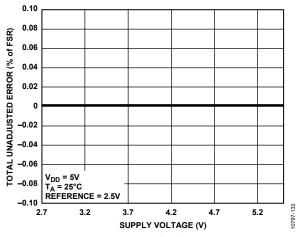

Figure 20. TUE vs. Supply Voltage, Gain = 1

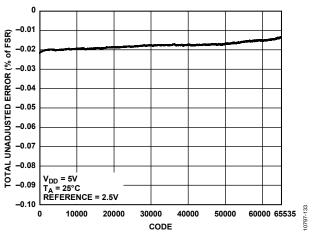

Figure 21. TUE vs. Code

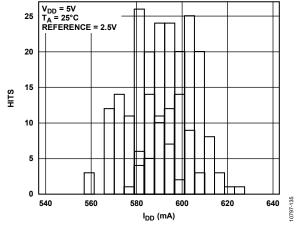

Figure 22. IDD Histogram

Figure 23. Headroom/Footroom vs. Load Current

Figure 24. Source and Sink Capability at 5  $\it V$

Figure 25. Source and Sink Capability at 3 V

Figure 26. Supply Current vs. Temperature

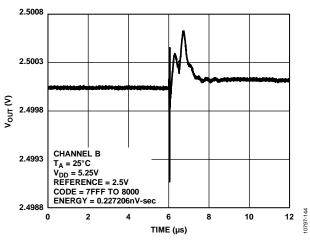

Figure 27. Settling Time, 5 V

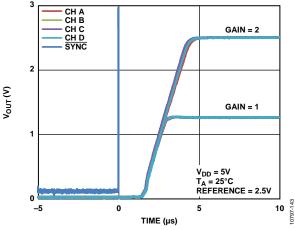

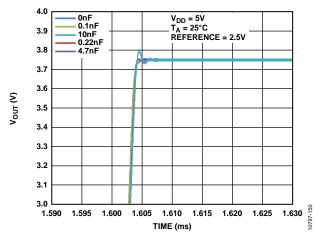

Figure 29. Exiting Power-Down to Midscale

Figure 30. Digital-to-Analog Glitch Impulse

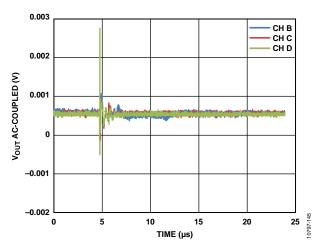

Figure 31. Analog Crosstalk, Channel A

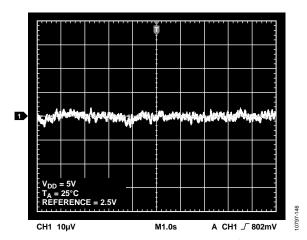

Figure 32. 0.1 Hz to 10 Hz Output Noise Plot

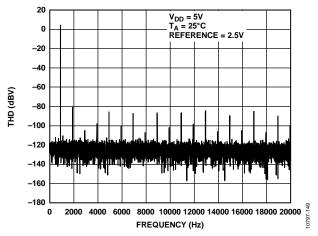

Figure 33. Total Harmonic Distortion @ 1 kHz

Figure 34. Settling Time vs. Capacitive Load

Figure 35. Multiplying Bandwidth, Reference = 2.5 V,  $\pm$ 0.1 V p-p, 10 kHz to 10 MHz

# **TERMINOLOGY**

# Relative Accuracy or Integral Nonlinearity (INL)

For the DAC, relative accuracy or integral nonlinearity is a measurement of the maximum deviation, in LSBs, from a straight line passing through the endpoints of the DAC transfer function. A typical INL vs. code plot is shown in Figure 8.

### Differential Nonlinearity (DNL)

Differential nonlinearity is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of  $\pm 1$  LSB maximum ensures monotonicity. These DACs are guaranteed monotonic by design. A typical DNL vs. code plot can be seen in Figure 10.

### **Zero-Code Error**

Zero-code error is a measurement of the output error when zero code (0x0000) is loaded to the DAC register. Ideally, the output should be 0 V. The zero-code error is always positive in the AD5686/AD5684 because the output of the DAC cannot go below 0 V due to a combination of the offset errors in the DAC and the output amplifier. Zero-code error is expressed in mV. A plot of zero-code error vs. temperature can be seen in Figure 16.

### **Full-Scale Error**

Full-scale error is a measurement of the output error when full-scale code (0xFFFF) is loaded to the DAC register. Ideally, the output should be  $V_{\rm DD}-1$  LSB. Full-scale error is expressed in percent of full-scale range (% of FSR). A plot of full-scale error vs. temperature can be seen in Figure 15.

#### **Gain Error**

Gain error is a measurement of the span error of the DAC. It is the deviation in slope of the DAC transfer characteristic from the ideal expressed as % of FSR.

### Offset Error Drift

Offset error drift is a measurement of the change in offset error with a change in temperature. It is expressed in  $\mu V/^{\circ}C$ .

### **Gain Temperature Coefficient**

Gain temperature coefficient is a measurement of the change in gain error with changes in temperature. It is expressed in ppm of FSR/°C.

#### **Offset Error**

Offset error is a measurement of the difference between  $V_{\text{OUT}}$  (actual) and  $V_{\text{OUT}}$  (ideal) expressed in mV in the linear region of the transfer function. It can be negative or positive.

### DC Power Supply Rejection Ratio (PSRR)

DC PSRR indicates how the output of the DAC is affected by changes in the supply voltage. PSRR is the ratio of the change in  $V_{\text{OUT}}$  to a change in  $V_{\text{DD}}$  for full-scale output of the DAC. It is measured in mV/V.  $V_{\text{REF}}$  is held at 2.5 V, and  $V_{\text{DD}}$  is varied by  $\pm 10\%$ .

### **Output Voltage Settling Time**

The output voltage setting time is the amount of time it takes for the output of a DAC to settle to a specified level for a  $\frac{1}{4}$  to  $\frac{3}{4}$  full-scale input change and is measured from the rising edge of  $\frac{1}{2}$

# Digital-to-Analog Glitch Impulse

Digital-to-analog glitch impulse is the impulse injected into the analog output when the input code in the DAC register changes state. It is normally specified as the area of the glitch in nV-sec, and is measured when the digital input code is changed by 1 LSB at the major carry transition (0x7FFF to 0x8000) (see Figure 30).

## Digital Feedthrough

Digital feedthrough is a measure of the impulse injected into the analog output of the DAC from the digital inputs of the DAC, but is measured when the DAC output is not updated. It is specified in nV-sec and measured with a full-scale code change on the data bus, that is, from all 0s to all 1s and vice versa.

# **Noise Spectral Density**

Noise spectral density is a measurement of the internally generated random noise. Random noise is characterized as a spectral density ( $nV/\sqrt{Hz}$ ). It is measured by loading the DAC to midscale and measuring noise at the output. It is measured in  $nV/\sqrt{Hz}$ .

### DC Crosstalk

DC crosstalk is the dc change in the output level of one DAC in response to a change in the output of another DAC. It is measured with a full-scale output change on one DAC (or soft power-down and power-up) while monitoring another DAC kept at midscale. It is expressed in  $\mu V$ .

DC crosstalk due to load current change is a measurement of the impact that a change in load current on one DAC has to another DAC kept at midscale. It is expressed in  $\mu V/mA$ .

### **Digital Crosstalk**

Digital crosstalk is the glitch impulse transferred to the output of one DAC at midscale in response to a full-scale code change (all 0s to all 1s and vice versa) in the input register of another DAC. It is measured in standalone mode and is expressed in nV-sec.

# **Analog Crosstalk**

Analog crosstalk is the glitch impulse transferred to the output of one DAC due to a change in the output of another DAC. It is measured by loading one of the input registers with a full-scale code change (all 0s to all 1s and vice versa). Then execute a software LDAC and monitor the output of the DAC whose digital code was not changed. The area of the glitch is expressed in nV-sec.

### **DAC-to-DAC Crosstalk**

DAC-to-DAC crosstalk is the glitch impulse transferred to the output of one DAC in response to a digital code change and subsequent analog output change of another DAC. It is measured by loading the attack channel with a full-scale code change (all 0s to all 1s and vice versa) using the write to and update commands while monitoring the output of another channel that is at midscale. The energy of the glitch is expressed in nV-sec.

### **Multiplying Bandwidth**

The amplifiers within the DAC have a finite bandwidth. The multiplying bandwidth is a measure of this. A sine wave on the reference (with full-scale code loaded to the DAC) appears on the output.

# **Total Harmonic Distortion (THD)**

THD is the difference between an ideal sine wave and its attenuated version using the DAC. The sine wave is used as the reference for the DAC, and the THD is a measurement of the harmonics present on the DAC output. It is measured in dB.

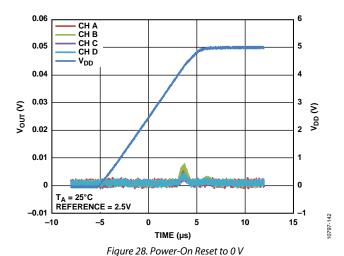

# THEORY OF OPERATION DIGITAL-TO-ANALOG CONVERTER

The AD5686/AD5684 are quad, 16-/12-bit, serial input, voltage output DACs. The parts operate from supply voltages of 2.7 V to 5.5 V. Data is written to the AD5686/AD5684 in a 24-bit word format via a 3-wire serial interface. The AD5686/AD5684 incorporate a power-on reset circuit to ensure that the DAC output powers up to a known output state. The devices also have a software power-down mode that reduces the typical current consumption to typically 4  $\mu A$ .

### TRANSFER FUNCTION

Because the input coding to the DAC is straight binary, the ideal output voltage when using an external reference is given by

$$V_{OUT} = V_{REF} \times Gain \left[ \frac{D}{2^{N}} \right]$$

where:

*D* is the decimal equivalent of the binary code that is loaded to the DAC register as follows:

0 to 4095 for the 12-bit device.

0 to 65,535 for the 16-bit device.

*N* is the DAC resolution.

$V_{REF}$  is the value of the external reference.

*Gain* is the gain of the output amplifier and is set to 1 by default. The gain can be set to  $\times 1$  or  $\times 2$  using the gain select pin. When this pin is tied to GND, all four DAC outputs have a span of 0 V to  $V_{REF}$ . When this pin is tied to  $V_{DD}$ , all four DAC outputs have a span of 0 V to  $2 \times V_{REF}$ .

## **DAC ARCHITECTURE**

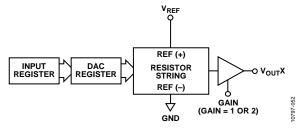

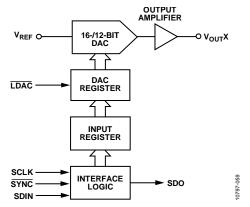

The DAC architecture consists of a string DAC followed by an output amplifier. Figure 36 shows a block diagram of the DAC architecture.

Figure 36. Single DAC Channel Architecture Block Diagram

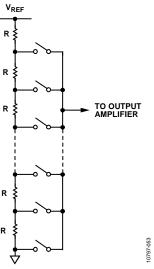

The resistor string structure is shown in Figure 37. It is a string of resistors, each of Value R. The code loaded to the DAC register determines the node on the string where the voltage is to be tapped off and fed into the output amplifier. The voltage is tapped off by closing one of the switches connecting the string to the amplifier. Because the DAC is a string of resistors, it is guaranteed monotonic.

Figure 37. Resistor String Structure

### **Output Amplifiers**

The output buffer amplifier can generate rail-to-rail voltages on its output, which gives an output range of 0 V to  $V_{\rm DD}$ . The actual range depends on the value of  $V_{\rm REF}$ , the GAIN pin, offset error, and gain error. The GAIN pin selects the gain of the output.

- If this pin is tied to GND, all four outputs have a gain of 1, and the output range is 0 V to V<sub>REF</sub>.

- If this pin is tied to V<sub>DD</sub>, all four outputs have a gain of 2, and the output range is 0 V to 2 × V<sub>REF</sub>.

These amplifiers are capable of driving a load of 1 k $\Omega$  in parallel with 2 nF to GND. The slew rate is 0.8 V/ $\mu$ s with a  $\frac{1}{4}$  to  $\frac{3}{4}$  scale settling time of 5  $\mu$ s.

### **SERIAL INTERFACE**

The AD5686/AD5684 have a 3-wire serial interface (SYNC, SCLK, and SDIN) that is compatible with SPI, QSPI™, and MICROWIRE® interface standards as well as most DSPs. See Figure 2 for a timing diagram of a typical write sequence. The AD5686/AD5684 contain an SDO pin to allow the user to daisy-chain multiple devices together (see the Daisy-Chain Operation section) or for readback.

# **Input Shift Register**

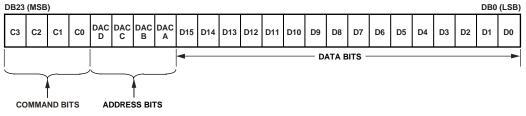

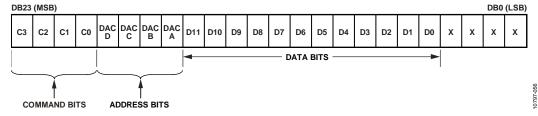

The input shift register of the AD5686/AD5684 is 24 bits wide. Data is loaded MSB first (DB23). The first four bits are the command bits, C3 to C0 (see Table 8), followed by the 4-bit DAC address bits, DAC A, DAC B, DAC C, and DAC D (see Table 9), and finally the bit data-word.

For the AD5686, the data-word comprises 16-bit input code(see Figure 38). For the AD5684, the data-word comprises 12-bit input code, followed by zero or four don't care bits (see Figure 39). These data bits are transferred to the input register on the 24 falling edges of SCLK and are updated on the rising edge of SYNC.

Commands can be executed on individual DAC channels, combined DAC channels, or on all DACs, depending on the address bits selected (see Table 9).

**Table 8. Command Bit Definitions**

| Command Bits |    | ts         |    |                                                                    |  |  |

|--------------|----|------------|----|--------------------------------------------------------------------|--|--|

| C3           | C2 | <b>C</b> 1 | CO | Description                                                        |  |  |

| 0            | 0  | 0          | 0  | No operation                                                       |  |  |

| 0            | 0  | 0          | 1  | Write to Input Register n (dependent on $\overline{\text{LDAC}}$ ) |  |  |

| 0            | 0  | 1          | 0  | Update DAC Register n with contents of Input<br>Register n         |  |  |

| 0            | 0  | 1          | 1  | Write to and update DAC Channel n                                  |  |  |

| 0            | 1  | 0          | 0  | Power down/power up DAC                                            |  |  |

| 0            | 1  | 0          | 1  | Hardware LDAC mask register                                        |  |  |

| 0            | 1  | 1          | 0  | Software reset (power-on reset)                                    |  |  |

| 0            | 1  | 1          | 1  | Reserved                                                           |  |  |

| 1            | 0  | 0          | 0  | Set up DCEN register (daisy-chain enable)                          |  |  |

| 1            | 0  | 0          | 1  | Set up readback register (readback enable)                         |  |  |

| 1            | 0  | 1          | 0  | Reserved                                                           |  |  |

|              |    |            |    | Reserved                                                           |  |  |

| 1            | 1  | 1          | 1  | Reserved                                                           |  |  |

Table 9. Address Bits and Selected DACs

|       | Addre | ss Bits |       |                                   |

|-------|-------|---------|-------|-----------------------------------|

| DAC D | DAC C | DAC B   | DAC A | Selected DAC Channel <sup>1</sup> |

| 0     | 0     | 0       | 1     | DAC A                             |

| 0     | 0     | 1       | 0     | DAC B                             |

| 0     | 1     | 0       | 0     | DAC C                             |

| 1     | 0     | 0       | 0     | DAC D                             |

| 0     | 0     | 1       | 1     | DAC A and DAC B                   |

| 1     | 1     | 1       | 1     | All DACs                          |

<sup>&</sup>lt;sup>1</sup> Any combination of DAC channels can be selected using the address bits.

Figure 38. AD5686 Input Shift Register Contents

Figure 39. AD5684 Input Shift Register Contents

### STANDALONE OPERATION

The write sequence begins by bringing the  $\overline{SYNC}$  line low. Data from the SDIN line is clocked into the 24-bit input shift register on the falling edge of SCLK. After the last of 24 data bits is clocked in,  $\overline{SYNC}$  should be brought high. The programmed function is then executed, that is, an  $\overline{LDAC}$ -dependent change in DAC register contents and/or a change in the mode of operation. If  $\overline{SYNC}$  is taken high at a clock before the 24<sup>th</sup> clock, it is considered a valid frame and invalid data may be loaded to the DAC.  $\overline{SYNC}$  must be brought high for a minimum of 20 ns (single channel, see t<sub>8</sub> in Figure 2) before the next write sequence so that a falling edge of  $\overline{SYNC}$  can initiate the next write sequences for even lower power operation of the part. The  $\overline{SYNC}$  line is kept low for 24 falling edges of SCLK, and the DAC is updated on the rising edge of  $\overline{SYNC}$ .

After data is transferred into the input register of the addressed DAC, all DAC registers and outputs can be updated by taking LDAC low while the SYNC line is high.

### WRITE AND UPDATE COMMANDS

# Write to Input Register n (Dependent on LDAC)

Command 0001 allows the user to write to each DAC's dedicated input register individually. When  $\overline{LDAC}$  is low, the input register is transparent (if not controlled by the  $\overline{LDAC}$  mask register).

### Update DAC Register n with Contents of Input Register n

Command 0010 loads the DAC registers/outputs with the contents of the selected input registers and updates the DAC outputs directly.

# Write to and Update DAC Channel n (Independent of $\overline{LDAC}$ )

Command 0011 allows the user to write to the DAC registers and update the DAC outputs directly.

# **DAISY-CHAIN OPERATION**

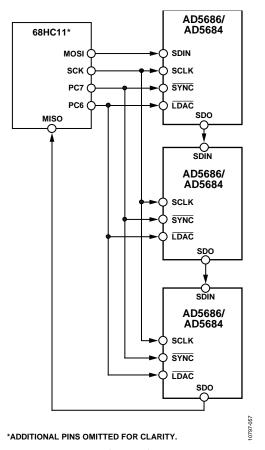

For systems that contain several DACs, the SDO pin can be used to daisy-chain several devices together. This function is enabled through a software executable daisy-chain enable (DCEN) command. Command 1000 is reserved for this DCEN function (see Table 8). The daisy-chain mode is enabled by setting Bit DB0 in the DCEN register. The default setting is standalone mode, where DB0 = 0. Table 10 shows how the state of the bit corresponds to the mode of operation of the device.

Table 10. Daisy-Chain Enable (DCEN) Register

| DB0 | Description               |

|-----|---------------------------|

| 0   | Standalone mode (default) |

| 1   | DCEN mode                 |

Figure 40. Daisy-Chaining the AD5686/AD5684

The SCLK pin is continuously applied to the input shift register when SYNC is low. If more than 24 clock pulses are applied, the data ripples out of the input shift register and appears on the SDO line. This data is clocked out on the rising edge of SCLK and is valid on the falling edge. By connecting the SDO line to the SDIN input on the next DAC in the chain, a daisy-chain interface is constructed. Each DAC in the system requires 24 clock pulses. Therefore, the total number of clock cycles must equal  $24 \times N$ , where N is the total number of devices that are updated. If SYNC is taken high at a clock that is not a multiple of 24, it is considered a valid frame and invalid data may be loaded to the DAC. When the serial transfer to all devices is complete, SYNC is taken high. This latches the input data in each device in the daisy chain and prevents any further data from being clocked into the input shift register. The serial clock can be continuous or a gated clock. A continuous SCLK source can be used only if SYNC can be held low for the correct number of clock cycles. In gated clock mode, a burst clock containing the exact number of clock cycles must be used, and SYNC must be taken high after the final clock to latch the data.

### READBACK OPERATION

Readback mode is invoked through a software executable readback command. If the SDO output is disabled via the daisy-chain mode disable bit in the control register, it is automatically enabled for the duration of the read operation, after which it is disabled again. Command 1001 is reserved for the readback function. This command, in association with selecting one of the address bits, DAC A to DAC D, selects the register to read. Note that only one DAC register can be selected during readback. The remaining three address bits must be set to Logic 0. The remaining data bits in the write sequence are don't care bits. If more than one or no bits are selected, DAC Channel A is read back by default. During the next SPI write, the data appearing on the SDO output contains the data from the previously addressed register.

For example, to read back the DAC register for Channel A, the following sequence should be implemented:

- Write 0x900000 to the AD5686/AD5684 input register.

This configures the part for read mode with the DAC register of Channel A selected. Note that all data bits, DB15 to DB0, are don't care bits.

- Follow this with a second write, a NOP condition, 0x0000000. During this write, the data from the register is clocked out on the SDO line. DB23 to DB20 contain undefined data, and the last 16 bits contain the DB19 to DB4 DAC register contents.

### **POWER-DOWN OPERATION**

The AD5686/AD5684 provide three separate power-down modes (see Table 11). Command 0100 is designated for the power-down function (see Table 8). These power-down modes are software programmable by setting eight bits, Bit DB7 to Bit DB0, in the input shift register. Two bits are associated with each DAC channel. Table 11 shows how the state of the two bits corresponds to the mode of operation of the device.

Table 11. Modes of Operation

| Operating Mode        | PDx1 | PDx0 |

|-----------------------|------|------|

| Normal Operation      | 0    | 0    |

| Power-Down Modes      |      |      |

| 1 kΩ to GND           | 0    | 1    |

| 100 k $\Omega$ to GND | 1    | 0    |

| Three-State           | 1    | 1    |

Any or all DACs (DAC A to DAC D) can be powered down to the selected mode by setting the corresponding bits. See Table 12 for the contents of the input shift register during the power-down/power-up operation.

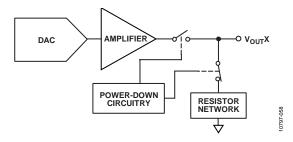

When both Bit PDx1 and Bit PDx0 (where x is the channel selected) in the input shift register are set to 0, the parts work normally with their normal power consumption of 0.59 mA at 5 V. However, for the three power-down modes, the supply current falls to 4  $\mu A$  at 5 V. Not only does the supply current fall, but the output stage is also internally switched from the output of the amplifier to a resistor network of known values. This has the advantage that the output impedance of the part is known while the part is in power-down mode. There are three different power-down options (see Table 11). The output is connected internally to GND through either a 1  $k\Omega$  or a 100  $k\Omega$  resistor, or it is left open-circuited (three-state). The output stage is illustrated in Figure 41.

Figure 41. Output Stage During Power-Down

The bias generator, output amplifier, resistor string, and other associated linear circuitry are shut down when the power-down mode is activated. However, the contents of the DAC registers are unaffected when in power-down. The DAC registers can be updated while the device is in power-down mode. The time required to exit power-down is typically 4.5  $\mu s$  for  $V_{\rm DD}$  = 5 V.

Table 12. 24-Bit Input Shift Register Contents for Power-Down/Power-Up Operation<sup>1</sup>

| DB23                    | DB22 | DB21 | DB20                      | DB19 to DB16 | DB15<br>to<br>DB8          | DB7  | DB6  | DB5  | DB4              | DB3  | DB2  | DB1            | DB0<br>(LSB) |

|-------------------------|------|------|---------------------------|--------------|----------------------------|------|------|------|------------------|------|------|----------------|--------------|

| 0                       | 1    | 0    | 0                         | Х            | Χ                          | PDD1 | PDD0 | PDC1 | PDC0             | PDB1 | PDB0 | PDA1           | PDA0         |

| Command bits (C3 to C0) |      |      | Address bits (don't care) |              | Power-Down<br>Select DAC D |      |      |      | Power-<br>Select |      |      | -Down<br>DAC A |              |

<sup>&</sup>lt;sup>1</sup> X = don't care.

# **LOAD DAC (HARDWARE LDAC PIN)**

The AD5686/AD5684 DACs have double buffered interfaces consisting of two banks of registers: input registers and DAC registers. The user can write to any combination of the input registers. Updates to the DAC register are controlled by the LDAC pin.

Figure 42. Simplified Diagram of Input Loading Circuitry for a Single DAC

# Instantaneous DAC Updating (LDAC Held Low)

LDAC is held low while data is clocked into the input register using Command 0001. Both the addressed input register and the DAC register are updated on the rising edge of SYNC and the output begins to change (see Table 14).

# Deferred DAC Updating (LDAC Is Pulsed Low)

LDAC is held high while data is clocked into the input register using Command 0001. All DAC outputs are asynchronously updated by taking LDAC low after SYNC has been taken high. The update now occurs on the falling edge of LDAC.

## **LDAC MASK REGISTER**

Command 0101 is reserved for the software  $\overline{LDAC}$  function. Address bits are ignored. Writing to the DAC using Command 0101 loads the 4-bit  $\overline{LDAC}$  register (DB3 to DB0). The default for each channel is 0; that is, the  $\overline{LDAC}$  pin works normally. Setting the bits to 1 forces this DAC channel to ignore transitions on the  $\overline{LDAC}$  pin, regardless of the state of the hardware  $\overline{LDAC}$  pin. This flexibility is useful in applications where the user wishes to select which channels respond to the  $\overline{LDAC}$  pin.

The LDAC register gives the user extra flexibility and control over the hardware LDAC pin (see Table 13). Setting the LDAC bits (DB3 to DB0) to 0 for a DAC channel means that this channel's update is controlled by the hardware LDAC pin.

Table 13. LDAC Overwrite Definition

| Load LDAC                 | Register       |                                                                                 |

|---------------------------|----------------|---------------------------------------------------------------------------------|

| LDAC Bits<br>(DB3 to DB0) | LDAC Pin       | LDAC Operation                                                                  |

| 0                         | 1 or 0         | Determined by the LDAC pin.                                                     |

| 1                         | X <sup>1</sup> | DAC channels are updated and override the LDAC pin. DAC channels see LDAC as 1. |

$<sup>^{1}</sup>$  X = don't care.

Table 14. Write Commands and LDAC Pin Truth Table<sup>1</sup>

| Command | Description                                   | Hardware LDAC Pin State | Input Register<br>Contents | DAC Register Contents                |

|---------|-----------------------------------------------|-------------------------|----------------------------|--------------------------------------|

| 0001    | Write to Input Register n (dependent on LDAC) | V <sub>LOGIC</sub>      | Data update                | No change (no update)                |

|         |                                               | GND <sup>2</sup>        | Data update                | Data update                          |

| 0010    | Update DAC Register n with contents of Input  | V <sub>LOGIC</sub>      | No change                  | Updated with input register contents |

|         | Register n                                    | GND                     | No change                  | Updated with input register contents |

| 0011    | Write to and update DAC Channel n             | V <sub>LOGIC</sub>      | Data update                | Data update                          |

|         |                                               | GND                     | Data update                | Data update                          |

<sup>&</sup>lt;sup>1</sup> A high to low hardware LDAC pin transition always updates the contents of the DAC register with the contents of the input register on channels that are not masked (blocked) by the LDAC mask register.

<sup>&</sup>lt;sup>2</sup> When LDAC is permanently tied low, the LDAC mask bits are ignored.

# HARDWARE RESET (RESET)

RESET is an active low reset that allows the outputs to be cleared to either zero scale or midscale. The clear code value is user selectable via the RESET select pin. It is necessary to keep RESET low for a minimum of 30 ns to complete the operation (see Figure 2). When the RESET signal is returned high, the output remains at the cleared value until a new value is programmed. The outputs cannot be updated with a new value while the RESET pin is low. There is also a software executable reset function that resets the DAC to the power-on reset code. Command 0110 is designated for this software reset function (see Table 8). Any events on LDAC or RESET during power-on reset are ignored.

# **RESET SELECT PIN (RSTSEL)**

The AD5686/AD5684 contain a power-on reset circuit that controls the output voltage during power-up. By connecting the RSTSEL pin low, the output powers up to zero scale. Note that this is outside the linear region of the DAC. By connecting the RSTSEL pin high,  $V_{\text{OUT}}$  powers up to midscale. The output remains powered up at this level until a valid write sequence is made to the DAC.

# APPLICATIONS INFORMATION MICROPROCESSOR INTERFACING

Microprocessor interfacing to the AD5686/AD5684 is via a serial bus that uses a standard protocol that is compatible with DSP processors and microcontrollers. The communications channel requires a 3- or 4-wire interface consisting of a clock signal, a data signal, and a synchronization signal. The devices require a 24-bit data-word with data valid on the rising edge of SYNC.

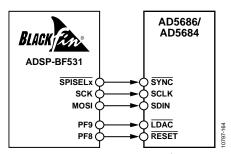

## AD5686/AD5684 TO ADSP-BF531 INTERFACE

The SPI interface of the AD5686/AD5684 is designed to be easily connected to industry-standard DSPs and microcontrollers. Figure 43 shows the AD5686/AD5684 connected to the Analog Devices, Inc., Blackfin\* DSP. The Blackfin has an integrated SPI port that can be connected directly to the SPI pins of the AD5686/AD5684.

Figure 43. ADSP-BF531 Interface

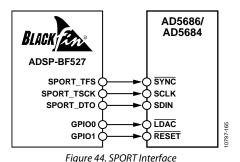

### AD5686/AD5684 TO SPORT INTERFACE

The Analog Devices ADSP-BF527 has one SPORT serial port. Figure 44 shows how one SPORT interface can be used to control the AD5686/AD5684.

**LAYOUT GUIDELINES**

In any circuit where accuracy is important, careful consideration of the power supply and ground return layout helps to ensure the rated performance. The PCB on which the AD5686/AD5684 are mounted should be designed so that the AD5686/AD5684 lie on the analog plane.

The AD5686/AD5684 should have ample supply bypassing of  $10~\mu F$  in parallel with  $0.1~\mu F$  on each supply, located as close to the package as possible, ideally right up against the device. The  $10~\mu F$  capacitors are the tantalum bead type. The  $0.1~\mu F$  capacitor should have low effective series resistance (ESR) and low effective series inductance (ESI), such as the common ceramic types, which provide a low impedance path to ground at high frequencies to handle transient currents due to internal logic switching.

In systems where there are many devices on one board, it is often useful to provide some heat sinking capability to allow the power to dissipate easily.

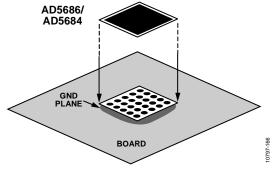

The AD5686/AD5684 LFCSP models have an exposed pad beneath the device. Connect this pad to the GND supply for the part. For optimum performance, use special considerations to design the motherboard and to mount the package. For enhanced thermal, electrical, and board level performance, solder the exposed pad on the bottom of the package to the corresponding thermal land pad on the PCB. Design thermal vias into the PCB land pad area to further improve heat dissipation.

The GND plane on the device can be increased (as shown in Figure 45) to provide a natural heat sinking effect.

Figure 45. Pad Connection to Board

### **GALVANICALLY ISOLATED INTERFACE**

In many process control applications, it is necessary to provide an isolation barrier between the controller and the unit being controlled to protect and isolate the controlling circuitry from any hazardous common-mode voltages that may occur. *i*Coupler® products from Analog Devices provide voltage isolation in excess of 2.5 kV. The serial loading structure of the AD5686/AD5684 makes the part ideal for isolated interfaces because the number of interface lines is kept to a minimum. Figure 46 shows a 4-channel isolated interface to the AD5686/AD5684 using an ADuM1400. For more information, visit http://www.analog.com/icouplers.

<sup>1</sup>ADDITIONAL PINS OMITTED FOR CLARITY.

Figure 46. Isolated Interface

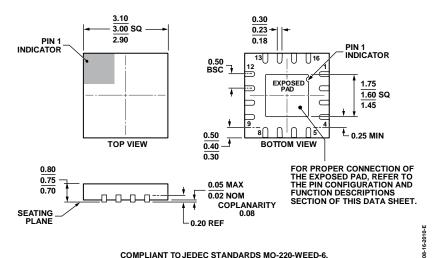

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-220-WEED-6.

Figure 47. 16-Lead Lead Frame Chip Scale Package [LFCSP\_WQ] 3 mm × 3 mm Body, Very Very Thin Quad (CP-16-22) Dimensions shown in millimeters

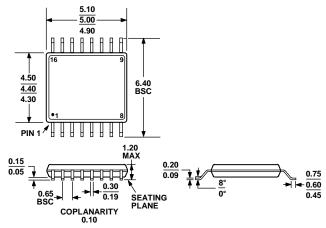

## COMPLIANT TO JEDEC STANDARDS MO-153-AB

Figure 48. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU-16) Dimensions shown in millimeters

# **ORDERING GUIDE**

| Model <sup>1, 2</sup> | Resolution | Temperature Range | Accuracy   | Package<br>Description  | Package<br>Option | Branding |

|-----------------------|------------|-------------------|------------|-------------------------|-------------------|----------|

|                       |            |                   |            | •                       | •                 |          |

| AD5686ACPZ-RL7        | 16 Bits    | −40°C to +105°C   | ±8 LSB INL | 16-Lead LFCSP_WQ        | CP-16-22          | DJH      |

| AD5686BCPZ-RL7        | 16 Bits    | −40°C to +105°C   | ±2 LSB INL | 16-Lead LFCSP_WQ        | CP-16-22          | וום      |

| AD5686ARUZ            | 16 Bits    | −40°C to +105°C   | ±8 LSB INL | 16-Lead TSSOP           | RU-16             |          |

| AD5686ARUZ-RL7        | 16 Bits    | −40°C to +105°C   | ±8 LSB INL | 16-Lead TSSOP           | RU-16             |          |

| AD5686BRUZ            | 16 Bits    | −40°C to +105°C   | ±2 LSB INL | 16-Lead TSSOP           | RU-16             |          |

| AD5686BRUZ-RL7        | 16 Bits    | −40°C to +105°C   | ±2 LSB INL | 16-Lead TSSOP           | RU-16             |          |

| AD5684BCPZ-RL7        | 12 Bits    | −40°C to +105°C   | ±1 LSB INL | 16-Lead LFCSP_WQ        | CP-16-22          | DJP      |

| AD5684ARUZ            | 12 Bits    | −40°C to +105°C   | ±2 LSB INL | 16-Lead TSSOP           | RU-16             |          |

| AD5684ARUZ-RL7        | 12 Bits    | −40°C to +105°C   | ±2 LSB INL | 16-Lead TSSOP           | RU-16             |          |

| AD5684BRUZ            | 12 Bits    | −40°C to +105°C   | ±1 LSB INL | 16-Lead TSSOP           | RU-16             |          |

| AD5684BRUZ-RL7        | 12 Bits    | −40°C to +105°C   | ±1 LSB INL | 16-Lead TSSOP           | RU-16             |          |

| EVAL-AD5686RSDZ       |            |                   |            | 16-Bit Evaluation Board |                   |          |

| EVAL-AD5684RSDZ       |            |                   |            | 12-Bit Evaluation Board |                   |          |

$<sup>^1</sup>$  Z = RoHS Compliant Part.  $^2$  The EVAL-AD5686RSDZ requires the EVAL-SDP-CB1Z support board for operation. The EVAL-AD5684RSDZ requires the EVAL-SDP-CS1Z support board for operation.

**NOTES**