Contents VB6955CM

# **Contents**

| 1 | Ove  | rview .   |                                                        | 9  |

|---|------|-----------|--------------------------------------------------------|----|

|   | 1.1  | VB695     | 55CM use in system with software image processing      | 10 |

|   | 1.2  | Refere    | ence documents                                         | 10 |

| 2 | Devi | ce pino   | ut                                                     | 11 |

| 3 | Fund | ctional c | description                                            | 13 |

|   | 3.1  | Extern    | al clock                                               | 13 |

|   |      | 3.1.1     | Clock input type                                       | 13 |

|   |      | 3.1.2     | PLL and clock input                                    | 13 |

|   | 3.2  | Device    | e operating modes                                      | 14 |

|   |      | 3.2.1     | Power-up procedure                                     | 15 |

|   |      | 3.2.2     | Power-down procedure                                   | 18 |

|   |      | 3.2.3     | Internal power-on reset (POR)                          | 20 |

|   |      | 3.2.4     | Power off                                              | 21 |

|   |      | 3.2.5     | Hardware standby                                       | 21 |

|   |      | 3.2.6     | Software standby                                       | 21 |

|   |      | 3.2.7     | Streaming                                              | 21 |

|   |      | 3.2.8     | Fast standby mode                                      | 22 |

| 4 | Cam  | era con   | trol interface (CCI)                                   | 23 |

|   | 4.1  | Valid re  | egister data types                                     | 23 |

|   | 4.2  | Regist    | er map                                                 | 24 |

|   |      | 4.2.1     | Status registers [0x0000 to 0x001f]                    | 24 |

|   |      | 4.2.2     | Frame format description registers [0x0040 to 0x0049]  | 26 |

|   |      | 4.2.3     | Analogue gain description registers [0x0080 to 0x0093] | 26 |

|   |      | 4.2.4     | Data format description registers [0x00c0 to 0x00c9]   | 27 |

|   |      | 4.2.5     | Setup registers [0x0100 to 0x0137]                     | 28 |

|   |      | 4.2.6     | Integration and gain registers [0x0200 to 0x0215]      | 30 |

|   |      | 4.2.7     | Video timing registers [0x0300 to 0x0387]              | 30 |

|   |      | 4.2.8     | Scaler and digital crop registers [0x0400 to 0x040f]   | 32 |

|   |      | 4.2.9     | Compression setup registers [0x0500 to 0x0501]         | 33 |

|   |      | 4.2.10    | Test pattern registers [0x0600 to 0x0611]              | 33 |

|   |      | 4.2.11    | CSI2 registers [0x808]                                 | 34 |

|   |      |           |                                                        |    |

VB6955CM Contents

|            |      | 4.2.12    | DPHY registers [0x820 to 0x823]                              | 34       |

|------------|------|-----------|--------------------------------------------------------------|----------|

|            |      | 4.2.13    | Binning registers [0x900 to 0x902]                           | 35       |

|            |      | 4.2.14    | Data transfer registers [0x0a00 to 0x0a43]                   | 35       |

|            |      | 4.2.15    | Ideal raw registers [0x0b04 to 0x0b05]                       | 36       |

|            |      | 4.2.16    | Flash registers [0x0c12 to 0x0c2a]                           | 36       |

|            |      | 4.2.17    | Sensor - high level auto focus registers [0x0d80 to 0x0d89]  | 37       |

|            |      | 4.2.18    | Bracketing LUT registers [0x0e00 to 0x0e55]                  | 38       |

|            |      | 4.2.19    | Integration and gain limit registers [0x1000 to 0x1089]      | 40       |

|            |      | 4.2.20    | Video timing limit registers [0x1100 to 0x11c7]              | 41       |

|            |      | 4.2.21    | Scaling limit registers [0x1200 to 0x120f]                   | 45       |

|            |      | 4.2.22    | Compression capability registers [0x1300 to 0x1301]          | 45       |

|            |      | 4.2.23    | Derate capability registers [0x1500 to 0x1502]               | 45       |

|            |      | 4.2.24    | DPHY capability registers [0x1600 to 0x1604]                 | 46       |

|            |      | 4.2.25    | Bitrate limit registers [0x1608 to 0x1617]                   | 46       |

|            |      | 4.2.26    | Binning capability registers [0x1700 to 0x1714]              | 47       |

|            |      | 4.2.27    | Data transfer capability registers [0x1800]                  | 47       |

|            |      | 4.2.28    | Ideal raw capability registers [0x1900 to 0x1907]            | 48       |

|            |      | 4.2.29    | EDOF capability registers [0x1980 to 0x19c5]                 | 48       |

|            |      | 4.2.30    | Timer capability registers [0x1a00 to 0x1a02]                | 48       |

|            |      | 4.2.31    | Mechanical shutter capability registers [0x1b00 to 0x1b04]   | 49       |

|            |      | 4.2.32    | Static autofocus actuator capability registers [0x1b40 to 0x | 1b45] 49 |

|            |      | 4.2.33    | Bracketing LUT capability registers [0x1c00 to 0x1c02]       | 49       |

|            |      | 4.2.34    | Manufacturer specific registers [0x6006 to 0x6008]           | 50       |

| 5          | Vide | o data ii | nterface                                                     | 51       |

|            | 5.1  |           | format                                                       |          |

|            | 0.1  | Tramo     | 10111at                                                      | 02       |

| 6          | Vide | o timing  |                                                              | 55       |

|            | 6.1  | Output    | size                                                         | 55       |

|            |      | 6.1.1     | Analog crop                                                  | 56       |

|            |      | 6.1.2     | Subsampling                                                  | 57       |

|            |      | 6.1.3     | Binning                                                      | 58       |

|            |      | 6.1.4     | Digital crop                                                 | 58       |

|            |      | 6.1.5     | Scaling                                                      | 59       |

|            |      | 6.1.6     | Output crop                                                  | 61       |

|            | 6.2  | Video t   | iming                                                        | 62       |

|            |      | 6.2.1     | PLL block                                                    | 62       |

|            |      |           |                                                              |          |

| <b>577</b> |      |           | DocID028544 Rev 1                                            | 3/101    |

|    |      | 6.2.2     | Framerate                                |    |

|----|------|-----------|------------------------------------------|----|

|    |      | 6.2.3     | Derating                                 |    |

|    | 6.3  | •         | and video size capabilities              |    |

|    | 6.4  | Bayer     | pattern                                  | 66 |

|    | 6.5  | Image     | compression                              | 68 |

|    | 6.6  | Expos     | ure and gain control                     | 68 |

|    |      | 6.6.1     | Analogue gain model                      | 69 |

|    |      | 6.6.2     | Digital gain                             | 70 |

|    |      | 6.6.3     | Integration and gain parameter re-timing | 70 |

| 7  | Elec | trical ch | haracteristics                           | 71 |

|    | 7.1  | Absolu    | ute maximum ratings                      | 71 |

|    | 7.2  | Opera     | ting conditions                          | 72 |

|    | 7.3  | DC ele    | ectrical characteristics                 | 72 |

|    |      | 7.3.1     | Power supply - VDIG, VANA, VBAT          | 72 |

|    |      | 7.3.2     | CCI interface                            | 73 |

|    | 7.4  | AC ele    | ectrical and timing characteristics      | 73 |

|    |      | 7.4.1     | Power supply (peak current) - VDIG, VANA | 73 |

|    |      | 7.4.2     | System clock - EXTCLK                    | 74 |

|    |      | 7.4.3     | EXTCLK - timing characteristics          | 74 |

|    |      | 7.4.4     | CCI interface - timing characteristics   | 74 |

|    |      | 7.4.5     | CSI interface - DATA+, DATA-, CLK+, CLK  | 75 |

| 8  | Opti | cal spe   | cification                               | 76 |

|    | 8.1  | Lens o    | characteristics                          | 76 |

|    | 8.2  | User p    | precaution                               | 76 |

| 9  | Auto | ofocus .  |                                          | 77 |

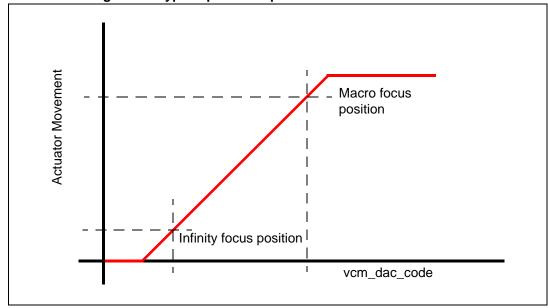

|    | 9.1  | VCM a     | actuator                                 | 77 |

|    | 9.2  | VCM o     | driver/DAC                               | 78 |

|    |      | 9.2.1     | VCM driver control                       | 78 |

|    |      | 9.2.2     | VCM driver register access               | 78 |

|    | 9.3  | Examp     | oles                                     | 79 |

|    | 9.4  | •         | ication                                  |    |

| 10 | Non  | -volatile | e memory (NVM)                           | 83 |

|    |      |           |                                          |    |

| 11 | Defe      | ct categ | gorization                                | 84  |

|----|-----------|----------|-------------------------------------------|-----|

|    | 11.1      | Pixel d  | lefects                                   | 84  |

|    |           | 11.1.1   | Overview                                  | 84  |

|    |           | 11.1.2   | Defect detection                          | 84  |

|    |           | 11.1.3   | Defect categorisation: Single pixels      | 85  |

|    |           | 11.1.4   | Defect categorisation: Couplets           | 85  |

|    |           | 11.1.5   | Defect categorisation: Clusters and blobs | 85  |

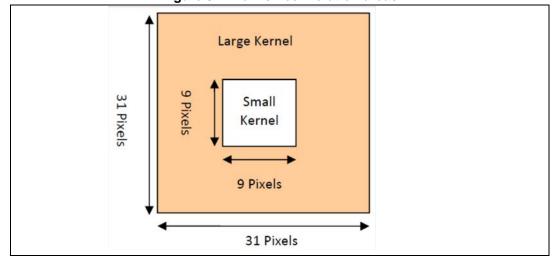

|    | 11.2      | Blemis   | shes                                      | 86  |

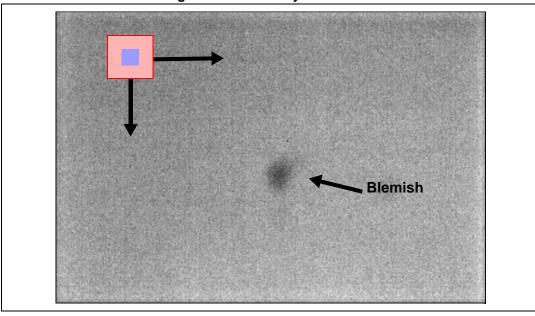

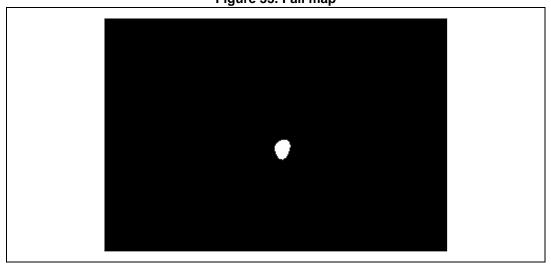

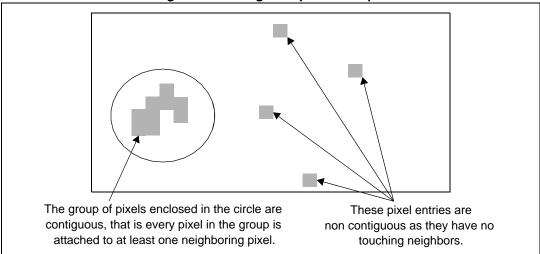

|    |           | 11.2.1   | Blemish overview                          | 86  |

|    |           | 11.2.2   | Blemish algorithm                         | 86  |

| 12 | On-c      | hip ima  | age optimization                          | 89  |

|    | 12.1      | Марре    | ed couplet correction (Bruce filter)      | 89  |

| 13 | Mech      | nanical  |                                           | 90  |

| 14 | Appl      | ication  |                                           | 96  |

|    | 14.1      | Schem    | natic                                     | 96  |

| 15 | Acro      | nyms a   | and abbreviations                         | 97  |

| 16 | ECOPACK®9 |          |                                           | 99  |

| 17 | Revi      | sion his | story                                     | 100 |

List of tables VB6955CM

# List of tables

| Table 1.  |                                                                                 | 1  |

|-----------|---------------------------------------------------------------------------------|----|

| Table 2.  | Technical specification                                                         | 9  |

| Table 3.  | Reference documents                                                             | 10 |

| Table 4.  | Pin description                                                                 | 11 |

| Table 5.  | System input clock frequency range                                              | 13 |

| Table 6.  | Power-up sequence timing constraints                                            | 15 |

| Table 7.  | Power-down sequence timing constraints for CSI2 communications                  | 18 |

| Table 8.  | POR cell characteristics                                                        | 21 |

| Table 9.  | Valid register data types                                                       | 23 |

| Table 10. | Status registers [0x0000 to 0x001f]                                             | 24 |

| Table 11. | Frame format description registers [0x0040 to 0x0049]                           | 26 |

| Table 12. | Analogue gain description [0x0080 to 0x0093]                                    | 26 |

| Table 13. | Data format description registers [0x00c0 to 0x00c9]                            | 27 |

| Table 14. | Setup registers [0x0100 to 0x0137]                                              | 28 |

| Table 15. | Integration and gain registers [0x0200 to 0x0215]                               | 30 |

| Table 16. | Video timing registers [0x0300 to 0x0387]                                       | 30 |

| Table 17. | Scaler and digital crop registers [0x0400 to 0x040f]                            | 32 |

| Table 18. | Compression setup registers [0x0500 to 0x0501]                                  | 33 |

| Table 19. | Test pattern registers [0x0600 to 0x0611]                                       | 33 |

| Table 20. | CSI2 registers [0x808]                                                          | 34 |

| Table 21. | DPHY registers [0x820 to 0x823]                                                 | 34 |

| Table 22. | Binning registers [0x900 to 0x902]                                              | 35 |

| Table 23. | Data transfer registers [0x0a00 to 0x0a43]                                      | 35 |

| Table 24. | Ideal raw registers [0x0b04 to 0x0b05]                                          | 36 |

| Table 25. | Flash registers [0x0c12 to 0x0c2a]                                              |    |

| Table 26. | Sensor - high level auto focus registers [0x0d80 to 0x0d89]                     | 37 |

| Table 27. | Bracketing LUT registers [0x0e00 to 0x0e55]                                     | 38 |

| Table 28. | Integration and gain limit registers [0x1000 to 0x1089]                         | 40 |

| Table 29. | Video timing limit registers [0x1100 to 0x11c7]                                 |    |

| Table 30. | Scaling limit registers [0x1200 to 0x120f]                                      | 45 |

| Table 31. | Compression capability registers [0x1300 to 0x1301]                             | 45 |

| Table 32. | Derate capability registers [0x1500 to 0x1502]                                  |    |

| Table 33. | DPHY capability registers [0x1600 to 0x1604]                                    | 46 |

| Table 34. | Bitrate limit registers [0x1608 to 0x1617]                                      |    |

| Table 35. | Binning capability registers [0x1700 to 0x1714]                                 |    |

| Table 36. | Data transfer capability registers [0x1800]                                     |    |

| Table 37. | Ideal raw capability registers [0x1900 to 0x1907]                               |    |

| Table 38. | EDOF capability registers [0x1980 to 0x19c5]                                    | 48 |

| Table 39. | Timer capability registers [0x1a00 to 0x1a02]                                   |    |

| Table 40. | Mechanical shutter capability registers [0x1b00 to 0x1b04]                      |    |

| Table 41. | Static autofocus actuator capability registers [0x1b40 to 0x1b45]               |    |

| Table 42. | Bracketing LUT capability registers [0x1c00 to 0x1c02]                          | 49 |

| Table 43. | Manufacturer specific registers [0x6006 to 0x6008]                              |    |

| Table 44. | External clock frequency examples - 5.0 Mpixel Raw10 30 fps (CSI-2 dual lane)   |    |

| Table 45. | External clock frequency examples - 5.0 Mpixel Raw10 15 fps (CSI-2 single lane) |    |

| Table 46. | Examples of video mode capabilities                                             |    |

| Table 47. | Analogue gain control                                                           |    |

| Table 48. | Absolute maximum ratings                                                        | 71 |

|           |                                                                                 |    |

**577**

VB6955CM List of tables

| Table 49. | Operating conditions                                       | . 72 |

|-----------|------------------------------------------------------------|------|

| Table 50. | Power supply - VDIG, VANA, VBAT                            | . 72 |

| Table 51. | CCI interface                                              | . 73 |

| Table 52. | In-rush current - VDIG, VANA (CSI-2)                       | . 73 |

| Table 53. | System clock                                               | . 74 |

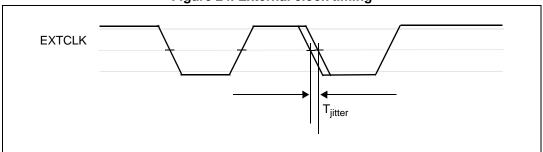

| Table 54. | External clock timing characteristics                      | . 74 |

| Table 55. | CCI interface timing characteristics                       | . 74 |

| Table 56. | CSI interface - DATA+, DATA-, CLK+, CLK- characteristics   | . 75 |

| Table 57. | Lens design characteristics for first source lens supplier | . 76 |

| Table 58. | Autofocus specification - Type M                           | . 79 |

| Table 59. | Autofocus specification - Type L                           | . 81 |

| Table 60. | NVM register summary                                       | . 83 |

| Table 61. | Pixel defect specification                                 | . 84 |

| Table 62. | Image settings                                             |      |

| Table 63. | Acronyms and abbreviations                                 |      |

| Table 64. | Document revision history                                  |      |

List of figures VB6955CM

# List of figures

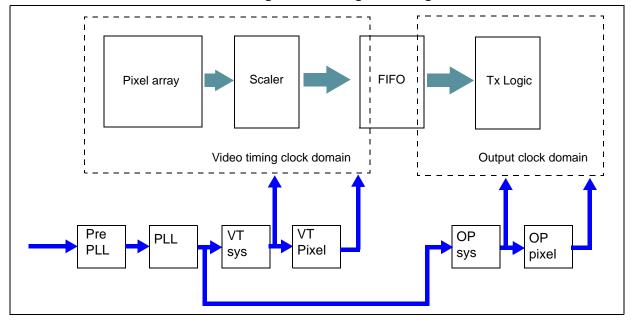

| Figure 1.  | VB6955CM in system with software image processing            |      |

|------------|--------------------------------------------------------------|------|

| Figure 2.  | VB6955CM module pinout (viewed from bottom of camera module) | . 11 |

| Figure 3.  | Clock input types                                            |      |

| Figure 4.  | System state diagram                                         |      |

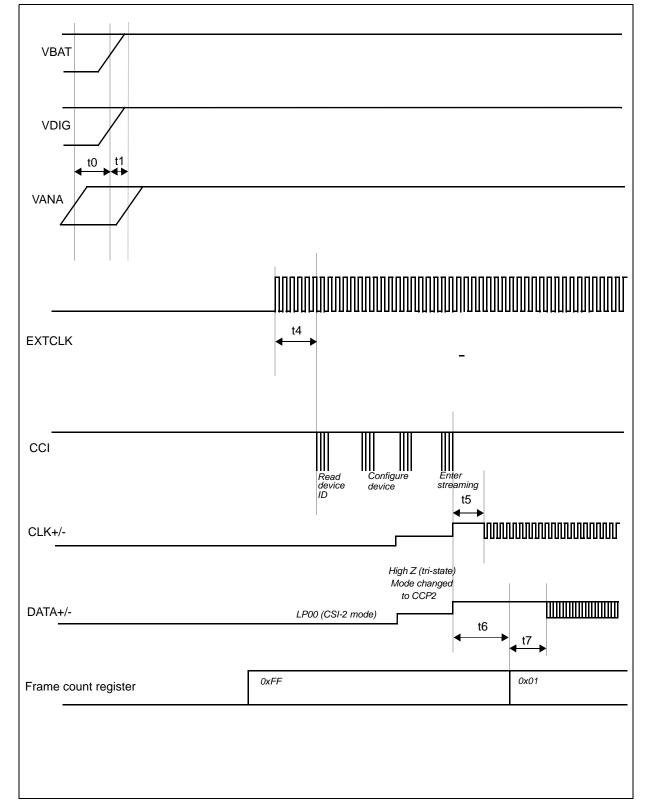

| Figure 5.  | VB6955CM power-up sequence for CCP2 mode                     | . 16 |

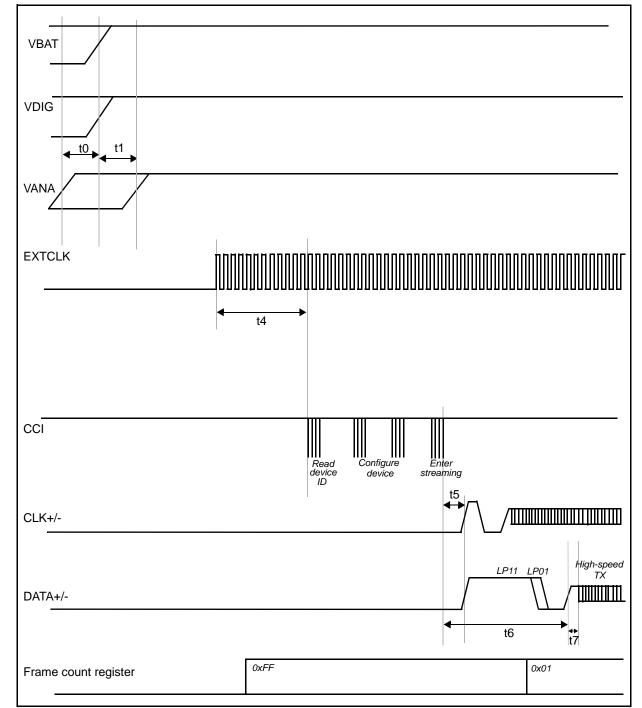

| Figure 6.  | VB6955CM power-up sequence for CSI-2 mode                    | . 17 |

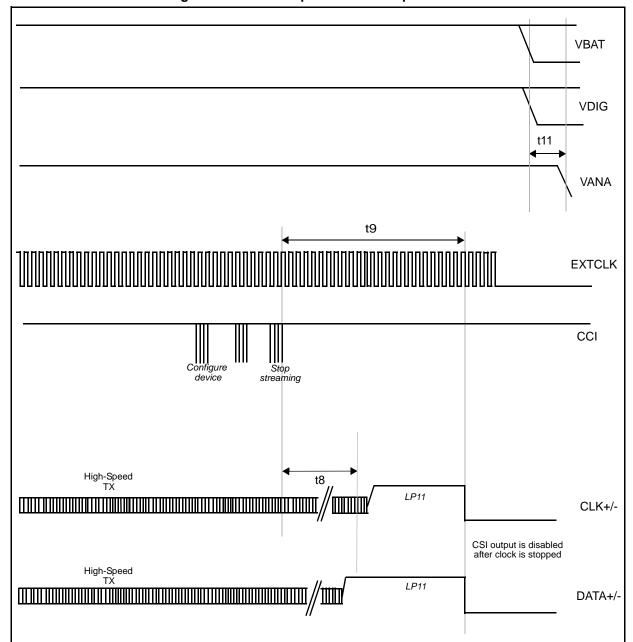

| Figure 7.  | VB6955CM power-down sequence for CSI-2 mode                  | . 19 |

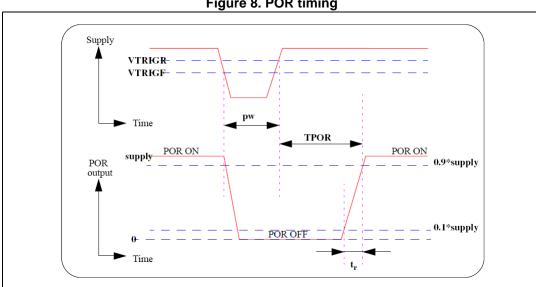

| Figure 8.  | POR timing                                                   | . 20 |

| Figure 9.  | VB6955CM CCP2 frame format                                   | . 52 |

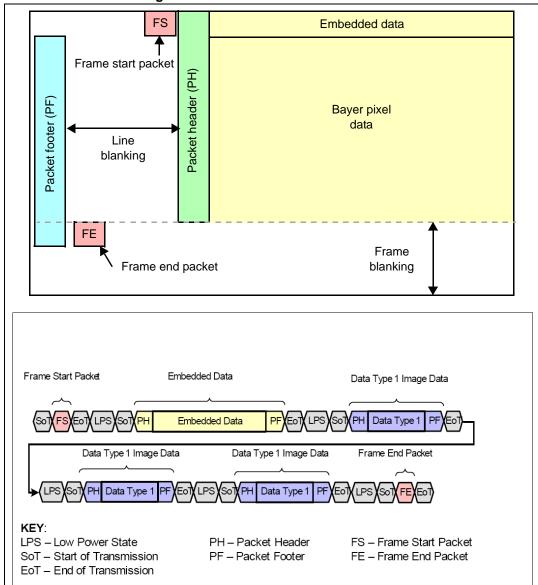

| Figure 10. | VB6955CM CSI-2 frame format                                  | . 53 |

| Figure 11. | Data flow                                                    | . 55 |

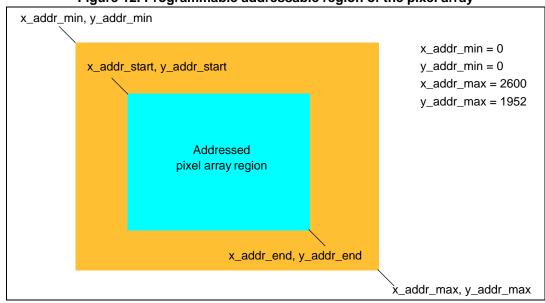

| Figure 12. | Programmable addressable region of the pixel array           | . 56 |

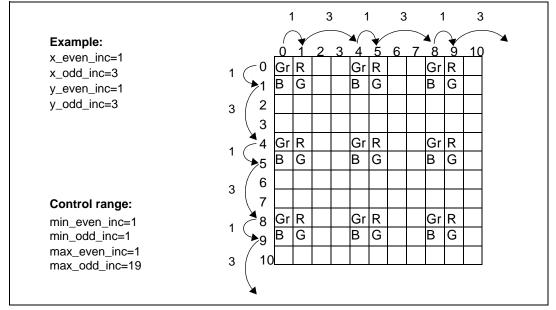

| Figure 13. | Subsample readout example                                    | . 57 |

| Figure 14. | Digital crop                                                 | . 58 |

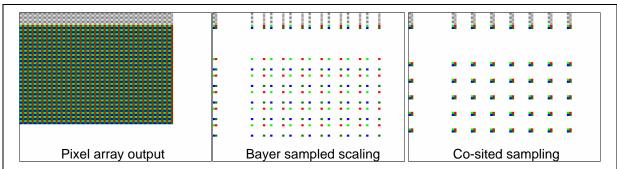

| Figure 15. | Scaling modes                                                | . 59 |

| Figure 16. | Scaler quality                                               | . 60 |

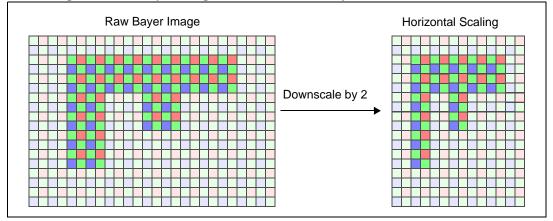

| Figure 17. | Example image horizontal scaled by a downscale factor of 2   | . 60 |

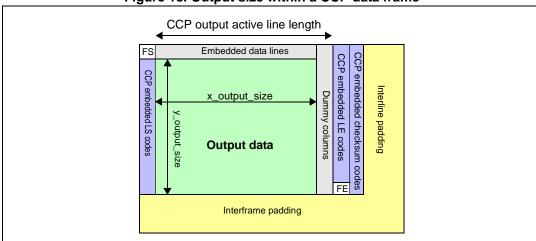

| Figure 18. | Output size within a CCP data frame                          | . 61 |

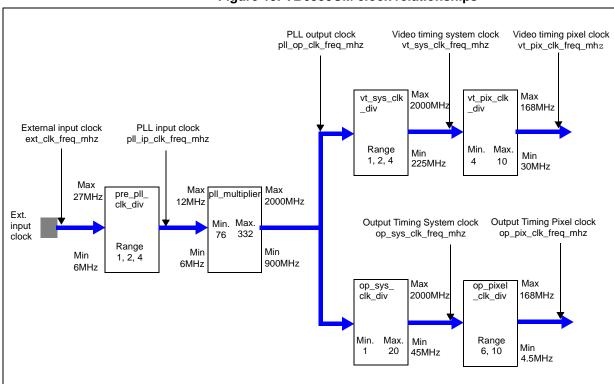

| Figure 19. | VB6955CM clock relationships                                 | . 62 |

| Figure 20. | Timing block diagram                                         | . 64 |

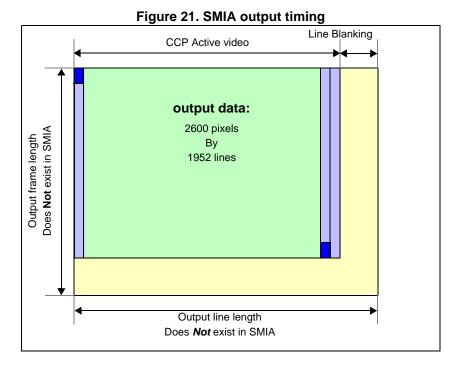

| Figure 21. | SMIA output timing                                           | . 65 |

| Figure 22. | Bayer pattern                                                | . 67 |

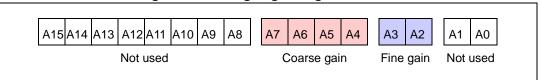

| Figure 23. | Analogue gain register format                                | . 69 |

| Figure 24. | External clock timing                                        | . 74 |

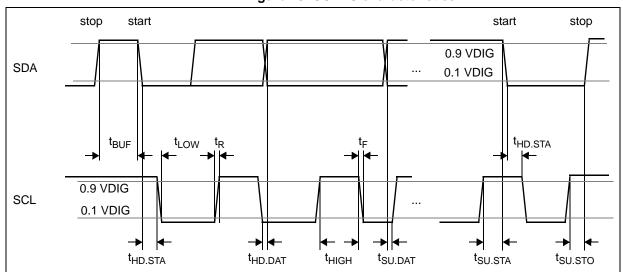

| Figure 25. | CCI AC characteristics                                       | . 75 |

| Figure 26. | Host and VB6955CM module system overview                     | . 77 |

| Figure 27. | Typical plot of displacement versus DAC control              | . 78 |

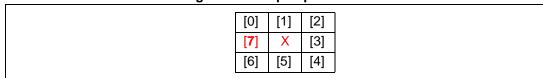

| Figure 28. | Pixel numbering notation                                     | . 85 |

| Figure 29. | Single pixel fault                                           | . 85 |

| Figure 30. | Couplet pixel fault                                          | . 85 |

| Figure 31. | Blemish convolution areas                                    | . 86 |

| Figure 32. | Scan array for blemish                                       | . 87 |

| Figure 33. | Fail map                                                     | . 87 |

| Figure 34. | Contiguous pixel example                                     | . 88 |

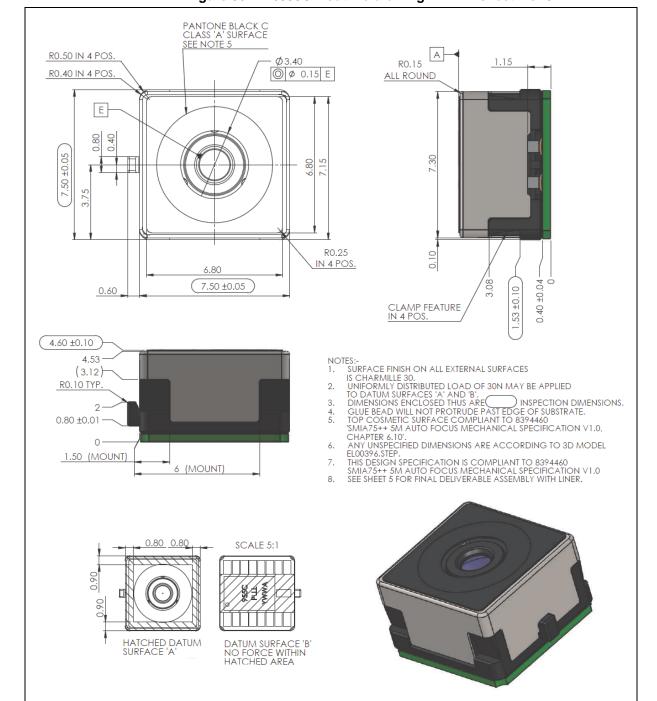

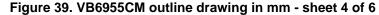

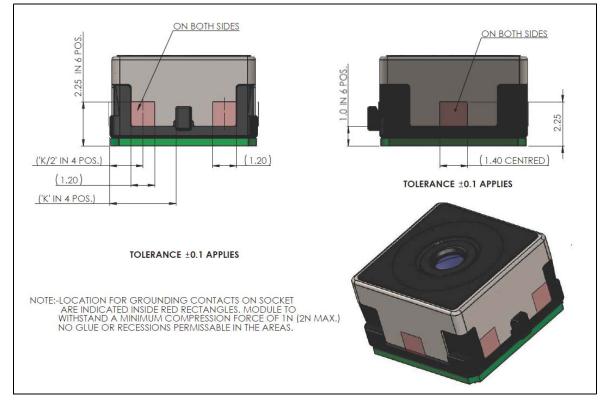

| Figure 35. | VB6955CM exploded view                                       | . 90 |

| Figure 36. | VB6955CM outline drawing in mm - sheet 1 of 6                | . 91 |

| Figure 37. | VB6955CM outline drawing in mm - sheet 2 of 6                | . 92 |

| Figure 38. | VB6955CM outline drawing in mm - sheet 3 of 6                | . 93 |

| Figure 39. | VB6955CM outline drawing in mm - sheet 4 of 6                |      |

| Figure 40. | VB6955CM outline drawing in mm - sheet 5 of 6                | . 94 |

| Figure 41. | VB6955CM outline drawing in mm - sheet 6 of 6                |      |

| Figure 42  | Mobile camera application                                    | 96   |

VB6955CM Overview

### 1 Overview

The VB6955CM image sensor produces raw digital video data at up to 30 frames per second. The sensor supports horizontal flip and vertical mirroring. Output frequency can be derated as defined in the specification for power saving. Higher frame rate can be achieved through analog binning and subsampling modes.

The image data is digitized using an internal 10-bit column ADC. The resulting pixel data is output together with checksums and embedded codes for synchronization. The interface conforms to MIPI CSI-2 interface standards.

The sensor is fully configurable through a CCI serial interface. Both the CSI-2 and CCI interfaces are specified in a separate document: MIPI alliance standard for camera serial interface 2 (CSI-2).

**Table 2. Technical specification**

| Feature                          | Detail                                                            |

|----------------------------------|-------------------------------------------------------------------|

| Pixel resolution                 | 2600x 1952 with border pixels                                     |

| Sensor technology                | ST IMG140 FSI Gen2 based CMOS imaging process                     |

| Pixel size                       | 1.4 μm x 1.4 μm                                                   |

| Analog gain                      | + 24 dB                                                           |

| Digital gain                     | + 6 dB                                                            |

| Dynamic range                    | 60 dB                                                             |

| Signal to noise                  | 36 dB (@ 100 lux)                                                 |

| Supply voltages                  | Analog: 2.6 to 2.9V<br>Digital: 1.7 to 1.9 V<br>VBAT: 2.5 to 4.8V |

| Typical power consumption 30 fps | 130 mA (typical)                                                  |

| Operating temperature            | -30°C to +70°C                                                    |

| Storage temperature              | -40°C to +85°C                                                    |

| Average dark current (60C)       | 25 e/s                                                            |

| Shading (60C)                    | 12 e/s                                                            |

Overview VB6955CM

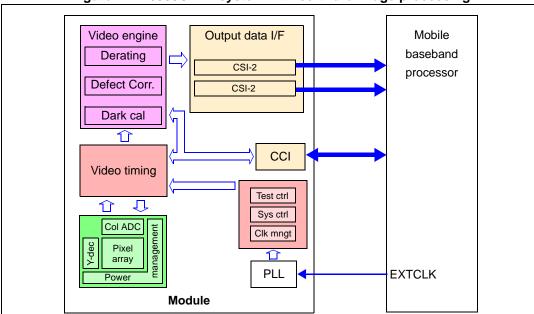

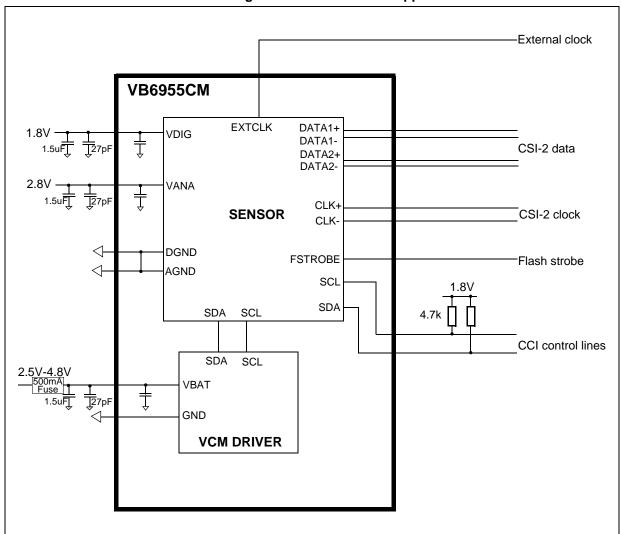

# 1.1 VB6955CM use in system with software image processing

The VB6955CM image sensor can be directly connected to a baseband or multimedia processor. The image processing is done in software or hardware within the baseband processor.

Figure 1. VB6955CM in system with software image processing

#### 1.2 Reference documents

**Table 3. Reference documents**

| Title                                                             | Date       |

|-------------------------------------------------------------------|------------|

| MIPI Alliance Standard for Camera Serial Interface 2 (CSI-2) v1.0 | 29/11/2005 |

| MIPI Alliance D-PHY Specification (v1.00.00)                      | 14/05/2009 |

**\7/**

VB6955CM Device pinout

# 2 Device pinout

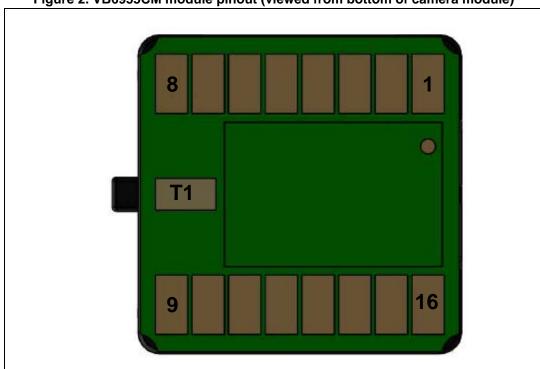

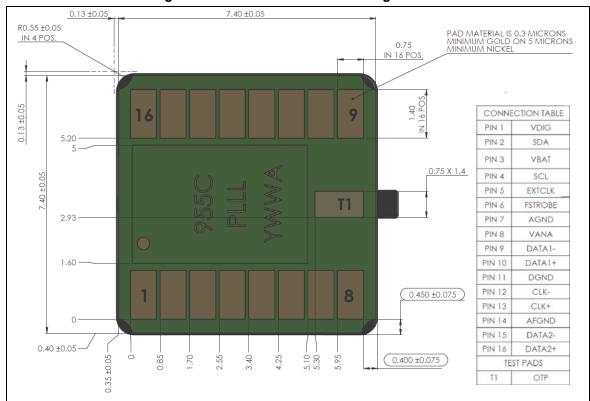

*Figure 2* shows the position of the pins on the module and *Table 4* provides the signal descriptions.

Figure 2. VB6955CM module pinout (viewed from bottom of camera module)

Table 4. Pin description

| Pad number     | Pad name       | Description                |  |  |  |

|----------------|----------------|----------------------------|--|--|--|

| Power supplies | Power supplies |                            |  |  |  |

| 3              | VBAT           | VCM power                  |  |  |  |

| 7, 11          | DGND, AGND     | Digital and analog ground  |  |  |  |

| 8              | VANA           | Analog power               |  |  |  |

| 14             | VCM_GND        | VCM ground                 |  |  |  |

| 1              | VDIG           | Digital power              |  |  |  |

| System         |                |                            |  |  |  |

| 6              | FSTROBE        | Flash strobe               |  |  |  |

| 5              | EXTCLK         | System clock input         |  |  |  |

| Control        |                |                            |  |  |  |

| 4              | SCL            | Serial communication clock |  |  |  |

| 2              | SDA            | Serial communication data  |  |  |  |

DocID028544 Rev 1

11/101

Device pinout VB6955CM

Table 4. Pin description (continued)

| Pad number | Pad name                          | Description                   |  |  |

|------------|-----------------------------------|-------------------------------|--|--|

| Data       |                                   |                               |  |  |

| 12         | CLK- <sup>(1)</sup>               | Output qualifying clock       |  |  |

| 13         | CLK+ <sup>(1)</sup>               | Output qualifying clock       |  |  |

| 9          | DATA1- <sup>(1)</sup>             | Serial output data            |  |  |

| 10         | DATA1+ <sup>(1)</sup>             | Serial output data            |  |  |

| 15         | DATA2- <sup>(1)</sup> / CCP DATA+ | Serial output data            |  |  |

| 16         | DATA2+ <sup>(1)</sup> / CCP DATA- | Serial output data            |  |  |

| ST test    |                                   |                               |  |  |

| T1         | ST test pin                       | Do not connect <sup>(2)</sup> |  |  |

<sup>1.</sup> By default, the polarity of the CSI-2 data lanes and clock lanes are swapped. It is necessary to swap them by writing 0x02 to the registers 0x6006, 0x6007 and 0x6008. It is not possible to swap the CCP data lanes.

**577**

<sup>2.</sup> Test pin is not floating.

# 3 Functional description

#### 3.1 External clock

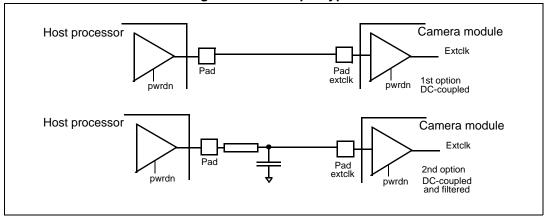

#### 3.1.1 Clock input type

The external clock provided by the host to the VB6955CM must be a DC coupled square wave and may also be RC-filtered.

Figure 3. Clock input types

### 3.1.2 PLL and clock input

The VB6955CM has an embedded PLL block. This block generates all necessary internal clocks from an input range defined in *Table 5*.

Table 5. System input clock frequency range

| Minimum (MHz) | Maximum (MHz) |

|---------------|---------------|

| 6             | 27            |

The value of the external clock frequency must be written to the register 0x0136 (extclk\_frequency\_mhz).

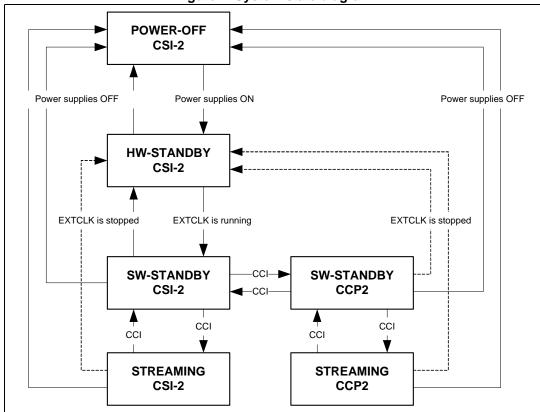

# 3.2 Device operating modes

The mode changes in VB6955CM are shown in *Figure 4*. Further details are provided in Section 3.2.1 to Section 3.2.8.

Figure 4. System state diagram

#### 3.2.1 Power-up procedure

To start the sensor, VDIG, VANA should be set high and EXTCLK started. These can be powered up in any order and have no time constraints. After all three signals are working, the software standby state is reached, the OTP data is read internally<sup>(b)</sup> and CCI activity can begin.

On power-up the on-chip power-on reset cell ensures that the CCI register values are initialized correctly to their default values.

The power-up sequence timing constraints are shown in *Table 6*.

Table 6. Power-up sequence timing constraints

| Symbol | Parameter                                                                               | Minimum                              | Maximum | Units |

|--------|-----------------------------------------------------------------------------------------|--------------------------------------|---------|-------|

| tO     | VANA rising – VDIG rising                                                               | VBAT, VANA and                       | ,       | ns    |

| t1     | VDIG rising – VANA rising                                                               | any order. The ri<br>can vary from 0 |         | ms    |

| t4     | EXTCLK – first CCI transaction with gated clock                                         | 5                                    | -       | ms    |

| t5     | PLL start up/lock time                                                                  | -                                    | 1       | ms    |

| t6     | Entering streaming mode – First frame start sequence (fixed part)                       | -                                    | 10      | ms    |

| t7     | Entering streaming mode – First frame start sequence (variable part) = Integration time | fine_integration_<br>time_min        | -       | ms    |

b. The OTP is read once coming out from hardware standby and VANA powers the OTP.

DocID028544 Rev 1 15/101

Figure 5. VB6955CM power-up sequence for CCP2 mode

Figure 6. VB6955CM power-up sequence for CSI-2 mode

#### 3.2.2 Power-down procedure

The power-down sequence timing constraints are shown in *Table 7*.

Table 7. Power-down sequence timing constraints for CSI2 communications

| Symbol | Parameter                                                                                  | Minimum                                                | Maximum          | Units        |

|--------|--------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|--------------|

| t8     | Last CCI transaction to MIPI frame end <sup>(1)</sup>                                      | -                                                      | 1 frame          |              |

| t9     | Minimum EXTCLK cycles required after last CCI transaction or MIPI frame end <sup>(2)</sup> | 512                                                    | -                | clock cycles |

| t11    | VBAT, VANA, VDIG falling                                                                   | VBAT, VANA and<br>any order, the fa<br>can vary from 0 | lling separation |              |

The whole power-down sequence is triggered by the CCI power-down request, however the power-down sequence only starts after the end of the frame when all active data is consumed on CSI-2 DN/DP pins. Once this is done, the CSI-2 DN/DP signals enter LP11 and the system enters software standby. The CSI-2 clock enters LP11 with a delay of 5 us (corresponding to TcIk\_post + TcIk\_trail) compared to DN/DP pins.

<sup>2.</sup> After the last frame completion, the gated clock needs to be kept for at least 512 cycles so the system can enter LP11 Low Power mode. After the system enters LP11 mode, you can keep or stop the EXTCLK.

Figure 7. VB6955CM power-down sequence for CSI-2 mode

#### 3.2.3 Internal power-on reset (POR)

The VB6955CM internally performs a power-on reset (POR) when the 1V2 VDD digital supply rises through the trigger level, Vtrig rising. Similarly, if the 1V2 VDD digital power supply falls through the trigger level, Vtrig falling, then the power-on reset also triggers.

#### **Definitions**

Rise threshold voltage (VTRIGR) This is the supply voltage level that is recognized by the

> POR as voltage "HIGH". Only after the supply reaches this level does the output of POR change to high level if

it is off, after a specified amount of delay.

This is the supply voltage level that is recognized by the Fall threshold voltage (VTRIGF)

POR as voltage "LOW". Only after the supply reaches this level does the output of POR change to low

(ground) level if it is on.

Burst width (pw) Burst is the negative pulse riding the supply signal. The

> burst width is measured as the amount of duration for which the supply signal dropped beyond the threshold

levels.

Delay duration (TPOR) Delay duration is defined as the time duration for which

POR stays off before re-powering. Each reset of POR imparts a specified delay duration before POR re-

powers.

Figure 8. POR timing

Table 8. POR cell characteristics

| Symbol      | Constraint                 | Minimum | Typical | Maximum | Units |

|-------------|----------------------------|---------|---------|---------|-------|

| VTRIGR      | POR rise voltage detection |         |         | 0.95    | V     |

| VTRIGF      | POR fall voltage detection | 0.4     |         |         | V     |

| Tburst (pw) | Burst filter               |         | 2       | 8       | μs    |

| Tpor        | Delay duration             |         | 20      | 45      | μs    |

#### 3.2.4 Power off

The power off state is defined as either or both of the digital and analog supplies not present.

#### 3.2.5 Hardware standby

This is the lowest power consumption mode. CCI communications are not supported in this mode. The PLL and the video blocks are powered down. This state is entered by stopping the external clock. All registers are returned to their default values

#### 3.2.6 Software standby

Software standby mode preserves the contents of the CCI register map. CCI communications are supported in this mode. The software standby mode is selected using a serial interface command. If this state is entered from hardware standby, the data pads remain at LP-00. If this state is entered from streaming then the data pads go to LP-11 at the end of the current frame. The internal video timing is reset to the start of a video frame in preparation for the enabling of active video. The values of the serial interface registers such as exposure and gain are preserved. The system clock must remain active when communicating with the sensor.

This state is entered by releasing the device from hard reset by writing 0x00 to the mode control register (0x0100) or commanding a soft reset by writing 0x01 to the software reset register (0x0103).

Note: After a soft reset, all registers are returned to their default values.

#### 3.2.7 Streaming

The VB6955CM streams live video. This mode is entered by writing 0x01 to the mode control register (0x0100).

#### 3.2.8 Fast standby mode

The fast software standby mode can be controlled using register 0x0106. By default it is disabled.

If this mode is disabled (that is, standard mode is enabled) and the software standby command is issued while streaming, the transmission of the current frame completes before the VB6955CM enters software standby.

If fast software standby mode is enabled, there are three possibilities for where the VB6955CM may be in the frame that is being read out when the command to go to software standby is received:

- command received during frame blanking

There is no difference in this situation if fast standby mode is enabled or disabled. The VB6955CM immediately enters software standby.

- · command received during the active line

- In CCP2 mode, the VB6955CM outputs the current line including the line end code and then terminates the frame by transmitting a line start code and a frame end code. The VB6955CM then immediately enters software standby mode.

- In CSI-2 mode, the VB6955CM outputs the current packet and terminates the frame with a frame end packet. The VB6955CM then immediately enters software standby mode.

- command received during the line blanking

- In CCP2 mode, the VB6955CM terminates the frame by transmitting a line start code and a frame end code. The VB6955CM then immediately enters software standby mode.

In CSI-2 mode, as the VB6955CM is already in an LP idle state, the VB6955CM immediately enters software standby mode.

57

# 4 Camera control interface (CCI)

This chapter specifies the camera control interface (CCI). The I<sup>2</sup>C-type interface uses 1.8 V I/O with two signals: serial data line (SDA) and serial clock line (SCL). CCI is used for control data transfer. Clock signal (SCL) generation is performed by the master device (the camera module is a slave device). The master device initiates data transfer. The CCI bus on the camera module has a maximum speed of 400 Kbits/s and has a software switchable device address. The default device address is 0x20.

Any internal register that can be written to, can also be read from. There are also read only registers that contain device status information, for example, design revision details. A read instruction from an unused register location returns the value 0x00. A read instruction from a reserved address may return any value. A write instruction to a reserved or unused register location is illegal and the effect of such a write is undefined. It is the responsibility of the host system to only write to register locations which have been defined.

#### 4.1 Valid register data types

The contents of the registers can represent a number of different data types (see *Table 9*). The register map uses this coding to help with the interpretation of the contents of each register.

Data type Name Range Description 8UI 0 to 255 8-bit unsigned integer 8SI 8-bit signed integer -128 to 127 Two's complement notation **16UI** 16-bit unsigned integer 0 to 65535 16SI 16-bit signed integer -32768 to 32767 Two's complement notation 08.08 fixed point number. 8 integer **16UR** 16-bit unsigned iReal 0 to 255.99609375 bits (MS Byte), 8 fractional bits (LS Byte) Two's complement notation, 16SR 16-bit signed iReal -128 to 127.9960375 8 fractional bits 16.16 fixed point number. 32UR 32-bit unsigned iReal 0 to 65535.99998474 16 integer bits (MS 2 Bytes), 16 fractional bits (LS 2 Bytes) 32-bit IEEE floating-As per IEEE 754. 1 sign bit, 32SF As per IEEE 754 point number 8 exponent bits, 23 fractional bits This indicates that the value is 8C or 16C 8-bit or 16-bit coded decoded to select one of several functions or modes. Each bit represents a specific 8B or 16B 8 or 16 bits -b function or mode.

Table 9. Valid register data types

# 4.2 Register map

The registers default values are expressed as hexadecimal numbers.

## 4.2.1 Status registers [0x0000 to 0x001f]

Table 10. Status registers [0x0000 to 0x001f]

| Index | Byte  | Register name         | Data<br>type | Default | Туре | Comment                                                                                                                                                                                                       |

|-------|-------|-----------------------|--------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | Hi    |                       |              | 07      |      | 1955                                                                                                                                                                                                          |

| 1     | LO    | module_model_id       | 16UI         | a3      | RO   | Camera model identification number.  Default values depend on NVM content.                                                                                                                                    |

| 2     |       | revision_number_major | 8UI          | 00      | RO   | Revision identifier of the camera for DCC change. Default value depends on NVM content.                                                                                                                       |

| 3     |       | manufacturer_id       | 8UI          | 01      | RO   | Module manufacturer number. Default value depends on NVM content.                                                                                                                                             |

| 4     |       | smia_version          | 8UI          | 0a      | RO   | SMIA version that sensor complies with 10 - Version 1.0                                                                                                                                                       |

| 5     |       | frame_count           | 8UI          | ff      | RW   | Frame count register. Increments from 1 to 254 when streaming. Reports 255 when idle.                                                                                                                         |

| 6     |       | pixel_order           | 8UI          | 00      | RO   | Color pixel readout order. Changes with mirror and flip (register 0x0101). 0x00 - GR/BG normal. 0x01 - RG/GB horizontal mirror. 0x02 - BG/GR vertical flip. 0x03 - GB/RG vertical flip and horizontal mirror. |

| 8     | HI    | data pedestal         | 16UI         | 00      | RO   | Offset applied to the video data.                                                                                                                                                                             |

| 9     | LO    | data_pedestal         | 1001         | 40      | NO   | Onset applied to the video data.                                                                                                                                                                              |

| С     |       | pixel_depth           | 8UI          | 0a      | RO   | Pixel depth resolution of the sensor.                                                                                                                                                                         |

| 10    |       | revision_number_minor | 8UI          | 00      | RO   | Revision identifier of the camera for minor changes. Default value depends on NVM content.                                                                                                                    |

| 11    |       | additional_spec_ver   | 8UI          | 08      | RO   | Additional specification identifier.                                                                                                                                                                          |

| 12    | [3:0] | module_date_year      | 8UI          | 00      | RO   | Last digit of manufacturing year. Default value depends on NVM content.                                                                                                                                       |

Table 10. Status registers [0x0000 to 0x001f] (continued)

| Index | Byte  | Register name               | Data<br>type | Default | Туре | Comment                                                                                                                                                                           |

|-------|-------|-----------------------------|--------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13    | [3:0] | module_date_month           | 8UI          | 00      | RO   | Manufacturing month. Default value depends on NVM content.                                                                                                                        |

| 14    | [4:0] | module_date_day             | 8UI          | 00      | RO   | Manufacturing day. Default value depends on NVM content.                                                                                                                          |

| 15    | [2:0] | module_date_phase           | 8UI          | 01      | RO   | Manufacturing phase identification.  0 = TS (Test Sample)  1 = ES (Engineering Sample)  2 = CS (Customer Sample)  3 = MP (Mass Production)  Default value depends on NVM content. |

| 16    |       |                             |              | 03      |      | Silicon identification number.                                                                                                                                                    |

| 17    |       | sensor_model_id             | 16UI         | bb      | RO   | This may not be the same as the module identification number, for example, in the case where the same silicon is used in two different modules.                                   |

| 18    | [3:0] | sensor_nvm_revision_id      | 8UI          | 00      | RO   | Silicon NVM revision number. Default value depends on NVM content.                                                                                                                |

|       | [7:4] | sensor_mask_set_revision_id |              | 01      | RO   | Silicon mask revision code.                                                                                                                                                       |

| 19    |       | sensor_manufacturer_id      | 8UI          | 01      | RO   | Silicon manufacturer number -<br>ST Microelectronics.                                                                                                                             |

| 1a    |       | sensor_firmware_version     | 8UI          | 11      | RO   | Silicon firmware version with format "[7:4].[3:0]", for example 0x11 = "1.1".                                                                                                     |

| 1c    | НІ    |                             |              | 00      |      | Sequential number starting at 0 and                                                                                                                                               |

| 1d    | 3rd   | - serial_number             | 32UI         | 00      | RO   | incrementing by 1. Specification identifier.                                                                                                                                      |

| 1e    | 2nd   |                             | 5201         | 00      |      | Default value depends on NVM                                                                                                                                                      |

| 1f    | LO    |                             |              | 00      |      | content.                                                                                                                                                                          |

#### 4.2.2 Frame format description registers [0x0040 to 0x0049]

For a full description of the frame format description refer to Section 5.1.

Table 11. Frame format description registers [0x0040 to 0x0049]

| Index | Byte | Register name                  | Data<br>type | Default | Туре | Comment                                                                                                                                                                        |

|-------|------|--------------------------------|--------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40    |      | frame_format_model_type        | 8UI          | 01      | RO   | Generic frame format.                                                                                                                                                          |

| 41    |      | frame_format_model_<br>subtype | 8UI          | 22      | RO   | Contains the number of 2-byte data format descriptors used. The upper nibble defines the number of column descriptors. The lower nibble defines the number of row descriptors. |

| 42    | HI   | frame_format_descriptor_0_     | 16UI 5a      | 5a      | RO   | number of visible columns.                                                                                                                                                     |

| 43    | LO   | req                            | 1001         | 28      | KO   | number of visible columns.                                                                                                                                                     |

| 44    | HI   | frame_format_descriptor_1      | 16UI         | 20      | RO   | 8 dummy columns.                                                                                                                                                               |

| 45    | LO   | name_format_descriptor_f       | 1001         | 08      | NO   | o durning columns.                                                                                                                                                             |

| 46    | HI   | frome format descriptor 2      | 16UI         | 10      | RO   | 2 omboddod rowo (SOE)                                                                                                                                                          |

| 47    | LO   | frame_format_descriptor_2      | 1001         | 03      | INO. | 3 embedded rows (SOF).                                                                                                                                                         |

| 48    | HI   | frame_format_descriptor_3_     | 16UI         | 57      | RO   | number of visible rows                                                                                                                                                         |

| 49    | LO   | req                            | 1001         | a0      | INO. | Trumber of visible tows                                                                                                                                                        |

# 4.2.3 Analogue gain description registers [0x0080 to 0x0093]

For a full description of the analogue gain description registers refer to Section 6.6.1.

Table 12. Analogue gain description [0x0080 to 0x0093]

| Index | Byte | Register name            | Data<br>type | Default | Туре | Comment                                 |

|-------|------|--------------------------|--------------|---------|------|-----------------------------------------|

| 80    | HI   | analogue_gain_capability | 16UI         | 00      | RO   | Analogue gain capability - single       |

| 81    | LO   | analogue_gain_capability | 1001         | 00      | INO  | global gain only.                       |

| 84    | HI   | analogue gain code min   | 16UI         | 00      | RO   | Minimum recommended analogue            |

| 85    | LO   | analogue_gain_code_min   | 1001         | 00      | KO   | gain code.                              |

| 86    | HI   |                          | 16UI         | 00      | RO   | Maximum recommended analogue gain code. |

| 87    | LO   | analogue_gain_code_max   | 1001         | fO      |      |                                         |

| 88    | HI   | analogue gain ando aton  | 40111        | 00      | RO   | Analogue spin and stan sing             |

| 89    | LO   | analogue_gain_code_step  | 16UI         | 10      | KO   | Analogue gain code step size.           |

| 8a    | HI   | analogue gain tune       | 16111        | 00      | RO   | Analogue gain tune                      |

| 8b    | LO   | analogue_gain_type       | 16UI         | 00      | RO   | Analogue gain type.                     |

| 8c    | HI   | - analogue_gain_m0 16l   | 16111        | 00      | DO.  | Analogue gain constant MO               |

| 8d    | LO   |                          | 1001         | 00      | RO   | Analogue gain constant M0.              |

Table 12. Analogue gain description [0x0080 to 0x0093] (continued)

| Index | Byte | Register name    | Data<br>type | Default | Туре                      | Comment                    |

|-------|------|------------------|--------------|---------|---------------------------|----------------------------|

| 8e    | HI   | analamus main s0 | 16UI         | 01      | RO                        | Analogue gain constant C0. |

| 8f    | LO   | analogue_gain_c0 | 1001         | 00      | INO                       | Analogue gain constant co. |

| 90    | HI   | analogue gain m1 | ff ff        | RO      | Analagua gain agnatant M4 |                            |

| 91    | LO   | analogue_gain_m1 | 16UI         | ff      | KO                        | Analogue gain constant M1. |

| 92    | HI   | analagua gain at | 40111        | 01      | RO                        | Analogue gain constant C1. |

| 93    | LO   | analogue_gain_c1 | 16UI         | 00      |                           |                            |

### 4.2.4 Data format description registers [0x00c0 to 0x00c9]

Table 13. Data format description registers [0x00c0 to 0x00c9]

| Index | Byte | Register name                 | Data<br>type | Default                            | Туре                                             | Comment                                          |

|-------|------|-------------------------------|--------------|------------------------------------|--------------------------------------------------|--------------------------------------------------|

| с0    |      | data_format_model_type        | 8UI          | 01                                 | RO                                               | 2-byte generic data format model type            |

| c1    |      | data_format_model_<br>subtype | 8UI          | 04                                 | RO                                               | Number of data format descriptors.               |

| c2    | HI   | data farrant danarintar O     | 16UI 08 RO   | RAW8 mode - transmit top 8 bits of |                                                  |                                                  |

| с3    | LO   | data_format_descriptor_0      | 1001         | 08                                 | NO                                               | pixel data.                                      |

| с4    | HI   | data format doggrintar 1      | 16UI         | 0a                                 | 0a RO                                            | RAW10 mode - transmit top 10 bits of pixel data. |

| c5    | LO   | data_format_descriptor_1      | 1001         | 0a                                 |                                                  |                                                  |

| с6    | HI   |                               |              | 0a                                 |                                                  | 10-8 compressed mode - transmit                  |

| с7    | LO   | data_format_descriptor_2      | 16UI         | 08                                 | RO                                               | top 10 bits of pixel data, compressed to 8 bits. |

| c8    | HI   |                               | 40111        | 0a                                 |                                                  | 10-6 compressed mode - transmit                  |

| с9    | LO   | data_format_descriptor_3      | 16UI         | 06 RO                              | top 10 bits of pixel data, compressed to 6 bits. |                                                  |

# 4.2.5 Setup registers [0x0100 to 0x0137]

Table 14. Setup registers [0x0100 to 0x0137]

| Index | Byte | Register name          | Data<br>type | Default | Туре | Comment                                                                                                                                                                                   |

|-------|------|------------------------|--------------|---------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100   |      | mode_select            | 8UI          | 00      | RW   | Mode select. 0 = Software standby. 1 = Streaming.                                                                                                                                         |

| 101   | [0]  | x_rev_req              | - 8UI        | 00      | RW   | Image orientation in X.  0 = Normal  1 = X-mirror mode.                                                                                                                                   |

| 101   | [1]  | y_rev_req              | - 601        | 00      | RW   | Image orientation in Y. 0 = Normal 1 = Y-flip mode.                                                                                                                                       |

| 103   |      | soft_reset             | 8UI          | 00      | RW   | Software reset returns the sensor to its power-on defaults.  0 = Normal operation.  1 = Software reset enabled.                                                                           |

| 104   |      | inhibit_retime         | 8UI          | 00      | RW   | The grouped parameter hold register disables the consumption of integration, gain and video timing parameters.  0 = Consume values as normal.  1 = Do not consume values whilst set high. |

| 105   |      | mask_corrupt           | 8UI          | 00      | RW   | Setting this register to 1 prevents the sensor out-putting frames that have been corrupted by video timing parameter changes.  0 = Output as normal.  1 = Mask corrupted frames.          |

| 107   |      | cci_addr               | 8UI          | 20      | RW   | Device address.                                                                                                                                                                           |

| 108   | [0]  | second_i2c_if_en       | - 8UI        | 00      | RW   | Second I <sup>2</sup> C interface enable. 0 = Disabled 1 = Enabled                                                                                                                        |

| 100   | [1]  | second_i2c_if_ack_en   | - 601        | 00      | RW   | Second I <sup>2</sup> C interface ACK enable.<br>0 = Disabled<br>1 = Enabled                                                                                                              |

| 109   |      | cci_2nd_addr           | 8UI          | 20      | RW   | Additional device address that can be responded to.                                                                                                                                       |

| 110   |      | csi_channel_identifier | 8UI          | 00      | RW   | The DMA (CCP2) or virtual (CSI2) channel identifier.  Valid range = 0 to 7 for CCP2.  Valid range = 0 to 3 for CSI2.                                                                      |

Table 14. Setup registers [0x0100 to 0x0137] (continued)

| Index | Byte | Register name       | Data<br>type | Default | Туре | Comment                                                                                                                                  |

|-------|------|---------------------|--------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------|

| 111   |      | csi_signalling_mode | 8UI          | 02      | RW   | Determines which transmission signalling mode is to be used.  0 = CCP2 data-clock signaling.  1 = CCP2 data-strobe signaling.  2 = CSI2. |

| 112   | НІ   |                     | 16UI         | 0a      | RW - | The value of this register contains the pixel width of the uncompressed pixel data.  Valid values are 0xA and 0x8.                       |

| 113   | LO   | csi_data_format     | 1601         | 0a      |      | The value of this register contains the pixel width of the compressed pixel data.  Valid values are 0xA and 0x8.                         |

| 114   |      | csi_lane_mode       | 8UI          | 01      | RW   | Number of data lanes in use. 0 = 1-lane. 1 = 2-lane.                                                                                     |

| 115   |      | csi2_10_to_8_dt     | 8UI          | 30      | RW   | CSI-2 data type for 10-to-8 compression.                                                                                                 |

| 117   |      | csi2_10_to_6_dt     | 8UI          | 31      | RW   | CSI-2 data type for 10-to-6 compression.                                                                                                 |

| 120   |      | gain_mode           | 8UI          | 00      | RO   | Global gain mode - this device only supports 0x00.                                                                                       |

| 130   | HI   | vana voltago        | 16UR         | 02      | RW   | Typical supplied VANA voltage.                                                                                                           |

| 131   | LO   | vana_voltage        | IOUK         | сс      | KVV  | Typical Supplied VAINA Voltage.                                                                                                          |

| 132   | HI   | vdig_voltage        | 16UR         | 01      | RW   | Typical supplied VDIG voltage.                                                                                                           |

| 133   | LO   | vaig_voitage        | 10010        | сс      | 1700 | Typical supplied VBIC Voltage.                                                                                                           |

| 134   | HI   | vio_voltage         | 16UR         | 01      | RW   | Typical IO voltage.                                                                                                                      |

| 135   | LO   |                     | 10011        | сс      |      | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                                                                  |

| 136   | HI   | ext_clkfreq         | 16UR         | 06      | RW   | 8.8 fixed-point representation of the                                                                                                    |

| 137   | LO   | <u>-</u>            |              | 00      |      | external clock-frequency, in MHz.                                                                                                        |

#### 4.2.6 Integration and gain registers [0x0200 to 0x0215]

These registers are used to control the image exposure. See Section 6.6 for more information.

Table 15. Integration and gain registers [0x0200 to 0x0215]

| Index | Byte | Register name       | Data<br>type | Default | Туре | Comment                                      |

|-------|------|---------------------|--------------|---------|------|----------------------------------------------|

| 200   | HI   | fine over year      | 16UI         | 02      | RW   | Fine integration time in pixels.             |

| 201   | LO   | fine_exp_req        | 1001         | ae      | IXVV | ine integration time in pixels.              |

| 202   | HI   | goorge eve reg      | 16UI         | 00      | RW   | Coargo integration time in lines             |

| 203   | LO   | coarse_exp_req      | 1001         | 00      | KVV  | Coarse integration time in lines.            |

| 204   |      | gain_req_dummy_hi   | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC test |

| 205   |      | gain_req            | 8UI          | 00      | RW   | Gain code for all channels.                  |

| 20e   | HI   | digital gain groopP | 16UR         | 01      | DW   | Green (red row) channel digital gain         |

| 20f   | LO   | digital_gain_greenR | IOUK         | 00      | RW   | value                                        |

| 210   | HI   | digital gain rad    | 16LID        | 01      | DW   | Dod shannel digital gain value               |

| 211   | LO   | digital_gain_red    | 16UR         | 00      | RW   | Red channel digital gain value               |

| 212   | HI   | digital gain blue   | 16LID        | 01      | RW   | Dive channel digital gain value              |

| 213   | LO   | digital_gain_blue   | 16UR         | 00      | KVV  | Blue channel digital gain value              |

| 214   | HI   | dicital main manage |              | 01      | DW   | Green (blue row) channel digital gain        |

| 215   | LO   | digital_gain_greenB | 16UR         | 00      | RW   | value.                                       |

### 4.2.7 Video timing registers [0x0300 to 0x0387]

For a full description of the video timing registers refer to *Chapter 5*.

Table 16. Video timing registers [0x0300 to 0x0387]

| Index | Byte | Register name           | Data<br>type | Default | Туре | Comment                                                                                                 |

|-------|------|-------------------------|--------------|---------|------|---------------------------------------------------------------------------------------------------------|

| 300   |      | vt_pix_clk_div_dummy_hi | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC.                                                                |

| 301   |      | vt_pix_clk_div          | 8UI          | 0a      | RW   | Video timing pixel clock divider.                                                                       |

| 302   |      | vt_sys_clk_div_dummy_hi | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC.                                                                |

| 303   |      | vt_sys_clk_div          | 8UI          | 01      | RW   | Video timing system clock divider.                                                                      |

| 304   |      | pre_pll_div_dummy_hi    | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC.                                                                |

| 305   |      | pre_pll_div             | 8UI          | 01      | RW   | Pre-PLL clock divider value.  1 = Divide EXTCLK by 1.  2 = Divide EXTCLK by 2.  4 = Divide EXTCLK by 4. |

Table 16. Video timing registers [0x0300 to 0x0387] (continued)

| Index | Byte | Register name           | Data<br>type | Default | Туре | Comment                                                                                                                                                 |

|-------|------|-------------------------|--------------|---------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| 306   |      | pll_mult_dummy_hi       | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC.                                                                                                                |

| 307   |      | pll_mult                | 8UI          | 85      | RW   | PLL multiplier value. Odd and even values can be used, but odd values result in the nearest lower even value being used (for example, 133 becomes 132). |

| 308   |      | op_pix_clk_div_dummy_hi | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC.                                                                                                                |

| 309   |      | op_pix_clk_div          | 8UI          | 0a      | RW   | Output timing pixel clock divider.                                                                                                                      |

| 30a   |      | op_sys_clk_div_dummy_hi | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC.                                                                                                                |

| 30b   |      | op_sys_clk_div          | 8UI          | 01      | RW   | Output timing system clock divider.                                                                                                                     |

| 340   | HI   | frame_length_req        | 16UI         | 08      | RW   | Length of the video frame in lines                                                                                                                      |

| 341   | LO   | mame_lengtii_req        | 1001         | 24      | IXVV | Length of the video frame in lines.                                                                                                                     |

| 342   | HI   | line_length_req         | 16UI         | 0a      | RW   | Length of a line of video in pixels.                                                                                                                    |

| 343   | LO   | inte_terigut_req        | 1001         | be      | IXVV | Length of a line of video in pixels.                                                                                                                    |

| 344   | HI   | - x_start_req           | 16UI         | 00      | RW   | X pixel address of the top left corner                                                                                                                  |

| 345   | LO   |                         | 1001         | 00      |      | of the visible pixel data.                                                                                                                              |

| 346   | HI   | y_start_req             | 16UI         | 00      | RW   | Y line address of the top left corner of                                                                                                                |

| 347   | LO   | 7                       |              | 00      |      | the visible pixel data.                                                                                                                                 |

| 348   | HI   | x_end_req               | 16UI         | 0a      | RW   | X pixel address of the bottom right corner of the visible pixel data.                                                                                   |

| 349   | LO   | ,                       |              | 27      |      |                                                                                                                                                         |

| 34a   | HI   | y_end_req               | 16UI         | 07      | RW   | Y line address of bottom right corner                                                                                                                   |

| 34b   | LO   | 7 1                     |              | 9f      |      | of the visible pixel data.                                                                                                                              |

| 34c   | HI   | x_op_size_req           | 16UI         | 0a      | RW   | Width in pixels of the output image                                                                                                                     |

| 34d   | LO   |                         |              | 28      |      | from the sensor.                                                                                                                                        |

| 34e   | HI   | y_op_size_req           | 16UI         | 07      | RW   | Height in lines of the output image                                                                                                                     |

| 34f   | LO   |                         |              | a0      |      | from the sensor.                                                                                                                                        |

| 380   |      | x_even_inc_req_dummy_hi | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC Test                                                                                                            |

| 381   |      | x_even_inc_req          | 8UI          | 01      | RW   | X address increment for even pixels.                                                                                                                    |

| 382   |      | x_odd_inc_req_dummy_hi  | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC test                                                                                                            |

| 383   |      | x_odd_inc_req           | 8UI          | 01      | RW   | X address increment for odd pixels.                                                                                                                     |

| 384   |      | y_even_inc_req_dummy_hi | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC test                                                                                                            |

DocID028544 Rev 1

Table 16. Video timing registers [0x0300 to 0x0387] (continued)

| Index | Byte | Register name          | Data<br>type | Default | Туре | Comment                                      |

|-------|------|------------------------|--------------|---------|------|----------------------------------------------|

| 385   |      | y_even_inc_req         | 8UI          | 01      | RW   | Y address increment for even lines.          |

| 386   |      | y_odd_inc_req_dummy_hi | 8UI          | 00      | RO   | Dummy HI byte to ensure presence in SLC test |

| 387   |      | y_odd_inc_req          | 8UI          | 01      | RW   | Y address increment for odd lines.           |

## 4.2.8 Scaler and digital crop registers [0x0400 to 0x040f]

Table 17. Scaler and digital crop registers [0x0400 to 0x040f]

| Index | Byte | Register name                 | Data<br>type | Default | Туре  | Comment                                                                                                  |

|-------|------|-------------------------------|--------------|---------|-------|----------------------------------------------------------------------------------------------------------|

| 400   |      | scale_mode_req_dummy_hi       | 8UI          | 00      | RO    |                                                                                                          |

| 401   |      | scale_mode_req                | 8UI          | 00      | RW    | Scaling mode 0 = No scaling 1 = Horizontal scaling                                                       |

| 402   |      | scale_cosite_req_dummy_<br>hi | 8UI          | 00      | RO    |                                                                                                          |

| 403   |      | scale_cosite_req              | 8UI          | 00      | RW    | Spatial sampling 0 = Bayer sampling 1 = Co-sited (2- or 4-component) 2 = Co-sited (3-component)          |

| 404   |      | scale_m_req_dummy_hi          | 8UI          | 00      | RO    |                                                                                                          |

| 405   |      | scale_m_req                   | 8UI          | 10      | RW    | Down scale factor. M component.                                                                          |

| 406   | HI   | anala n                       | 16UI         | 00      | RO    | Down scale factor N component                                                                            |

| 407   | LO   | scale_n                       | 1001         | 10      | INO   | Down scale factor. N component.                                                                          |

| 408   | HI   |                               |              | 00      |       | Offset from X-address of the top left                                                                    |