# Contents

| 1                                                                        | Simp    | lified ap | oplication schematic              | 6  |

|--------------------------------------------------------------------------|---------|-----------|-----------------------------------|----|

| 2                                                                        | Pin s   | ettings   |                                   | 7  |

|                                                                          | 2.1     | Connec    | tions                             | 7  |

|                                                                          | 2.2     | Pin des   | criptions                         | 7  |

| 3                                                                        | Elect   | rical da  | ta1                               | 0  |

|                                                                          | 3.1     | Maximu    | ım rating                         | 0  |

|                                                                          | 3.2     | Therma    | al data                           | 0  |

| 4                                                                        | Reco    | mmend     | ed operating conditions1          | 1  |

| 5                                                                        | Elect   | rical ch  | aracteristics1                    | 2  |

| 6                                                                        | Туріс   | al opera  | ating characteristics1            | 5  |

|                                                                          | 6.1     | Screen    | shots 1                           | 9  |

| 7                                                                        | Block   | < diagra  | m 2                               | 3  |

| <ul> <li>8 Device description</li> <li>8.1 Switching sections</li> </ul> | ription | 4         |                                   |    |

|                                                                          | 8.1     | Switchi   | ng sections                       | :4 |

|                                                                          |         | 8.1.1     | Output voltage set up 2           | 24 |

|                                                                          |         | 8.1.2     | Constant on time control (COT) 2  | 26 |

|                                                                          |         | 8.1.3     | PWM                               | 28 |

|                                                                          |         | 8.1.4     | SKIP                              | 29 |

|                                                                          |         | 8.1.5     | Non audible SKIP (NA SKIP) 2      | 29 |

|                                                                          |         | 8.1.6     | Gate drivers and logic supply3    | 90 |

|                                                                          |         | 8.1.7     | Current sensing and current limit | 31 |

|                                                                          |         | 8.1.8     | Soft-start and soft-end           | 32 |

| 9                                                                        | Monit   | toring a  | nd protections                    | 4  |

|                                                                          | 9.1     | Overvo    | Itage protection                  | 4  |

|                                                                          | 9.2     | Underv    | oltage protection                 | 4  |

|                                                                          | 9.3     | PVCC r    | monitor                           | 4  |

Doc ID 15281 Rev 4

2/50

|    | 9.4   | Linear r  | egulator section           |

|----|-------|-----------|----------------------------|

|    | 9.5   | Charge    | pump                       |

|    | 9.6   | Voltage   | references                 |

|    | 9.7   | Genera    | I device fault management  |

|    |       | 9.7.1     | Thermal protection         |

| 10 | Appli | cation i  | nformation                 |

|    | 10.1  | Externa   | Il components selection    |

|    |       | 10.1.1    | Inductor                   |

|    |       | 10.1.2    | Input capacitor            |

|    |       | 10.1.3    | Output capacitor           |

|    |       | 10.1.4    | MOSFET                     |

| 11 | Diode | e selecti | ion                        |

|    | 11.1  | Freewh    | eeling diode               |

|    | 11.2  | Charge    | pump diode 42              |

|    | 11.3  | Other ir  | nportant components 43     |

|    |       | 11.3.1    | VIN filter                 |

|    |       | 11.3.2    | PVCC and VCC               |

|    |       | 11.3.3    | VREF2 and VREF3 capacitors |

|    |       | 11.3.4    | LDO output capacitors      |

|    |       | 11.3.5    | Bootstrap circuit          |

| 12 | PCB   | design    | guidelines                 |

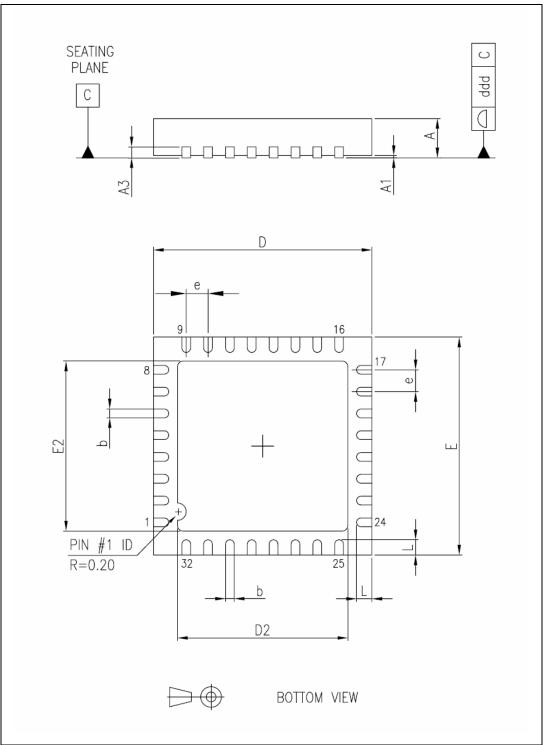

| 13 | Packa | age med   | chanical data 47           |

| 14 | Revis | ion his   | tory                       |

# List of figures

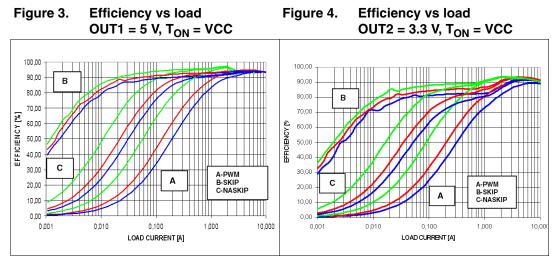

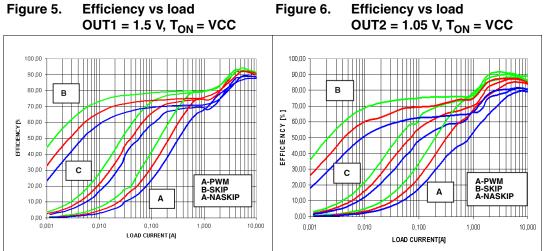

| Figure 1.  | Simplified application schematic                      | 6    |

|------------|-------------------------------------------------------|------|

| Figure 2.  | Pin connection (through top view)                     |      |

| Figure 3.  | Efficiency vs load OUT1 = 5 V, TON = VCC.             | . 15 |

| Figure 4.  | Efficiency vs load OUT2 = 3.3 V, TON = VCC            | . 15 |

| Figure 5.  | Efficiency vs load OUT1 = 1.5 V, TON = VCC            | . 15 |

| Figure 6.  | Efficiency vs load OUT2 = 1.05 V, TON = VCC           |      |

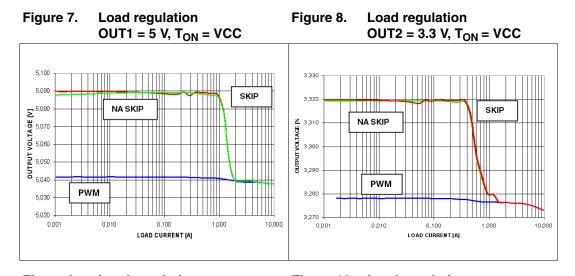

| Figure 7.  | Load regulationOUT1 = 5 V, TON = VCC                  |      |

| Figure 8.  | Load regulationOUT2 = 3.3 V, TON = VCC                |      |

| Figure 9.  | Load regulation OUT1 = 1.5 V, TON = VCC               |      |

| Figure 10. | Load regulation OUT2 = 1.05 V, TON = VCC.             |      |

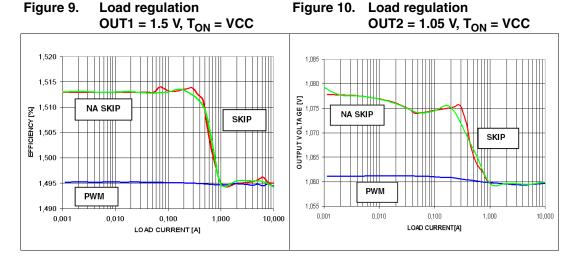

| Figure 11. | Switching frequency vs load OUT1 = 5 V, TON = VCC     |      |

| Figure 12. | Switching frequency vs load OUT2 = 3.3 V, TON = VCC.  |      |

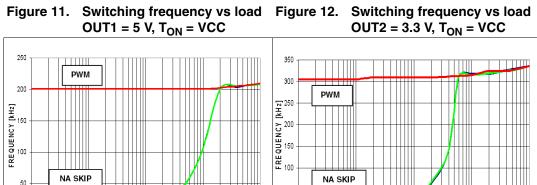

| Figure 13. | Section 1 line regulation OUT1 = 5 V, TON = VCC       |      |

| Figure 14. | Section 2 line regulation OUT2 = 3.3 V, TON = VCC     |      |

| Figure 15. | Section 1 line regulation OUT1 = 1,5 V, TON = VCC     |      |

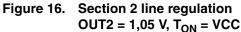

| Figure 16. | Section 2 line regulation OUT2 = 1,05 V, TON = VCC    |      |

| Figure 17. | Stand-by mode input battery current vs input voltage  |      |

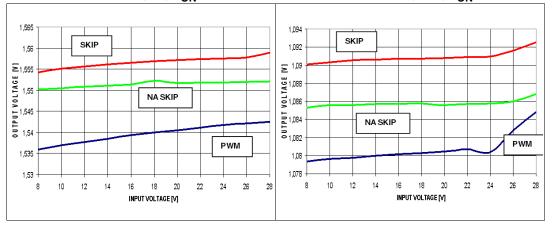

| Figure 18. | Shut-down mode input battery current vs input voltage |      |

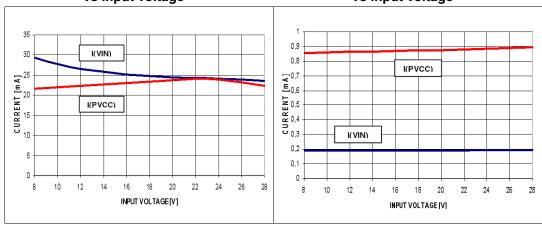

| Figure 19. | PWM no load input currents vs input voltage           |      |

| Figure 20. | SKIP no load input currents vs input voltage          |      |

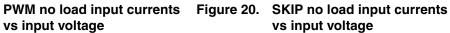

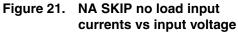

| Figure 20. | NA SKIP no load input currents vs input voltage       |      |

| Figure 21. | VREF3 load regulation                                 |      |

|            | •                                                     |      |

| Figure 23. | VREF2 load regulation                                 |      |

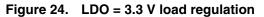

| Figure 24. | LDO = 3,3 V load regulation                           |      |

| Figure 25. | LDO = 5 V load regulation                             |      |

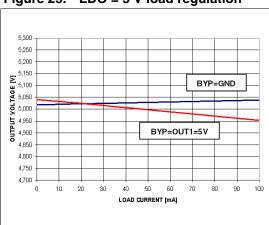

| Figure 26. | OUT1 soft-start no load                               |      |

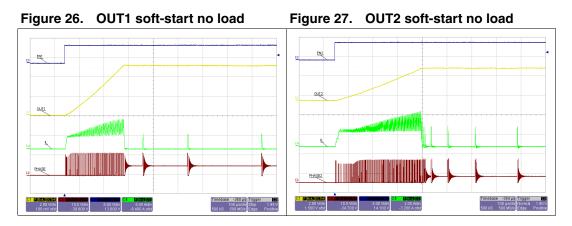

| Figure 27. | OUT2 soft-start no load                               |      |

| Figure 28. | OUT1 soft-start 8 A constant current load             |      |

| Figure 29. | OUT2 soft-start loaded 8 A constant current load      |      |

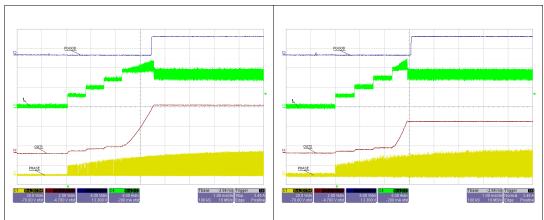

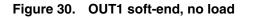

| Figure 30. | OUT1 soft-end, no load                                |      |

| Figure 31. | OUT2 soft-end, no load                                |      |

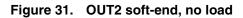

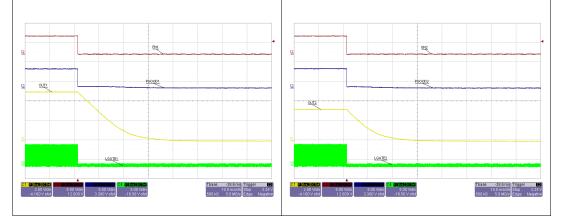

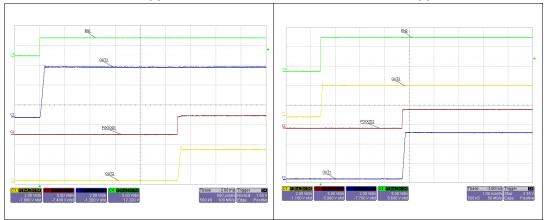

| Figure 32. | OUT1 soft-start, EN2 = VREF2 no loads applied         |      |

| Figure 33. | OUT2 soft-start, EN1=VREF2 no loads applied           |      |

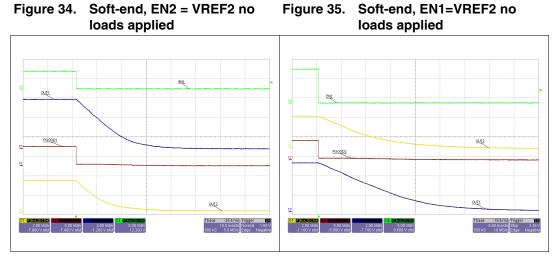

| Figure 34. | soft-end, EN2 = VREF2 no loads applied                |      |

| Figure 35. | soft-end, EN1=VREF2 no loads applied                  |      |

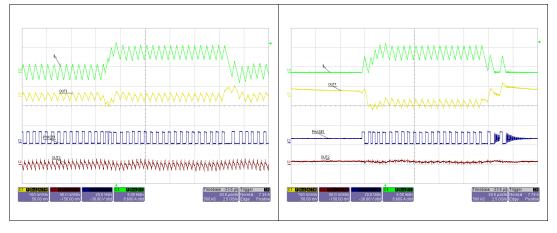

| Figure 36. | Load transient 0-5 A 2 A/µs OUT1 = 5 V PWM mode       |      |

| Figure 37. | Load transient 0-5 A 2 A/µs OUT1 = 5 V SKIP mode      |      |

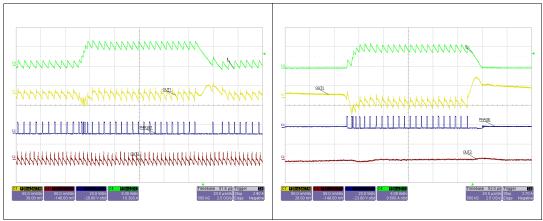

| Figure 38. | Load transient 0-5 A 2 A/ µs OUT1 = 1,5 V PWM mode    |      |

| Figure 39. | Load transient 0-5 A 2 A/ µs OUT1 = 1,5 V SKIP mode   |      |

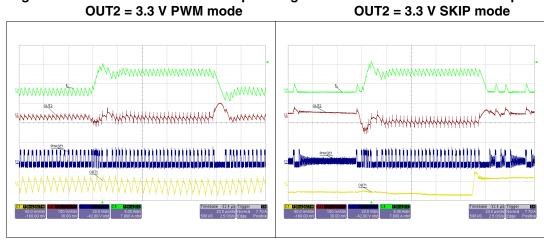

| Figure 40. | Load transient 0-5 A 2 A/µs OUT2 = 3.3 V PWM mode     |      |

| Figure 41. | Load transient 0-5 A 2 A/µs OUT2 = 3.3 V SKIP mode    |      |

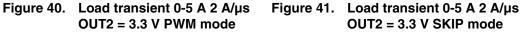

| Figure 42. | Load transient 0-5 A 2 A/ µs OUT2 = 1,05 V PWM mode   |      |

| Figure 43. | Load transient 0-5 A 2 A/ µs OUT2 = 1,05 V SKIP mode  | . 22 |

| Figure 44. | Functional block diagram                              |      |

| Figure 45. | Resistor divider to configure the output voltage      | . 25 |

| Figure 46. | Constant on time block diagram                        |      |

| Figure 47. | Inductor current and output voltage in PWM mode       |      |

| Figure 48. | Inductor current and output voltage in SKIP mode      | . 29 |

| Figure 49. | Inductor current and output voltage in NA SKIP mode       | 30 |

|------------|-----------------------------------------------------------|----|

| Figure 50. | Internal supply diagram                                   | 31 |

| Figure 51. | Current waveforms in current limit conditions             | 31 |

| Figure 52. | Current limit circuit block diagram                       | 32 |

| Figure 53. | VOUT2 behavior if EN2 is connected to VREF2               | 33 |

| Figure 54. | Charge pump application circuit                           | 36 |

| Figure 55. | VIN pin filter                                            | 43 |

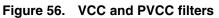

| Figure 56. | VCC and PVCC filters.                                     | 43 |

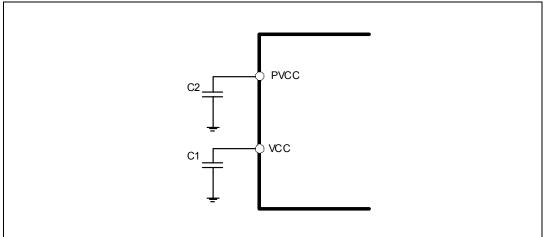

| Figure 57. | Bootstrap circuit                                         | 44 |

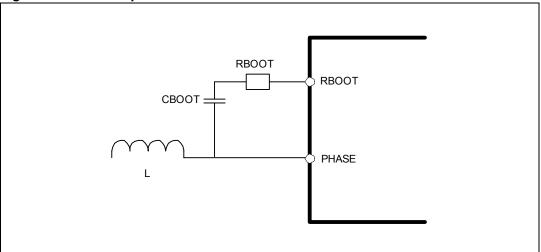

| Figure 58. | Current paths, ground connection and driver traces layout | 46 |

| Figure 59. | Package dimensions                                        | 48 |

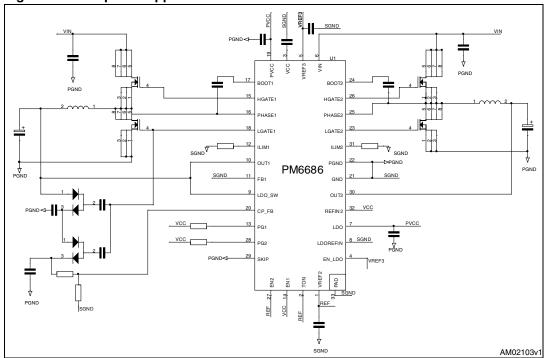

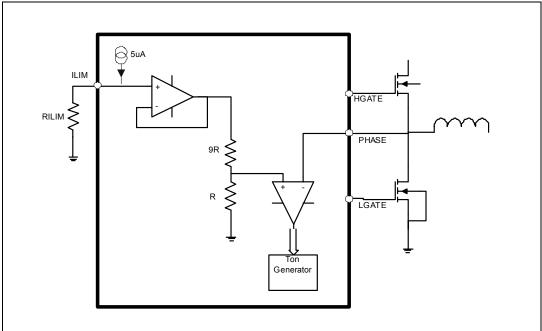

# **1** Simplified application schematic

Figure 1. Simplified application schematic

6/50

# 2 Pin settings

## 2.1 Connections

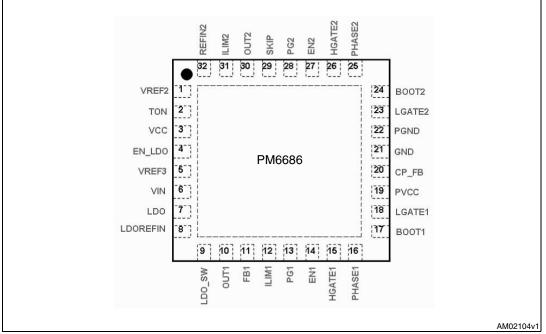

### Figure 2. Pin connection (through top view)

# 2.2 Pin descriptions

| Table 2. Pin descriptions |        |                                                                                                                                                                                                                                                                       |  |

|---------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| N°                        | Pin    | Function                                                                                                                                                                                                                                                              |  |

| 1                         | VREF2  | Internal 2 V high accuracy voltage reference. It can deliver 50 $\mu A.$ Loading VREF2 can affect FB and output accuracy. Bypass to GND with a 100 nF capacitor.                                                                                                      |  |

| 2                         | TON    | Frequency selection pin. It provides a selectable switching frequency, allowing three different values of switching frequencies for the switching sections.                                                                                                           |  |

| 3                         | VCC    | Controller supply voltage input. Bypass to GND with a 1 $\mu\text{F}$ capacitor.                                                                                                                                                                                      |  |

| 4                         | EN_LDO | Enable input for the linear regulator. The LDO is enabled if $EN_LDO$ is > 1.6 V and is disabled if $EN_LDO < 1$ V.                                                                                                                                                   |  |

| 5                         | VREF3  | Internal 3.3 V high accuracy voltage reference. It can deliver 5 mA if bypassed to GND with a 10 nF capacitor. If not used, it can be left floating.                                                                                                                  |  |

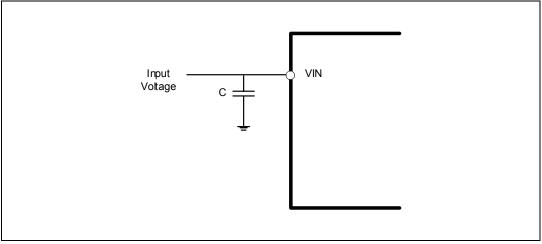

| 6                         | VIN    | Device supply voltage pin. VIN is used in the on-time generators of the two switching controllers. VIN is also used to power the linear regulator when the switchover function is not active. Connect VIN to the battery input and bypass with a 1 $\mu$ F capacitor. |  |

#### Table 2. Pin descriptions

| N° | Pin      | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | LDO      | Linear regulator output. It can provide up to 100 mA peak current. The LDO regulates at 5 V If LDOREFIN is connected to GND. When the LDO is set at 5 V and LDO_SW is within 5 V switchover threshold, the internal regulator shuts down and the LDO output pin is connected to LDO_SW through a 0.8 $\Omega$ switch. The LDO regulates at 3.3 V if LDOREFIN is connected to VCC. When the LDO is set at 3.3 V and LDO_SW is within 3.3 V switchover threshold, the internal regulator shuts down and the LDO set at 3.1 $\Omega$ switch. Bypass LDO output pin is connected to GND with a minimum of 4.7 $\mu$ F ceramic capacitor. |

| 8  | LDOREFIN | Feedback of the adjustable linear regulator. Connect LDOREFIN to GND for fixed 5 V operation. Connect LDOREFIN to VCC for fixed 3.3 V operation. LDOREFIN can be used to program LDO output voltage from 0.7 V to 4.5 V: LDO output is two times the voltage of LDOREFIN. The switchover function is disabled in adjustable mode.                                                                                                                                                                                                                                                                                                    |

| 9  | LDO_SW   | Source of the switchover connection. LDO_SW is the switchover source voltage for the LDO when LDOREFIN is connected to GND or VCC. Connect LDO_SW to 5 V if LDOREFIN is tied to GND. Connect LDO_SW to 3.3 V if LDOREFIN is tied to VCC.                                                                                                                                                                                                                                                                                                                                                                                             |

| 10 | OUT1     | Output voltage sense for the switching section 1. This pin must be directly connected to the output voltage of the switching section. It provides also the feedback for the switching section 1 when FB1 is tied to GND/VCC.                                                                                                                                                                                                                                                                                                                                                                                                         |

| 11 | FB1      | <ul> <li>Feedback input for the switching section 1:</li> <li>If this pin is connected to GND, OUT1 operates at 5 V</li> <li>If this pin is connected to VCC, OUT1 operates at 1.5 V</li> <li>This pin is connected to a resistive voltage-divider from OUT1 to GND to adjust the output voltage from 0.7 V to 5.5 V.</li> </ul>                                                                                                                                                                                                                                                                                                     |

| 12 | ILIM1    | Positive current sense input for the switching section 1. It is possible to set a threshold voltage that is compared with 1/10 <sup>th</sup> of the GND-PHASE1 drop during the off time.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 13 | PG1      | Power Good output signal for the section 1. This pin is an open drain output and It is pulled down when the output of the switching section 1 is out of $+/-10\%$ of its nominal value.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 14 | EN1      | <ul> <li>Enable input for the switching section 1.</li> <li>If EN1 &lt; 0.8 V the switching section OUT1 is turned off and all faults are cleared.</li> <li>If EN1 &gt; 2.4 V the switching section OUT1 is turned on.</li> <li>If EN1 is connected to VREF2, the switching section OUT1 turns on after the switching section OUT2 reaches regulation.</li> </ul>                                                                                                                                                                                                                                                                    |

| 15 | HGATE1   | High-side gate driver output for section 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16 | PHASE1   | Switch node connection and return path for the high-side driver for the section 1.It is also used as positive and negative current sense input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 17 | BOOT1    | Bootstrap capacitor connection for the switching section 1. It supplies the high-side gate driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 18 | LGATE1   | Low-side gate driver output for the section 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 19 | PVCC     | 5 V low-side gate drivers supply voltage input. Bypass to PGND with a 1 $\mu\text{F}$ capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### Table 2. Pin descriptions (continued)

8/50

|    | Table 2.         Pin descriptions (continued) |                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|----|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| N° | Pin                                           | Function                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 20 | CP_FB                                         | The CP_FB is used to monitor the optional external 14 V charge pump.<br>Connect a resistive voltage-divider from 14 V charge pump output to GND. If<br>CP_FB drops below the threshold voltage, the device performs a no audible<br>skip cycle. This charges the charge pump output (driven by LGATE1). Leave<br>CP_FB floating if the charge pump feedback is not needed.       |  |  |  |

| 21 | GND                                           | Signal ground reference for internal logic circuitry and LDO. It must be connected to the signal ground plan of the power supply and to the exposed pad. The signal ground plan and the power ground plan must be connected together in one point near the PGND pin.                                                                                                             |  |  |  |

| 22 | PGND                                          | Power ground. This pin must be connected to the power ground plan of the power supply.                                                                                                                                                                                                                                                                                           |  |  |  |

| 23 | LGATE2                                        | Low-side gate driver output for the section 2.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 24 | BOOT2                                         | Bootstrap capacitor connection for the switching section 2. It supplies the high-side gate driver.                                                                                                                                                                                                                                                                               |  |  |  |

| 25 | PHASE2                                        | Switch node connection and return path for the high-side driver for the section 2. It is also used as positive and negative current sense input.                                                                                                                                                                                                                                 |  |  |  |

| 26 | HGATE2                                        | High-side gate driver output for section 2.                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 27 | EN2                                           | <ul> <li>Enable input for the switching section 2.</li> <li>If EN2 &lt; 0.8 V the switching section OUT2 is turned off and all faults are cleared.</li> <li>If EN2 &gt; 2.4 V the switching section OUT2 is turned on.</li> <li>If EN2 is connected to VREF2, the switching section OUT2 turns on after the switching section OUT1 reaches regulation.</li> </ul>                |  |  |  |

| 28 | PG2                                           | Power Good output signal for the section 2. This pin is an open drain output and It is pulled down when the output of the switching section 2 is out of $+ 14\% / - 10\%$ of its nominal value.                                                                                                                                                                                  |  |  |  |

| 29 | SKIP                                          | <ul> <li>Pulse skipping mode control input.</li> <li>If the pin is connected to VCC the PWM mode is enabled.</li> <li>If the pin is connected to GND, the pulse skip mode is enabled.</li> <li>If the pin is connected to VREF2 (or floating) the pulse skip mode is enabled but and the switching frequency is kept higher than 33 kHz (No-audible pulse skip mode).</li> </ul> |  |  |  |

| 30 | OUT2                                          | Output voltage sense for the switching section 2. This pin must be directly connected to the output voltage of the switching section. It provides also the feedback for the switching section 2 when REFIN2 is tied to VREF3/VCC.                                                                                                                                                |  |  |  |

| 31 | ILIM2                                         | Positive current sense input for the switching section 2. It is possible to set a threshold voltage that is compared with 1/10 <sup>th</sup> of the GND-PHASE2 drop during the off time.                                                                                                                                                                                         |  |  |  |

| 32 | REFIN2                                        | <ul> <li>Feedback input for the switching section 2:</li> <li>If this pin is connected to VCC, OUT2 operates at 3.3 V</li> <li>If this pin is connected to VREF3, OUT2 operates at 1.05 V</li> <li>If this pin is connected to an external reference from 0.7 V to 2.5 V, OUT2 works in tracking with this reference. Bypass REFIN2 to GND with a 100 nF capacitor.</li> </ul>   |  |  |  |

| Table 2. | <b>Pin descriptions</b> | (continued) |

|----------|-------------------------|-------------|

|----------|-------------------------|-------------|

# 3 Electrical data

# 3.1 Maximum rating

## Table 3. Absolute maximum ratings

| Parameter                                                                                                                         | Value              | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------|------|

| VIN to PGND                                                                                                                       | -0.3 to 38         | V    |

| PHASEx to PGND                                                                                                                    | -0.3 to 38         | V    |

| BOOTx to PHASEx                                                                                                                   | -0.3 to 6          | V    |

| PVCC to PGND                                                                                                                      | -0.3 to 6          | V    |

| HGATEx to PHASEx                                                                                                                  | -0.3 to BOOTx +0.3 | V    |

| LGATEx, CP_FB to PGND                                                                                                             | -0.3 to PVCC +0.3  | V    |

| VCC, ENx, SKIP, PGx, LDO, REFIN2, OUTx, VREF3,<br>LDOREFIN, LDO_SW, TON to GND                                                    | -0.3 to 6          | V    |

| FB1, ILIMx to GND                                                                                                                 | -0.3 to VCC+0.3    | V    |

| EN_LDO to GND                                                                                                                     | -0.3 to 7          | V    |

| VREF2 to GND                                                                                                                      | -0.3 to VREF3+0.3  | V    |

| PGND to GND                                                                                                                       | -0.3 to +0.3       | V    |

| Power dissipation at $T_A = 25 \ ^{\circ}C$                                                                                       | 2                  | W    |

| Maximum withstanding voltage range test condition: CDF-AEC-Q100-002- "human body model" acceptance criteria: "normal performance" | ±1250              | v    |

## 3.2 Thermal data

#### Table 4. Thermal data

| Symbol            | Parameter                              | Value      | Unit |

|-------------------|----------------------------------------|------------|------|

| R <sub>thJA</sub> | Thermal resistance junction to ambient | 35         | °C/W |

| TJ                | Junction operating temperature range   | -40 to 125 | °C   |

| T <sub>STG</sub>  | Storage temperature range              | -50 to 150 | °C   |

| T <sub>A</sub>    | Operating ambient temperature range    | -40 to 85  | °C   |

# 4 Recommended operating conditions

| Symbol                                                              | Parameter                                                              |      | Value |      |      |  |

|---------------------------------------------------------------------|------------------------------------------------------------------------|------|-------|------|------|--|

| Symbol                                                              |                                                                        |      | Тур   | Max  | Unit |  |

| VIN                                                                 | Input voltage range, LDO = 5 V in regulation                           | 5.5  | -     | 28   | V    |  |

| VCC                                                                 | VCC operative voltage range                                            | 4.5  | -     | 5.5  | V    |  |

| REFIN2                                                              | REFIN2 voltage range with OUT2 in adjustable mode, VIN = 5.5 V to 28 V | 0.7  | -     | 2.5  | V    |  |

| OUT1                                                                | OUT1 output voltage range                                              | 0.70 | -     | 5.50 | V    |  |

| ILIM ILIM voltage range                                             |                                                                        | 0.2  | -     | 2    | V    |  |

| LDOREFIN LDOREFIN setting with LDO = 2 x LDOREFIN (adjustable mode) |                                                                        | 0.35 | -     | 2.25 | V    |  |

| LDO DC output current<br>(switchover function                       | VIN = 5.5 V to 28 V, LDO_SW = 5 V,<br>LDOREFIN = GND                   |      | -     | 200  | mA   |  |

| enabled)                                                            | VIN = 5.5 V to 28 V, LDO_SW = 3.3 V,<br>LDOREFIN = VCC                 |      | -     | 100  | mA   |  |

| LDO DC output current<br>(switchover function<br>disabled)          | VIN = 5.5 V to 28 V, LDO_SW = 0 V,<br>LDOREFIN = GND, VCC              |      | -     | 100  | mA   |  |

### Table 5. Recommended operating conditions

# 5 Electrical characteristics

VIN = 12 V, no load on LDO, OUT1, OUT2, VREF3, and VREF2. EN2 = EN1 = VCC, LDO\_SW = 5 V, PVCC = 5 V, EN\_LDO = 5 V,  $T_J$  = 25 °C unless otherwise specified)

Table 6.

Electrical characteristics

| Symbol       | Parameter                                      | Test co                                       | ondition              | Min   | Тур   | Max   | Unit |

|--------------|------------------------------------------------|-----------------------------------------------|-----------------------|-------|-------|-------|------|

| Switching    | controller output accuracy                     |                                               |                       | ·     |       |       |      |

|              | Quita ut us lta an                             | VIN = 5.5 V to 28 V,<br>SKIP = VCC            | REFIN2 = VCC,         | 3.25  | 3.330 | 3.397 | V    |

| OUT2         | Output voltage                                 | VIN = 5.5 V to 28 V,<br>REFIN2 = VREF3, S     | SKIP = VCC            | 1.038 | 1.05  | 1.062 | V    |

|              | Quality to us have                             | VIN = 5.5 V to 28 V,<br>SKIP = VCC            | FB1 = VCC,            | 1.482 | 1.500 | 1.518 | V    |

| OUT1         | Output voltage                                 | VIN = 5.5 V to 28 V,<br>SKIP = VCC            | FB1 = GND,            | 4.975 | 5.050 | 5.125 | V    |

| FB1          | Feedback accuracy with OUT1 in adjustable mode | VIN = 5.5 V to 28 V,                          | SKIP = VCC            | 0.693 | 0.700 | 0.707 | V    |

| REFIN2       | Accuracy referred to REFIN2                    | REFIN2 = 0.7 V to 2<br>SKIP = VCC             | .5 V,                 | -1    |       | 1     | %    |

| Current lin  | nit and zero crossing compara                  | tor                                           |                       |       |       |       |      |

| ILIM         | ILIM bias current                              | T <sub>A</sub> = +25 °C.                      |                       | 4.5   | 5     | 5.5   | μA   |

|              |                                                | Adjustable, VILIM = 0.5 V, GND-PHASE          |                       | 35    | 50    | 65    | mV   |

|              | Positive current limit threshold               | Adjustable, VILIM = 1 V or VCC, GND-<br>PHASE |                       | 85    | 100   | 115   | mV   |

|              |                                                | Adjustable, VILIM = 2 V, GND-PHASE            |                       | 180   | 200   | 220   | mV   |

|              | Zero crossing current threshold                | SKIP = GND, VREF2, or OPEN, GND-<br>PHASE     |                       | -1    |       | +11   | mV   |

| Switching    | frequency                                      |                                               |                       |       |       |       |      |

|              |                                                | OUT1 = 5.125 V                                | TON = GND or<br>VREF2 | 0.908 | 1.068 | 1.228 |      |

|              | On-time pulse width                            |                                               | TON = VCC             | 1.815 | 2.135 | 2.455 |      |

|              |                                                | OUT2 = 3.368 V                                | TON = GND             | 0.477 | 0.561 | 0.655 | μs   |

|              |                                                |                                               | TON = VCC or<br>VREF2 | 0.796 | 0.936 | 1.076 |      |

|              | Minimum Off-time                               |                                               |                       |       | 350   | 472   |      |

|              | No-audible skip mode operating frequency       | SKIP = VREF2(or O                             | PEN)                  | 25    | 33    |       | kHz  |

| Soft-start a | and soft-end                                   |                                               |                       | ·     |       |       |      |

|              | Soft-start ramp time                           |                                               |                       | 2     |       | 4     | ms   |

| Table 6. Electrical characteristics (continued) | Table 6. | Electrical characteristics | (continued) |

|-------------------------------------------------|----------|----------------------------|-------------|

|-------------------------------------------------|----------|----------------------------|-------------|

|             |                                                                  |                                                                                                                      |       |       |       | -    |

|-------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------|-------|-------|------|

| Symbol      | Parameter                                                        | Test condition                                                                                                       | Min   | Тур   | Max   | Unit |

| Linear regu | lator and reference                                              | ·                                                                                                                    |       |       |       |      |

|             |                                                                  | LDO_SW = GND, 5.5 V < VIN < 28 V,<br>LDOREFIN < 0.3 V, 0 < ILDO < 100 mA                                             | 4.925 | 5.000 | 5.075 | V    |

| LDO         | LDO output voltage                                               | LDO_SW = GND, 5.5 V < VIN < 28 V,<br>LDOREFIN = VREF3,<br>0 < ILDO < 100 mA                                          | 3.250 | 3.300 | 3.350 | V    |

|             | LDO accuracy in adjustable mode                                  | VIN = 5.5 V to 28 V, LDOREFIN = 0.35 V to 2.25 V, no load                                                            | -2.5  |       | +2.5  | %    |

|             | LDO short circuit current<br>(linear regulator enabled)          | LDO = 4.3 V, LDO_SW = GND                                                                                            | 260   | 320   | 380   | mA   |

| LDO_SW      | LDO_SW switch on threshold                                       | LDO = 5 V, rising edge of LDO_SW,<br>LDOREFIN = GND                                                                  | 4.64  | 4.75  | 4.84  | V    |

| LDO_SW      | LDO_SW hysteresis                                                | LDO = 5 V, falling edge of LDO_SW,<br>LDOREFIN = GND                                                                 |       | 200   | 400   | mV   |

|             | LDO_SW switch resistance                                         | LDO = 5 V, rising edge of LDO_SW,<br>LDOREFIN = GND,<br>output current = 200 mA                                      |       | 0.81  | 1.275 | Ω    |

| VDEEO       | VREF3 output voltage                                             | No load                                                                                                              | 3.235 | 3.300 | 3.365 | V    |

| VREF3       | VREF3 current limit                                              | VREF3 = GND                                                                                                          |       | 22    | 30    | mA   |

| VREF2       | VREF2 output voltage                                             | No load                                                                                                              | 1.980 | 2.000 | 2.02  | V    |

|             | VREF2 load regulation                                            | 0 < Load < 50 μA                                                                                                     |       | 6     |       | mV   |

|             | VREF2 sink current                                               | VREF2 > 2.030 V                                                                                                      | 10    |       |       | μA   |

|             | VIN shutdown current                                             | EN1 and EN2 low, EN_LDO low                                                                                          |       | 49    | 70    | μA   |

|             | VIN standby current                                              | EN1 and EN2 low, EN_LDO high,<br>LDOREFIN = GND                                                                      |       | 132   | 180   | μA   |

|             | Operating power consumption<br>(VCC and VIN pins<br>consumption) | Switching regulators on,<br>FB1 = SKIP = GND, REFIN2 = VCC,<br>LDOREFIN = GND,<br>OUT1 = LDO_SW = 5.3V, OUT2 = 3.5 V |       | 4,3   | 6,5   | mW   |

| Fault mana  | gement                                                           |                                                                                                                      |       |       |       |      |

|             |                                                                  | Rising edge of PVCC                                                                                                  |       | 4.33  |       | V    |

|             | PVCC UVLO threshold                                              | Falling edge of PVCC                                                                                                 |       | 4     |       | V    |

|             |                                                                  | Referred to FB1 nominal regulation point                                                                             |       | +11   |       | %    |

|             | Overvoltage trip threshold                                       | Referred to REFIN2 nominal regulation point. worst case:REFIN2 = 0.7 V                                               |       | +14   |       | %    |

|             | PG threshold                                                     | Lower threshold                                                                                                      | -13   | -10   | -7    | %    |

|             | PG low voltage                                                   | ISink = 4 mA                                                                                                         | 159   | 235   | 405   | mV   |

|             | PG leakage current                                               | PG = 5 V                                                                                                             |       |       | 1     | μA   |

| Table 6.     | Electrical characteristics             | (continued)                                      |               |       |       |      |

|--------------|----------------------------------------|--------------------------------------------------|---------------|-------|-------|------|

| Symbol       | Parameter                              | Test condition                                   | Min           | Тур   | Max   | Unit |

|              | Output undervoltage shutdown threshold | Referred to FB1, REFIN2 nominal regulation point | 67            | 70    | 73    | %    |

| Inputs and   | outputs                                |                                                  |               |       |       |      |

| <b>ED</b> 4  |                                        | fixed OUT1 = 5 V                                 |               |       | 0.528 | V    |

| FB1          | FB1 logic level                        | fixed OUT1 = 1.5 V                               | 4.1           |       |       | V    |

|              |                                        | fixed OUT2 = 1.05 V, VCC = 5 V                   |               | VREF3 |       | V    |

| REFIN2       | REFIN2 logic level                     | fixed OUT 2= 3.3 V, VCC = 5 V                    | VCC-<br>0.838 |       |       | V    |

|              | LDOREFIN logic level                   | fixed LDO = 5 V                                  |               |       | 0.4   | V    |

| LDONEFIN     |                                        | fixed LDO = 3.3 V                                | 2.43          |       |       | V    |

|              |                                        | Pulse skip mode                                  |               |       | 0.8   | V    |

| SKIP         | SKIP logic level                       | No audible skip mode (VREF2 or floating)         |               | VREF2 |       | V    |

|              |                                        | PWM mode                                         | 2.4           |       |       | V    |

|              |                                        | Low level                                        |               |       | 0.8   | V    |

| TON          | TON logic level                        | Middle level                                     |               | VREF2 |       | V    |

|              |                                        | High level                                       | 2.4           |       |       | V    |

|              |                                        | Switching regulators off level                   |               |       | 0.8   | V    |

| EN1,2        | EN level                               | Delay start level                                |               | VREF2 |       | V    |

|              |                                        | Switching regulators on level                    | 2.4           |       |       | V    |

| EN_LDO       | EN LDO level                           | Linear regulator off level                       | 0.905         | 1.00  | 1.050 | V    |

|              |                                        | Linear regulator on level                        | 1.500         | 1.6   | 1.650 | V    |

|              | Input leakage current                  | FB1 = 0.7 V                                      | -1            |       | +1    | μA   |

|              |                                        | REFIN2 = 2.5 V                                   |               | 12    |       |      |

| Internal boo | otstrap diode                          |                                                  |               |       |       |      |

|              | Diode forward voltage                  | PVCC = -BOOT, Idiode = 10 mA                     |               | 0.2   |       | V    |

|              | Diode Leakage current                  | BOOT= 30 V, PHASE = 28 V, PVCC = 5 V             |               |       | 500   | nA   |

| High-side a  | nd low-side gate drivers               |                                                  |               |       |       |      |

|              | LIGATE driver on registeres            | HGATEx high state (pull-up)<br>Isource = 100 mA  |               | 1.8   |       |      |

|              | HGATE driver on-resistance             | HGATEx low state (pull-down)<br>Isink = 100 mA   |               | 1.3   | 1.9   | Ω    |

|              | LGATE driver on-resistance             | LGATEx high state (pull-up)<br>Isource = 100 mA  |               | 1.3   |       | 52   |

|              |                                        | LGATEx low state (pull-down)<br>Isink = 100 mA   |               | 0.6   | 0.8   |      |

### Table 6. Electrical characteristics (continued)

14/50

# 6 Typical operating characteristics

(T<sub>ON</sub> = VCC (200 / 300 kHz), SKIP = GND (skip mode), LDOREFIN = SGND (LDO = 5 V), LDO\_SW = OUT1, PVCC connected to LDO,  $V_{IN}$  = 12 V, EN1-EN2-EN\_LDO are high, no load unless specified). Measures performed on the demonstration kit (PM6686\_SYSTEM and PM6686\_CHIPSET)

Efficiency traces: Green: VIN = 7 V, red: VIN = 12 V, blue: VIN = 19 V.

Doc ID 15281 Rev 4

50 50 ТП SKIP SKIP 0. n 0,001 0,010 1,000 10,000 0,100 0,001 0,010 0,100 1,000 10,000 LOAD CURRENT [A] LOAD CURRENT [A]

Doc ID 15281 Rev 4

Figure 15. Section 1 line regulation OUT1 = 1,5 V, T<sub>ON</sub> = VCC

Figure 17. Stand-by mode input battery Figure 18. Shut-down mode input current vs input voltage

Figure 19.

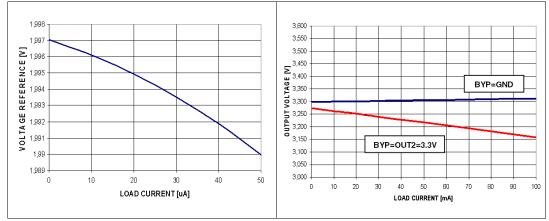

Figure 25. LDO = 5 V load regulation

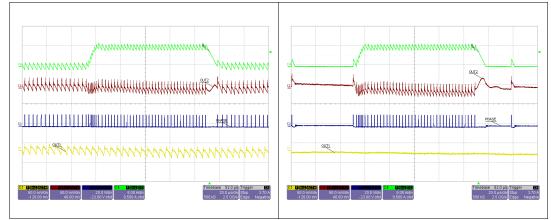

## 6.1 Screen shots

Typical operating characteristic ( $T_{ON}$  = VCC (200 / 300 kHz), SKIP = GND (skip mode), FB1 = GND (OUT1 = 5 V), REFIN2 = VCC (OUT2 = 3.3 V), LDOREFIN = SGND (LDO = 5 V), CP\_FB = floating, LDO\_SW = OUT1, PVCC connected to LDO, VIN = 12 V, EN1-EN2-EN\_LDO are high, no load unless specified)

# Figure 28. OUT1 soft-start 8 A constant Figure 29. OUT2 soft-start loaded 8 A current load constant current load

Figure 32. OUT1 soft-start, EN2 = VREF2 Figure 33. OUT2 soft-start, EN1=VREF2 no loads applied no loads applied

Figure 36. Load transient 0-5 A 2 A/ $\mu$ s OUT1 = 5 V PWM mode

Figure 37. Load transient 0-5 A 2 A/µs OUT1 = 5 V SKIP mode

Figure 38. Load transient 0-5 A 2 A/ µs Figure 39. Load to OUT1 = 1.5 V PWM mode OUT1

e 39. Load transient 0-5 A 2 A/ μs OUT1 = 1.5 V SKIP mode

#### PM6686

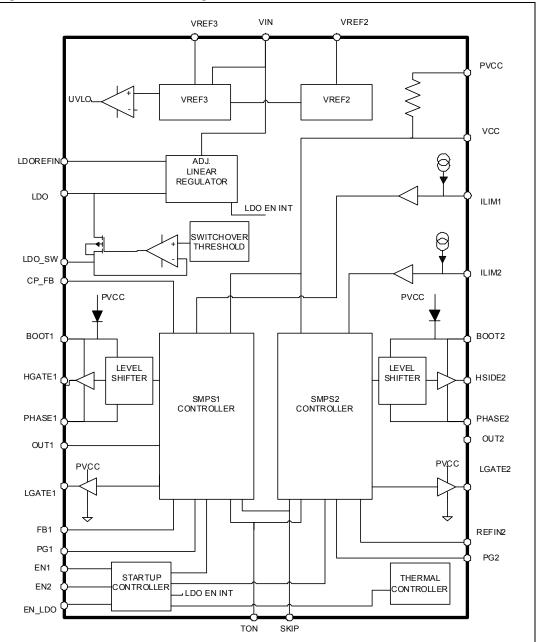

# 7 Block diagram

Figure 44. Functional block diagram

# 8 Device description

The PM6686 is a dual step down controller dedicated to provide logic voltages for notebook computers. It offers several operating configurations: it combines two synchronous buck controllers, an internal linear regulator (LDO), two voltage references and a charge pump controller.

Each buck controller is based on constant on time (COT) architecture. This type of control offers a very fast load transient response with a minimum external components count.

The two switching sections (SMPS) generate two output voltages OUT1 and OUT2 that regulate adjustable voltages. A fixed output voltage configuration can also be selected, reducing further the external components count because no external resistor divider is needed.

In fixed mode, OUT1 provides 5 V or 1.5 V; in adjustable mode OUT1 can regulate an output voltage between 0.7 V and 5.5 V. In fixed mode, OUT2 provides 3.3 V or 1.05 V, in adjustable mode OUT2 can regulate an output between 0.7 V to 2.5 V by tracking an external reference.

The switching frequencies of both switching controllers can be adjusted to 200 kHz/300 kHz, 400 kHz/300 kHz or 400 kHz/500 kHz respectively. To maximize the efficiency at light loads a pulse skipping mode can be selected. Moreover a pulse skipping mode with a minimum switching frequency of 33 kHz (non audible skip operation mode) can be selected to avoid audible noise issue. The linear regulator can provide a fixed (5 V or 3.3 V) or an adjustable output voltage. In order to reduce the power consumption the internal LDO can be turned off and the LDO output can be supplied with an external voltage applied at LDO\_SW pin (switch-over function).

The PM6686 supplies two voltage references: 3.3 V and 2 V. The charge pump controller can be programmed to regulate a 14 V output. The switching sections and the LDO have independent enable signals. Moreover the switching sections have a selectable power up sequence and a turn off management.

The device is protected against overvoltage, undervoltage and over temperature. Two independent Power Good signals monitor the output voltage range of each switching sections.

## 8.1 Switching sections

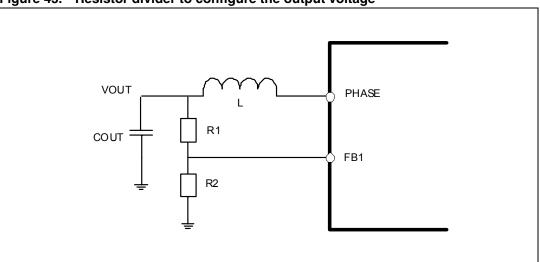

### 8.1.1 Output voltage set up

The switching sections can be configured in several ways.

OUT1 output voltage is configured with FB1 pin. If FB1 pin is tied to GND the PM6686 regulates 5 V while if FB1 is connected to VCC the controller set OUT1 at 1.5 V. Using an external resistor divider the output can be adjusted following this equation:

#### **Equation 1**

$$V_{OUT1}=0,7V\cdot\left(\frac{R1}{R2}+1\right)$$

24/50

Doc ID 15281 Rev 4

Figure 45. Resistor divider to configure the output voltage

OUT2 output voltage is programmed with REFIN2 pin. Fixed output voltage is selected connecting REFIN2 to VREF3 (OUT2 = 1.05 V) or to VCC (OUT2 = 3.3 V). When the REFIN2 voltage is between 0.7 V and 2.5 V, OUT2 output voltage tracks REFIN2 voltage. When REFIN2 is lower than 0.5 V the section is turned OFF.

| Table 7.Switching output voltages configuration |

|-------------------------------------------------|

|-------------------------------------------------|

| Output      | control pin      | Control pin<br>connected to | Operation mode                                         | Output voltage |

|-------------|------------------|-----------------------------|--------------------------------------------------------|----------------|

|             |                  | GND                         | Fixed                                                  | 5 V            |

|             |                  | VCC                         | Fixed                                                  | 1.5 V          |

| OUT1 FB1    | Resistor divider | Adj                         | $V_{OUT1} = 0.7V \cdot \left(\frac{R1}{R2} + 1\right)$ |                |

| OUT2 REFIN2 | VCC              | Fixed                       | 3.3 V                                                  |                |

|             | REFIN2           | VREF3                       | Fixed                                                  | 1.05 V         |

|             |                  | Ext source                  | Tracking                                               | =REFIN2        |

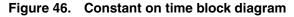

### 8.1.2 Constant on time control (COT)

PM6686 implements a pseudo-fixed frequency algorithm using the COT architecture. The two sections are completely independent with separated switching controllers (SMPS).

The COT architecture bases its algorithm on the output ripple derived across the output capacitor's ESR. The controller has an internal on time ( $T_{ON}$ ) generator triggered on the output voltage valley: when VOUT reaches the regulation value a new  $T_{ON}$  starts. The  $T_{ON}$  duration is given by the following equation:

#### **Equation 2**

$$T_{ON} = K \cdot \frac{V_{OUT}}{V_{IN}}$$

Where  $T_{ON}$  is the on time duration, K is a constant,  $V_{OUT}$  is the sensed output voltage and VIN is the input voltage.

The duty cycle in a buck converter is:

#### **Equation 3**

$$\frac{T_{ON}}{T_{SW}} = D = \frac{V_{OUT}}{V_{IN}}$$

The switching frequency in continuous current mode (CCM) is:

#### **Equation 4**

$$f_{SW} = \frac{D}{T_{ON}} = \frac{\frac{V_{OUT}}{V_{IN}}}{K \cdot \frac{V_{OUT}}{V_{IN}}} = \frac{1}{K}$$

The switching frequency is theoretically constant, but in a real application it depends on parasitic voltage drops that occur during the charging path (high-side switch resistance, inductor resistance (DCR)) and discharging path (low-side switch resistance, DCR). As a result the switching frequency increases as a function of the load current. The following table shows the switching frequencies that can be selected through TON pin:

Table 8. Frequency configurations

| TON           | SMF       | PS 1   | SMPS 2    |         |  |

|---------------|-----------|--------|-----------|---------|--|

| ION           | Frequency | К      | Frequency | К       |  |

| VCC           | 200 kHz   | 5 µs   | 300 kHz   | 3.33 µs |  |

| VREF2 or open | 400 kHz   | 2.5 µs | 300 kHz   | 3.33 µs |  |

| GND           | 400 kHz   | 2.5 µs | 500 kHz   | 2 µs    |  |

The COT architecture uses a minimum off-time ( $T_{OFFMIN}$ ) to allow inductor valley current sense on the synchronous switch and to allow the charge of the bootstrap capacitor. A minimum on-time is also introduced to assure the start-up sequence.

An adaptive anti-cross conduction algorithm avoids current paths between  $\rm V_{IN}$  and GND during switching transition.

The PM6686 has three different operation modes selectable with SKIP pin: forced PWM (PWM), pulse SKIP (SKIP) and non audible pulse SKIP (NA SKIP). The following paragraphs explain in details the different features of these operation modes.

| Table 9. | Operative mode configurations |

|----------|-------------------------------|

|----------|-------------------------------|

| Control pin | Control pin<br>connected to | Operation mode |

|-------------|-----------------------------|----------------|

|             | VCC                         | PWM            |

| SKIP        | GND                         | SKIP           |

|             | VREF2 or floating           | NA SKIP        |

Doc ID 15281 Rev 4

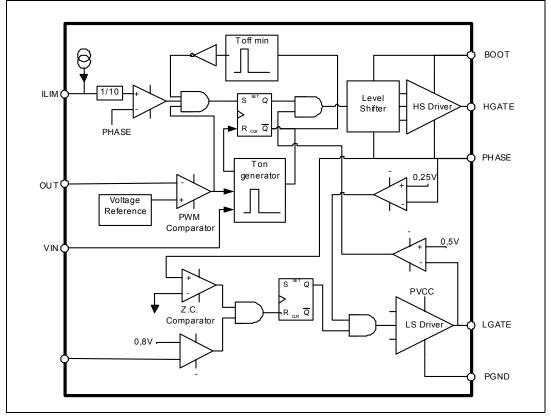

#### 8.1.3 PWM

PWM implements the continuous current mode (CCM). During  $T_{ON}$ , the high-side MOSFET is turned on and the inductor current starts increasing. When the Ton is elapsed the high-side MOSFET is turned off and after a dead time during which neither MOSFET conducts, the low-side MOSFET turns on. The inductor current decreases until these three conditions are verified:

- Output voltage reaches the regulation voltage

- Inductor current is below the current limit

- T<sub>OFFMIN</sub> is elapsed

When these conditions are satisfied a new  $T_{\mbox{ON}}$  starts.

PWM operation mode has a quasi-constant switching frequency, avoiding any audible noise issue and the continuous current mode assures better load transitions despite of a lower efficiency at light loads.

Figure 47. Inductor current and output voltage in PWM mode

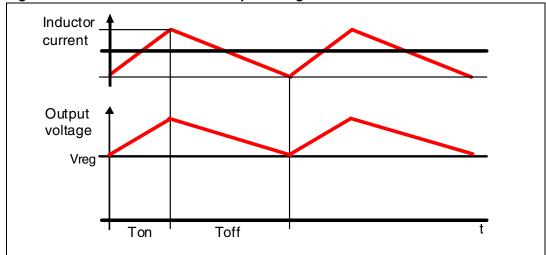

### 8.1.4 SKIP

To improve the efficiency at light load the PM6686 implements pulse skip operation mode. When SKIP pin is tied to GND the inductor current is sensed and if it is equal to zero the synchronous MOSFET is turned off. As a consequence the output capacitor is left floating and the discharge depends only on the current sourced by the load. The new  $T_{ON}$  starts when the output reaches the voltage regulation. As a consequence at light load conditions the switching frequency decreases improving the total efficiency of the converter. Working in discontinuous current mode, the switching and the conduction losses are decreased skipping some cycles.

If the output load is high enough to make the system work in CCM, skip mode is automatically changed in PWM mode.

Figure 48. Inductor current and output voltage in SKIP mode

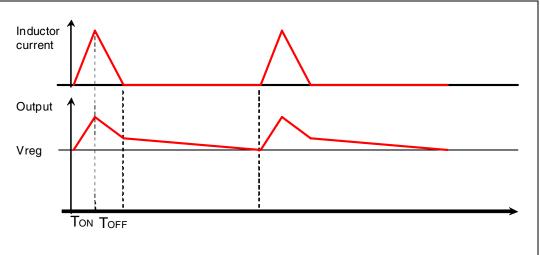

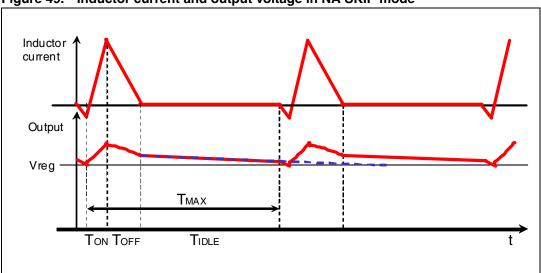

### 8.1.5 Non audible SKIP (NA SKIP)

To avoid audio noise the NA SKIP operation mode can be selected, connecting SKIP pin to VREF2 or leaving it floating. In this condition if a new cycle doesn't start within 30  $\mu$ s typ. from the previous one the PM6686 turns on the low-side MOSFET to discharge the output capacitor. The inductor current goes negative until the output reaches the voltage regulation voltage allowing a new cycle to begin. If the switching frequency is above 33 kHz the device works in SKIP mode.

This operation mode is useful to avoid audio noise but it lowers the efficiency at light loads if it is compared to the SKIP mode.

Figure 49. Inductor current and output voltage in NA SKIP mode

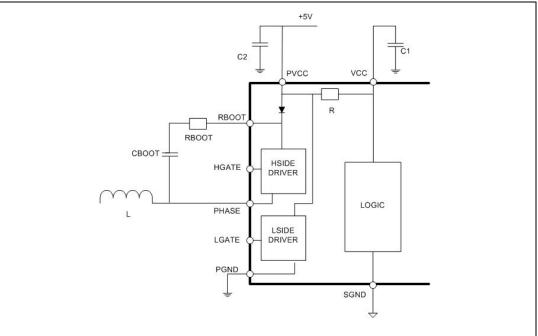

### 8.1.6 Gate drivers and logic supply

The integrated high-current drivers allow the use of different power MOSFET.

high-side driver is supplied with a bootstrap circuit with an integrated bootstrap diode. The BOOT and the PHASE pins work respectively as supply and return rails for the HS driver.

The PVCC pin is the input for the supply of the low-side driver and PGND is the pin used as return rail.

The PM6686 implements an anti-cross conduction protection which prevents high-side and low-side MOSFET from being on at the same time.

The power dissipation of each driver can be calculated as:

#### **Equation 5**

$$\mathsf{P}_{\mathsf{DISS}} = \mathsf{V}_{\mathsf{PVCC}} \cdot \mathsf{Q}_{\mathsf{G}} \cdot \mathsf{f}_{\mathsf{sw}}$$

Where  $V_{PVCC}$  is the voltage applied to PVCC pin (+5 V) and  $f_{SW}$  is the switching frequency.

The power dissipated by the drivers can be reduced lowering the sections switching frequencies and mounting MOSFET with smaller  $Q_G$ .

VCC pin is the input voltage rail to supply the internal logic circuit. This pin is connected internally with a resistor to PVCC. As usual analog supply should be divided by the power supply with a low pass filter to reduce the noise for the analog supply of the logic. Being the resistor integrated it is enough to put a decoupling capacitor near VCC pin to realize the filter with a components count reduction.

#### Figure 50. Internal supply diagram

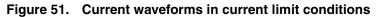

### 8.1.7 Current sensing and current limit

The PM6686 implements a positive valley current limit to protect the application from an overcurrent fault. Each section has an independent current limit setting. A new switching cycle can't start until the inductor current is under the positive current limit threshold. Note that the peak current flowing in the inductor can reach a value greater than the current limit threshold by an amount equal to the inductor ripple current.

The inductor current is sensed during the off time  $T_{OFF}$  by measuring the voltage drop across the low-side MOSFET using the  $R_{DS(on)}$  as a lossless sensing element (PHASE to PGND voltage). The voltage drop is compared to the threshold set with ILIM pin. If ILIM is connected to a voltage higher than VCC-1V the limit is 100mV. A current of 5  $\mu$ A is sourced from the pin ILIM; if a resistor is connected between ILIM and ground the current limit is given by the voltage at the ILIM pin. The device sets the PHASE voltage threshold at 1/10 of the ILIM voltage.

Figure 52. Current limit circuit block diagram

#### Table 10. Current limit configuration

| Control pin    | Control pin voltage                                                            | Threshold SET         |

|----------------|--------------------------------------------------------------------------------|-----------------------|

| II IM1         | V <sub>ILIM</sub> = VCC-1 V                                                    | 100 mV                |

| ILIM1<br>ILIM2 | 0.2 V = V <sub>ILIM</sub> = 2 V<br>V <sub>ILIM</sub> = 5µA * R <sub>ILIM</sub> | V <sub>ILIM</sub> /10 |

A negative current control is also implemented: the low-side MOSFET is forced off when the current exceeds the negative limit. This function prevents the excessive negative inductor current during the PWM operating mode. The threshold is set approximately at the 120% of the positive current limit.

### 8.1.8 Soft-start and soft-end

The two sections have independent enable pins, EN1 and EN2. A not programmable softstart procedure takes place when EN pin rises above 2.4 V typ.

To prevent high input inrush currents, the current limit is increased from 25% to 100% with steps of 25%.

The procedure is not programmable and ends typically in 2.8 ms. The overvoltage protection is always active while the undervoltage protection is enabled typically 20 ms after the beginning of the soft-start procedure.

Driving one EN pin below 0.8 V makes the section perform a soft-end: gate driving signals are pulled low and the output is discharged through an internal MOSFET with  $R_{DS(on)}$  of 28  $\Omega$  typ.

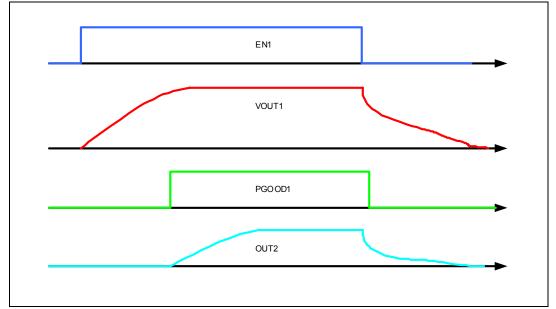

A power up sequence for the switching sections can be selected connecting one EN pin to VREF2.

The section with the EN pin connected to VREF2 begins the soft-start only when the other section is in regulation (its PGOOD is high) and makes a soft-end suddenly when the other section is turned off.

Figure 53. VOUT2 behavior if EN2 is connected to VREF2

To protect the EN1, EN2, EN\_LDO and SKIP pin of the PM6686 an external divider or a series resistor is required, in order to prevent a large inrush current flowing into the device in case the voltage spike is exceeding the recommended operating conditions.

PM6686

## 9 Monitoring and protections

The PM6686 controls its switching output to prevent any damage or uncontrolled working condition.

The device offers also PGOOD signals to monitor the state of each switching output voltage. PGOOD is an open drain output: it is pulled low if the output voltage is below the 90% or above the OVP threshold. of the nominal value.

## 9.1 Overvoltage protection

PM6686 provides a latched overvoltage protection (OVP). If the output voltage rises above the +111% typ. for section 1 and above the +116% typ. for the section 2, a latched OVP protection is activated. The controller tries to pull down the output voltage down to 0 V, working in PWM. The current is limited by the negative current limit. The low-side MOSFET is kept on when the output voltage is about 0 V. This management avoids high negative undervoltage of the output rail that may damage the load.

The protection is latched and this fault is cleared toggling cleared by toggling EN or by driving PVCC<3.979V and then PVCC>4.025V (PVCC Power On Reset).

## 9.2 Undervoltage protection

If during regulation the output voltage droops under the 70% of the nominal value, an undervoltage latched fault is detected. The controller performs a soft-end procedure (see "soft-start and soft-end" paragraph). The undervoltage fault is cleared by toggling EN or by driving PVCC<3.979V and then PVCC>4.025V (PVCC power on reset).

## 9.3 **PVCC** monitor

The device monitors the driver supply voltage at PVCC pin. The switching sections can start operating only if the voltage at PVCC pin is above 4,025 V typ. If PVCC falls below 3,979 V typ., both the switching sections are turned off until the PVCC voltage goes over 4,025 V typ.

| Fault                                           | Condition               | Device reaction                                                                                                                                                                                                  |

|-------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Overvoltage<br>section1 V <sub>OUT</sub> >+111% |                         | Negative current limit protection activated. Low-side MOSFET is turned on when the output voltage is about 0 V. Latched fault, cleared by toggling EN or by driving PVCC<3.979V and then PVCC>4.025V (PVCC POR). |

| Overvoltage section 2                           | V <sub>OUT</sub> >+116% | Negative current limit protection activated. Low-side MOSFET is turned on when the output voltage is about 0 V. Latched fault, cleared by toggling EN or by driving PVCC<3.979V and then PVCC>4.025V (PVCC POR). |

| Undervoltage                                    | V <sub>OUT</sub> <70%   | The controller performs a soft-end. Latched fault cleared by toggling EN or by driving PVCC<3.979V and then PVCC>4.025V (PVCC POR).                                                                              |

| PVCC<br>undervoltage                            | PVCC<3,979 V            | The controller turns off the switching sections. All faults of switching sections are cleared. Not latched fault                                                                                                 |

Table 11. Faults management summary

34/50

## 9.4 Linear regulator section

The PM6686 has an integrated linear regulator (LDO) that can provide an average of 100 mA typ. with a peak current of 270 mA typ. The LDO can be enabled using EN\_LDO pin. If VIN is applied the linear regulator is active even if PVCC is low.

The output voltage can be programmed by LDOREFIN pin. If LDOREFIN pin is tied to ground (GND) the LDO provides a +5 V output voltage. If it is connected to VREF3 pin the LDO regulates 3.3 V. If the voltage at the LDOREFIN pin is between 0.35 V and 2.25 V the LDO generates an output voltage equals to  $2xV_{LDOREFIN}$ .

| LDOREFIN voltage                        | LDO voltage              |

|-----------------------------------------|--------------------------|

| GND                                     | +5 V                     |

| VREF3                                   | +3,3 V                   |

| 0,35 V < V <sub>LDOREFIN</sub> < 2,25 V | 2x V <sub>LDOREFIN</sub> |

Table 12. LDO output voltage configuration

The controller provides a switchover function when LDOREFIN pin is connected to VCC or GND. If the voltage at LDO\_SW pin is high enough, the internal linear regulator is turned off and the LDO pin is connected with an internal MOSFET to the LDO\_SW pin. This feature decreases the power dissipation of the device.

When the switchover function is used the maximum current capability is 200 mA if LDO output is +5 V and 100 mA if the LDO output is +3.3 V.

| V <sub>LDOREFIN</sub>                   | V <sub>BYPLDO_SW</sub> | V <sub>LDO</sub>         | Internal LDO | Switchover resistance |

|-----------------------------------------|------------------------|--------------------------|--------------|-----------------------|

| < 0,35 V                                | > 4,75 V               | +5 V                     | Disabled     | 0.81 Ω                |

| < 0,35 V                                | < 4,55 V               | +5 V                     | Enabled      | -                     |

| > 2.43 V                                | > 3.18 V               | +3,3 V                   | Disabled     | 1.12 Ω                |

| > 2.43 V                                | < 3.05 V               | +3,3 V                   | Enabled      | -                     |

| 0,35 V < V <sub>LDOREFIN</sub> < 2,25 V |                        | 2x V <sub>LDOREFIN</sub> | Enabled      | -                     |

Table 13. LDO switchover management

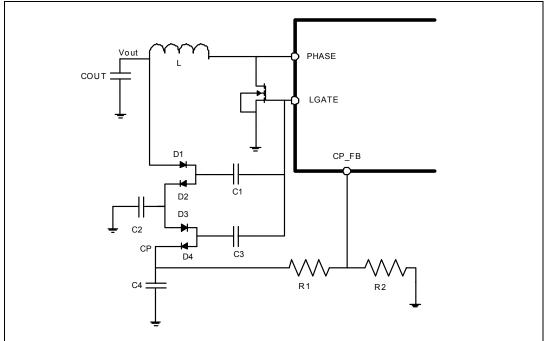

## 9.5 Charge pump

The PM6686 can drive an external charge pump circuit whose typical application schematic is shown in the next figure.

The charge pump works in 4 phases:

- 1. LGATE is low. C1 is charged through the D1a diode at OUT1 voltage minus the diode drop.

- 2. LGATE is driven high and C1 transfers the charge to C2. C2 voltage is OUT1 voltage plus the LGATE voltage minus the voltage drops on D1 and D2.

- 3. LGATE is turned low and C2 shares its charge with C3 thought D3.

- 4. LGATE becomes high and C3 can charge C4 thought diode D4.

Every diode used to transfer charge introduces a voltage drop that decreases the charge pump output voltage.

Repeating this cycle several times makes the charge pump output voltage equals to:

#### **Equation 6**

$$V_{CP} = V_{OUT1} + 2V_{LGATE1} - 4V_{DIODE}$$

Where V<sub>CP</sub> is the charge pump output voltage, V<sub>OUT1</sub> is the output voltage of the switching section 1, V<sub>LGATE1</sub> is the low-side MOSFET gate driving voltage and V<sub>DIODE</sub> is the forward voltage droop of the diodes used in the application.

CP\_FB pin must be connected to the output of the charge pump with a resistor divider; when CP\_FB pin droops below 2 V typ., OUT1 controller starts a NA SKIP cycle to boost the voltage of the charge pump.

Doc ID 15281 Rev 4

The minimum voltage of the charge pump is:

#### **Equation 7**

$$V_{CP\_MIN} = V_{CP\_FB} \cdot \left(1 + \frac{R_1}{R_2}\right)$$

Where  $V_{CP}$  <sub>FB</sub> is the minimum voltage of CP\_FB pin(2V typ.).

In case the charge pump feedback is not used, leave the CP\_FB pin floating or connect the pin to VCC.

## 9.6 Voltage references

The PM6686 provides two voltage references.

The device regulates a 3,3 V voltage reference (VREF3) with ±2% accuracy over temperature. VREF3 can source up to 5 mA. VREF3 voltage is always available if V<sub>IN</sub> is applied. The device allows the enabling of the outputs if VREF3 is above 2,8V typ. and turns off when VREF3 falls under 2,7 V typ.

VREF2 is a + 2 V reference with an accuracy of  $\pm 1\%$  over temperature. It can source up to 50 µA typ. and sink up to 10 µA. VREF2 is adopted as internal reference; this voltage can be used as voltage threshold to set configuration pins (e.g. TON, SKIP pins). VREF2 is enabled when one enable pin (EN1, EN2 or EN\_LDO) is pulled high.

## 9.7 General device fault management

### 9.7.1 Thermal protection

If the internal temperature of the device exceeds typically +150 °C, the controller shuts down immediately all the internal circuitry. Switching sections performs the soft-end management. Toggling EN, EN LDO or cycling VIN resets the latched fault.

# **10** Application information

# 10.1 External components selection

## 10.1.1 Inductor

Once that switching frequency is defined, inductor selection depends on the desired inductor ripple current and load transient performance.

Low inductance means great ripple current and could generate great output noise. On the other hand, low inductor values involve fast load transient response.

A good compromise between the transient response time, the efficiency, the cost and the size is to choose the inductor value in order to maintain the inductor ripple current  $\Delta I_L$  between 20% and 50% of the maximum output current ILOAD (max). The maximum  $\Delta I_L$  occurs at the maximum input voltage. With these considerations, the inductor value can be calculated with the following relationship:

### **Equation 8**

$$L = \frac{V_{IN} - V_{OUT}}{f_{sw} \times \Delta I_L} \times \frac{V_{OUT}}{V_{IN}}$$

Where  $f_{SW}$  is the switching frequency,  $V_{IN}$  is the input voltage,  $V_{OUT}$  is the output voltage and  $\Delta I_L$  is the selected inductor ripple current.

In order to prevent overtemperature working conditions, inductor must be able to provide an RMS current greater than the maximum RMS inductor current  $I_{LRMS}$ :

### **Equation 9**

$$I_{LRMS} = \sqrt{(I_{LOAD}(max))^2 + \frac{(\Delta I_{L}(max))^2}{12}}$$

Where  $\Delta I_{L}(max)$  is the maximum ripple current:

### **Equation 10**

$$\Delta I_{L}(max) = \frac{V_{INmax} - V_{OUT}}{f_{sw} \times L} \times \frac{V_{OUT}}{V_{INmax}}$$

If hard saturation inductors are used, the inductor saturation current should be much greater than the maximum inductor peak current Ipeak:

### **Equation 11**

Ipeak =

$$I_{LOAD}(max) + \frac{\Delta I_L(max)}{2}$$

Using soft-saturation inductors it's possible to choose inductors with saturation current limit nearly to Ipeak.