---

The following document contains information on Cypress products. The document has the series name, product name, and ordering part numbering with the prefix "MB". However, Cypress will offer these products to new and existing customers with the series name, product name, and ordering part number with the prefix "CY".

#### **How to Check the Ordering Part Number**

1. Go to [www.cypress.com/pcn](http://www.cypress.com/pcn).

2. Enter the keyword (for example, ordering part number) in the **SEARCH PCNS** field and click **Apply**.

3. Click the corresponding title from the search results.

4. Download the Affected Parts List file, which has details of all changes

#### **For More Information**

Please contact your local sales office for additional information about Cypress products and solutions.

#### **About Cypress**

Cypress is the leader in advanced embedded system solutions for the world's most innovative automotive, industrial, smart home appliances, consumer electronics and medical products. Cypress' microcontrollers, analog ICs, wireless and USB-based connectivity solutions and reliable, high-performance memories help engineers design differentiated products and get them to market first. Cypress is committed to providing customers with the best support and development resources on the planet enabling them to disrupt markets by creating new product categories in record time. To learn more, go to [www.cypress.com](http://www.cypress.com).

The MB90360E-series, loaded 1 channel FULL-CAN\* interface and Flash ROM, is general-purpose Cypress 16-bit microcontroller designing for automotive and industrial applications. Its main feature is the on-board CAN Interfaces, which conform to Ver 2.0 Part A and Part B, while supporting a very flexible message buffer scheme and so offering more functions than a normal FULL-CAN approach. With the new 0.35  $\mu$ m CMOS technology, Cypress now offers on-chip Flash ROM program memory up to 64 Kbytes.

The power supply (3 V) is supplied to the MCU core from an internal regulator circuit. This creates a major advantage in terms of EMI and power consumption.

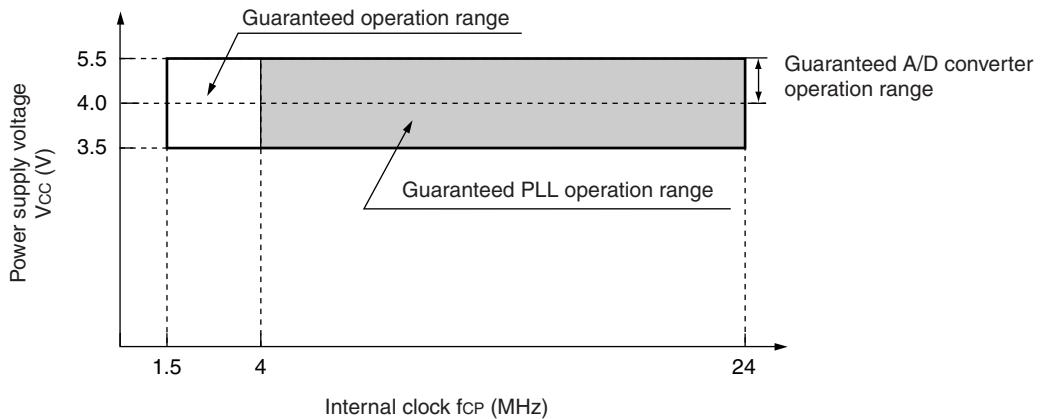

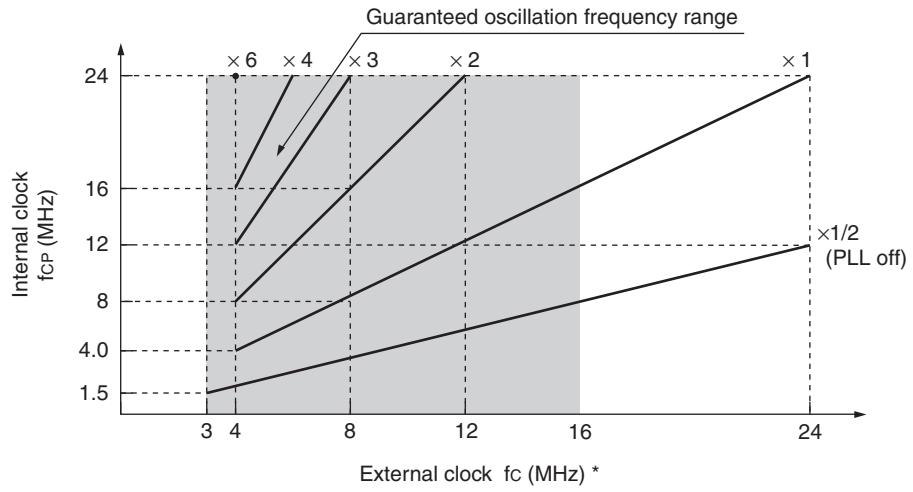

The internal PLL clock frequency multiplier provides an internal 42 ns instruction execution time from an external 4 MHz clock. Also, main and sub clock can be monitored independently using the clock supervisor function.

The unit features a 4-channel input capture unit 1 channel 16-bit free running timer, 2-channel LIN-UART, and 16-channel 8/10-bit A/D converter as the peripheral resource.

\*: Controller Area Network (CAN) - License of Robert Bosch GmbH

## Features

### Clock

- Built-in PLL clock frequency multiplication circuit

- Selection of machine clocks (PLL clocks) is allowed among frequency division by 2 on oscillation clock and multiplication of 1 to 6 times of oscillation clock (for 4 MHz oscillation clock, 4 MHz to 24 MHz)

- Operation by sub clock : internal operating clock frequency: up to 50 kHz (for operating with 100 kHz oscillation clock divided two and devices without S-suffix only) is available

- Minimum execution time of instruction: 42 ns (when operating with 4-MHz oscillation clock and 6-time multiplied PLL clock)

### Clock supervisor (MB90x367x only)

- Main clock or sub clock is monitored independently

### Instruction system best suited to controller

- 16 Mbytes CPU memory space

- 24-bit internal addressing

- Wide choice of data types (bit, byte, word, and long word)

- Wide choice of addressing modes (23 types)

- Enhanced multiply-divide instructions with sign and RETI instructions

- Enhanced high-precision computing with 32-bit accumulator

### Instruction system compatible with high-level language (C language) and multitask

- Employing system stack pointer

- Enhanced various pointer indirect instructions

- Barrel shift instructions

### Increased processing speed

4-byte instruction queue

### Powerful interrupt function

- Powerful 8-level, 34-condition interrupt feature

- Up to 8 channels external interrupts are supported

### Automatic data transfer function independent of CPU

Expanded intelligent I/O service function (EI<sup>2</sup>OS) : up to 16 channels

### Low power consumption (standby) mode

- Sleep mode (a mode that halts CPU operating clock)

- Main timer mode (timebase timer mode that is transferred from main clock mode)

- PLL timer mode (timebase timer mode that is transferred from PLL clock mode)

- Watch mode (a mode that operates sub clock and watch timer only, devices without S-suffix)

- Stop mode (a mode that stops oscillation clock and sub clock)

- CPU blocking operation mode

### Process

CMOS technology

### I/O port

General purpose input/output port (CMOS output) :

- 34 ports (devices without S-suffix)

- 36 ports (devices with S-suffix)

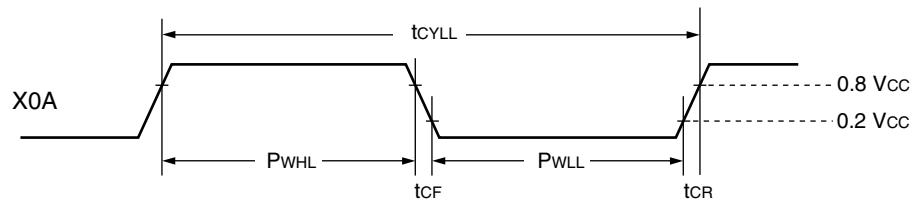

### Sub clock pin (X0A and X1A)

- Provided (used for external oscillation), devices without S-suffix

- Not provided, devices with S-suffix

### Timer

- Timebase timer, watch timer (device without S-suffix) , watchdog timer: 1 channel

- 8/16-bit PPG timer: 8-bit × 4 channels or 16-bit × 2 channels

- 16-bit reload timer: 2 channels

- 16-bit input/output timer

- 16-bit free-run timer: 1 channel (FRT0: ICU 0/1/2/3)

- 16-bit input capture: (ICU) : 4 channels

#### **FULL-CAN interface: 1 channel**

- Compliant with CAN specifications Version 2.0 Part A and B

- 16 message buffers are built in

- CAN wake-up function

#### **LIN-UART: 2 channels**

- Equipped with full-duplex double buffer

- Clock-asynchronous or clock-synchronous serial transmission is available

#### **DTP/External interrupt: up to 8 channels, CAN wakeup: up to 1 channel**

Module for activation of expanded intelligent I/O service (EI<sup>2</sup>OS) and generation of external interrupt by external input

#### **Delay interrupt generator module**

Generates interrupt request for task switching

#### **8/10-bit A/D converter: 16 channels**

- Resolution is selectable between 8-bit and 10-bit

- Activation by external trigger input is allowed

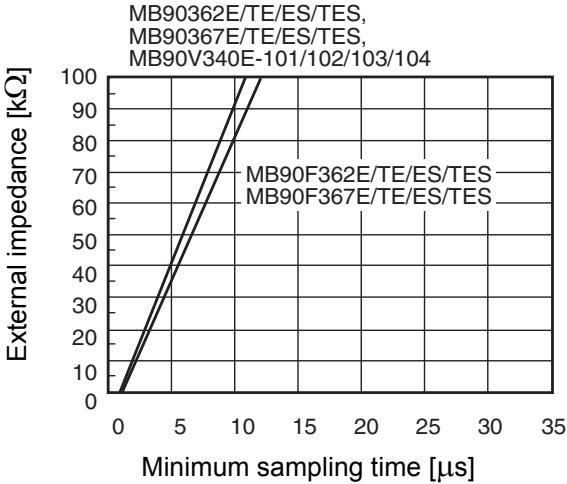

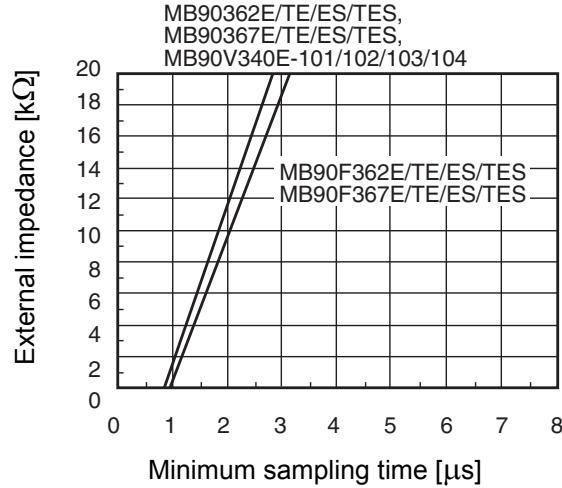

- Conversion time: 3 µs (at 24-MHz machine clock, including sampling time)

#### **Address matching detection (program patch) function**

Address matching detection for 6 address pointers

#### **Low voltage/CPU operation detection reset (devices with T-suffix)**

- Detects low voltage (4.0 V ± 0.3 V) and resets automatically

- Resets automatically when program is runaway and counter is not cleared within interval time (approx. 262 ms: external 4 MHz)

#### **Capable of changing input voltage for port**

Automotive/CMOS-Schmitt input level (initial level is Automotive in single-chip mode)

#### **Flash memory security function**

Protects the content of Flash memory (MB90F362x, MB90F367x only)

## Contents

|                                                                               |           |

|-------------------------------------------------------------------------------|-----------|

| <b>Product Lineup</b> .....                                                   | <b>3</b>  |

| <b>Pin Assignment</b> .....                                                   | <b>6</b>  |

| <b>Pin Description</b> .....                                                  | <b>7</b>  |

| <b>I/O Circuit Type</b> .....                                                 | <b>10</b> |

| <b>Handling Devices</b> .....                                                 | <b>13</b> |

| <b>Block Diagrams</b> .....                                                   | <b>16</b> |

| <b>Memory Map</b> .....                                                       | <b>20</b> |

| <b>I/O Map</b> .....                                                          | <b>21</b> |

| <b>CAN Controllers</b> .....                                                  | <b>28</b> |

| <b>Interrupt Factors, Interrupt Vectors, Interrupt Control Register</b> ..... | <b>35</b> |

| <b>Electrical Characteristics</b> .....                                       | <b>37</b> |

| Absolute Maximum Ratings .....                                                | 37        |

| Recommended Conditions .....                                                  | 39        |

| DC Characteristics .....                                                      | 40        |

| <b>AC Characteristics</b> .....                                               | <b>43</b> |

| <b>Clock Timing</b> .....                                                     | <b>43</b> |

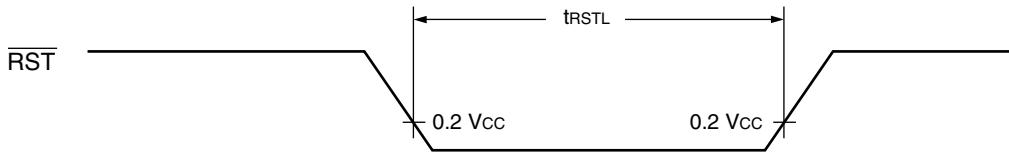

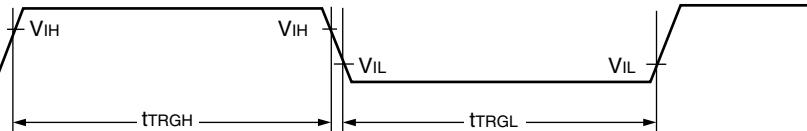

| <b>Reset Standby Input</b> .....                                              | <b>46</b> |

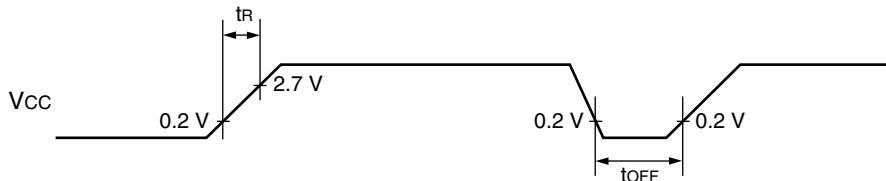

| <b>Power-on Reset</b> .....                                                   | <b>47</b> |

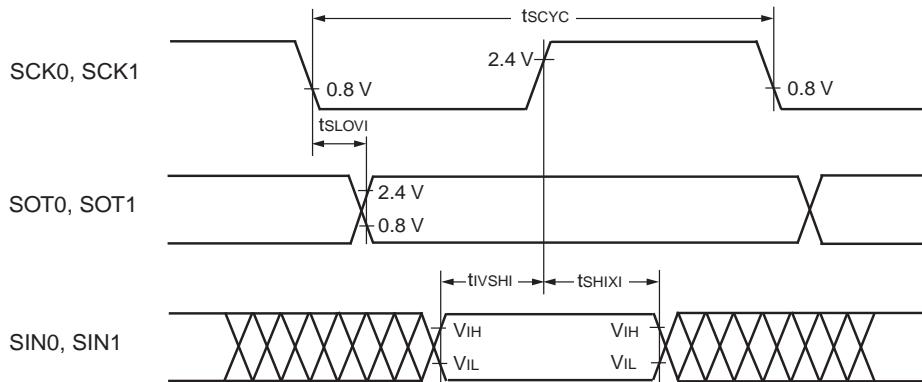

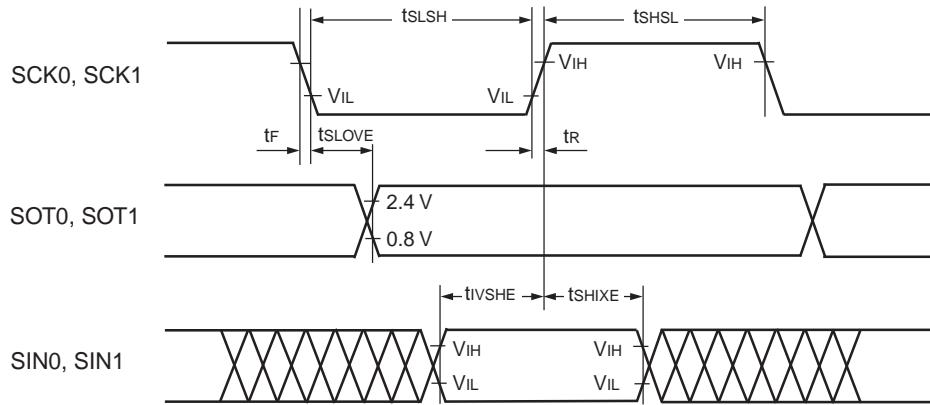

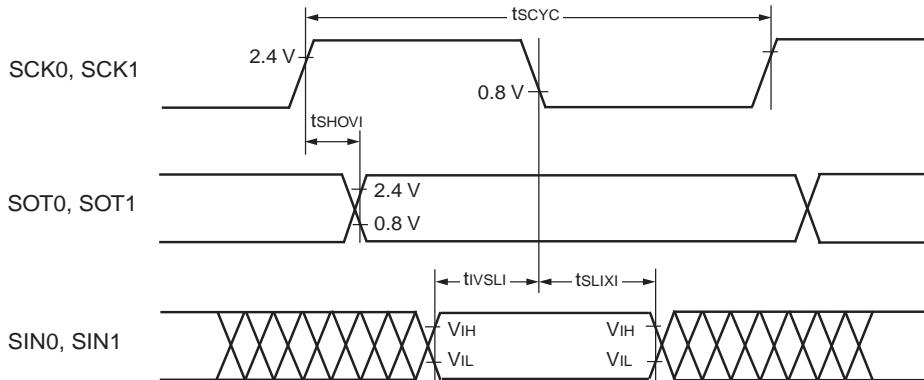

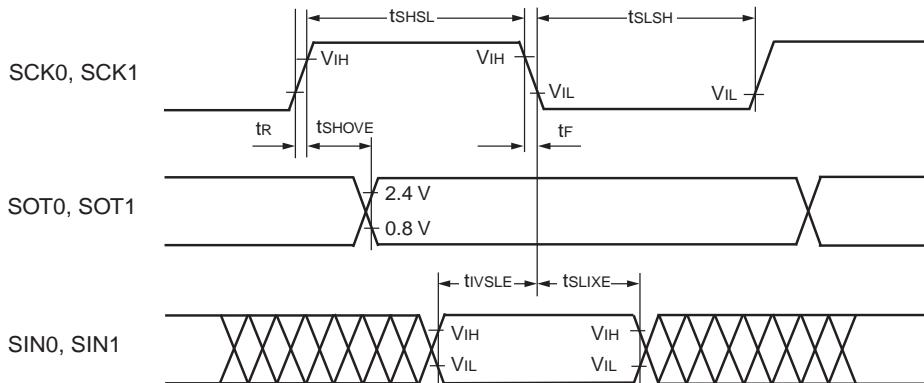

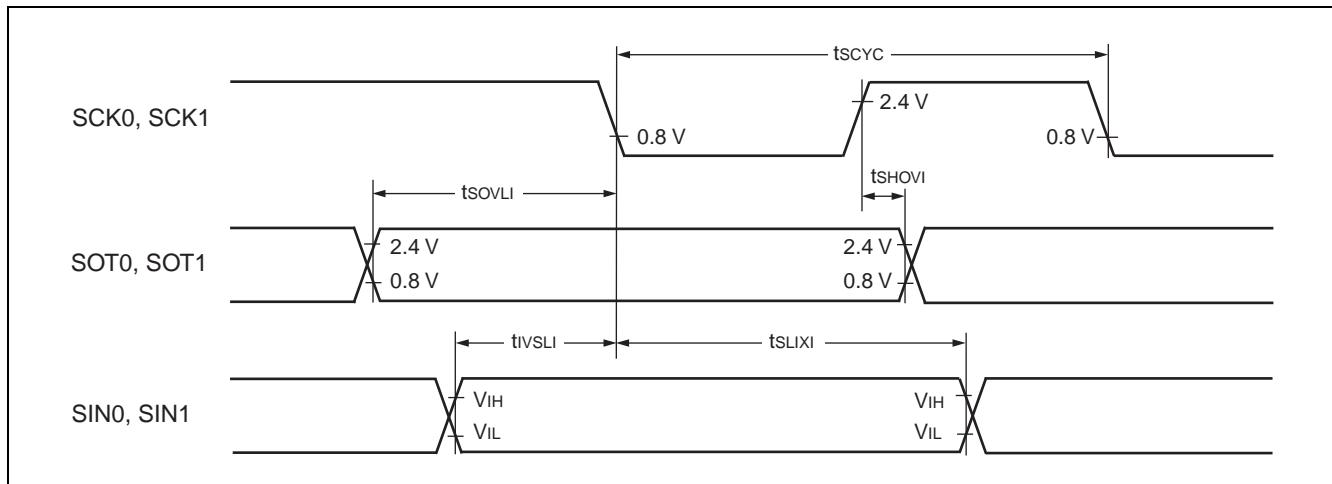

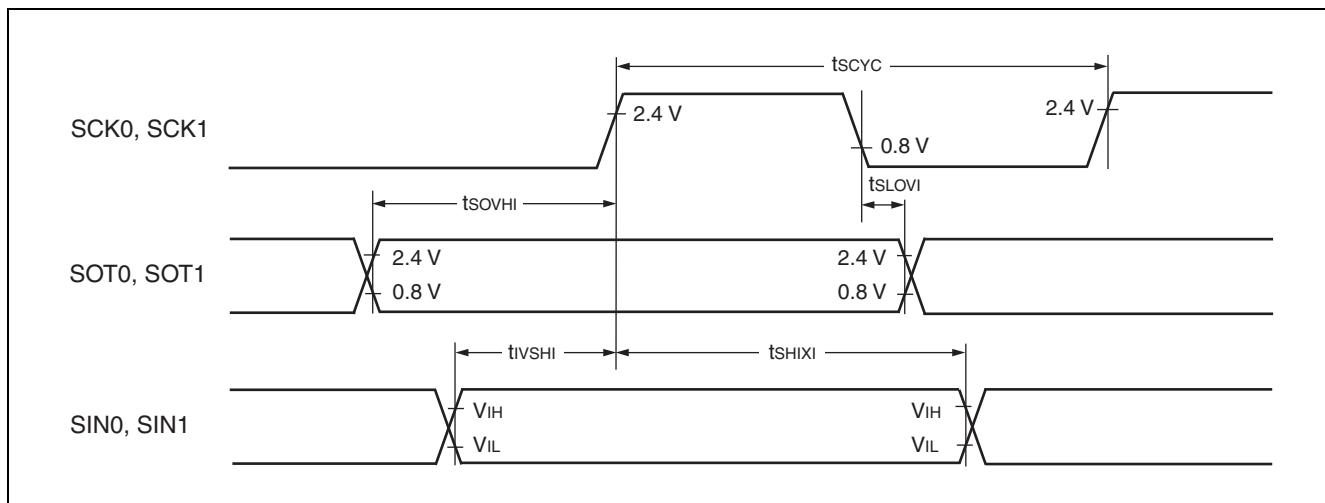

| <b>LIN-UART0/1</b> .....                                                      | <b>48</b> |

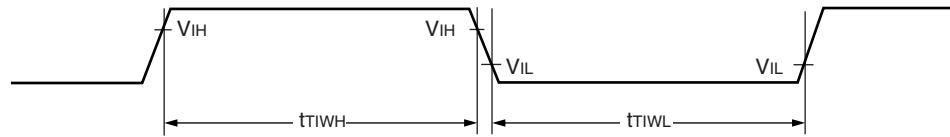

| <b>Trigger Input Timing</b> .....                                             | <b>52</b> |

| <b>Timer Related Resource Input Timing</b> .....                              | <b>53</b> |

| <b>Timer Related Resource Output Timing</b> .....                             | <b>53</b> |

| <b>A/D Converter</b> .....                                                    | <b>54</b> |

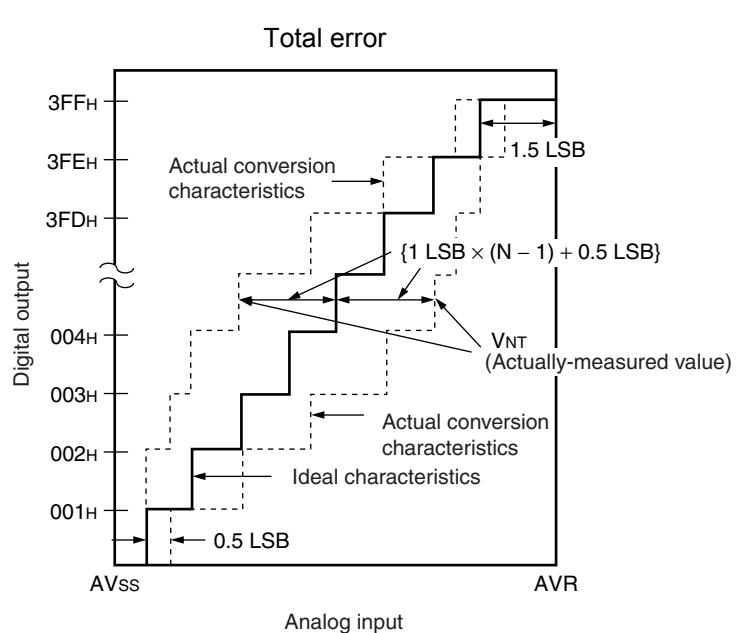

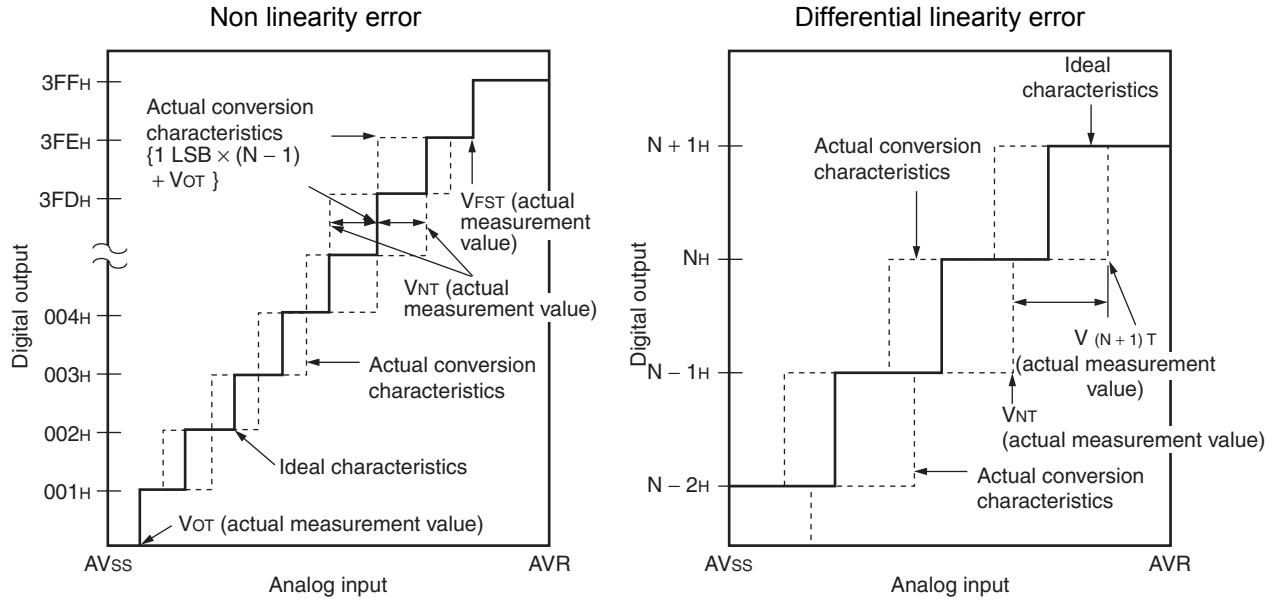

| Definition of A/D Converter Terms .....                                       | 57        |

| Flash Memory Program/Erase Characteristics .....                              | 58        |

| <b>Ordering Information</b> .....                                             | <b>59</b> |

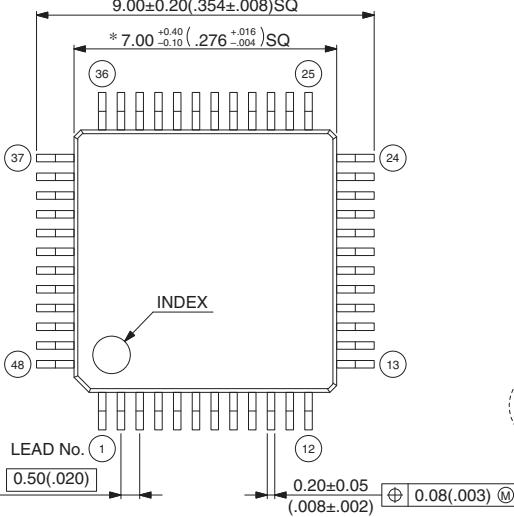

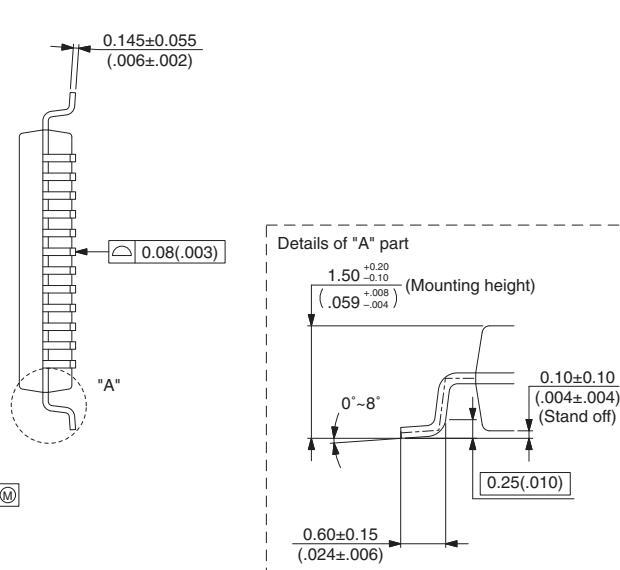

| <b>Package Dimension</b> .....                                                | <b>60</b> |

| <b>Major Changes</b> .....                                                    | <b>61</b> |

## 1. Product Lineup

| Features                                  | MB90362E                                                                                                                                           | MB90362TE | MB90362ES     | MB90362TES | MB90V340E-101      | MB90V340E-102 |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|------------|--------------------|---------------|

| Type                                      | MASK ROM product                                                                                                                                   |           |               |            | Evaluation product |               |

| CPU                                       | F <sup>2</sup> MC-16LX CPU                                                                                                                         |           |               |            |                    |               |

| System clock                              | PLL clock multiplier (× 1, × 2, × 3, × 4, × 6, 1/2 when PLL stops)<br>Minimum instruction execution time: 42 ns (4 MHz oscillation clock, PLL × 6) |           |               |            |                    |               |

| Sub clock pin (X0A, X1A)                  | Yes                                                                                                                                                |           | No            | No         | Yes                |               |

| Clock supervisor                          | No                                                                                                                                                 |           |               |            |                    |               |

| ROM                                       | MASK ROM, 64 Kbytes                                                                                                                                |           |               |            | External           |               |

| RAM capacitance                           | 3 Kbytes                                                                                                                                           |           |               |            | 30 Kbytes          |               |

| CAN interface                             | 1 channel                                                                                                                                          |           |               |            | 3 channels         |               |

| LIN-UART                                  | 2 channels                                                                                                                                         |           |               |            |                    |               |

| Low voltage/CPU operation detection reset | No                                                                                                                                                 | Yes       | No            | Yes        | No                 |               |

| Package                                   | LQFP-48P                                                                                                                                           |           |               |            | PGA-299C           |               |

| Emulator-specific power supply *          | —                                                                                                                                                  |           |               |            | Yes                |               |

| Corresponding evaluation product          | MB90V340E-102                                                                                                                                      |           | MB90V340E-101 |            | —                  |               |

\*: It is setting of Jumper switch (TOOL VCC) when emulator (MB2147-01) is used. Please refer to the Emulator hardware manual for the details.

| Features                                  | MB90F362E                                                                                                                                                | MB90F362TE | MB90F362ES    | MB90F362TES |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|-------------|

| Type                                      | Flash memory product                                                                                                                                     |            |               |             |

| CPU                                       | F <sup>2</sup> MC-16LX CPU                                                                                                                               |            |               |             |

| System clock                              | PLL clock multiplier<br>(× 1, × 2, × 3, × 4, × 6, 1/2 when PLL stops)<br>Minimum instruction execution time: 42 ns<br>(4 MHz oscillation clock, PLL × 6) |            |               |             |

| Sub clock pin (X0A, X1A)                  | Yes                                                                                                                                                      |            |               | No          |

| Clock supervisor                          | No                                                                                                                                                       |            |               |             |

| ROM                                       | Flash memory, 64 Kbytes                                                                                                                                  |            |               |             |

| RAM capacitance                           | 3 Kbytes                                                                                                                                                 |            |               |             |

| CAN interface                             | 1 channel                                                                                                                                                |            |               |             |

| LIN-UART                                  | 2 channels                                                                                                                                               |            |               |             |

| Low voltage/CPU operation detection reset | No                                                                                                                                                       | Yes        | No            | Yes         |

| Package                                   | LQFP-48P                                                                                                                                                 |            |               |             |

| Corresponding evaluation product          | MB90V340E-102                                                                                                                                            |            | MB90V340E-101 |             |

| Features                                  | MB90367E                                                                                                                                      | MB90367TE | MB90367ES     | MB90367TES | MB90V340E-103      | MB90V340E-104 |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|------------|--------------------|---------------|--|--|

| Type                                      | MASK ROM product                                                                                                                              |           |               |            | Evaluation product |               |  |  |

| CPU                                       | F <sup>2</sup> MC-16LX CPU                                                                                                                    |           |               |            |                    |               |  |  |

| System clock                              | PLL clock multiplier (×1, ×2, ×3, ×4, ×6, 1/2 when PLL stops)<br>Minimum instruction execution time: 42 ns (4 MHz oscillation clock, PLL × 6) |           |               |            |                    |               |  |  |

| Sub clock pin (X0A, X1A)                  | Yes                                                                                                                                           |           |               | No         |                    |               |  |  |

| Clock supervisor                          |                                                                                                                                               |           | Yes           |            |                    |               |  |  |

| ROM                                       | MASK ROM, 64 Kbytes                                                                                                                           |           |               |            | External           |               |  |  |

| RAM capacitance                           | 3 Kbytes                                                                                                                                      |           |               |            | 30 Kbytes          |               |  |  |

| CAN interface                             | 1 channel                                                                                                                                     |           |               |            | 3 channels         |               |  |  |

| LIN-UART                                  | 2 channels                                                                                                                                    |           |               |            |                    |               |  |  |

| Low voltage/CPU operation detection reset | No                                                                                                                                            | Yes       | No            | Yes        | No                 |               |  |  |

| Package                                   | LQFP-48P                                                                                                                                      |           |               |            | PGA-299C           |               |  |  |

| Emulator-specific power supply *          | —                                                                                                                                             |           |               |            | Yes                |               |  |  |

| Corresponding EVA product                 | MB90V340E-104                                                                                                                                 |           | MB90V340E-103 |            | —                  |               |  |  |

\*: It is setting of Jumper switch (TOOL VCC) when emulator (MB2147-01) is used. Please refer to the Emulator hardware manual for the details.

| Features                                  | MB90F367E                                                                                                                                           | MB90F367TE | MB90F367ES    | MB90F367TES |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------|-------------|--|--|

| Type                                      | Flash memory product                                                                                                                                |            |               |             |  |  |

| CPU                                       | F <sup>2</sup> MC-16LX CPU                                                                                                                          |            |               |             |  |  |

| System clock                              | PLL clock multiplier<br>(×1, ×2, ×3, ×4, ×6, 1/2 when PLL stops)<br>Minimum instruction execution time: 42 ns<br>(4 MHz oscillation clock, PLL × 6) |            |               |             |  |  |

| Sub clock pin (X0A, X1A)                  | Yes                                                                                                                                                 |            | No            |             |  |  |

| Clock supervisor                          | Yes                                                                                                                                                 |            |               |             |  |  |

| ROM                                       | Flash memory, 64 Kbytes                                                                                                                             |            |               |             |  |  |

| RAM capacitance                           | 3 Kbytes                                                                                                                                            |            |               |             |  |  |

| CAN interface                             | 1 channel                                                                                                                                           |            |               |             |  |  |

| LIN-UART                                  | 2 channels                                                                                                                                          |            |               |             |  |  |

| Low voltage/CPU operation detection reset | No                                                                                                                                                  | Yes        | No            | Yes         |  |  |

| Package                                   | LQFP-48P                                                                                                                                            |            |               |             |  |  |

| Corresponding EVA product                 | MB90V340E-104                                                                                                                                       |            | MB90V340E-103 |             |  |  |

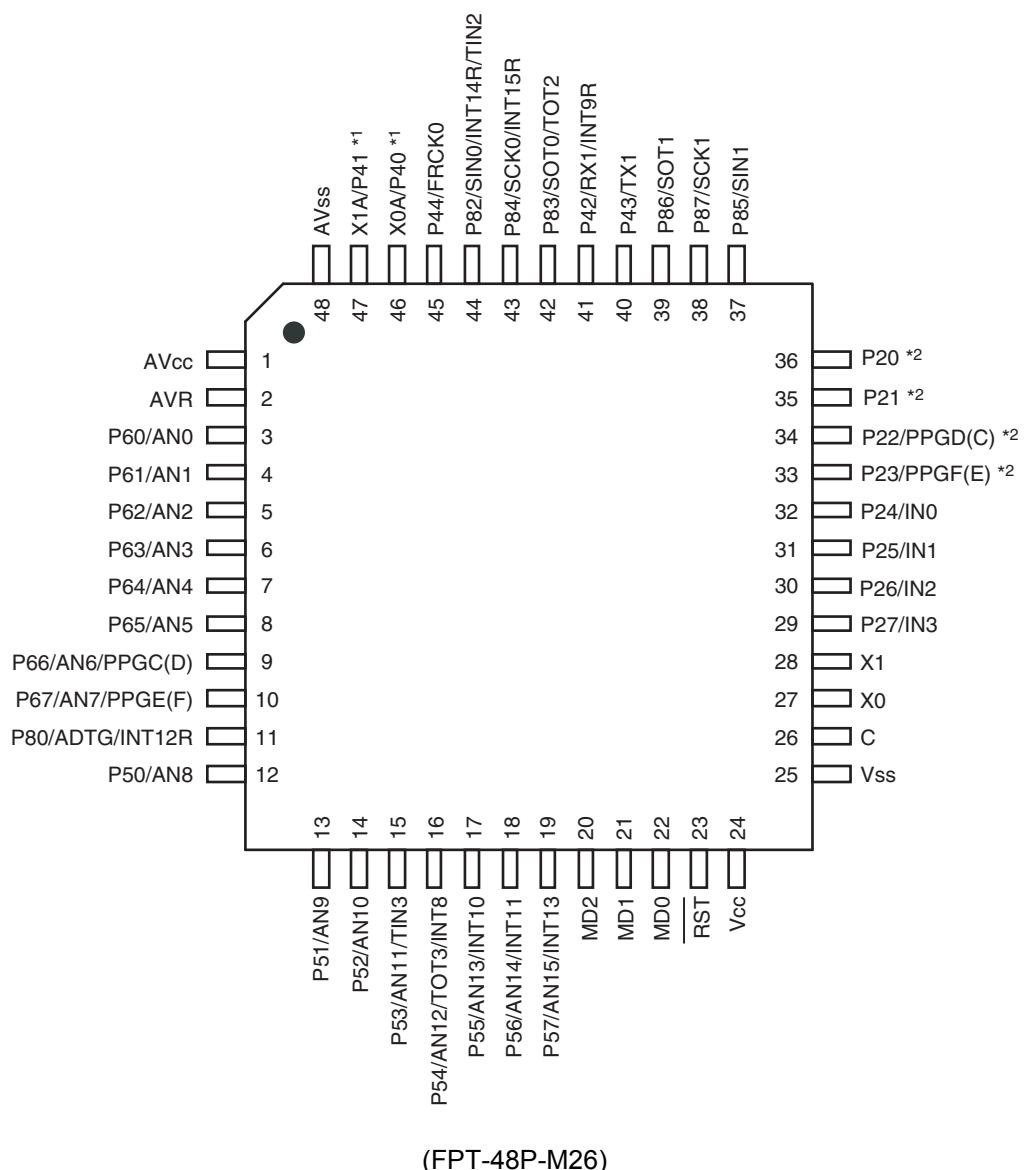

## 2. Pin Assignment

■ MB90F362E/TE/ES/TES, MB90362E/TE/ES/TES, MB90F367E/TE/ES/TES, MB90367E/TE/ES/TES

\*1 : MB90F362E/TE, MB90362E/TE, MB90F367E/TE, MB90367E/TE : X0A, X1A

MB90F362ES/TES, MB90362ES/TES, MB90F367ES/TES, MB90367ES/TES : P40, P41

\*2 : High current output port

### 3. Pin Description

| Pin No.  | Pin name            | I/O circuit type* | Function                                                                                                                     |

|----------|---------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------|

| 1        | AV <sub>CC</sub>    | I                 | V <sub>CC</sub> power input pin for analog circuit.                                                                          |

| 2        | AVR                 | —                 | Power (V <sub>ref+</sub> ) input pin for A/D converter.<br>It should be below V <sub>CC</sub> .                              |

| 3 to 8   | P60 to P65          | H                 | General-purpose I/O port.                                                                                                    |

|          | AN0 to AN5          |                   | Analog input pins for A/D converter.                                                                                         |

| 9, 10    | P66, P67            | H                 | General-purpose I/O port.                                                                                                    |

|          | AN6, AN7            |                   | Analog input pins for A/D converter.                                                                                         |

|          | PPGC (D), PPGE (F)  |                   | Output pins for PPG.                                                                                                         |

| 11       | P80                 | F                 | General-purpose I/O port.                                                                                                    |

|          | ADTG                |                   | Trigger input pin for A/D converter.                                                                                         |

|          | INT12R              |                   | External interrupt request input pin for INT12.                                                                              |

| 12 to 14 | P50 to P52          | H                 | General-purpose I/O port (P50 has different I/O circuit type from MB90V340E).                                                |

|          | AN8 to AN10         |                   | Analog input pins for A/D converter.                                                                                         |

| 15       | P53                 | H                 | General-purpose I/O port.                                                                                                    |

|          | AN11                |                   | Analog input pin for A/D converter.                                                                                          |

|          | TIN3                |                   | Event input pin for reload timer 3.                                                                                          |

| 16       | P54                 | H                 | General-purpose I/O port.                                                                                                    |

|          | AN12                |                   | Analog input pin for A/D converter.                                                                                          |

|          | TOT3                |                   | Output pin for reload timer 3                                                                                                |

|          | INT8                |                   | External interrupt request input pin for INT8.                                                                               |

| 17 to 19 | P55 to P57          | H                 | General-purpose I/O port.                                                                                                    |

|          | AN13 to AN15        |                   | Analog input pins for A/D converter.                                                                                         |

|          | INT10, INT11, INT13 |                   | External interrupt request input pins for INT10, INT11, INT13.                                                               |

| 20       | MD2                 | D                 | Input pin for operation mode specification.                                                                                  |

| 21, 22   | MD1, MD0            | C                 | Input pins for operation mode specification.                                                                                 |

| 23       | <u>RST</u>          | E                 | Reset input pin.                                                                                                             |

| 24       | V <sub>CC</sub>     | —                 | Power input pin (3.5 V to 5.5 V).                                                                                            |

| 25       | V <sub>SS</sub>     | —                 | Power input pin (0 V).                                                                                                       |

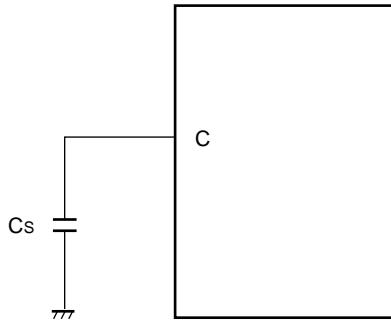

| 26       | C                   | I                 | Power supply stabilization capacitor pin. It should be connected to a higher than or equal to 0.1 $\mu$ F ceramic condenser. |

(Continued)

| Pin No.  | Pin name              | I/O circuit type* | Function                                                                                                                                                                     |

|----------|-----------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

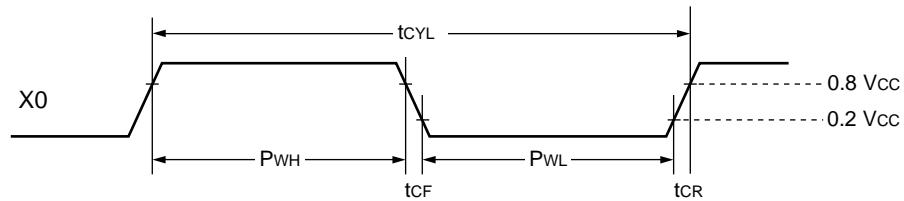

| 27       | X0                    | A                 | Oscillation input pin.                                                                                                                                                       |

| 28       | X1                    |                   | Oscillation output pin.                                                                                                                                                      |

| 29 to 32 | P27 to P24            | G                 | General-purpose I/O port.<br>The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.                              |

|          | IN3 to IN0            |                   | Event input pins for input capture 0 to 3.                                                                                                                                   |

|          | P23, P22              |                   | General-purpose I/O port.<br>The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.<br>High current output port. |

| 33, 34   | PPGF (E),<br>PPGD (C) | J                 | Output pins for PPG.                                                                                                                                                         |

|          | P21, P20              |                   | General-purpose I/O port.<br>The register can be set to select whether to use a pull-up resistor. This function is enabled in single-chip mode.<br>High current output port. |

| 37       | P85                   | K                 | General-purpose I/O port.                                                                                                                                                    |

|          | SIN1                  |                   | Serial data input pin for LIN-UART1.                                                                                                                                         |

| 38       | P87                   | F                 | General-purpose I/O port.                                                                                                                                                    |

|          | SCK1                  |                   | Clock I/O pin for LIN-UART1.                                                                                                                                                 |

| 39       | P86                   | F                 | General-purpose I/O port.                                                                                                                                                    |

|          | SOT1                  |                   | Serial data output pin for LIN-UART1.                                                                                                                                        |

| 40       | P43                   | F                 | General-purpose I/O port.                                                                                                                                                    |

|          | TX1                   |                   | TX output pin for CAN1 interface.                                                                                                                                            |

| 41       | P42                   | F                 | General-purpose I/O port.                                                                                                                                                    |

|          | RX1                   |                   | RX input pin for CAN1 interface.                                                                                                                                             |

|          | INT9R                 |                   | External interrupt request input pin for INT9 (Sub) .                                                                                                                        |

| 42       | P83                   | F                 | General-purpose I/O port.                                                                                                                                                    |

|          | SOT0                  |                   | Serial data output pin for LIN-UART0.                                                                                                                                        |

|          | TOT2                  |                   | Output pin for reload timer 2.                                                                                                                                               |

| 43       | P84                   | F                 | General-purpose I/O port.                                                                                                                                                    |

|          | SCK0                  |                   | Clock I/O pin for LIN-UART0.                                                                                                                                                 |

|          | INT15R                |                   | External interrupt request input pin for INT15.                                                                                                                              |

*(Continued)*

*(Continued)*

| Pin No. | Pin name         | I/O circuit type* | Function                                                                                  |

|---------|------------------|-------------------|-------------------------------------------------------------------------------------------|

| 44      | P82              | K                 | General-purpose I/O port.                                                                 |

|         | SIN0             |                   | Serial data input pin for LIN-UART0.                                                      |

|         | INT14R           |                   | External interrupt request input pin for INT14.                                           |

|         | TIN2             |                   | Event input pin for reload timer 2.                                                       |

| 45      | P44              | F                 | General-purpose I/O port<br>(Different I/O circuit type from MB90V340E) .                 |

|         | FRCK0            |                   | Free-run timer 0 clock pin.                                                               |

| 46, 47  | P40, P41         | F                 | General-purpose I/O port<br>(Devices with S-suffix and MB90V340E-101/103 only) .          |

|         | X0A, X1A         | B                 | Oscillation pins for sub clock<br>(Devices without S-suffix and MB90V340E-102/104 only) . |

| 48      | AV <sub>SS</sub> | I                 | V <sub>SS</sub> power input pin for analog circuit.                                       |

\*: For the I/O circuit type, refer to "[I/O Circuit Type](#)"

#### 4. I/O Circuit Type

| Type | Circuit                                                                             | Remarks                                                                                                                                                                                                                      |

|------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

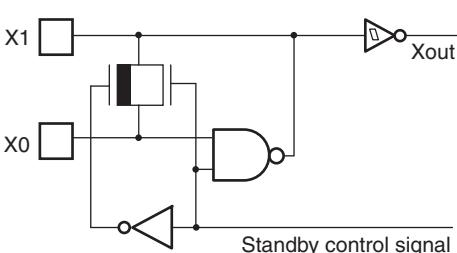

| A    |    | Oscillation circuit:<br>High-speed oscillation feedback resistor = approx. 1 MΩ                                                                                                                                              |

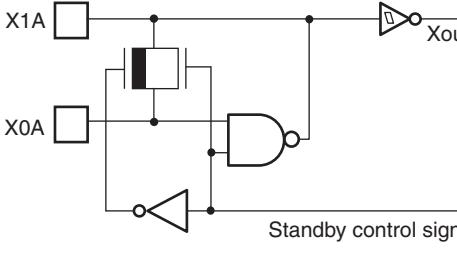

| B    |   | Oscillation circuit:<br>Low-speed oscillation feedback resistor = approx. 10 MΩ                                                                                                                                              |

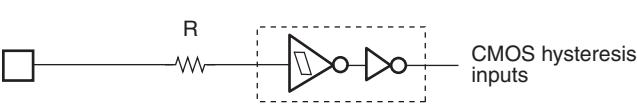

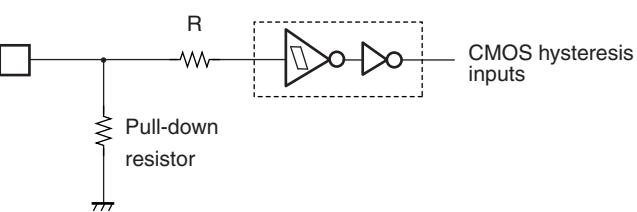

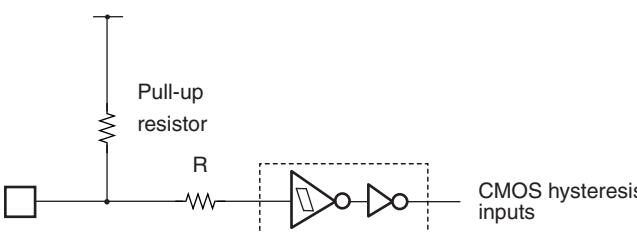

| C    |  | <ul style="list-style-type: none"> <li>■ MASK ROM product: CMOS hysteresis input pin</li> <li>■ Flash memory product: CMOS input pin</li> </ul>                                                                              |

| D    |  | <ul style="list-style-type: none"> <li>■ MASK ROM product: CMOS hysteresis input pin</li> <li>■ Flash memory product: <ul style="list-style-type: none"> <li>- CMOS input pin</li> <li>- No Pull-down</li> </ul> </li> </ul> |

| E    |  | CMOS hysteresis input pin                                                                                                                                                                                                    |

*(Continued)*

| Type | Circuit                                                                                                                                                                                                                            | Remarks                                                                                                                                                                                                                                                         |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

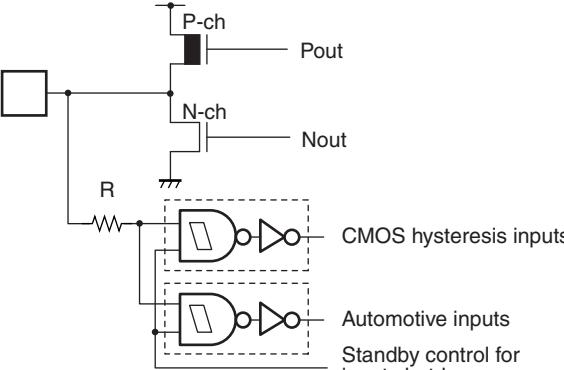

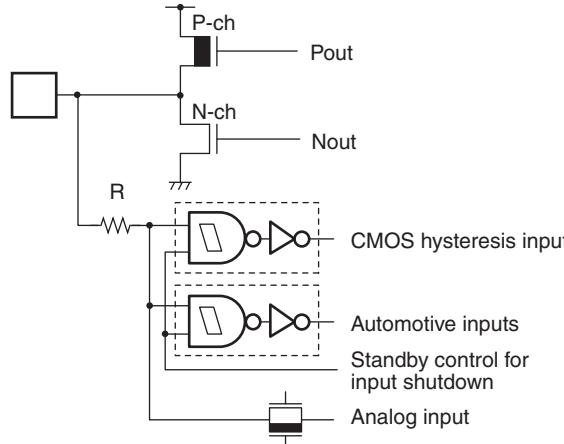

| F    |  <p>CMOS hysteresis inputs</p> <p>Automotive inputs</p> <p>Standby control for input shutdown</p>                                                 | <ul style="list-style-type: none"> <li>■ CMOS level output</li> <li>■ CMOS hysteresis inputs (With the standby-time input shutdown function)</li> <li>■ Automotive input (With the standby-time input shutdown function)</li> </ul>                             |

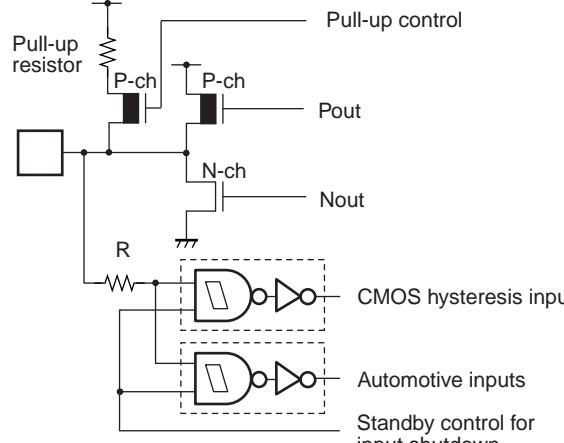

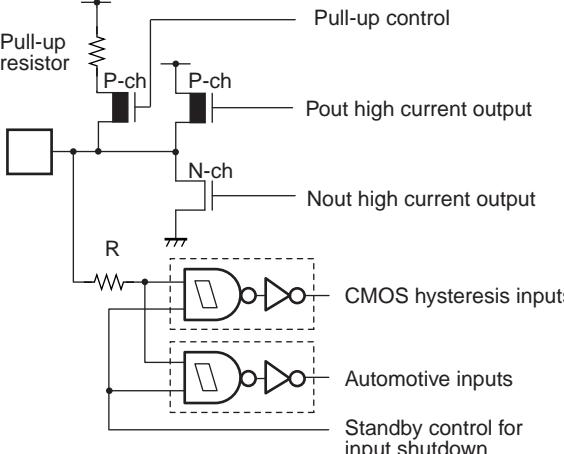

| G    |  <p>Pull-up resistor</p> <p>Pull-up control</p> <p>CMOS hysteresis inputs</p> <p>Automotive inputs</p> <p>Standby control for input shutdown</p> | <ul style="list-style-type: none"> <li>■ CMOS level output</li> <li>■ CMOS hysteresis inputs (With the standby-time input shutdown function)</li> <li>■ Automotive input (With the standby-time input shutdown function)</li> </ul>                             |

| H    |  <p>CMOS hysteresis inputs</p> <p>Automotive inputs</p> <p>Standby control for input shutdown</p> <p>Analog input</p>                           | <ul style="list-style-type: none"> <li>■ CMOS level output</li> <li>■ CMOS hysteresis inputs (With the standby-time input shutdown function)</li> <li>■ Automotive input (With the standby-time input shutdown function)</li> <li>■ A/D analog input</li> </ul> |

*(Continued)*

*(Continued)*

| Type | Circuit                                                                             | Remarks                                                                                                                                                                                                                             |

|------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

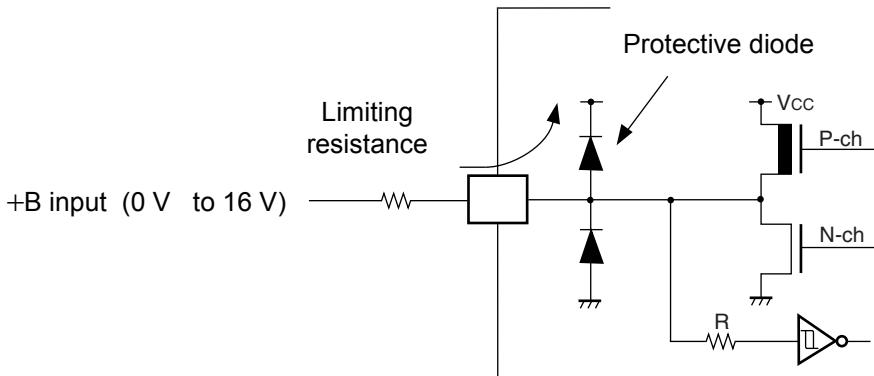

| I    |    | Protection circuit for power supply input                                                                                                                                                                                           |

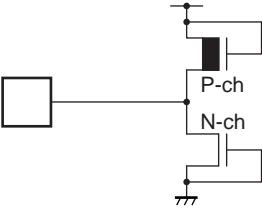

| J    |   | <ul style="list-style-type: none"> <li>■ CMOS level output</li> <li>■ CMOS hysteresis inputs (With the standby-time input shutdown function)</li> <li>■ Automotive input (With the standby-time input shutdown function)</li> </ul> |

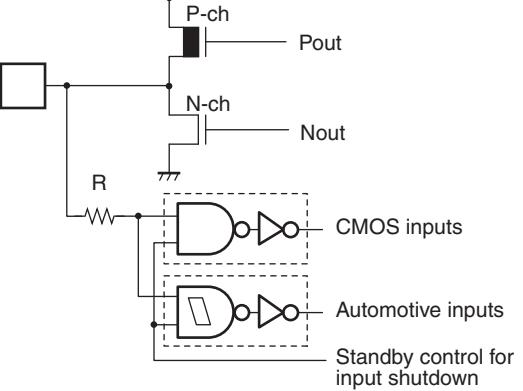

| K    |  | <ul style="list-style-type: none"> <li>■ CMOS level output</li> <li>■ CMOS input (With standby-time input shutdown function)</li> <li>■ Automotive input (With standby-time input shutdown function)</li> </ul>                     |

## 5. Handling Devices

### 1. Preventing latch-up

CMOS IC chips may suffer latch-up under the following conditions:

- A voltage higher than  $V_{CC}$  pin or lower than  $V_{SS}$  pin is applied to an input or output pin.

- A voltage higher than the rated voltage is applied between  $V_{CC}$  pin and  $V_{SS}$  pin.

- The  $AV_{CC}$  power supply is applied before the  $V_{CC}$  voltage.

Latch-up may increase the power supply current drastically, causing thermal damage to the device.

Use meticulous care not to exceed the rating.

For the same reason, also be careful not to let the analog power-supply voltage ( $AV_{CC}$ , AVR) exceed the digital power-supply voltage.

### 2. Treatment of unused pins

Leaving unused input pins open may result in permanent damage of the device due to misbehavior or latch-up. Therefore, they must be pulled up or pulled down through resistors. In this case, those resistors should be more than  $2\text{ k}\Omega$ .

Unused bidirectional pins should be set to the output state and can be left open, or the input state with the above described connection.

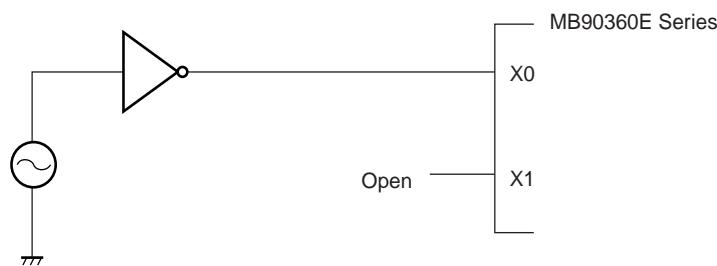

### 3. Using external clock

To use external clock, drive the X0 pin and leave X1 pin open.

### 4. Precautions for when not using a sub clock signal

If you do not connect pins X0A and X1A to an oscillator, use pull-down handling on the X0A pin and leave the X1A pin open.

### 5. Notes on during operation of PLL clock mode

On this microcontroller, if in case the crystal oscillator breaks off or an external reference clock input stops while the PLL clock mode is selected, a self-oscillator circuit contained in the PLL may continue its operation at its self-running frequency. However, Fujitsu will not guarantee results of operations if such failure occurs.

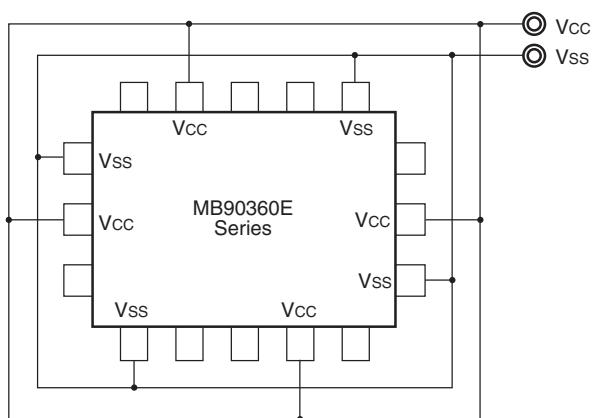

### 6. Power supply pins ( $V_{CC}/V_{SS}$ )

- If there are multiple  $V_{CC}$  and  $V_{SS}$  pins, from the point of view of device design, pins to be of the same potential are connected the inside of the device to prevent malfunction such as latch-up.

- To reduce unnecessary radiation, prevent malfunctioning of the strobe signal due to the rise of ground level, and observe the standard for total output current, be sure to connect the  $V_{CC}$  and  $V_{SS}$  pins to the power supply and ground externally.

- Connect  $V_{CC}$  and  $V_{SS}$  pins to the device from the current supply source at a low impedance.

- As a measure against power supply noise, connect a capacitor of about  $0.1 \mu\text{F}$  as a bypass capacitor between  $V_{CC}$  pin and  $V_{SS}$  pin in the vicinity of  $V_{CC}$  and  $V_{SS}$  pins of the device.

## 7. Pull-up/down resistors

The MB90360E Series does not support internal pull-up/down resistors (Port 2: built-in pull-up resistors) . Use external components where needed.

## 8. Crystal oscillator circuit

Noises around  $X0$  or  $X1$  pin may be possible causes of abnormal operations. Make sure to provide bypass capacitors via shortest distance from  $X0$ ,  $X1$  pins, crystal oscillator (or ceramic resonator) and ground lines, and make sure, to the utmost effort, that lines of oscillation circuit do not cross the lines of other circuits.

It is highly recommended to provide a printed circuit board artwork surrounding  $X0$  and  $X1$  pins with a ground area for stabilizing the operation. Please ask the crystal maker to evaluate the oscillational characteristics of the crystal and this device.

## 9. Turning-on sequence of power supply to A/D converter and analog inputs

Make sure to turn on the A/D converter power supply ( $AV_{CC}$  and  $AV_R$ ) and analog inputs (AN0 to AN15) after turning-on the digital power supply ( $V_{CC}$ ).

Turn-off the digital power after turning off the A/D converter power supply and analog inputs. In this case, make sure that the voltage does not exceed  $AV_{RH}$  or  $AV_{CC}$  (turning on/off the analog and digital power supplies simultaneously is acceptable).

## 10. Connection of unused pins of A/D converter if A/D converter is not used

Connect unused pins of A/D converter to  $AV_{CC} = V_{CC}$ ,  $AV_{SS} = AVR = V_{SS}$ .

## 11. Notes on energization

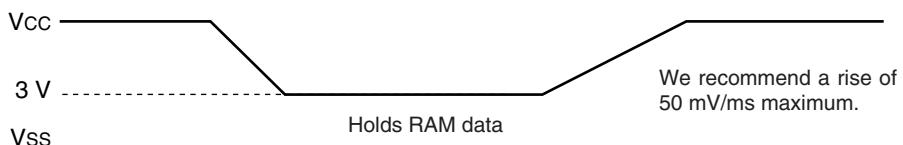

To prevent the internal regulator circuit from malfunctioning, set the voltage rise time during energization at  $50 \mu\text{s}$  or more (0.2 V to 2.7 V) .

## 12. Stabilization of power supply voltage

A sudden change in the power supply voltage may cause the device to malfunction even within the specified  $V_{CC}$  power supply voltage operating guarantee range. Therefore, the  $V_{CC}$  power supply voltage should be stabilized.

For reference, the power supply voltage should be controlled so that  $V_{CC}$  ripple variations (peak-to-peak value) at commercial frequencies (50 Hz/60 Hz) fall below 10% of the standard  $V_{CC}$  power supply voltage and the coefficient of transient fluctuation does not exceed 0.1 V/ms at instantaneous power switching.

## 13. Initialization

In the device, there are internal registers which are initialized only by a power-on reset. To initialize these registers, turn on the power again.

## 14. Notes on using CAN function

To use CAN function, please set '1' to DIRECT bit of CAN direct mode register (CDMR) .

If DIRECT bit is set to '0' (initial value) , wait states will be performed when accessing CAN registers.

Note: Please refer to Hardware Manual of "MB90360E series for detail of CAN Direct Mode Register".

## 15. Flash security function

The security bit is located in the area of the Flash memory.

If protection code  $01_H$  is written in the security bit, the Flash memory is in the protected state by security.

Therefore, please do not write  $01_H$  in this address if you do not use the security function.

Please refer to following table for the address of the security bit.

|                                                                                                              | Flash memory size               | Address for security bit |

|--------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------|

| MB90F362E<br>MB90F362ES<br>MB90F362TE<br>MB90F362TES<br>MB90F367E<br>MB90F367ES<br>MB90F367TE<br>MB90F367TES | Embedded 512 Kbits Flash Memory | $FF0001_H$               |

## 16. Correspondence with $T_A = +105^\circ C$ or more

There is a restriction of reliability if the product is used exceeding  $T_A = +105^\circ C$ .

Contact the sales or support representative.

It is ensured to write/erase data to the Flash memory between  $T_A = -40^\circ C$  and  $+105^\circ C$ .

## 17. Serial communication

There is a possibility to receive wrong data due to the noise or other causes on the serial communication.

Therefore, design a printed circuit board so as to avoid noise.

Retransmit the data if an error occurs because of applying the checksum to the last data in consideration of receiving wrong data due to the noise.

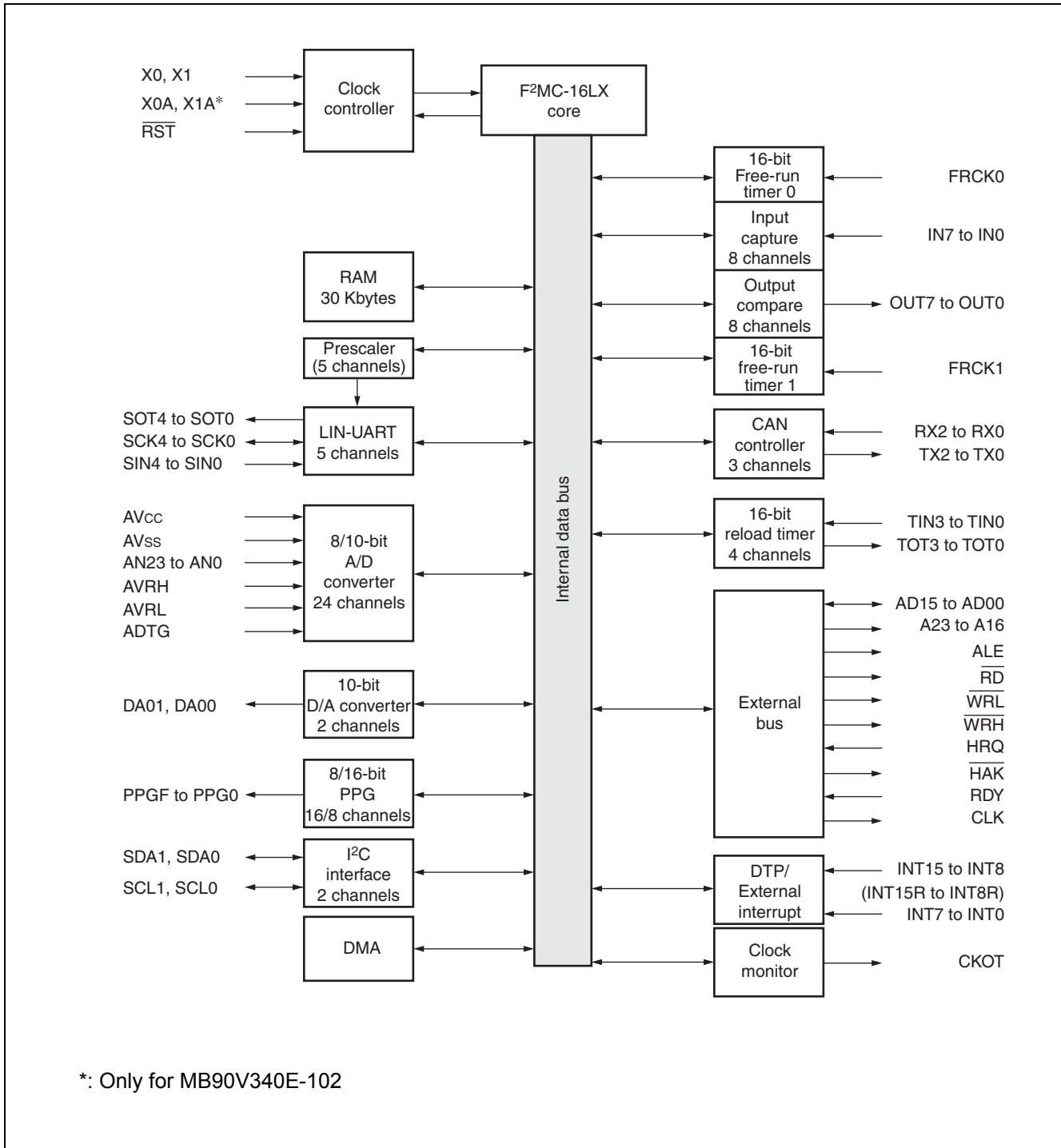

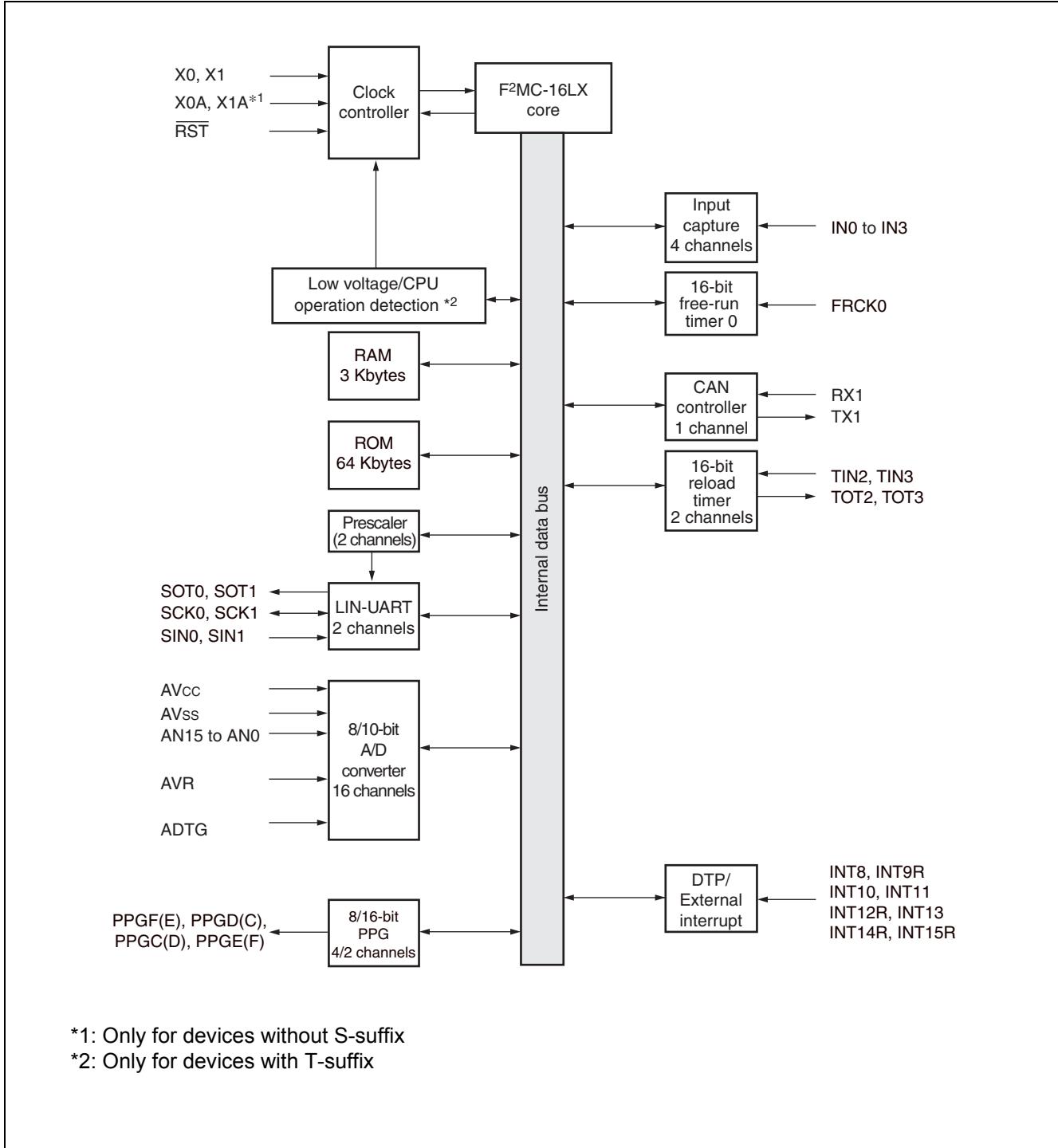

## 6. Block Diagrams

### ■ MB90V340E-101/102

\*: Only for MB90V340E-102

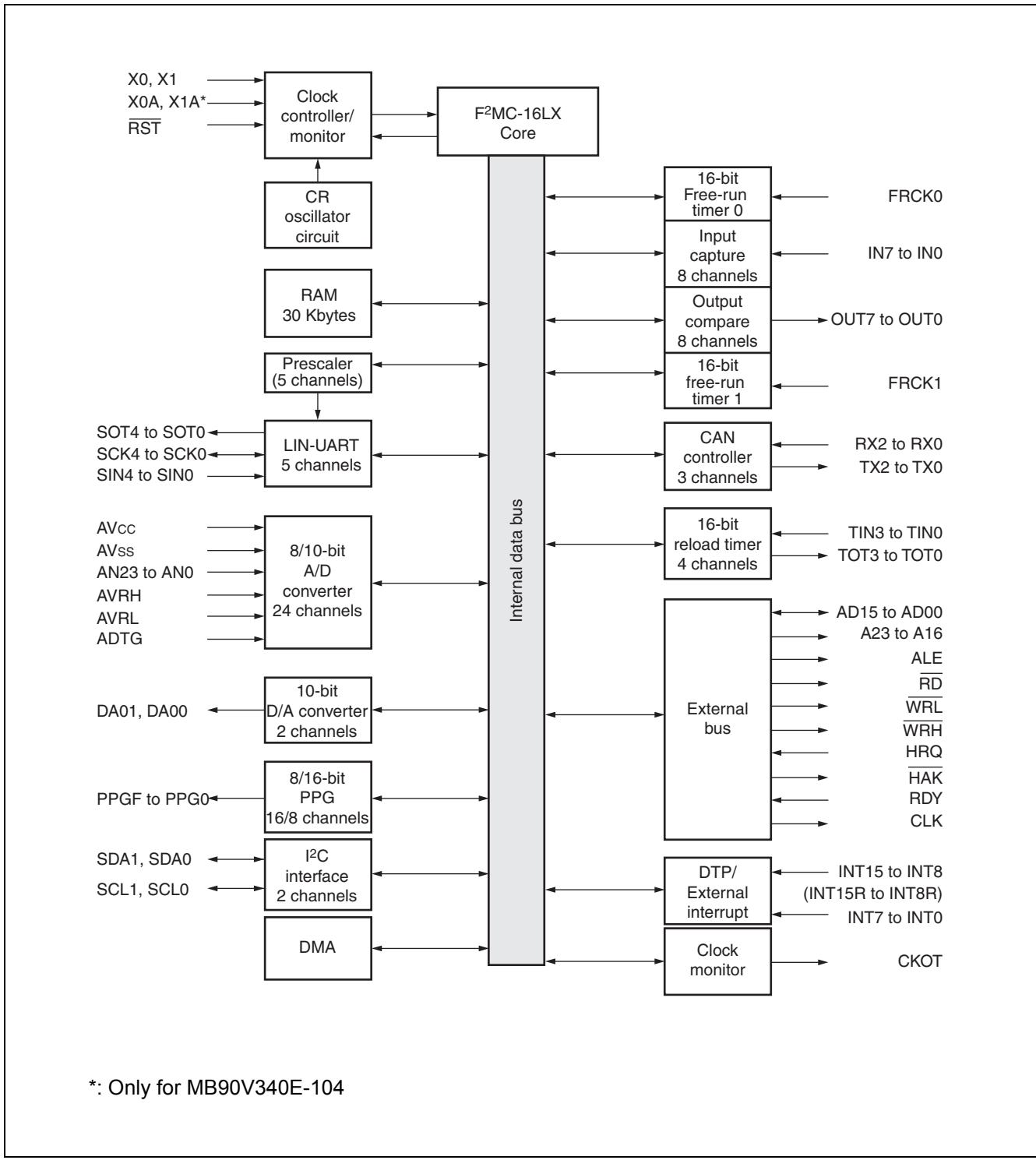

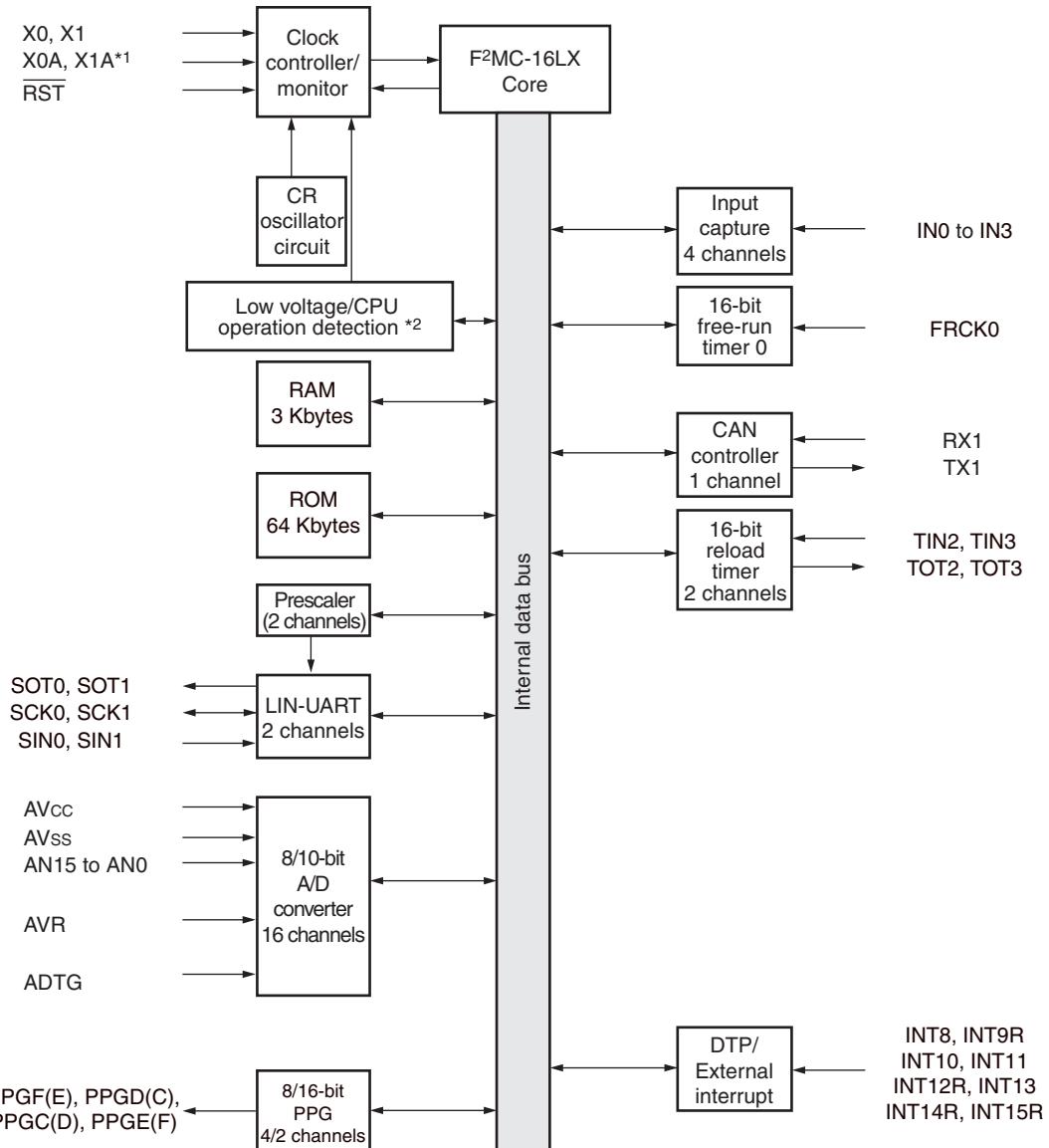

**■ MB90V340E-103/104**

## ■ MB90F362E/TE/ES/TES, MB90362E/TE/ES/TES

\*1: Only for devices without S-suffix

\*2: Only for devices with T-suffix

**■ MB90F367E/TE/ES/TES, MB90367E/TE/ES/TES**

\*1: Only for devices without S-suffix

\*2: Only for devices with T-suffix

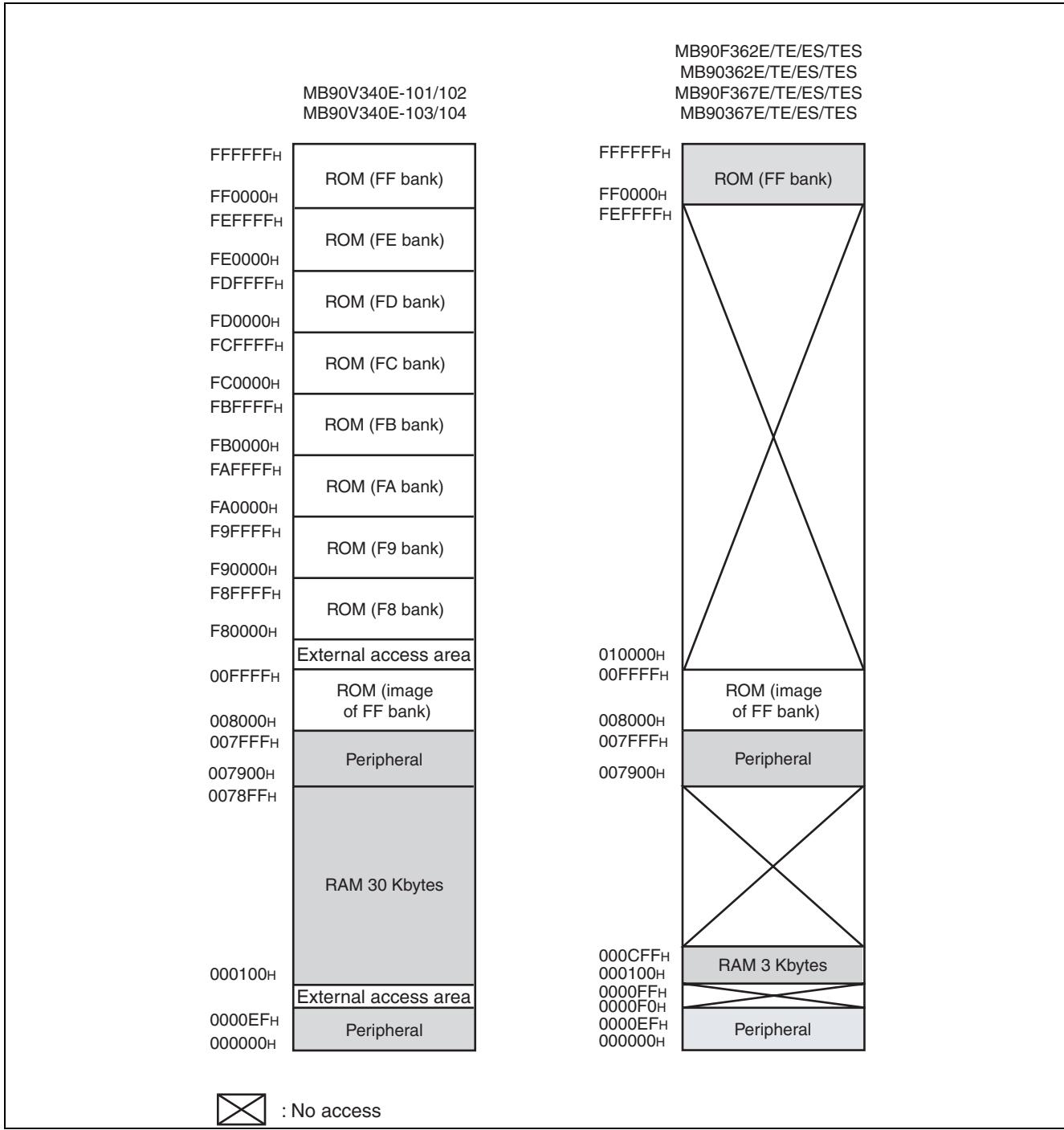

## 7. Memory Map

Note: The high-order portion of bank 00 gives the image of the FF bank ROM to make the small model of the C compiler effective. Since the low-order 16 bits are the same, the table in ROM can be referred without using the far specification in the pointer declaration.

For example, an attempt to access  $00C000_H$  practically accesses the value at  $FFC000_H$  in ROM.

The ROM area in bank FF exceeds 32 Kbytes, and its entire image cannot be shown in bank 00.

The image between  $FF8000_H$  and  $FFFFFH$  is visible in bank 00, while the image between  $FF0000_H$  and  $FF7FFF_H$  is visible only in bank FF.

## 8. I/O Map

| Address                                    | Register                            | Abbrevia-tion | Access | Resource name | Initial value         |

|--------------------------------------------|-------------------------------------|---------------|--------|---------------|-----------------------|

| 000000 <sub>H</sub> ,00 0001 <sub>H</sub>  |                                     | Reserved      |        |               |                       |

| 000002 <sub>H</sub>                        | Port 2 Data Register                | PDR2          | R/W    | Port 2        | XXXXXXXX <sub>B</sub> |

| 000003 <sub>H</sub>                        |                                     | Reserved      |        |               |                       |

| 000004 <sub>H</sub>                        | Port 4 Data Register                | PDR4          | R/W    | Port 4        | XXXXXXXX <sub>B</sub> |

| 000005 <sub>H</sub>                        | Port 5 Data Register                | PDR5          | R/W    | Port 5        | XXXXXXXX <sub>B</sub> |

| 000006 <sub>H</sub>                        | Port 6 Data Register                | PDR6          | R/W    | Port 6        | XXXXXXXX <sub>B</sub> |

| 000007 <sub>H</sub>                        |                                     | Reserved      |        |               |                       |

| 000008 <sub>H</sub>                        | Port 8 Data Register                | PDR8          | R/W    | Port 8        | XXXXXXXX <sub>B</sub> |

| 000009 <sub>H</sub> ,00 000A <sub>H</sub>  |                                     | Reserved      |        |               |                       |

| 00000B <sub>H</sub>                        | Port 5 Analog Input Enable Register | ADER5         | R/W    | Port 5, A/D   | 11111111 <sub>B</sub> |

| 00000C <sub>H</sub>                        | Port 6 Analog Input Enable Register | ADER6         | R/W    | Port 6, A/D   | 11111111 <sub>B</sub> |

| 00000D <sub>H</sub>                        |                                     | Reserved      |        |               |                       |

| 00000E <sub>H</sub>                        | Input Level Select Register         | ILSR0         | R/W    | Ports         | XXXX0XXX <sub>B</sub> |

| 00000F <sub>H</sub>                        | Input Level Select Register         | ILSR1         | R/W    | Ports         | XXXXXXXX <sub>B</sub> |

| 000010 <sub>H</sub> ,00 0011 <sub>H</sub>  |                                     | Reserved      |        |               |                       |

| 000012 <sub>H</sub>                        | Port 2 Direction Register           | DDR2          | R/W    | Port 2        | 00000000 <sub>B</sub> |

| 000013 <sub>H</sub>                        |                                     | Reserved      |        |               |                       |

| 000014 <sub>H</sub>                        | Port 4 Direction Register           | DDR4          | R/W    | Port 4        | XXX00000 <sub>B</sub> |

| 000015 <sub>H</sub>                        | Port 5 Direction Register           | DDR5          | R/W    | Port 5        | 00000000 <sub>B</sub> |

| 000016 <sub>H</sub>                        | Port 6 Direction Register           | DDR6          | R/W    | Port 6        | 00000000 <sub>B</sub> |

| 000017 <sub>H</sub>                        |                                     | Reserved      |        |               |                       |

| 000018 <sub>H</sub>                        | Port 8 Direction Register           | DDR8          | R/W    | Port 8        | 000000X0 <sub>B</sub> |

| 000019 <sub>H</sub>                        |                                     | Reserved      |        |               |                       |

| 00001A <sub>H</sub>                        | Port A Direction Register           | DDRA          | W      | Port A        | XXX00XXX <sub>B</sub> |

| 00001B <sub>H</sub> to 00001D <sub>H</sub> |                                     | Reserved      |        |               |                       |

| 00001E <sub>H</sub>                        | Port 2 Pull-up Control Register     | PUCR2         | R/W    | Port 2        | 00000000 <sub>B</sub> |

| 00001F <sub>H</sub>                        |                                     | Reserved      |        |               |                       |

| Address                                    | Register                                  | Abbreviation | Access    | Resource name             | Initial value         |

|--------------------------------------------|-------------------------------------------|--------------|-----------|---------------------------|-----------------------|

| 000020 <sub>H</sub>                        | Serial Mode Register 0                    | SMR0         | W, R/W    | LIN-UART0                 | 00000000 <sub>B</sub> |

| 000021 <sub>H</sub>                        | Serial Control Register 0                 | SCR0         | W, R/W    |                           | 00000000 <sub>B</sub> |

| 000022 <sub>H</sub>                        | Reception/Transmission Data Register 0    | RDR0/TDR0    | R/W       |                           | 00000000 <sub>B</sub> |

| 000023 <sub>H</sub>                        | Serial Status Register 0                  | SSR0         | R, R/W    |                           | 00001000 <sub>B</sub> |

| 000024 <sub>H</sub>                        | Extended Communication Control Register 0 | ECCR0        | R, W, R/W |                           | 000000XX <sub>B</sub> |

| 000025 <sub>H</sub>                        | Extended Status/Control Register 0        | ESCR0        | R/W       |                           | 00000100 <sub>B</sub> |

| 000026 <sub>H</sub>                        | Baud Rate Generator Register 00           | BGR00        | R/W, R    |                           | 00000000 <sub>B</sub> |

| 000027 <sub>H</sub>                        | Baud Rate Generator Register 01           | BGR01        | R/W, R    |                           | 00000000 <sub>B</sub> |

| 000028 <sub>H</sub>                        | Serial Mode Register 1                    | SMR1         | W, R/W    | LIN-UART1                 | 00000000 <sub>B</sub> |

| 000029 <sub>H</sub>                        | Serial Control Register 1                 | SCR1         | W, R/W    |                           | 00000000 <sub>B</sub> |

| 00002A <sub>H</sub>                        | Reception/Transmission Data Register 1    | RDR1/TDR1    | R/W       |                           | 00000000 <sub>B</sub> |

| 00002B <sub>H</sub>                        | Serial Status Register 1                  | SSR1         | R, R/W    |                           | 00001000 <sub>B</sub> |

| 00002C <sub>H</sub>                        | Extended Communication Control Register 1 | ECCR1        | R, W, R/W |                           | 000000XX <sub>B</sub> |

| 00002D <sub>H</sub>                        | Extended Status/Control Register 1        | ESCR1        | R/W       |                           | 00000100 <sub>B</sub> |

| 00002E <sub>H</sub>                        | Baud Rate Generator Register 10           | BGR10        | R/W, R    |                           | 00000000 <sub>B</sub> |

| 00002F <sub>H</sub>                        | Baud Rate Generator Register 11           | BGR11        | R/W, R    |                           | 00000000 <sub>B</sub> |

| 000030 <sub>H</sub> to 00003A <sub>H</sub> | Reserved                                  |              |           |                           |                       |

| 00003B <sub>H</sub>                        | Address Detect Control Register 1         | PACSR1       | R/W       | Address Match Detection 1 | 00000000 <sub>B</sub> |

| 00003C <sub>H</sub> to 000047 <sub>H</sub> | Reserved                                  |              |           |                           |                       |

| 000048 <sub>H</sub>                        | PPG C Operation Mode Control Register     | PPGCC        | W, R/W    | 16-bit PPG C/D            | 0X000XX1 <sub>B</sub> |

| 000049 <sub>H</sub>                        | PPG D Operation Mode Control Register     | PPGCD        | W, R/W    |                           | 0X000001 <sub>B</sub> |

| 00004A <sub>H</sub>                        | PPG C/PPG D Count Clock Select Register   | PPGCD        | R/W       |                           | 000000X0 <sub>B</sub> |

| 00004B <sub>H</sub>                        | Reserved                                  |              |           |                           |                       |

| 00004C <sub>H</sub>                        | PPG E Operation Mode Control Register     | PPGCE        | W, R/W    | 16-bit PPG E/F            | 0X000XX1 <sub>B</sub> |

| 00004D <sub>H</sub>                        | PPG F Operation Mode Control Register     | PPGCF        | W, R/W    |                           | 0X000001 <sub>B</sub> |

| 00004E <sub>H</sub>                        | PPG E/PPG F Count Clock Select Register   | PPGEF        | R/W       |                           | 000000X0 <sub>B</sub> |

| 00004F <sub>H</sub>                        | Reserved                                  |              |           |                           |                       |

*(Continued)*

| Address                                    | Register                                                                   | Abbreviation | Access | Resource name                             | Initial value         |

|--------------------------------------------|----------------------------------------------------------------------------|--------------|--------|-------------------------------------------|-----------------------|

| 000050 <sub>H</sub>                        | Input Capture Control Status 0/1                                           | ICS01        | R/W    | Input Capture 0/1                         | 00000000 <sub>B</sub> |

| 000051 <sub>H</sub>                        | Input Capture Edge 0/1                                                     | ICE01        | R/W, R |                                           | XXX0X0XX <sub>B</sub> |

| 000052 <sub>H</sub>                        | Input Capture Control Status 2/3                                           | ICS23        | R/W    | Input Capture 2/3                         | 00000000 <sub>B</sub> |

| 000053 <sub>H</sub>                        | Input Capture Edge 2/3                                                     | ICE23        | R      |                                           | XXXXXXX <sub>B</sub>  |

| 000054 <sub>H</sub> to 000063 <sub>H</sub> | Reserved                                                                   |              |        |                                           |                       |

| 000064 <sub>H</sub>                        | Timer Control Status 2                                                     | TMCSR2       | R/W    | 16-bit Reload Timer 2                     | 00000000 <sub>B</sub> |

| 000065 <sub>H</sub>                        | Timer Control Status 2                                                     | TMCSR2       | R/W    |                                           | XXXX0000 <sub>B</sub> |

| 000066 <sub>H</sub>                        | Timer Control Status 3                                                     | TMCSR3       | R/W    | 16-bit Reload Timer 3                     | 00000000 <sub>B</sub> |

| 000067 <sub>H</sub>                        | Timer Control Status 3                                                     | TMCSR3       | R/W    |                                           | XXXX0000 <sub>B</sub> |

| 000068 <sub>H</sub>                        | A/D Control Status 0                                                       | ADCS0        | R/W    | A/D Converter                             | 000XXX0 <sub>B</sub>  |

| 000069 <sub>H</sub>                        | A/D Control Status 1                                                       | ADCS1        | R/W, W |                                           | 000000X <sub>B</sub>  |

| 00006A <sub>H</sub>                        | A/D Data 0                                                                 | ADCR0        | R      |                                           | 00000000 <sub>B</sub> |

| 00006B <sub>H</sub>                        | A/D Data 1                                                                 | ADCR1        | R      |                                           | XXXXXX00 <sub>B</sub> |

| 00006C <sub>H</sub>                        | ADC Setting 0                                                              | ADSR0        | R/W    |                                           | 00000000 <sub>B</sub> |

| 00006D <sub>H</sub>                        | ADC Setting 1                                                              | ADSR1        | R/W    |                                           | 00000000 <sub>B</sub> |

| 00006E <sub>H</sub>                        | Low Voltage/CPU Operation Detection Reset Control Register                 | LVRC         | R/W, W | Low voltage/CPU operation detection reset | 00111000 <sub>B</sub> |

| 00006F <sub>H</sub>                        | ROM Mirror Function Select                                                 | ROMM         | W      | ROM Mirror                                | XXXXXXX1 <sub>B</sub> |

| 000070 <sub>H</sub> to 00007F <sub>H</sub> | Reserved                                                                   |              |        |                                           |                       |

| 000080 <sub>H</sub> to 00008F <sub>H</sub> | Reserved for CAN Interface 1. Refer to " <a href="#">CAN Controllers</a> " |              |        |                                           |                       |

| 000090 <sub>H</sub> to 00009D <sub>H</sub> | Reserved                                                                   |              |        |                                           |                       |

| 00009E <sub>H</sub>                        | Address Detect Control Register 0                                          | PACSR0       | R/W    | Address Match Detection 0                 | 00000000 <sub>B</sub> |

| 00009F <sub>H</sub>                        | Delayed Interrupt/Release Register                                         | DIRR         | R/W    | Delayed Interrupt generation module       | XXXXXX00 <sub>B</sub> |

| 0000A0 <sub>H</sub>                        | Low-power Consumption Mode Control Register                                | LPMCR        | W, R/W | Low-Power consumption Control Circuit     | 00011000 <sub>B</sub> |

| 0000A1 <sub>H</sub>                        | Clock Selection Register                                                   | CKSCR        | R, R/W | Low-Power consumption Control Circuit     | 11111100 <sub>B</sub> |

*(Continued)*

| Address                                    | Register                                                            | Abbreviation | Access | Resource name        | Initial value         |  |

|--------------------------------------------|---------------------------------------------------------------------|--------------|--------|----------------------|-----------------------|--|

| 0000A2 <sub>H</sub> to 0000A7 <sub>H</sub> | Reserved                                                            |              |        |                      |                       |  |

| 0000A8 <sub>H</sub>                        | Watchdog Control Register                                           | WDTC         | R, W   | Watchdog Timer       | XXXXX111 <sub>B</sub> |  |

| 0000A9 <sub>H</sub>                        | Timebase Timer Control Register                                     | TBTC         | W, R/W | Timebase Timer       | 1XX00100 <sub>B</sub> |  |

| 0000AA <sub>H</sub>                        | Watch Timer Control register                                        | WTC          | R, R/W | Watch Timer          | 1X001000 <sub>B</sub> |  |

| 0000AB <sub>H</sub> to 0000AD <sub>H</sub> | Reserved                                                            |              |        |                      |                       |  |

| 0000AE <sub>H</sub>                        | Flash Control Status<br>(Flash Devices only.<br>Otherwise reserved) | FMCS         | R, R/W | Flash Memory         | 000X0000 <sub>B</sub> |  |

| 0000AF <sub>H</sub>                        | Reserved                                                            |              |        |                      |                       |  |

| 0000B0 <sub>H</sub>                        | Interrupt Control Register 00                                       | ICR00        | W, R/W | Interrupt Control    | 00000111 <sub>B</sub> |  |

| 0000B1 <sub>H</sub>                        | Interrupt Control Register 01                                       | ICR01        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000B2 <sub>H</sub>                        | Interrupt Control Register 02                                       | ICR02        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000B3 <sub>H</sub>                        | Interrupt Control Register 03                                       | ICR03        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000B4 <sub>H</sub>                        | Interrupt Control Register 04                                       | ICR04        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000B5 <sub>H</sub>                        | Interrupt Control Register 05                                       | ICR05        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000B6 <sub>H</sub>                        | Interrupt Control Register 06                                       | ICR06        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000B7 <sub>H</sub>                        | Interrupt Control Register 07                                       | ICR07        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000B8 <sub>H</sub>                        | Interrupt Control Register 08                                       | ICR08        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000B9 <sub>H</sub>                        | Interrupt Control Register 09                                       | ICR09        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000BA <sub>H</sub>                        | Interrupt Control Register 10                                       | ICR10        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000BB <sub>H</sub>                        | Interrupt Control Register 11                                       | ICR11        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000BC <sub>H</sub>                        | Interrupt Control Register 12                                       | ICR12        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000BD <sub>H</sub>                        | Interrupt Control Register 13                                       | ICR13        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000BE <sub>H</sub>                        | Interrupt Control Register 14                                       | ICR14        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000BF <sub>H</sub>                        | Interrupt Control Register 15                                       | ICR15        | W, R/W |                      | 00000111 <sub>B</sub> |  |

| 0000C0 <sub>H</sub> to 0000C9 <sub>H</sub> | Reserved                                                            |              |        |                      |                       |  |

| 0000CA <sub>H</sub>                        | External Interrupt Enable 1                                         | ENIR1        | R/W    | External Interrupt 1 | 00000000 <sub>B</sub> |  |

| 0000CB <sub>H</sub>                        | External Interrupt Source 1                                         | EIRR1        | R/W    |                      | XXXXXXXX <sub>B</sub> |  |

| 0000CC <sub>H</sub>                        | Detection Level Setting 1                                           | ELVR1        | R/W    |                      | 00000000 <sub>B</sub> |  |

| 0000CD <sub>H</sub>                        |                                                                     |              |        |                      | 00000000 <sub>B</sub> |  |

| 0000CE <sub>H</sub>                        | External Interrupt Source Select                                    | EISSR        | R/W    |                      | 00000000 <sub>B</sub> |  |

| 0000CF <sub>H</sub>                        | PLL/Sub clock Control Register                                      | PSCCR        | W      |                      | XXXX0000 <sub>B</sub> |  |

*(Continued)*

| Address                                    | Register               | Abbreviation | Access   | Resource name         | Initial value          |

|--------------------------------------------|------------------------|--------------|----------|-----------------------|------------------------|

| 0000D0 <sub>H</sub> to 0000FF <sub>H</sub> |                        |              | Reserved |                       |                        |

| 007900 <sub>H</sub> to 007917 <sub>H</sub> |                        |              | Reserved |                       |                        |

| 007918 <sub>H</sub>                        | Reload Register LC     | PRLLC        | R/W      | 16-bit PPG C/D        | XXXXXXXX <sub>B</sub>  |

| 007919 <sub>H</sub>                        | Reload Register HC     | PRLHC        | R/W      |                       | XXXXXXXX <sub>B</sub>  |

| 00791A <sub>H</sub>                        | Reload Register LD     | PRLLD        | R/W      |                       | XXXXXXXX <sub>B</sub>  |

| 00791B <sub>H</sub>                        | Reload Register HD     | PRLHD        | R/W      |                       | XXXXXXXX <sub>B</sub>  |

| 00791C <sub>H</sub>                        | Reload Register LE     | PRLLE        | R/W      | 16-bit PPG E/F        | XXXXXXXX <sub>B</sub>  |

| 00791D <sub>H</sub>                        | Reload Register HE     | PRLHE        | R/W      |                       | XXXXXXXX <sub>B</sub>  |

| 00791E <sub>H</sub>                        | Reload Register LF     | PRLLF        | R/W      |                       | XXXXXXXX <sub>B</sub>  |

| 00791F <sub>H</sub>                        | Reload Register HF     | PRLHF        | R/W      |                       | XXXXXXXX <sub>B</sub>  |

| 007920 <sub>H</sub>                        | Input Capture 0        | IPCP0        | R        | Input Capture 0/1     | XXXXXXXX <sub>B</sub>  |

| 007921 <sub>H</sub>                        | Input Capture 0        | IPCP0        | R        |                       | XXXXXXXX <sub>B</sub>  |

| 007922 <sub>H</sub>                        | Input Capture 1        | IPCP1        | R        |                       | XXXXXXXX <sub>B</sub>  |

| 007923 <sub>H</sub>                        | Input Capture 1        | IPCP1        | R        |                       | XXXXXXXX <sub>B</sub>  |

| 007924 <sub>H</sub>                        | Input Capture 2        | IPCP2        | R        | Input Capture 2/3     | XXXXXXXX <sub>B</sub>  |

| 007925 <sub>H</sub>                        | Input Capture 2        | IPCP2        | R        |                       | XXXXXXXX <sub>B</sub>  |

| 007926 <sub>H</sub>                        | Input Capture 3        | IPCP3        | R        |                       | XXXXXXXX <sub>B</sub>  |

| 007927 <sub>H</sub>                        | Input Capture 3        | IPCP3        | R        |                       | XXXXXXXX <sub>B</sub>  |

| 007928 <sub>H</sub> to 00793F <sub>H</sub> |                        |              | Reserved |                       |                        |

| 007940 <sub>H</sub>                        | Timer Data 0           | TCDT0        | R/W      | Free-run Timer 0      | 00000000 <sub>B</sub>  |

| 007941 <sub>H</sub>                        | Timer Data 0           | TCDT0        | R/W      |                       | 00000000 <sub>B</sub>  |

| 007942 <sub>H</sub>                        | Timer Control Status 0 | TCCSL0       | R/W      |                       | 00000000 <sub>B</sub>  |

| 007943 <sub>H</sub>                        | Timer Control Status 0 | TCCSH0       | R/W      |                       | 0XXXXXXXX <sub>B</sub> |

| 007944 <sub>H</sub> to 00794B <sub>H</sub> |                        |              | Reserved |                       |                        |

| 00794C <sub>H</sub>                        | Timer 2/Reload 2       | TMR2/TMRL R2 | R/W      | 16-bit Reload Timer 2 | XXXXXXXX <sub>B</sub>  |

| 00794D <sub>H</sub>                        |                        |              | R/W      |                       | XXXXXXXX <sub>B</sub>  |

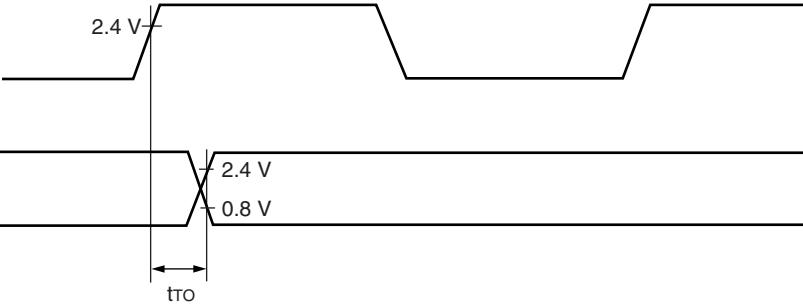

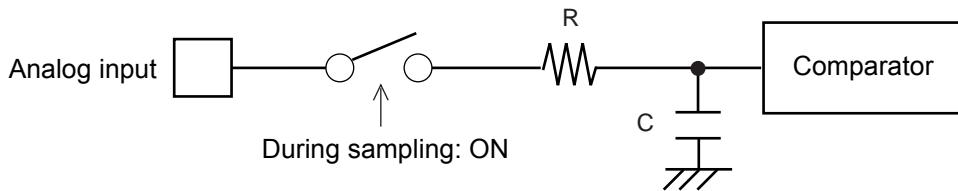

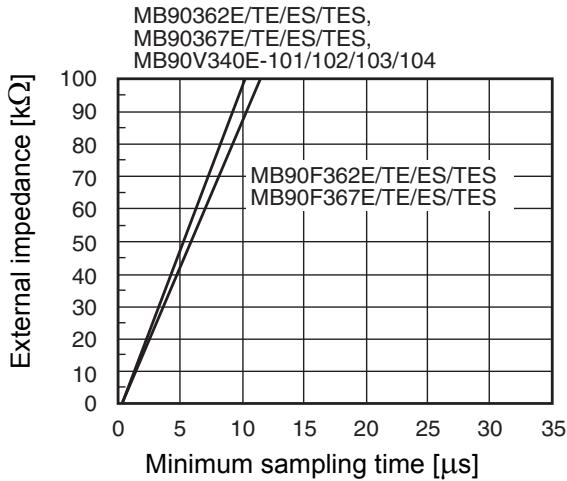

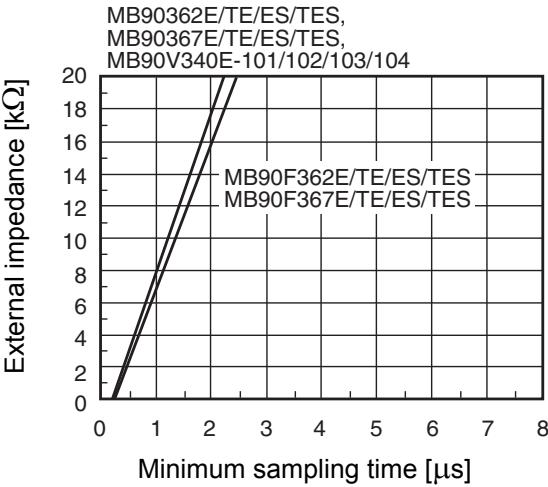

| 00794E <sub>H</sub>                        | Timer 3/Reload 3       | TMR3/TMRL R3 | R/W      | 16-bit Reload Timer 3 | XXXXXXXX <sub>B</sub>  |